Настоящее изобретение относится к полупроводниковому запоминающему устройству для предзаряда строчной цепи, и более конкретно, к синхронному полупроводниковому запоминающему устройству для автоматического предзаряда строчной цепи.

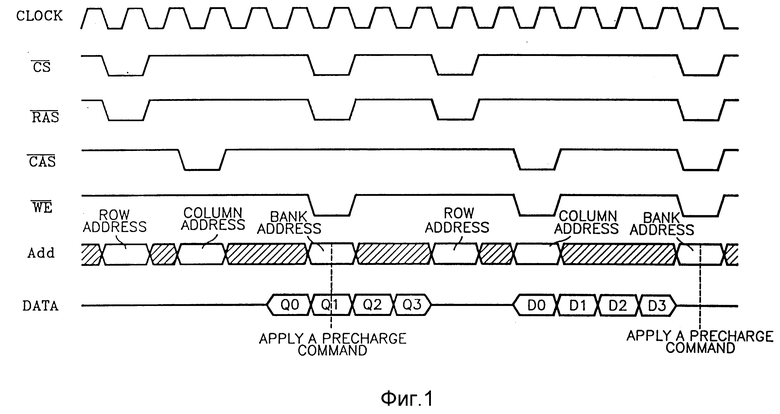

Синхронное полупроводниковое запоминающее устройство, которое было разработано для высокоскоростной работы, выполняет все операции, требуемые при выборке данных, в соответствии с системными тактовыми импульсами (или синхроимпульсами) постоянного периода, поданными извне. Используя регистр установки режима, такое синхронное полупроводниковое запоминающее устройство устанавливает различные режимы работы для определения задержки и длины пакета. В полупроводниковом запоминающем устройстве, при выполнении операции считывания или записи одной строки, возбуждаемая строчная цепь должна быть предзаряжена для выполнения операции считывания или записи другой строки. Как показано на фиг. 1, в обычном полупроводниковом запоминающем устройстве строчная цепь предзаряжается только, когда снаружи приложена команда предзаряда после того, как возбуждена одна строка. В синхронном полупроводниковом запоминающем устройстве, которое работает в соответствии с системными тактовыми импульсами и выполняет операцию считывания/записи согласно определенной информации о длине пакета и задержке, в случае, когда операция предзаряда выполняется в ответ на приложенную извне команду предзаряда, как описано выше, имеется неудобство в том, что подходящий для предзаряда строчной цепи момент времени должен быть жестко задан, и трудно выполнить эффективную (т.е. с уменьшенным потреблением энергии) операцию предзаряда.

Поэтому целью настоящего изобретения является выполнение синхронного полупроводникового запоминающего устройства, которое способно внутренне и автоматически предзаряжать строчную цепь.

Другая цель настоящего изобретения состоит в выполнении синхронного полупроводникового запоминающего устройства с надежным предзарядом строчной цепи.

Для достижения вышеназванных целей полупроводниковое запоминающее устройство по настоящему изобретению, которое включает в себя множество групп блоков памяти, буфер сигнала стробирования адреса строки, буфер сигнала адреса столбца и генератор адреса столбца, и которое выполняет операцию выборки данных, соответствующую информации о длине пакета и задержке, относительно системного тактирования с заранее заданной частотой, содержит прибор, который генерирует сигнал для автоматического предзаряда одной группы блоков памяти в ответ на сигнал стробирования адреса строки и сигнал с информацией о длине пакета и задержке после того, как операция адресации для одной группы блоков данных выполнена. Такой сигнал предзаряда передается в буфер сигнала стробирования адреса строки для предзаряда одной группы блоков памяти.

В подробном описании предпочтительного выполнения настоящего изобретения, представленном ниже, сделаны ссылки на сопровождающие чертежи, на которых:

Фиг. 1 является временной диаграммой, показывающей функционирование в соответствии с обычным способом предзаряда,

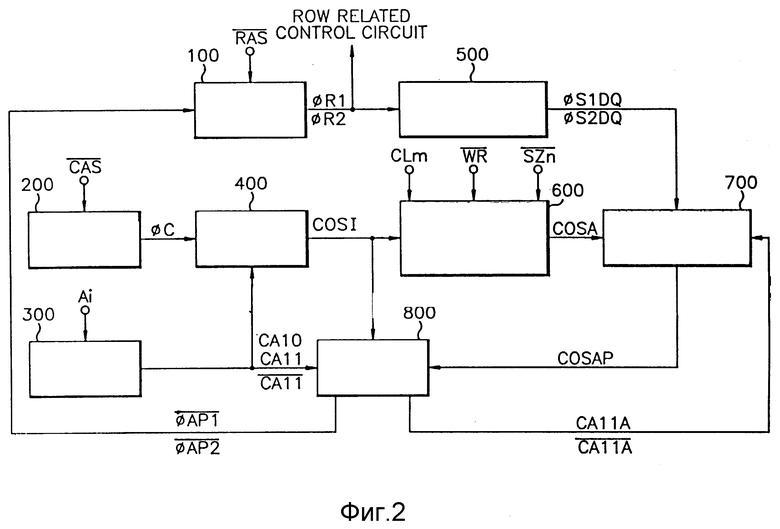

Фиг. 2 является блок-схемой, показывающей конструкцию для осуществления функции автоматического предзаряда согласно настоящему изобретению;

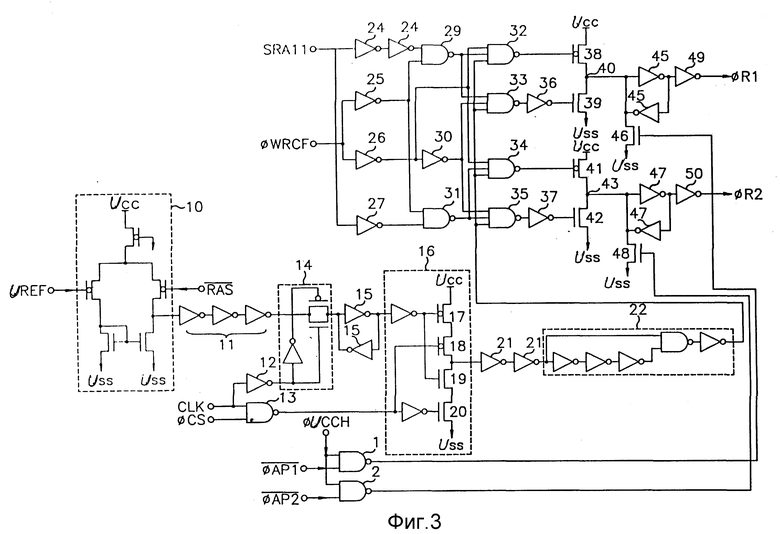

Фиг. 3 представляет принципиальную схему буфера RAS (строба адреса строки) согласно настоящему изобретению, показанному на фиг. 2;

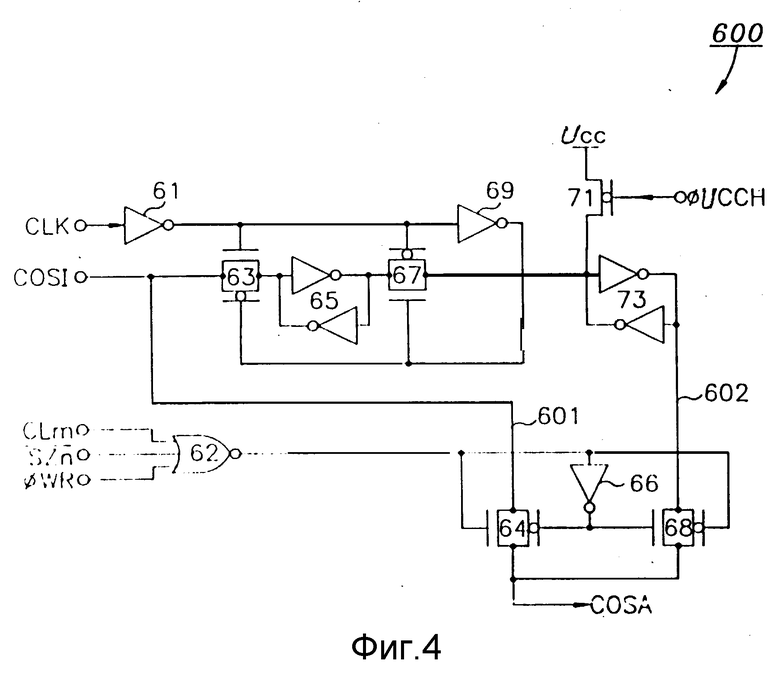

Фиг. 4 является принципиальной схемой генератора сигнала данных о пакете и задержке по настоящему изобретению, представленному на фиг. 2;

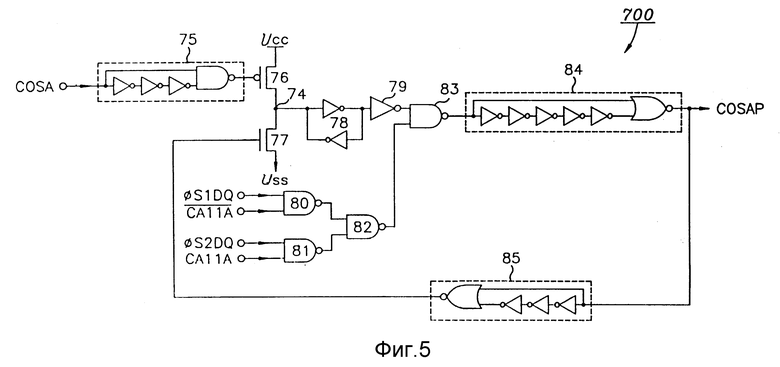

Фиг. 5 является принципиальной схемой детектора сигнала данных о пакете и задержке по настоящему изобретению, представленному на фиг. 2;

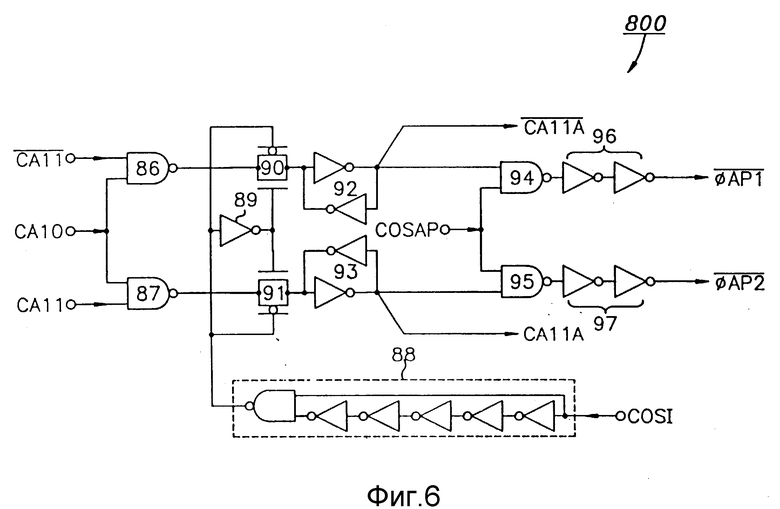

Фиг. 6 является принципиальной схемой генератора сигнала предзаряда по настоящему изобретению, представленному на фиг. 2;

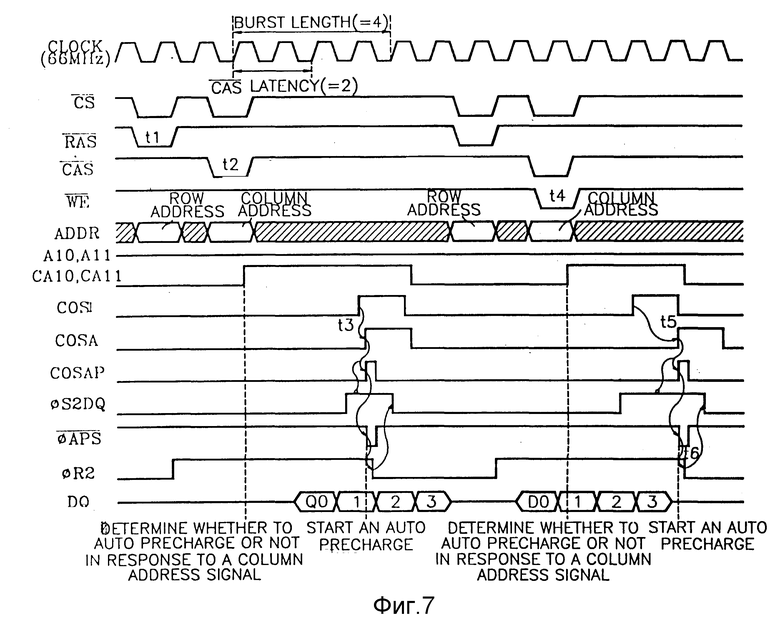

Фиг. 7 представляет временную диаграмму работы в соответствии со способом автоматического предзаряда настоящего изобретения в предположении, что системная тактовая частота составляет 66 МГц, длина пакета равна 4 тактам, а задержка CAS (строба адреса столбца) равна 2 тактам;

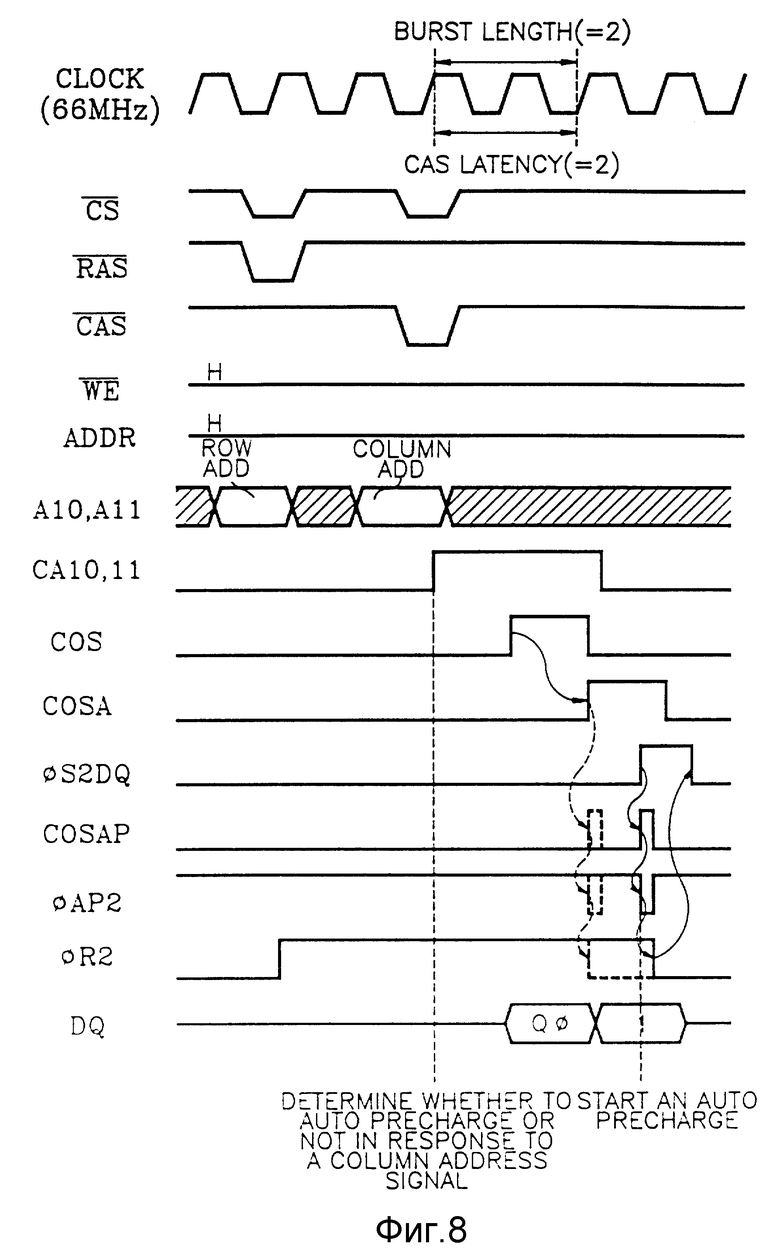

Фиг. 8 представляет временную диаграмму работы в соответствии со способом автоматического продзаряда настоящего изобретения в предположении, что системная тактовая частота составляет 66 МГц, длина пакета равна 2 тактам и задержка CAS равна 2 тактам.

Конструкция по фиг. 2, требуемая в реализации функции автоматического предзаряда согласно настоящему изобретению, содержит буфер 100  для приема сигнала

для приема сигнала  строба адреса строки и генерирования затем главных тактовых импульсов ⊘R1 и ⊘R2 строки, буфер 200

строба адреса строки и генерирования затем главных тактовых импульсов ⊘R1 и ⊘R2 строки, буфер 200  для приема сигнала

для приема сигнала  строба адреса столбца и генерирования затем главных тактовых импульсов ⊘С столбца, которые возбуждают схемы управления, относящиеся к столбцу, генератор 300 адреса столбца для приема и преобразования сигнала Ai адреса на КМОП-уровень и затем генерирования множества сигналов адреса столбца (включая CA10, CA11 и

строба адреса столбца и генерирования затем главных тактовых импульсов ⊘С столбца, которые возбуждают схемы управления, относящиеся к столбцу, генератор 300 адреса столбца для приема и преобразования сигнала Ai адреса на КМОП-уровень и затем генерирования множества сигналов адреса столбца (включая CA10, CA11 и  ) из преобразованного сигнала адреса, детектор 400 конца пакета для приема главных тактовых импульсов ⊘C столбца и отсчитанных сигналов адреса столбца и генерирования затем сигнала COSI обнаружения длины пакета, временной контроллер 500 для приема главных тактовых импульсов ⊘R1 и ⊘R2 строки и генерирования затем сигналов ⊘S1DQ и ⊘S2DQ временного управления, генератор 600 сигнала данных о пакете и задержке для приема сигнала COS1 обнаружения длины пакета, сигнала CLm данных о задержка

) из преобразованного сигнала адреса, детектор 400 конца пакета для приема главных тактовых импульсов ⊘C столбца и отсчитанных сигналов адреса столбца и генерирования затем сигнала COSI обнаружения длины пакета, временной контроллер 500 для приема главных тактовых импульсов ⊘R1 и ⊘R2 строки и генерирования затем сигналов ⊘S1DQ и ⊘S2DQ временного управления, генератор 600 сигнала данных о пакете и задержке для приема сигнала COS1 обнаружения длины пакета, сигнала CLm данных о задержка  (где m обозначает величину задержки), сигнала ⊘WR данных о возбуждении

(где m обозначает величину задержки), сигнала ⊘WR данных о возбуждении  (где

(где  - сигнал разрешения записи) и сигнала

- сигнал разрешения записи) и сигнала  длины пакета (где n обозначает длину пакета) и генерирования затем сигнала СOSA данных о пакете и задержке, детектор 700 данных о пакете и задержке для приема сигналов ⊘S1DQ и ⊘S2DQ временного управления, сигнала COSA данных о пакете и задержке и сигналов CA11A и

длины пакета (где n обозначает длину пакета) и генерирования затем сигнала СOSA данных о пакете и задержке, детектор 700 данных о пакете и задержке для приема сигналов ⊘S1DQ и ⊘S2DQ временного управления, сигнала COSA данных о пакете и задержке и сигналов CA11A и  обнаружения возбуждения адреса столбца, выработанных генератором 800 сигнала предзаряда, и генерирования затем сигнала COSAP обнаружение данных о пакете и задержке, и генератор 800 сигнала предзаряда для приема сигналов CA10, CA11 и

обнаружения возбуждения адреса столбца, выработанных генератором 800 сигнала предзаряда, и генерирования затем сигнала COSAP обнаружение данных о пакете и задержке, и генератор 800 сигнала предзаряда для приема сигналов CA10, CA11 и  адреса столбца, сигнала COS1 обнаружения длины пакета и сигнала COSAP обнаружения данных о пакете и задержке и генерирования и подачи затем сигналов

адреса столбца, сигнала COS1 обнаружения длины пакета и сигнала COSAP обнаружения данных о пакете и задержке и генерирования и подачи затем сигналов  предзаряда на буфер 100

предзаряда на буфер 100  и сигналов CA11A и

и сигналов CA11A и  обнаружения возбуждения адреса столбца на детектор 700 данных о пакете и задержке.

обнаружения возбуждения адреса столбца на детектор 700 данных о пакете и задержке.

Фиг. 3 является подробной принципиальной схемой, показывающей буфер 100  по фиг.2, представляющий конструкцию, минимально необходимую для реализации функции автоматического предзаряда согласно настоящему изобретению. Дифференциальный усилитель 10 с P-канальным входом принимает опорное напряжение UREF и сигнал

по фиг.2, представляющий конструкцию, минимально необходимую для реализации функции автоматического предзаряда согласно настоящему изобретению. Дифференциальный усилитель 10 с P-канальным входом принимает опорное напряжение UREF и сигнал  строба адреса строки, усиливает сигнал

строба адреса строки, усиливает сигнал  строба адреса строки в соответствии с разностью напряжений между ними и затем выводит внутренний сигнал

строба адреса строки в соответствии с разностью напряжений между ними и затем выводит внутренний сигнал  строба адреса строки, преобразованный на КМОП-уровень. Выход дифференциального усилителя 10 подан на вентильную схему 14 передачи через три инвертора 11. Работа вентильной схемы 14 передачи управляется системными тактовыми импульсами CLK. Прошедший через вентильную схему 14 передачи сигнал подается на фиксатор 15 ("защелку"). Выходной сигнал фиксатора 15 инвертируется и затем прикладывается к РМОП-транзистору 17 и NМОП-транзистору 19 в инверторе 16. Исток PМОП-транзистора 17 соединен с напряжением Uccпитания, а сток NМОП-транзистора 19 - с выходным контактом инвертора 16. Выходной сигнал вентиля 13 И-НЕ, принимающего системные тактовые импульсы CLK и сигнал ⊘CS выбора кристалла, приложен к затвору PМОН-транзистора 18, включенного между стоками PМОП-транзистора 17 и NМОП-транзистора 19, а инвертированный выходной сигнал вентиля 13 Н-НЕ приложен к затвору NМОП-транзистора 20, включенного между NМОП-транзистором 19 и напряжением Uss подложки (напряжение земли). Выходной сигнал инвертора 16 подан на схему 22 формирования импульсов через два инвертора 21.

строба адреса строки, преобразованный на КМОП-уровень. Выход дифференциального усилителя 10 подан на вентильную схему 14 передачи через три инвертора 11. Работа вентильной схемы 14 передачи управляется системными тактовыми импульсами CLK. Прошедший через вентильную схему 14 передачи сигнал подается на фиксатор 15 ("защелку"). Выходной сигнал фиксатора 15 инвертируется и затем прикладывается к РМОП-транзистору 17 и NМОП-транзистору 19 в инверторе 16. Исток PМОП-транзистора 17 соединен с напряжением Uccпитания, а сток NМОП-транзистора 19 - с выходным контактом инвертора 16. Выходной сигнал вентиля 13 И-НЕ, принимающего системные тактовые импульсы CLK и сигнал ⊘CS выбора кристалла, приложен к затвору PМОН-транзистора 18, включенного между стоками PМОП-транзистора 17 и NМОП-транзистора 19, а инвертированный выходной сигнал вентиля 13 Н-НЕ приложен к затвору NМОП-транзистора 20, включенного между NМОП-транзистором 19 и напряжением Uss подложки (напряжение земли). Выходной сигнал инвертора 16 подан на схему 22 формирования импульсов через два инвертора 21.

Сигнал SRA11 адреса, который выбирает группу блоков памяти, приложен к вентилю 29 И-НЕ через два инвертора 24, а к вентилю 31 И-НЕ - через инвертор 27. Сигнал ⊘WRCF, который возбуждается после того, как возбужден сигнал  возбуждения записи, приложен к вентилям 29 и 31 И-НЕ через инвертор 25, а к вентилям 32 и 34 И-НЕ - через инвертор 26. Выходной сигнал вентиля 29 И-НЕ приложен к вентилям 32 и 33 И-НЕ. Выходной сигнал инвертора 26 приложен к вентилям 33 и 35 И-НЕ через инвертор 30. Выходной сигнал вентиля 31 И-НЕ приложен к вентилям 34 и 35 И-НЕ. Выходной сигнал схемы 22 сформирования импульсов подается на вентили 32, 33, 34 и 35 И-НЕ одновременно. Выходной сигнал вентиля 32 И-НЕ приложен к затвору PМОП-транзистора 38, тракт исток-сток которого включен между напряжением Uccпитания и первым узлом 40 детектирования. Выходной сигнал вентиля 33 И-НЕ приложен через инвертор 36 к затвору NМОП-транзистора 39, тракт сток-исток которого включен между первым узлом 40 детектирования и напряжением Uss подложки (напряжение земли). Выходной сигнал вентиля 34 И-НЕ приложен к затвору PМОП-транзистора 41, тракт исток-сток которого включен между напряжением Uccпитания и вторым узлом 43 детектирования. Выход вентиля 35 И-НЕ приложен через инвестор 37 к затвору NМОП-транзистора 42, тракт сток-исток которого включен между вторым узлом 43 детектирования и напряжением Uss подложки.

возбуждения записи, приложен к вентилям 29 и 31 И-НЕ через инвертор 25, а к вентилям 32 и 34 И-НЕ - через инвертор 26. Выходной сигнал вентиля 29 И-НЕ приложен к вентилям 32 и 33 И-НЕ. Выходной сигнал инвертора 26 приложен к вентилям 33 и 35 И-НЕ через инвертор 30. Выходной сигнал вентиля 31 И-НЕ приложен к вентилям 34 и 35 И-НЕ. Выходной сигнал схемы 22 сформирования импульсов подается на вентили 32, 33, 34 и 35 И-НЕ одновременно. Выходной сигнал вентиля 32 И-НЕ приложен к затвору PМОП-транзистора 38, тракт исток-сток которого включен между напряжением Uccпитания и первым узлом 40 детектирования. Выходной сигнал вентиля 33 И-НЕ приложен через инвертор 36 к затвору NМОП-транзистора 39, тракт сток-исток которого включен между первым узлом 40 детектирования и напряжением Uss подложки (напряжение земли). Выходной сигнал вентиля 34 И-НЕ приложен к затвору PМОП-транзистора 41, тракт исток-сток которого включен между напряжением Uccпитания и вторым узлом 43 детектирования. Выход вентиля 35 И-НЕ приложен через инвестор 37 к затвору NМОП-транзистора 42, тракт сток-исток которого включен между вторым узлом 43 детектирования и напряжением Uss подложки.

Между первым узлом 40 детектирования и напряжением подложки включен тракт сток-исток NМОП-транзистора 46 с затвором, подключенным к выходу вентиля 1 И-НЕ, который принимает сигнал ⊘UCCH детектирования уровня напряжения питания и первый сигнал  предзаряда, выработанный генератором 800 сигнала предзаряда по фиг. 2. Точно так же между вторым узлом 43 детектирования и напряжением Uss подложки включен тракт сток-исток NМОП-транзистора 48 с затвором, подключенным к выходу вентиля 2 И-НЕ, который принимает сигнал ⊘UCCH обнаружения уровня напряжения питания и второй сигнал

предзаряда, выработанный генератором 800 сигнала предзаряда по фиг. 2. Точно так же между вторым узлом 43 детектирования и напряжением Uss подложки включен тракт сток-исток NМОП-транзистора 48 с затвором, подключенным к выходу вентиля 2 И-НЕ, который принимает сигнал ⊘UCCH обнаружения уровня напряжения питания и второй сигнал  предзаряда, выработанный генератором 800 сигнала предзаряда по фиг. 2. Сигналы на первом и втором узлах 40 и 43 детектирования вырабатываются соответственно как первый и второй главные тактовые импульсы ⊘R1 и ⊘R2 строки через фиксаторы 45 и 47 и инверторы 49 и 50. Главные тактовые импульсы ⊘R1 и ⊘R2 строки поданы на управляющие схемы, относящиеся к строке, т.е. к схемам, которые управляют группой блоков памяти и возбуждают в них числовые шины.

предзаряда, выработанный генератором 800 сигнала предзаряда по фиг. 2. Сигналы на первом и втором узлах 40 и 43 детектирования вырабатываются соответственно как первый и второй главные тактовые импульсы ⊘R1 и ⊘R2 строки через фиксаторы 45 и 47 и инверторы 49 и 50. Главные тактовые импульсы ⊘R1 и ⊘R2 строки поданы на управляющие схемы, относящиеся к строке, т.е. к схемам, которые управляют группой блоков памяти и возбуждают в них числовые шины.

Фиг. 4 является подробной принципиальной схемой, показывающей генератор 600 сигнала данных о пакете и задержке по фиг. 2. Сигнал COS1 обнаружения длины пакеты, выработанный детектором 400 конца пакета на фиг. 2, передается на фиксатор 73 через вентиль 63 передачи КМОП-типа, фиксатор 65 и вентиль 67 передачи. Электрод n-типа проводимости вентиля 63 передачи и электрод p-типа проводимости вентиля 67 передачи управляются системными тактовыми импульсами CLK, которые проинвертированы на инверторе 61. Электрод p-типа проводимости вентиля 63 передачи и электрод n-типа проводимости вентиля 67 передачи управляются системными тактовыми импульсами CLK, которые проходят через инверторы 61 и 69. Тракт исток-сток PМОП-транзистора 71 включен между напряжением Uccпитания и фиксатором 73, а к его затвору приложен сигнал ⊘UCCH обнаружения уровня напряжения питания. Сигнал COS1 обнаружения длины пакета выводится в качестве сигнала COSA данных о пакете и задержке через вентиль 64 передачи, и выходной сигнал фиксатора 73 также выводится в качестве сигнала COSA данных о пакете и задержке через вентиль 68 передачи. Вентили 64 и 68 передачи управляются по выходному сигналу вентиля 62 И-НЕ, который принимает сигнал CLm данных о задержке  , сигнал

, сигнал  длины пакета и сигнал ⊘WR данных о возбуждении

длины пакета и сигнал ⊘WR данных о возбуждении  . Электрод n-типа проводимости вентиля 64 передачи и электрод p-типа проводимости вентиля 68 передачи подключены непосредственно к выходу вентиля 62 И-НЕ, а электрод p-типа проводимости вентиля 64 передачи и электрод n-типа проводимости вентиля 68 передачи управляются выходным сигналом вентиля 62 И-НЕ, который пропускается через инвертор 66. Сигнал COSA данных о пакете и задержке, выработанный через вентили 64 и 68 передачи, передается на детектор 700 данных о пакете и задержке по фиг. 2.

. Электрод n-типа проводимости вентиля 64 передачи и электрод p-типа проводимости вентиля 68 передачи подключены непосредственно к выходу вентиля 62 И-НЕ, а электрод p-типа проводимости вентиля 64 передачи и электрод n-типа проводимости вентиля 68 передачи управляются выходным сигналом вентиля 62 И-НЕ, который пропускается через инвертор 66. Сигнал COSA данных о пакете и задержке, выработанный через вентили 64 и 68 передачи, передается на детектор 700 данных о пакете и задержке по фиг. 2.

Фиг. 5 является подробной принципиальной схемой детектора 700 данных о пакете и задержке по фиг. 2. Сигнал COSA данных о пакете и задержке приложен к схеме 75 формирования импульсов, а выход схемы 76 формирования импульсов соединен с затвором PМОП-транзистора 76, тракт исток-сток которого включен между напряжением Uccпитания и узлом 74. Тракт сток-исток NМОП-транзистора 77 включен между узлом 74 и напряжением Uss подложки. Узел 74 подключен ко входу вентиля 83 И-НЕ через фиксатор 78 и инвертор 79. Другой вход вентиля 83 И-НЕ соединен с выходом вентиля 82 И-НЕ, который выдает логическое состояние комбинации сравнения между сигналами CA11A и  обнаружения возбуждения адреса столбца, вырабатываемыми генератором 800 сигнала предзаряда по фиг. 2, и сигналами ⊘S1DQ и ⊘S2DQ временного управления, вырабатываемыми временным контроллером 500 по фиг. 2. Сигнал ⊘S1DQ временного управления и сигнал

обнаружения возбуждения адреса столбца, вырабатываемыми генератором 800 сигнала предзаряда по фиг. 2, и сигналами ⊘S1DQ и ⊘S2DQ временного управления, вырабатываемыми временным контроллером 500 по фиг. 2. Сигнал ⊘S1DQ временного управления и сигнал  обнаружения возбуждения адреса столбца приложены к вентилю 80 И-НЕ, а сигнал ⊘S2DQ временного управления и сигнал CA11A обнаружения возбуждения адреса столбца - к вентилю 82 И-НЕ. Выходной сигнал вентиля 83 И-НЕ выдается в качестве сигнала COSAP обнаружения данных о пакете и задержке через схему 84 формирования импульсов, а выход схемы 84 формирования импульсов подключен к затвору NМОП-транзистора 77 через схему 85 формирования импульсов.

обнаружения возбуждения адреса столбца приложены к вентилю 80 И-НЕ, а сигнал ⊘S2DQ временного управления и сигнал CA11A обнаружения возбуждения адреса столбца - к вентилю 82 И-НЕ. Выходной сигнал вентиля 83 И-НЕ выдается в качестве сигнала COSAP обнаружения данных о пакете и задержке через схему 84 формирования импульсов, а выход схемы 84 формирования импульсов подключен к затвору NМОП-транзистора 77 через схему 85 формирования импульсов.

Фиг. 6 является подробной принципиальной схемой, показывающей генератор 800 сигнала предзаряда по фиг. 2. Сигналы  и CA11 адреса столбца приложены соответственно к вентилям 86 и 87 И-НЕ и сигнал CA10 адреса столбца одновременно приложен к вентилям 86 и 87 И-НЕ. Выходной сигнал вентиля 86 И-НЕ выдается в качестве сигнала

и CA11 адреса столбца приложены соответственно к вентилям 86 и 87 И-НЕ и сигнал CA10 адреса столбца одновременно приложен к вентилям 86 и 87 И-НЕ. Выходной сигнал вентиля 86 И-НЕ выдается в качестве сигнала  обнаружения возбуждения адреса столбца через вентиль 90 передачи и фиксатор 92, а выходной сигнал вентиля 87 И-НЕ выдается в качестве сигнала CA11A обнаружения возбуждения адреса столбца через вентиль 91 передачи и фиксатор 93. Вентили 90 и 91 передачи управляются выходным сигналом схемы 88 формирования импульсов, которая принимает сигнал COS1 обнаружения длины пакета. Электроды p-типа проводимости вентилей 90 и 91 передачи соединены непосредственно с выходом схемы 88 формирования импульсов, а электроды n-типа проводимости этих вентилей соединены с выходом схемы 68 сформирования импульсов, пропущенным через инвертор 89. Выходные сигналы фиксаторов 92 и 93 приложены соответственно к вентилям 94 и 95 И-НЕ, которые вместе принимают сигнал COSAP обнаружения данных о пакете и задержке. Выходные сигналы вентилей 94 и 95 И-НЕ выдаются соответственно в качестве первого и второго сигналов

обнаружения возбуждения адреса столбца через вентиль 90 передачи и фиксатор 92, а выходной сигнал вентиля 87 И-НЕ выдается в качестве сигнала CA11A обнаружения возбуждения адреса столбца через вентиль 91 передачи и фиксатор 93. Вентили 90 и 91 передачи управляются выходным сигналом схемы 88 формирования импульсов, которая принимает сигнал COS1 обнаружения длины пакета. Электроды p-типа проводимости вентилей 90 и 91 передачи соединены непосредственно с выходом схемы 88 формирования импульсов, а электроды n-типа проводимости этих вентилей соединены с выходом схемы 68 сформирования импульсов, пропущенным через инвертор 89. Выходные сигналы фиксаторов 92 и 93 приложены соответственно к вентилям 94 и 95 И-НЕ, которые вместе принимают сигнал COSAP обнаружения данных о пакете и задержке. Выходные сигналы вентилей 94 и 95 И-НЕ выдаются соответственно в качестве первого и второго сигналов  предзаряда через инверторы 96 и 97.

предзаряда через инверторы 96 и 97.

Теперь, с обращением к временной диаграмме фиг. 7, будет описана операция предзаряда согласно настоящему изобретению в предположении, что частота системных тактовых импульсов составляет 66 МГц, длина пакета равна 4 тактам, а величина задержки  равна 2 тактам. Сначала будет описан процесс предзаряда в цикле считывания, который начинается от момента времени t1. В момент t1, если сигнал

равна 2 тактам. Сначала будет описан процесс предзаряда в цикле считывания, который начинается от момента времени t1. В момент t1, если сигнал  строба адреса строки возбужден в низкоуровневое состояние, фиксируется адрес строки. Как показано на фиг. 3, выходной сигнал дифференциального усилителя 10 приобретает логическое высокое состояние посредством возбужденного сигнала

строба адреса строки возбужден в низкоуровневое состояние, фиксируется адрес строки. Как показано на фиг. 3, выходной сигнал дифференциального усилителя 10 приобретает логическое высокое состояние посредством возбужденного сигнала  строба адреса строки и, если системный такт CLK находится в логическом низком состоянии, то сигнал логического низкого состояния прикладывается к затвору PМОП-транзистора 17 в инверторе 16. Когда системный такт CLK переходит в логическое высокое состояние (такт 1), схема 14 вентиля передачи выключается, а P-канальный транзистор 18 инвертора 16 включается (сигнал ⊘CS выбора кристалла остается в логическом высоком состоянии во время этой операции), в результате чего выходной сигнал инвертора 16 переходит в логическое высокое состояние. Таким образом, на выходе схемы 22 формирования импульса появляется короткий импульс логического высокого уровня, который затем прикладывается к вентилям 32, 33, 34 и 35 И-ИЕ, тем самым возбуждая эти вентили И-НЕ. Поскольку сигнал ⊘WRCF находится в логическом низком состоянии (из-за того, что сигнал

строба адреса строки и, если системный такт CLK находится в логическом низком состоянии, то сигнал логического низкого состояния прикладывается к затвору PМОП-транзистора 17 в инверторе 16. Когда системный такт CLK переходит в логическое высокое состояние (такт 1), схема 14 вентиля передачи выключается, а P-канальный транзистор 18 инвертора 16 включается (сигнал ⊘CS выбора кристалла остается в логическом высоком состоянии во время этой операции), в результате чего выходной сигнал инвертора 16 переходит в логическое высокое состояние. Таким образом, на выходе схемы 22 формирования импульса появляется короткий импульс логического высокого уровня, который затем прикладывается к вентилям 32, 33, 34 и 35 И-ИЕ, тем самым возбуждая эти вентили И-НЕ. Поскольку сигнал ⊘WRCF находится в логическом низком состоянии (из-за того, что сигнал  возбуждения записи не возбужден), если сигнал SRA11 выбора группы блоков переведен в логическое высокое состояние, главный тактовый импульс ⊘R2 строки логического высокого уровня генерируется PМОП-транзистором 41, который включен выходным сигналом вентиля 34 И-НЕ логического низкого состояния. Полагая, что этот главный тактовый импульс ⊘R2 строки подан на схемы, относящиеся к строке, для второй группы блоков памяти (настоящее изобретение приложено к устройству полупроводниковой памяти с двумя группами блоков памяти), все время, пока вводится сигнал SRA11 выбора группы блоков логического высокого состояния, главный тактовый импульс ⊘R2 строки остается в логическом высоком состоянии с помощью фиксатора 47, как показано на фиг. 7. И обратно, если вводится сигнал SRA11 выбора группы блоков логического низкого состояния, выдается главный тактовый импульс ⊘R1 строки логического высокого состояния вместо главного тактового импульса ⊘R2 строки, чтобы возбудить схемы, относящиеся к строке, для первой группы блоков памяти.

возбуждения записи не возбужден), если сигнал SRA11 выбора группы блоков переведен в логическое высокое состояние, главный тактовый импульс ⊘R2 строки логического высокого уровня генерируется PМОП-транзистором 41, который включен выходным сигналом вентиля 34 И-НЕ логического низкого состояния. Полагая, что этот главный тактовый импульс ⊘R2 строки подан на схемы, относящиеся к строке, для второй группы блоков памяти (настоящее изобретение приложено к устройству полупроводниковой памяти с двумя группами блоков памяти), все время, пока вводится сигнал SRA11 выбора группы блоков логического высокого состояния, главный тактовый импульс ⊘R2 строки остается в логическом высоком состоянии с помощью фиксатора 47, как показано на фиг. 7. И обратно, если вводится сигнал SRA11 выбора группы блоков логического низкого состояния, выдается главный тактовый импульс ⊘R1 строки логического высокого состояния вместо главного тактового импульса ⊘R2 строки, чтобы возбудить схемы, относящиеся к строке, для первой группы блоков памяти.

В момент времени t2 возбуждается сигнал  строба адреса столбца, фиксируется сигнал CAi адреса столбца. Переходить в режим автоматического предзаряда или нет, определяется использованием логических состояний сигналов CA10 и CA11 адреса столбца. Т. е., как показано на фиг. 7, если сигнала CA10 и CA11 адреса столбца находятся в логическом высоком состоянии, то определено выполнять операцию автоматического предзаряда.

строба адреса столбца, фиксируется сигнал CAi адреса столбца. Переходить в режим автоматического предзаряда или нет, определяется использованием логических состояний сигналов CA10 и CA11 адреса столбца. Т. е., как показано на фиг. 7, если сигнала CA10 и CA11 адреса столбца находятся в логическом высоком состоянии, то определено выполнять операцию автоматического предзаряда.

Если в сигнале CLm данных о задержке  m=3 (сигнал CLm) принимает логическое высокое состояние, когда задержка

m=3 (сигнал CLm) принимает логическое высокое состояние, когда задержка  равна 3 тактам), а в сигнале

равна 3 тактам), а в сигнале  длины пакета n= 2 (сигнал

длины пакета n= 2 (сигнал  принимает логическое высокое состояние, когда длина пакета равна 2 тактам на фиг. 4, поскольку задержка

принимает логическое высокое состояние, когда длина пакета равна 2 тактам на фиг. 4, поскольку задержка  равна 2 тактам, и длина пакета равна 4 тактам на фиг. 7), оба сигнала CL3 и

равна 2 тактам, и длина пакета равна 4 тактам на фиг. 7), оба сигнала CL3 и  находятся в логическом низком состоянии. Кроме того, в цикле считывания, сигнал ⊘WR данных о возбуждении

находятся в логическом низком состоянии. Кроме того, в цикле считывания, сигнал ⊘WR данных о возбуждении  остается в логическом низком состоянии. Тем самым вентиль 64 передачи включается, а вентиль 68 передачи выключается, так что сигнал COS1 обнаружения длины пакета, который был возбужден в момент времени t3, выдается в качестве сигнала COSA данных о пакете и задержке логического высокого состояния через вентиль 64 передачи (здесь и далее обозначенным как "прямой тракт 601 передачи"). Как показано на фиг. 5, сигнал COSA данных о пакете и задержке логического высокого состояния пропускается через схему 75 сформирования импульса и затем прикладывается к затвору PМОП-транзистора 76 как короткий импульс логического низкого состояния. Затем короткий импульс логического высокого состояния прикладывается с узла 74 к вентилю 83 И-НЕ через фиксатор 78 и инвертор 79. Поскольку сигнал ⊘S1DQ временного управления и сигнал

остается в логическом низком состоянии. Тем самым вентиль 64 передачи включается, а вентиль 68 передачи выключается, так что сигнал COS1 обнаружения длины пакета, который был возбужден в момент времени t3, выдается в качестве сигнала COSA данных о пакете и задержке логического высокого состояния через вентиль 64 передачи (здесь и далее обозначенным как "прямой тракт 601 передачи"). Как показано на фиг. 5, сигнал COSA данных о пакете и задержке логического высокого состояния пропускается через схему 75 сформирования импульса и затем прикладывается к затвору PМОП-транзистора 76 как короткий импульс логического низкого состояния. Затем короткий импульс логического высокого состояния прикладывается с узла 74 к вентилю 83 И-НЕ через фиксатор 78 и инвертор 79. Поскольку сигнал ⊘S1DQ временного управления и сигнал  обнаружения возбуждения адреса столбца находятся в логическом низком состоянии, а сигнал ⊘S2DQ временного управления и сигнал CA11A обнаружения возбуждения адреса столбца находятся в логическом высоком состоянии, выходной сигнал вентиля 82 И-НЕ, прикладываемый к вентилю 83 И-НЕ, переводится в логическое высокое состояние. Отсюда, выходной сигнал вентиля 83 И-НЕ становится сигналом логического низкого состояния. Следовательно, сигнал логического низкого состояния выводится через схему 84 формирования импульсов в качестве сигнала COSAP обнаружения данных о пакете и задержке логического высокого состояния в виде короткого импульса, как показано на фиг. 7. Схема 85 формирования импульсов, которая образует петлю обратной связи между схемой 84 формирования импульсов и NМОП-транзистором 77, обнаруживает, что сигнал COSAP обнаружения данных о пакете и задержке логического высокого состояния изменен в логическое низкое состояние, и затем прикладывает короткий импульсный сигнал логического высокого состояния к затвору NМОП-транзистора 77, тем самым обеспечивая снятие возбуждения сигнала COSAP обнаружения данных о пакете и задержке.

обнаружения возбуждения адреса столбца находятся в логическом низком состоянии, а сигнал ⊘S2DQ временного управления и сигнал CA11A обнаружения возбуждения адреса столбца находятся в логическом высоком состоянии, выходной сигнал вентиля 82 И-НЕ, прикладываемый к вентилю 83 И-НЕ, переводится в логическое высокое состояние. Отсюда, выходной сигнал вентиля 83 И-НЕ становится сигналом логического низкого состояния. Следовательно, сигнал логического низкого состояния выводится через схему 84 формирования импульсов в качестве сигнала COSAP обнаружения данных о пакете и задержке логического высокого состояния в виде короткого импульса, как показано на фиг. 7. Схема 85 формирования импульсов, которая образует петлю обратной связи между схемой 84 формирования импульсов и NМОП-транзистором 77, обнаруживает, что сигнал COSAP обнаружения данных о пакете и задержке логического высокого состояния изменен в логическое низкое состояние, и затем прикладывает короткий импульсный сигнал логического высокого состояния к затвору NМОП-транзистора 77, тем самым обеспечивая снятие возбуждения сигнала COSAP обнаружения данных о пакете и задержке.

Как показано на фиг. 6, сигналы  и CA11A обнаружения возбуждения адреса столбца генерируются соответственно в логическом низком и высоком состояниях с фиксаторов 92 и 93 посредством сигналов CA10 и CA11 адреса столбца логического высокого состояния. Вентили 90 и 91 передачи включаются коротким импульсом логического низкого состояния, который является откликом на сигнал COS1 обнаружения длины пакета логического высокого состояния. Таким образом, фиксаторы 92 и 93 сохраняют логическое состояние запомненного сигнала CO11 адреса столбца с помощью сигнала COS1 обнаружения длины пакета. Поскольку сигнал COSAP обнаружения данных о пакете и задержке, выдаваемый с фиг. 5, находится в логическом высоком состоянии, первый сигнал

и CA11A обнаружения возбуждения адреса столбца генерируются соответственно в логическом низком и высоком состояниях с фиксаторов 92 и 93 посредством сигналов CA10 и CA11 адреса столбца логического высокого состояния. Вентили 90 и 91 передачи включаются коротким импульсом логического низкого состояния, который является откликом на сигнал COS1 обнаружения длины пакета логического высокого состояния. Таким образом, фиксаторы 92 и 93 сохраняют логическое состояние запомненного сигнала CO11 адреса столбца с помощью сигнала COS1 обнаружения длины пакета. Поскольку сигнал COSAP обнаружения данных о пакете и задержке, выдаваемый с фиг. 5, находится в логическом высоком состоянии, первый сигнал  предзаряда переводится в логическое высокое состояние (невозбужденное состояние), а второй сигнал

предзаряда переводится в логическое высокое состояние (невозбужденное состояние), а второй сигнал  предзаряда - в логическое низкое состояние (возбужденное состояние).

предзаряда - в логическое низкое состояние (возбужденное состояние).

На фиг. 3 показаны первый и второй сигналы  предзаряда, вырабатываемые соответственно в логическом высоком и низком состояниях с фиг. 6, прикладываются соответственно к вентилям 1 и 2 И-НЕ. Соответственно, сигнал логического низкого состояния прикладывается к затвору NМОП-транзистора 46, включенного между узлом 40 детектирования и напряжением Uss подложки, а сигнал логического высокого состояния к затвору NМОП-транзистора 48, включенного между узлом 43 детектирования и напряжением Uss подложки. В результате главный тактовый импульс ⊘R2 строки, который поддерживался в логическом высоком состояние, изменяется в логическое низкое состояние включением пониженного NМОП-транзистора 48, как показано на фиг. 6. Т. е., когда главный тактовый импульс ⊘R2 строки, который был возбужден для возбуждения второй группы блоков памяти (например, возбуждение для операции считывания), выводится из возбуждения, вторая группа блоков памяти автоматически выполняет операцию предзаряда. Операция предзаряда второй группы блоков памяти (не показана) выполняется хорошо известным образом, и поэтому не будет описана в предпочтительном выполнении настоящего изобретения. В аналоге команда предзаряда должна быть приложена насильно извне, чтобы предзарядить любую группу блоков памяти после того, как выполнена операция считывания одного цикла.

предзаряда, вырабатываемые соответственно в логическом высоком и низком состояниях с фиг. 6, прикладываются соответственно к вентилям 1 и 2 И-НЕ. Соответственно, сигнал логического низкого состояния прикладывается к затвору NМОП-транзистора 46, включенного между узлом 40 детектирования и напряжением Uss подложки, а сигнал логического высокого состояния к затвору NМОП-транзистора 48, включенного между узлом 43 детектирования и напряжением Uss подложки. В результате главный тактовый импульс ⊘R2 строки, который поддерживался в логическом высоком состояние, изменяется в логическое низкое состояние включением пониженного NМОП-транзистора 48, как показано на фиг. 6. Т. е., когда главный тактовый импульс ⊘R2 строки, который был возбужден для возбуждения второй группы блоков памяти (например, возбуждение для операции считывания), выводится из возбуждения, вторая группа блоков памяти автоматически выполняет операцию предзаряда. Операция предзаряда второй группы блоков памяти (не показана) выполняется хорошо известным образом, и поэтому не будет описана в предпочтительном выполнении настоящего изобретения. В аналоге команда предзаряда должна быть приложена насильно извне, чтобы предзарядить любую группу блоков памяти после того, как выполнена операция считывания одного цикла.

В операции предзаряда для цикла записи, который начинается в момент времени t4, поскольку сигнал ⊘WR данных о возбуждении  принимает логическое высокое состояние на фиг. 4, тогда как сигнал

принимает логическое высокое состояние на фиг. 4, тогда как сигнал  возбуждения записи возбуждается в логическое низкое состояние в момент времени t5, сигнал COSA данных о пакете и задержке вырабатывается, после задержки на один такт системных тактовых импульсов от сигнала COS1 обнаружения длины пакета, как показано на фиг. 7. Т. е., когда такт 14 системных тактовых импульсов CLK изменяется в логическое низкое состояние, сигнал COS1 обнаружения длины пакета проходит через вентиль 63 передачи, чтобы быть запомненным в фиксаторе 65 (в это время вентиль 67 передачи выключен), а когда такт 15 системных тактовых импульсов CLK изменяется в логическое высокое состояние, сигнал запомненный в фиксаторе 65, проходит через вентиль 67 передачи, фиксатор 73 и вентиль 68 передачи (здесь и далее обозначенные как "тракт 602 задержки") и затем выдается в качестве сигнала COSA данных о пакете и задержке, который задержан на один такт от сигнала COS1 обнаружения длины пакета. Остальные шаги такие же, как и в случае ранее описанного цикла считывания, и операция автоматического предзаряда для второй группы блоков памяти выполняется, когда главный тактовый импульс ⊘R2, который возбуждает вторую группу блоков памяти в момент времени t6, выводится из возбуждения в логическое низкое состояние посредством второго сигнала

возбуждения записи возбуждается в логическое низкое состояние в момент времени t5, сигнал COSA данных о пакете и задержке вырабатывается, после задержки на один такт системных тактовых импульсов от сигнала COS1 обнаружения длины пакета, как показано на фиг. 7. Т. е., когда такт 14 системных тактовых импульсов CLK изменяется в логическое низкое состояние, сигнал COS1 обнаружения длины пакета проходит через вентиль 63 передачи, чтобы быть запомненным в фиксаторе 65 (в это время вентиль 67 передачи выключен), а когда такт 15 системных тактовых импульсов CLK изменяется в логическое высокое состояние, сигнал запомненный в фиксаторе 65, проходит через вентиль 67 передачи, фиксатор 73 и вентиль 68 передачи (здесь и далее обозначенные как "тракт 602 задержки") и затем выдается в качестве сигнала COSA данных о пакете и задержке, который задержан на один такт от сигнала COS1 обнаружения длины пакета. Остальные шаги такие же, как и в случае ранее описанного цикла считывания, и операция автоматического предзаряда для второй группы блоков памяти выполняется, когда главный тактовый импульс ⊘R2, который возбуждает вторую группу блоков памяти в момент времени t6, выводится из возбуждения в логическое низкое состояние посредством второго сигнала  предзаряда логического низкого состояния.

предзаряда логического низкого состояния.

На фиг. 8 показан способ автоматического предзаряда по настоящему изобретению в случае, когда длина пакета равна 2, тогда как сигнал  (n=2) длины пакета находится в логическом высоком состоянии и выходной сигнал вентиля 62 ИЛИ-НЕ тем самым переводится в логическое низкое состояние, сигнал COS1 обнаружения длины пакета передается через такт 602 задержки. Поэтому сигнал COSA данных о пакете и задержке вырабатывается после задержки на один такт системных тактовых импульсов CLK от сигнала COS1 обнаружения длины пакета. Вдобавок, поскольку сигнала COSA данных о пакете и задержке, который выводится как короткий импульс через схему 25 формирования импульсов, соответствует логическому состоянию сигнала ⊘S2DQ временного управления, который вырабатывается спустя заданное время от момента времени возбуждения

(n=2) длины пакета находится в логическом высоком состоянии и выходной сигнал вентиля 62 ИЛИ-НЕ тем самым переводится в логическое низкое состояние, сигнал COS1 обнаружения длины пакета передается через такт 602 задержки. Поэтому сигнал COSA данных о пакете и задержке вырабатывается после задержки на один такт системных тактовых импульсов CLK от сигнала COS1 обнаружения длины пакета. Вдобавок, поскольку сигнала COSA данных о пакете и задержке, который выводится как короткий импульс через схему 25 формирования импульсов, соответствует логическому состоянию сигнала ⊘S2DQ временного управления, который вырабатывается спустя заданное время от момента времени возбуждения  чтобы пройти через вентиль 83 И-НЕ, если сигнал ⊘ S1DQ временного управления находится в логическом высоком состоянии, сигнал COSAP обнаружения данных о пакете и задержке переводится в логическое высокое состояние. Пунктирная линия на фиг. 8 показывает случай, когда данные

чтобы пройти через вентиль 83 И-НЕ, если сигнал ⊘ S1DQ временного управления находится в логическом высоком состоянии, сигнал COSAP обнаружения данных о пакете и задержке переводится в логическое высокое состояние. Пунктирная линия на фиг. 8 показывает случай, когда данные  не управляют автоматическим предзарядом. В результате фиг. 8 показывает, что на сигнал COSAP обнаружения данных о пакете и задержке, требуемый для выработки сигналов

не управляют автоматическим предзарядом. В результате фиг. 8 показывает, что на сигнал COSAP обнаружения данных о пакете и задержке, требуемый для выработки сигналов  автоматического предзаряда, влияет информация, относящаяся к

автоматического предзаряда, влияет информация, относящаяся к  как и информация, относящаяся к длине пакета и задержке

как и информация, относящаяся к длине пакета и задержке

Таким образом, поскольку сигнал автоматического предзаряда согласно настоящему изобретению генерируется в соответствии с информацией, относящейся к длине пакета и задержке, используемой в синхронном полупроводниковом запоминающем устройстве, как и информация, относящаяся к сигналам  и

и  строба адреса строки и столбца, в основном используемая при выборке данных в полупроводниковом запоминающем устройстве, может быть достигнута эффективная надежная функция автоматического предзаряда.

строба адреса строки и столбца, в основном используемая при выборке данных в полупроводниковом запоминающем устройстве, может быть достигнута эффективная надежная функция автоматического предзаряда.

Вышеприведенное описание настоящего изобретения использует схемную конструкции, как показано на фиг. 7, для отображения данных, требуемых при генерировании сигнала автоматического предзаряда, однако сигнал автоматического предзаряда согласно настоящему изобретению может вырабатываться и другой схемной конструкцией.

Изобретение относится к полупроводниковым запоминающим устройствам для автоматического предзаряда строчной цепи. Технический результат заключается в выполнении синхронным полупроводниковым запоминающим устройством автоматического предзаряда строчной цепи. Он достигается тем, что содержит множество групп блоков памяти, буферы для приема сигналов стробов адреса строки и столбца, выполняющие выборку данных в ответ на информацию о длине пакета и задержке. В состав устройства входит генератор адреса столбца, временной контроллер, детектор конца пакета, генератор сигнала данных о пакете и задержке, детектор данных о пакете и задержке, генератор сигнала предзаряда. 8 ил.

Полупроводниковое запоминающее устройство, содержащее множество групп блоков памяти, буфер для приема сигнала строба адреса строки, выполненный с возможностью генерирования главных тактовых импульсов строки, буфер для приема строба адреса столбца, выполненный с возможностью генерирования главных тактовых импульсов, столбца, генератор адреса столбца, выполненный с возможностью приема и преобразования сигнала адреса, отличающееся тем, что устройство содержит детектор конца пакета, один вход которого подключен к выходу буфера для приема строба адреса столбца, а другой - к выходу генератора адреса столба, временной контроллер, выполненный с возможностью приема тактовых импульсов строки и генерирования сигналов временного управления, генератор сигнала данных о пакете и задержке, выполненный с возможностью приема сигналов обнаружения длины пакета, вырабатываемых детектором конца пакета, сигнала данных о задержке строба адреса столбца, сигнала данных о возбуждении сигнала разрешения записи и сигнала длины пакета, а также выполненный с возможностью генерирования сигнала данных о пакете и задержке, детектор данных о пакете и задержке, выполненный с возможностью приема сигналов временного управления и сигнала данных о пакете и задержке, а также сигналов обнаружения возбуждения адреса столбца, вырабатываемых генератором сигнала предзаряда, выполненным с возможностью приема сигнала обнаружения данных о пакете и задержке от детектора данных о пакете и задержке и приема сигналов адреса столбца, сигнала обнаружения длины пакета и генерирования сигналов предзаряда на буфер для приема сигнала строба адреса строки, выполненный с возможностью управления группой блоков памяти и возбуждения в них числовых шин.

| US 4581722 A, 08.04.86 | |||

| US 4907199 A, 06.03.90 | |||

| US 4636982 A, 13.01.87 | |||

| Динамическое полупроводниковое запоминающее устройство | 1987 |

|

SU1439680A1 |

Авторы

Даты

1999-03-27—Публикация

1995-03-02—Подача