Изобретение относится к измерительной технике и приборостроению и предназначено для измерения частоты импульсных сигналов.

Известно устройство для измерения частоты, содержащее импульсный датчик, два счетчика, коммутатор, регистр памяти, генератор импульсов, дешифратор, элемент И и элемент ИЛИ, измеряющее частоту только на интервалах времени, кратных 2K, посредством сдвига кода расстояния K раз (см. авт. св. СССР N 1053007, кл. G 01 P 3/489, 1983).

Недостатками устройства являются значительная приборная погрешность, обусловленная большой дискретностью измерения, и невозможность измерения на произвольных интервалах времени.

Известен также цифровой измеритель частоты, содержащий генератор импульсов времени, управляемый делитель частоты, первый двоичный счетчик, программируемую память и регистр памяти, причем установочный выход управляемого делителя частоты соединен с сбросовым входом первого двоичного счетчика и входом записи информации регистра памяти и является входом устройства, выход генератора импульсов времени через делитель частоты включен на суммирующий вход первого двоичного счетчика, выходными разрядами, кроме старшего, соединенного с адресными разрядами памяти, а выходом переполнения - с управляющим входом делителя частоты (см. авт. св. СССР N 1278717, кл. G 01 P 3/489, 1986).

Недостатком цифрового измерителя частоты является увеличение разрядности элементов схемы, прежде всего, коммутатора и регистра результата, при расширении диапазона и увеличении точности измерения, обусловленное заложенным в принцип действия измерителя кодирования чисел в форме с фиксированной запятой. Это усложняет или делает невозможным сопряжение измерителя с компьютерной техникой, имеющей определенную разрядность, и увеличивает объем коммутатора настолько, что он становится практически нереализуемым.

Задачей, на решение которой направлено предлагаемое изобретение, является поддержание пространства разрядной сетки измерителя при расширении диапазона измерения и при увеличении точности измерения.

Технический результат, достигаемый при решении поставленной задачи, выражается в измерителе кодирования чисел в форме с плавающей запятой, что сохраняет постоянной разрядную сетку измерителя в неограниченном диапазоне измерения.

Поставленная задача решается тем, что цифровой измеритель частоты, содержащий генератор импульсов времени, управляемый делитель частоты, первый двоичный счетчик, программируемую память и регистр памяти, причем установочный вход управляемого делителя частоты соединен с сбросовым входом первого двоичного счетчика и входом записи информации регистра памяти и является входом устройства, выход генератора импульсов времени через делитель включен на суммирующий вход первого двоичного счетчика, входными разрядами, кроме старшего, соединенного с адресными разрядами памяти, а выходом переполнения - с управляющим входом делителя частоты, отличается тем, что в него введены второй двоичный счетчик, переключатель и триггер, причем вход устройства соединен с входами разрядов второго счетчика и сбросовым входом триггера, выходы разрядов памяти включены на входы разрядов регистра, выход переполнения первого счетчика связан с информационным входом переключателя, управляющий вход которого соединен с выходом триггера, а первый и второй выходы - с вычитающим и суммирующим соответственно выходами второго счетчика, выход обнуления которого включен на установочный вход триггера, а выходы разрядов второго двоичного счетчика и выход триггера заведены на входы разрядов регистра.

При этом введение в отличительную часть формулы изобретения дополнительных элементов с соответствующими связями позволяет решить следующие функциональные задачи.

Введение второго двоичного счетчика позволяет формировать модуль порядка кода измеряемой частоты и определять знак порядка. Переключатель обеспечивает правильное функционирование второго счетчика при смене знака порядка.

Введение же триггера дает возможность фиксировать знак порядка.

Сопоставительный анализ признаков заявляемого решения и признаков аналога и прототипа свидетельствует о его соответствии критерию "новизна".

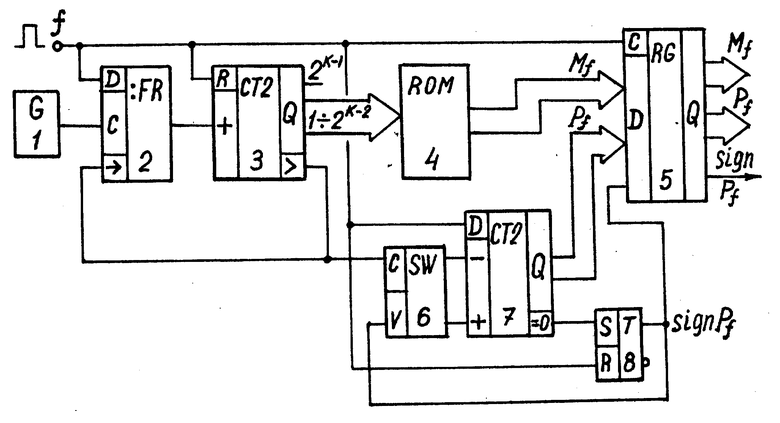

На чертеже приведена функциональная схема цифрового измерителя частоты.

Цифровой измеритель частоты содержит генератор импульсов времени 1 эталонной частоты, управляемый делитель частоты 2, первый двоичный счетчик 3, программируемую память 4, регистр памяти 5, переключатель 6, второй двоичный счетчик 7 и триггер 8.

Каждый импульс с выхода ">" переполнения счетчика 3 увеличивает вдвое коэффициент деления делителя частоты 2 и посредством переключателя 6 уменьшает на единицу порядок кода измеряемой частоты.

Частота импульсов f находится как величина обратная отрезку времени t, измеренному между соседними импульсами на входе устройства

f = C/t, (1)

где

C - коэффициент пропорциональности.

Время t определяется числом импульсов генератора 1, записанным в счетчик 3.

Согласно принципу действия измерителя времени t разделено на интервалы по закону двоичного ряда

2k+i-2≤t<2k+i-1, i=1,2,3,..., (2)

т.е. каждый очередной интервал длинней предыдущего в два раза и значения f на первом интервале (i=1) (область высоких частот), когда

C/2k-1≤f<C/2k, (3)

записываются в память 4 (величина K определяется требуемой точностью измерения и объемом памяти 4).

Значения же f на всех последующих интервалах

C/2k+i-2≤f<C/2k+i-1, i=2,3,4,... (4)

определяются через записанные в память значения уменьшением их в 2i-1 раз.

В измерителе искомый код частоты Nf вырабатывается в форме с плавающей запятой

где

Mf - мантисса кода;

Pf - модуль порядка кода;

SignPf - знак порядка кода (+ или -).

Согласно схеме измерителя мантисса Mf извлекается на памяти 4, модуль полрядка Pf формируется в счетчике 7, знак порядка SignPf определяется состоянием триггера 8 и все они - Mf, Pf, SignPf - записываются в регистр 5.

Цифровой измеритель частоты работает следующим образом.

Предварительно в память 4 записываются 2k-1 значений Mf для самых больших f (формула 3), соответствующих первому временному интервалу. В счетчике 3 соответственно K разрядов.

При появлении импульса на входе устройства начинается очередной интервал измерения. Этим импульсом схема приводится в исходное состояние: в регистр 5 заносятся измеренные на предыдущем интервале значения Mf, Pf, SignPf, обнуляется счетчик 3, устанавливается единичный коэффициент деления делителя 2, в счетчике 7 устанавливается значение Pf первого интервала и триггер 8 обнуляется. Нулевой сигнал на выходе триггера означает положительный знак порядка (в области наивысших частот - наибольший порядок, следовательно, наибольшее значение Pf и SignPf положителен). Подаваемый с выхода триггера 8 на управляющий вход V переключателя 6 нулевой сигнал устанавливает переключатель 6 в положение, при котором информационный вход C коммутируется со входом "-" счетчика 7. Каждый импульс генератора 1 проходит через делитель 2 на суммирующий вход счетчика 3. Код времени t в счетчике 3, за исключением старшего разряда, является адресом той ячейки памяти 4, в которой записана мантисса Mf соответствующего значения f=C/t. Действительно, согласно (3), f= C/2k-1 является первым измеряемым значением, а поэтому соответствующее значение Mf записано в первую ячейку памяти 4 с нулевым адресом, т.е. разряд 2k-1 не должен входить в адресный код (все остальные разряды обнулены). Поэтому после каждого импульса генератора 1 на выходах памяти 4 будет код соответствующего значения Mf.

Если очередной входной импульс, фиксирующий конец текущего и начало следующего интервалов измерения частоты, появляется при t<2k, то он заносит коды Mf, Pf и SignPf с выходов памяти 4, счетчика 7 и триггера 8 в регистр 5, обнуляет счетчик 3 и триггер 8 и подтверждает исходное состояние делителя 2.

При t≥2k работа схемы отличается от вышеописанного. В моменты времени t= 2k+i-2 (i= 2,3,4, ...) изменяется состояние счетчика 3, делителя частоты 2, переключателя 6, счетчика 7 и, возможно (при смене знака порядка), и триггера 8. В эти моменты времени на выходе ">" переполнения счетчика 3 появляется импульс, который вдвое (относительно предыдущего значения) увеличивает коэффициент деления делителя 2 и проходит через переключатель 6 на вычитающий вход счетчика 7, уменьшая на единицу код Pf.

Так, при t=2k первый импульс переполнения счетчика 3 задает коэффициент деления делится 2 равным двум и уменьшает на единицу Pf (действительно, модуль порядка кода частоты Nf второго интервала C/2k≤f<C/2k+1 на единицу меньше модуля порядка кода частоты Nf первого интервала C/2k-1≤f<C/2k). Если бы при t=2k появился очередной входной импульс, то т.к. все разряды счетчика 3 обнулены, из нулевой ячейки памяти 4 было извлечено и занесено в регистр 5 то же значение Mf, что и при t=2k-1, но из счетчика 7 в регистр 5 был бы занесен на единицу меньший код Pf.

Импульс t=2k+1 с генератора на счетчик 3 не проходит, т.к. теперь делитель 2 пропускает каждый второй импульс. Поэтому, если бы очередной входной импульс появился бы при t=2k+1, из памяти 4 в регистр 5 переписалось бы не истинное значение Mf, а предыдущее, т.е. значение Mf при t=2k+1 аппроксимировалось бы значением Mf, соответствующим t=2k. Следовательно, на интервале 2k≤t<2k+1 каждым двум соседним значениям измеренного времени ставится в соответствие одно значение Mf, т.е. половина значений Mf определяется точно, а половина аппроксимируется.

При t= 2k+1 вторым импульсом переполнения счетчика 3 устанавливается коэффициент деления делителя 2, равный 4, и еще на единицу уменьшается Pf. Т.е. на интервале 2k+1≤t<2k+2 каждым четырем соседним значениям t становится в соответствие одно значение Mf. И на каждом очередном интервале 2k+i-2≤t<2k+i-1 соблюдается вышеописанная закономерность работы схемы измерителя: в начале интервала (t=2k+i-2) импульсом переполнения счетчика 3 удваивается коэффициент деления делителя 2 и на единицу уменьшается код Pf. Из 2i знаний Mf (2i-1) значение аппроксимируется.

Но в процессе измерения при уменьшении f (уменьшении Pf) возможно уменьшение Pf до нуля и дальнейшее падение порядка (рост Pf с противоположным знаком). В этом случае формирующая Pf и SignPf часть схемы измерителя работает иначе.

При обнулении счетчика 7 сигналом с его выхода обнуления "=0" опрокидывается триггер 8, что говорит о смене знака порядка (SignPf=1 означает отрицательный знак порядка), и новое значение сигнала на выходе V переключателя 6 коммутирует его вход C с суммирующим входом счетчика 7. Теперь импульсы, приходящие с выхода переполнения счетчика 3, будут, наоборот, увеличивать код модуля Pf в счетчике 7, но знак порядка теперь отрицателен (SignPf<0), что по-прежнему будет означать уменьшение порядка кода f (рост со знаком "-").

Максимально возможная погрешность предлагаемого цифрового измерителя частоты, обусловленная аппроксимацией части значений Mf, оценивается на каждом временном интервале 2k+i-2≤t<2k+i-1 относительной максимальной ошибкой δmi(δmi равна отношению максимальной ошибки измерения на данном интервале к соответствующему точному значению)

Согласно (6) ошибка конечна, зависит от объема памяти и максимальна при i→ ∞ :δm∞ = 1/2k-1.и

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1995 |

|

RU2121753C1 |

| МАГНИТОСТРИКЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2109399C1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| АКУСТИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2099864C1 |

| Цифровой измеритель скорости | 1984 |

|

SU1278717A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПЛОТНОСТИ РАСПРЕДЕЛЕНИЯ ВЕРОЯТНОСТЕЙ СЛУЧАЙНОГО ПРОЦЕССА | 2000 |

|

RU2174706C1 |

| МАГНИТОСТРИКЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2090839C1 |

| АКУСТИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2090840C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДВУМЕРНЫХ РАСПРЕДЕЛЕНИЙ СЛУЧАЙНЫХ ПРОЦЕССОВ | 2003 |

|

RU2253892C1 |

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2000 |

|

RU2182358C2 |

Изобретение относится к измерительной технике и приборостроению и прдназначено для измерения частоты импульсных сигналов. Технический результат выражается в применение в измерителе кодирования чисел в форме с плавающей запятой, что сохраняет постоянной разрядную сетку измерителя практически в неограниченном диапазоне измерения. Сущность: введение дополнительного двоичного счетчика позволяет формировать модуль порядка кода измеряемой частоты и определять знак порядка. Переключатель обеспечивает правильное функционирование этого счетчика при смене знака порядка. Введение же триггера дает возможность фиксировать знак порядка. 1 ил.

Цифровой измеритель частоты, содержащий генератор импульсов эталонной частоты, управляемый делитель частоты, первый двоичный счетчик, программируемую память и регистр памяти, причем установочный вход управляемого делителя частоты соединен со сбросовым входом первого двоичного счетчика и входом записи информации регистра памяти и является входом устройства, выход генератора импульсов эталонной частоты через управляемый делитель частоты включен на суммирующий вход первого двоичного счетчика, выходными разрядами, кроме старшего, соединенного с адресными разрядами программируемой памяти, а выходом переполнения - с управляющим входом управляемого делителя частоты, отличающийся тем, что в него введены второй двоичный счетчик, переключатель и триггер, причем вход устройства соединен с входами разрядов второго двоичного счетчика и сбросовым входом триггера, выходы разрядов программируемой памяти включены на входы разрядов регистра памяти, выход переполнения первого двоичного счетчика связан с информационным входом переключателя, управляющий вход которого соединен с выходом триггера, а первый и второй выходы - с вычитающим и суммирующим соответственно входами второго двоичного счетчика, выход обнуления которого включен на установочный вход триггера, а выходы разрядов второго двоичного счетчика и выход триггера заведены на входы разрядов регистра памяти.

| SU, авторское свидетельство, 1053007, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| SU, авторское свидетельство, 1278717, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1998-09-10—Публикация

1995-11-14—Подача