Изобретение относится к измерительной технике и может использоваться в измерительных системах, предназначенных для анализа распределения случайных процессов.

Известно устройство для определения одномерной функции плотности распределения вероятностей случайных сигналов, содержащее генератор пилообразного напряжения, первый выход которого соединен с входом схемы синхронизации, второй выход соединен со входом сумматора, а вход соединен с первым выходом генератора тактовых импульсов, второй выход которого подключен к первому входу регистра сдвига, второй вход которого соединен с выходом схемы выборки, разрядные выходы регистра сдвига подключены к первым входам соответствующих ключей, вторые входы которых соединены с первым входом схемы синхронизации, выходы интеграторов через коммутатор соединены с регистром, кроме того, схема синхронизации содержит генератор синхроимпульсов, вход которого подключен ко входу схемы синхронизации, а выход через генератор меандра и генератор разнополярных импульсов подключен к выходу схемы синхронизации (А. с. СССР N 411458, МКИ G 06 F 15/36, БИ N 2, 1974).

Недостатком данного устройства является низкая точность определения плотности распределения вероятностей. В частности, это обусловлено тем, что для получения достаточной информации о плотности распределения вероятностей необходимо согласовывать период следования вспомогательного пилообразного сигнала с интервалом корреляции исследуемого сигнала, то есть для обеспечения заданной точности измерения длительность линейной части вспомогательного пилообразного сигнала должна быть не меньше интервала корреляции исследуемого сигнала.

Наиболее близким по технической сущности к предлагаемому изобретению является устройство для определения плотности распределения случайного сигнала, содержащее две пары амплитудных дискриминаторов, выходы каждой пары которых подключены соответственно ко входам двух элементов антисовпадения, выход первого элемента антисовпадения соединен с суммирующим входом блока цифрового отсчета, а выход второго элемента антисовпадения соединен с вычитающим входом блока цифрового отсчета, источник тока соединен с одним выводом блока задания ширины дифференциального коридора, выполненным в виде резистора, этот же вывод резистора подключен ко второму входу перового амплитудного дискриминатора и к первому входу первого сумматора, второй вывод резистора соединен со вторым входом второго амплитудного дискриминатора, с первым входом второго сумматора и с выходом цифроаналогового преобразователя, выход генератора вспомогательного сигнала подключен ко вторым входам первого и второго сумматоров, выход генератора тактовых импульсов соединен со входами стробирования всех четырех амплитудных дискриминаторов и со входом счетчика, выход которого подключен ко входу цифроаналогового преобразователя и к управляющему входу блока цифрового отсчета (А.с. СССР N 506867, МКИ G 06 F 15/36, БИ N 10, 1976).

Недостатком данного устройства является сложность его технической реализации. Оно содержит два измерительных канала - основной и дополнительный, в которых используется четыре амплитудных дискриминатора. Дополнительный канал служит для компенсации систематической погрешности, вызванной смещенностью оценок плотности распределения вероятностей случайного процесса. В соответствии с этим для получения результатов измерения с требуемой точностью необходимо обеспечивать согласование метрологических характеристик этих измерительных каналов. Кроме того, в процессе измерения не учитывается влияние на точность измерения реализации вспомогательного случайного сигнала.

Целью предлагаемого изобретения является повышение точности получения оценок плотности распределения вероятностей случайного процесса и упрощение устройства.

Цель достигается тем, что в устройство для определения плотности распределения случайного сигнала, содержащее генератор тактовых импульсов, двоичный счетчик, цифроаналоговый преобразователь, генератор вспомогательного случайного равномерно распределенного сигнала, выход которого соединен с вторым входом аналогового сумматора, выход которого соединен с первым входом первого компаратора, выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к выходу второго компаратора, реверсивный счетчик, выход которого соединен с входом данных блока памяти, введены двоичный регистр, цифровой сумматор, элемент ИЛИ и блок управления, причем первый вход аналогового сумматора является входом устройства, выход генератора вспомогательного случайного равномерно распределенного сигнала соединен с первым входом второго компаратора, второй вход которого подключен к шине нулевого потенциала, информационный вход двоичного регистра является входом задания начального уровня анализа, а выход соединен с первым входом цифрового сумматора, второй вход которого подключен к информационному выходу двоичного счетчика, выход цифрового сумматора соединен с входом цифро- аналогового преобразователя, выход которого соединен с вторым входом первого компаратора, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом управления направлением счета реверсивного счетчика, тактовый вход двоичного регистра, вход обнуления двоичного счетчика, первый вход элемента ИЛИ и вход запуска блока управления объединены и подключены к входу "Пуск" устройства, выход признака переполнения двоичного счетчика соединен с входом сброса блока управления, выход генератора тактовых импульсов соединен с входом синхронизации блока управления, вход начальной установки которого является входом задания интервала времени анализа, а выход управления изменением уровня анализа соединен со счетным входом двоичного счетчика и с вторым входом элемента ИЛИ, выход которого соединен с входом обнуления реверсивного счетчика, счетный вход которого подключен к выходу выдачи последовательности счетных импульсов блока управления, выход управления записью которого соединен с входом разрешения записи блока памяти, адресный вход которого подключен к информационному выходу двоичного счетчика.

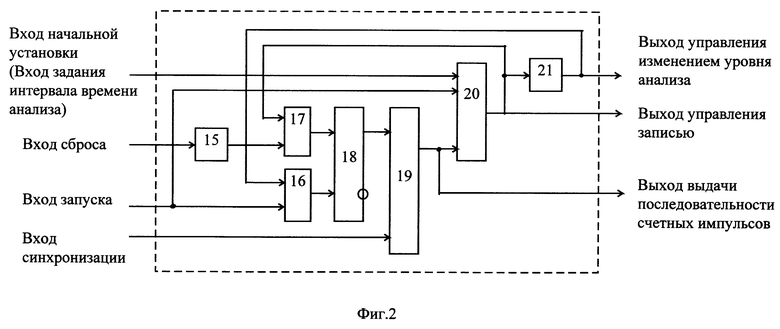

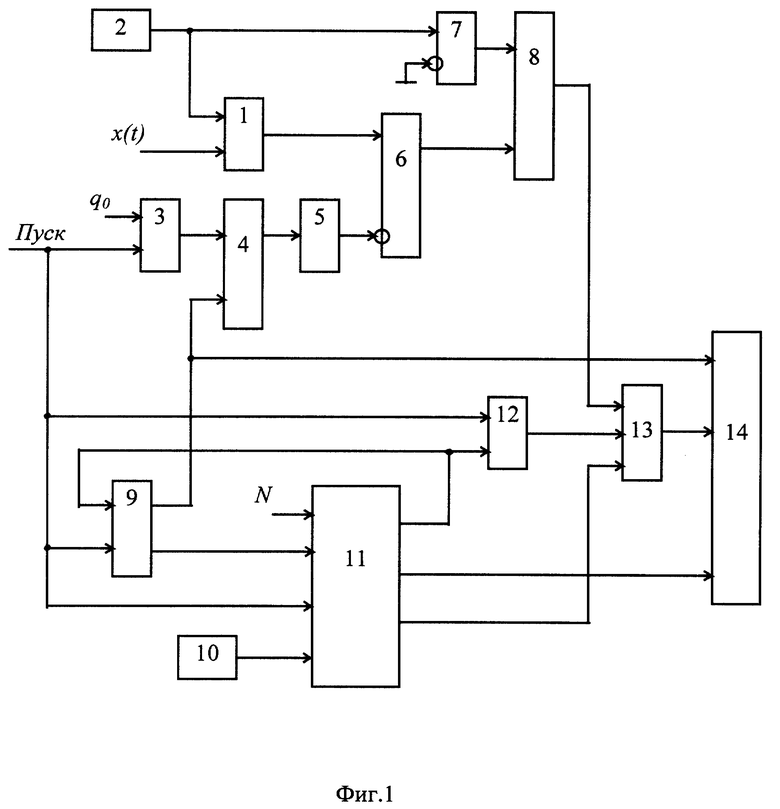

На фиг. 1 представлена структурная схема устройства для определения плотности распределения вероятностей случайного процесса; на фиг. 2 - структурная схема блока управления в одном из возможных вариантов его исполнения.

Устройство содержит аналоговый сумматор 1, генератор 2 вспомогательного случайного равномерно распределенного сигнала, двоичный регистр 3, цифровой сумматор 4, цифроаналоговый преобразователь 5, первый 6 и второй 7 компараторы, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8, двоичный счетчик 9, генератор 10 тактовых импульсов, блок управления 11, элемент ИЛИ 12, реверсивный счетчик 13, блок памяти 14.

Блок управления содержит формирователь импульсов 15, первый 16 и второй 17 элементы ИЛИ, RS-триггер 18, элемент И 19, делитель 20 с перестраиваемым коэффициентом деления и элемент задержки 21.

Первый вход аналогового сумматора 1 является входом устройства, а выход соединен с первым входом первого 6 компаратора, выход генератора 2 вспомогательного случайного равномерно распределенного сигнала соединен с вторым входом аналогового сумматора 1 и с первым входом второго 7 компаратора, второй вход которого подключен к шине нулевого потенциала, а выход соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8. Тактовый вход двоичного регистра 3, вход обнуления двоичного счетчика 9, вход запуска блока управления 11 и первый вход элемента ИЛИ 12 объединены и подключены к входу "Пуск" устройства. Информационный вход двоичного регистра 3 является входом задания начального уровня анализа, а выход соединен с первым входом цифрового сумматора 4, второй вход которого подключен к информационному выходу двоичного счетчика 9, выход цифрового сумматора 4 соединен с входом цифроаналогового преобразователя 5, выход которого соединен с вторым входом первого компаратора 6, выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8, выход которого соединен с входом управления направлением счета реверсивного счетчика 13, выход которого соединен с входом данных блока памяти 14. Выход признака переполнения двоичного счетчика 9 соединен с входом сброса блока управления 11, выход генератора 10 тактовых импульсов соединен с входом синхронизации блока управления 11, вход начальной установки которого является входом задания интервала времени анализа, а выход управления изменением уровня анализа соединен со счетным входом двоичного счетчика 9 и с вторым входом элемента ИЛИ 12, выход которого соединен с входом обнуления реверсивного счетчика 13, счетный вход которого подключен к выходу выдачи последовательности счетных импульсов блока управления 11, выход управления записью которого соединен с входом разрешения записи блока памяти 14, адресный вход которого подключен к информационному выходу двоичного счетчика 9.

В блоке управления первый вход первого 16 элемента ИЛИ и вход разрешения записи коэффициента деления делителя 20 с перестраиваемым коэффициентом деления объединены и являются входом запуска блока управления, вход формирователя импульсов 15 является входом сброса блока управления, а выход соединен с первым входом второго 17 элемента ИЛИ, выход которого соединен с R-входом RS-триггера 18, S-вход которого подключен к выходу первого 16 элемента ИЛИ, а прямой выход соединен с вторым входом элемента И 19, первый вход которого является входом синхронизации блока управления, а выход соединен со счетным входом делителя 20 с перестраиваемым коэффициентом деления и является выходом выдачи последовательности счетных импульсов блока управления, вход задания коэффициента деления делителя 20 с перестраиваемым коэффициентом деления является входом начальной установки блока управления, а выход соединен с вторым входом второго 17 элемента ИЛИ, с входом элемента задержки 21 и является выходом управления записью блока управления, выход элемента задержки 21 соединен с вторым входом первого 16 элемента ИЛИ и является выходом управления изменением уровня анализа блока управления.

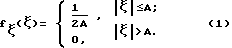

Работа устройства основана на знаковом методе измерения оценок  плотности распределения вероятностей случайного процесса X(t) с использованием вспомогательного сигнала ξ(t). Вспомогательный сигнал ξ (t) независим по отношению к исследуемому процессу X(t). Мгновенные значения сигнала ξ(t) распределены равномерно внутри интервала от -А до +А, то есть его плотность распределения вероятностей равна

плотности распределения вероятностей случайного процесса X(t) с использованием вспомогательного сигнала ξ(t). Вспомогательный сигнал ξ (t) независим по отношению к исследуемому процессу X(t). Мгновенные значения сигнала ξ(t) распределены равномерно внутри интервала от -А до +А, то есть его плотность распределения вероятностей равна

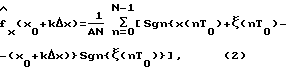

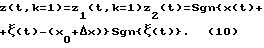

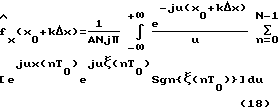

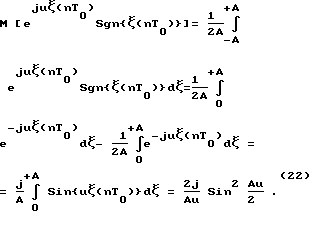

Алгоритм, непосредственно положенный в основу работы устройства, имеет следующий вид

где Sgn{ ...} - оператор знаковой функции; x(nT0) и ξ(nT0) - дискретное представление реализаций соответственно исследуемого процесса X(t) и вспомогательного сигнала ξ(t), x0 - начальный уровень анализа; Δx - интервал приращения уровня анализа; k - номер текущего уровня анализа (k=0, 1,2,3,... К), N - общее число выборок за интервал времени измерения оценки значения плотности распределения вероятностей на текущем k-ом уровне анализа; Т0 - период следования импульсов опроса (тактовых импульсов); А - параметр, определяющий границы интервала равномерного распределения мгновенных значений вспомогательного сигнала ξ(t) согласно выражению (1).

Устройство работает следующим образом.

Реализация x(t) исследуемого случайного процесса X(t) поступает на вход устройства, то есть на первый вход аналогового сумматора 1, на второй вход которого поступает сигнал ξ(t) с выхода генератора 2 вспомогательного случайного равномерно распределенного сигнала. Одновременно сигнал ξ(t) поступает на первый вход второго 7 компаратора, второй вход которого подключен к шине нулевого потенциала. В качестве вспомогательного сигнала ξ(t) допускается использование линейно изменяющегося периодического сигнала (см. Мирский Г.Я. Характеристики стохастической взаимосвязи и их измерения. - М.: Энергоиздат, 1982. - С. 190). В частности можно использовать сигнал треугольной формы (схему генератора сигнала треугольной формы см. в книге: Применение прецизионных аналоговых микросхем /А.Г.Алексенко, Е.А.Коломбет, Г.И. Стародуб. - М.: Радио и связь, 1985. - С. 165-166, рис. 4.11 - 4.13).

Начало работы устройства осуществляется по сигналу "Пуск", который представляет собой короткий импульс.

Сигнал "Пуск" поступает на тактовый вход двоичного регистра 3 и осуществляет запись в этот регистр с входа задания начального уровня анализа двоичное число q0, которое является цифровым эквивалентом значения начального уровня анализа x0.

Одновременно сигнал "Пуск" поступает на вход обнуления двоичного счетчика 9 и через элемент ИЛИ 12 на вход обнуления реверсивного счетчика 13 и обнуляет эти счетчики.

Сигнал "Пуск" также поступает на вход запуска блока управления 11. В этом блоке он поступает на вход разрешения записи коэффициента деления делителя 20 с перестраиваемым коэффициентом деления, что приводит к записи в этот делитель целочисленного значения N коэффициента деления с входа начальной установки блока управления 11, который является входом задания интервала времени анализа. При этом значение N коэффициента деления определяет общее число выборок за интервал времени измерения оценки значения плотности распределения вероятностей на текущем k-м уровне анализа согласно алгоритму (2). Параллельно сигнал "Пуск" в блоке управления 11 поступает через первый 16 элемент ИЛИ на S-вход RS-триггера 18, который в исходном состоянии находится в нулевом состоянии, то есть на его прямом выходе в исходном состоянии присутствует уровень логического нуля. Под действием сигнала "Пуск" RS-триггер 18 переходит в единичное состояние, то есть на его прямом выходе устанавливается уровень логической единицы, который поступает на второй вход элемента И 19 и разрешает прохождение на выход этого элемента тактовых импульсов с его первого входа, который является входом синхронизации блока управления 11 и подключен к выходу генератора 10 тактовых импульсов. Тактовые импульсы с выхода элемента И 19 поступают на счетный вход делителя 20 с перестраиваемым коэффициентом деления, а также проходят на выход выдачи последовательности счетных импульсов блока управления 11.

Число q0, записанное в регистр 3 по сигналу "Пуск" и соответствующее в двоичном коде значению начального уровня анализа x0, поступает на первый вход цифрового сумматора 4, второй вход которого подключен к информационному выходу двоичного счетчика 9, содержимое которого определяет номер k текущего уровня анализа. Как было показано выше, в начале цикла измерения двоичный счетчик 9 обнуляется и его содержимое равно нулю, то есть k=0. В соответствии с этим в начале цикла измерения на выходе цифрового сумматора 4 будет присутствовать число q0.

Результат суммирования с выхода цифрового сумматора 4, в данном случае это двоичное число q0, поступает на вход цифроаналогового преобразователя 5. Работа цифроаналогового преобразователя 5 осуществляется таким образом, что приращение его выходного напряжения, соответствующее изменению на единицу двоичного кода на его входе, равно интервалу приращения уровня анализа Δx. В соответствии с этим на выходе цифроаналогового преобразователя 5 получаем напряжение постоянного уровня, соответствующее начальному уровню анализа x0, то есть

x0= q0Δx . (3)

(Цифроаналоговые преобразователи и основные схемы их включения см. в книге: Применение прецизионных аналоговых микросхем /А.Г.Алексенко, Е.А. Коломбет, Г. И.Стародуб. - М.: Радио и связь, 1985. - С. 53-59, рис. 1.35-1.37).

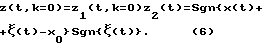

Сигнал постоянного напряжения, задающий начальный уровень анализа x0, с выхода цифроаналогового преобразователя 5 поступает на второй вход первого 6 компаратора, на первый вход которого поступает сигнал с выхода аналогового сумматора 1, являющийся суммой реализации x(t) исследуемого случайного процесса X(t) и вспомогательного сигнала ξ (t). В результате операции сравнения с учетом того, что номер текущего уровня анализа k=0, на выходе первого 6 компаратора образуется знаковый сигнал

z1(t,k=0)=Sgn{x(t)+ξ(t)-x0}. (4)

В тот же момент времени второй 7 компаратор осуществляет операцию сравнения вспомогательного сигнала ξ (t) с нулевым потенциалом. В результате на выходе второго 7 компаратора образуется знаковый сигнал

z2(t)=Sgn{ξ(t)}. (5)

При технической реализации устройства в качестве первого 6 и второго 7 компараторов можно использовать интегральные компараторы (см. Нефедов А.В. Интегральные микросхемы и их зарубежные аналоги: Справочник. Т.5. - М.: КУбК-а, 1997. - С. 113- 119). В этом случае уровни логической единицы на выходах первого 6 и второго 7 компараторов будут соответствовать значению "+1" знаковых сигналов z1(t,k=0) и z2(t), а уровни логического нуля на выходах этих компараторов будут соответствовать значению "-1" этих сигналов.

Сигналы с выходов первого 6 и второго 7 компараторов поступают соответственно на первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8, который выполняет функцию знакового умножения. С учетом того, что номер текущего уровня анализа k=0, на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 будет присутствовать знаковый сигнал

Если логические уровни выходных сигналов первого 6 и второго 7 компараторов совпадают, то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 будет присутствовать уровень логического нуля. Это означает, что результат произведения сигналов z1(t, k = 0) и z2(f) равен "+1". Если логические уровни выходных сигналов первого 6 и второго 7 компараторов являются противоположными, то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 будет присутствовать уровень логической единицы. Это означает, что результат произведения сигналов z1(t,k=0) и z2(t) равен "-1".

Сигнал с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 поступает на вход управления направлением счета реверсивного счетчика 13, на счетный вход которого поступают счетные импульсы с выхода выдачи последовательности счетных импульсов блока управления 11. При этом уровень логического нуля на входе управления направлением счета реверсивного счетчика 13 определят прямой счет этого счетчика (режим суммирования), а уровень логической единицы определяет обратный счет (режим вычитания). (В качестве реверсивного счетчика 13 можно использовать, например, реверсивный счетчик К555ИЕ13. См. Нефедов А.В. Интегральные микросхемы и их зарубежные аналоги: Справочник. Т.5. - М.: КУбК-а, 1997. - С. 168).

Процедура подсчета импульсов реверсивным счетчиком 13 под управлением сигнала с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 продолжается в течение времени поступления на его счетный вход последовательности из N счетных импульсов, которая задается блоком управления 11 и определяет время измерения оценки значения плотности распределения вероятностей исследуемого процесса X(t) на текущем уровне анализа.

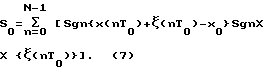

По истечению времени поступления последовательности из N счетных импульсов в реверсивном счетчике 13 будет накоплено число

Как следует из алгоритма (2), число S0 с точностью до постоянного множителя 1/AN является оценкой плотности распределения вероятностей случайного процесса X(t) на начальном уровне анализа x0.

Рассмотрим подробнее процедуру формирования последовательности из N счетных импульсов с помощью блока управления 11.

Как было показано выше, установление уровня логической единицы на прямом выходе RS-триггера 18 приводит к тому, что тактовые импульсы с первого входа элемента И 19 проходят на его выход и поступают на счетный вход делителя 20 с перестраиваемым коэффициентом и на выход выдачи последовательности счетных импульсов блока управления 11. После поступления N импульсов на счетный вход делителя 20 с перестраиваемым коэффициентом деления, этот делитель выдает на своем выходе импульс. (В качестве делителя 20 с перестраиваемым коэффициентом деления можно использовать, например, интегральную микросхему программируемого таймера К580ВИ53 или его аналоги. Режим работы 2 данного таймера обеспечивает период выходных импульсов таймера, равный N периодам входных импульсов, где N - начальное содержимое счетчика таймера. См. Алексенко А.Г. , Галицын А.А., Иванников А.Д. Проектирование радиоэлектронной аппаратуры на микропроцессорах: Программирование, типовые решения, методы отладки. - М.: Радио и связь, 1984. С. 65-72.).

Импульс с выхода делителя 20 с перестраиваемым коэффициентом деления через второй 17 элемент ИЛИ поступает на R-вход RS-триггера 18 и возвращает его в исходное нулевое состояние, то есть на прямом выходе RS-триггера устанавливается уровень логического нуля, который поступает на второй вход элемента И 19 и запрещает прохождение на выход этого элемента тактовых импульсов с его первого входа. Таким образом на выход выдачи последовательности счетных импульсов блока управления 11 проходит последовательность из N счетных импульсов.

Одновременно в блоке управления 11 импульс с выхода делителя 20 с перестраиваемым коэффициентом деления поступает на выход управления записью и с этого выхода далее поступает на вход разрешения записи блока памяти 14, в который записывается содержимое реверсивного счетчика 13 по адресу, поступающему с информационного выхода двоичного счетчика 9. Следует отметить, что содержимое двоичного счетчика 9 одновременно определяет номер k текущего уровня анализа и адрес, по которому осуществляется запись результата измерения на этом уровне. В данном случае номер текущего уровня анализа k=0, и, следовательно, адрес, по которому будет храниться текущий результат измерения, равен нулю. Таким образом, номер текущего уровня анализа и адрес ячейки, в которой хранится соответствующий результат измерения, совпадают, что обеспечивает взаимно однозначное соответствие между результатами измерений и организацией их хранения в блоке памяти 14. (Блок памяти 14 может быть построен, например, на основе микросхем серии К537. См. Полупроводниковые БИС запоминающих устройств: Справочник /В.В.Баранов, Н.В.Бекин, А.Ю.Гордонов и др. ; Под ред. А.Ю.Гордонова и Ю.Н.Дьякова. - М.: Радио и связь, 1987. - С. 196-209.)

Импульс с выхода делителя 20 с перестраиваемым коэффициентом деления в блоке управления 11 поступает также на вход элемента задержки 21. Элемент задержки 21 используется для согласования операции записи результата текущего измерения с последующим изменением номера уровня анализа и адреса записи для следующего результата измерения. В соответствии с этим время задержки импульса с выхода делителя 20 с перестраиваемым коэффициентом деления выбирается из условия организации режима записи, при котором обеспечивается правильное функционирование блока памяти 14. (Элемент задержки 21 может быть выполнен, например; на основе микросхем К555АГ3. См. Нефедов А.В. Интегральные микросхемы и их зарубежные аналоги: Справочник. Т.5. - М.: КУбК-а, 1997. - С. 125-126.)

Задержанный импульс с выхода элемента задержки 21 поступает на выход управления изменением уровня анализа блока управления 14 и с этого выхода поступает на счетный вход двоичного счетчика 9, в результате чего содержимое последнего увеличивается на единицу, что соответствует увеличению на единицу номера уровня текущего анализа и, следовательно, адреса по которому будет записан следующий результат измерения. (В качестве двоичного счетчика можно использовать, например, счетчик К555ИЕ10. См. Нефедов А.В. Интегральные микросхемы и их зарубежные аналоги: Справочник. Т.5. - М.: КУбК-а, 1997. - С. 166. ) Этот же импульс через элемент ИЛИ 12 поступает на вход обнуления реверсивного счетчика 13 и обнуляет его. В результате обнуления реверсивный счетчик 13 готов к следующему циклу измерения на следующем уровне анализа.

В блоке управления 11 импульс с выхода элемента задержки 21 через первый 16 элемент ИЛИ поступает на S-вход RS-триггера 18 и устанавливает его в единичное состояние. В итоге тактовые импульсы с первого входа элемента И 19 снова проходят на его выход и поступают на счетный вход делителя 20 с перестраиваемым коэффициентом и на выход выдачи счетных импульсов блока управления 11. Далее вся описанная выше процедура измерения оценки плотности распределения вероятностей повторяется с той лишь разницей, что номер текущего уровня анализа k=1. В соответствии с этим на выходе цифроаналогового преобразователя 5 получаем напряжение постоянного уровня, соответствующее первому уровню анализа x1, то есть

x1=(q0+1)Δx = q0Δx+Δx=x0+Δx. (8)

Тогда на выходе первого 6 компаратора образуется знаковый сигнал

z1(t,k=1)=Sgn{x(t)+ξ(t)-(x0+Δx)}.(9)

В свою очередь на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 будет присутствовать знаковый сигнал

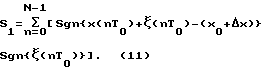

Сигнал z(t, k=1) поступает на вход управления направлением счета реверсивного счетчика 13, на счетный вход которого поступает последовательности из N счетных импульсов с выхода выдачи последовательности счетных импульсов блока управления 11. По истечению времени поступления последовательности из N счетных импульсов в реверсивном счетчике 13 будет накоплено число

Число S1 записывается в блок памяти 14 по адресу, поступающему с информационного выхода двоичного счетчика 9 и равному единице.

Из (2) нетрудно видеть, что число S1 с точностью до постоянного множителя 1/AN является оценкой плотности распределения вероятностей случайного процесса X(t) на первом уровне анализа x1=x0+ Δx.

Затем, как и в предыдущем случае, происходит увеличение на единицу содержимого двоичного счетчика 9, что соответствует увеличению на единицу номера уровня текущего уровня анализа и, следовательно, адреса, по которому будет записан следующий результат измерения, а также происходит обнуление реверсивного счетчика 13.

Далее вся процедура получения очередной оценки плотности распределения вероятностей случайного процесса X(t) согласно алгоритму (2) повторяется заново.

В общем случае для k-го уровня анализа, когда содержимое двоичного счетчика 9 будет равно k, на выходе цифроаналогового преобразователя 5 получаем напряжение постоянного уровня, соответствующее k-му уровню анализа xk то есть

xk=(q0+k)Δx=q0Δx+kΔx=x0+kΔx. (12)

Тогда на выходе первого 6 компаратора образуется знаковый сигнал

z1(t,k)=Sgn{x(t)+ξ(t)-(x0+kΔx)}.(13)

В свою очередь на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 будет присутствовать знаковый сигнал

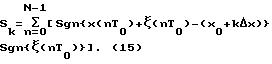

По истечению времени поступления последовательности из N счетных импульсов в реверсивном счетчике 13 будет накоплено число

Число Sk записывается в блок памяти 14 по адресу, поступающему с информационного выхода двоичного счетчика 9 и равному k.

Число Sk с точностью до постоянного множителя 1/AN является оценкой плотности распределения вероятностей случайного процесса X(t) на k-му уровне анализа xk = x0 + kΔx.

Постоянный коэффициент 1/AN может быть учтен путем простого масштабирования, что не представляет особого труда.

Процесс измерения оценок плотности распрделения вероятностей случайного процесса X(t) продолжается до тех пор, пока текущий уровень анализа не достигнет своего верхнего предела. Практически это означает, что в двоичном счетчике 9 будет накоплено максимальное число К. В этом случае будет получена последняя оценка плотности распределения вероятностей, соответствующая верхнему уровню анализа x = x + KΔx. После этого при поступлении импульса с выхода управления изменением уровня анализа блока управления 11 на счетный вход двоичного счетчика 9 на выходе признака переполнения последнего появляется сигнал переполнения, который поступает на вход сброса блока управления 11. В блоке управления 11 сигнал переполнения поступает на вход формирователя импульсов 15, который по этому сигналу выдает на своем выходе короткий импульс (формирователи импульсов см. в книге Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. - Л.: Энергоатомиздат. Ленингр. отд-ние, 1986. - С. 263-273, рис. 14-1 - 14-11). Этот импульс через второй 17 элемент ИЛИ поступает на R-вход RS-триггера 18 и устанавливает его в исходное нулевое состояние. В результате этого тактовые импульсы не проходят на счетный вход делителя 20 с перестраиваемым коэффициентом деления, и работа блока управления 11 прекращается. К этому моменту времени в блоке памяти 14 будут записаны все полученные результаты измерения оценок плотности распределения вероятностей случайного процесса X(t).

Проанализируем качество оценки (2).

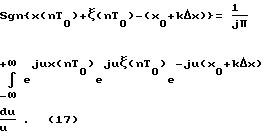

Справедливо следующее соотношение (см. Бронштейн И.Н., Семендяев К.А. Справочник по математике для инженеров и учащихся вузов. - М.: Наука, 1981. - С. 123, интеграл 13)

С учетом этого можно записать

Тогда соотношение (2) примет вид

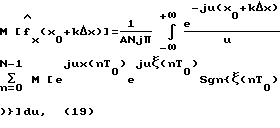

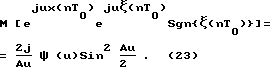

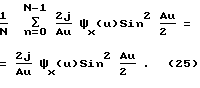

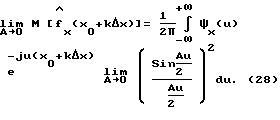

Найдем математическое ожидание оценки (18)

где M[...]- оператор математического ожидания.

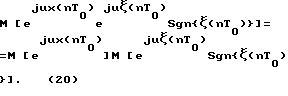

Так как вспомогательный сигнал ξ (t) независим по отношению к исследуемому процессу X(t), то можно записать, что

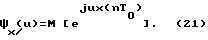

Первая часть выражения (20) представляет собой характеристическую функцию исследуемого случайного процесса X(t), то есть

Принимая во внимание выражение (1), вторая часть выражения (20) будет равна

Подставляя выражения (21) и (22) в (20), получаем

Тогда из (19) получаем

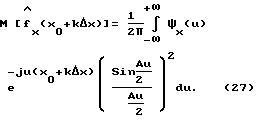

Из (24) нетрудно видеть, что

С учетом этого будем иметь

или

Из (27) следует, что

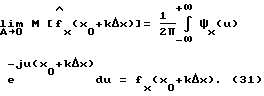

Принимая во внимание справедливость соотношения

получаем

Известно, что плотность распределения вероятностей и характеристическая функция связаны между собой прямым и обратным преобразованиями Фурье (см. Бендат Дж. , Пирсол А. Прикладной анализ случайных данных. - М.: Мир, 1989. -С. 67. - соотношения (3.18) и (3.19)). В соответствии с этим окончательно получаем

Это означает, что алгоритм (2) позволяет получать оценки  непосредственно плотности распределения вероятностей fx(х) случайного процесса X(t) при заданных уровнях анализа (x0+k Δx). При этом соответствующим выбором величины А погрешность от смещенности оценки

непосредственно плотности распределения вероятностей fx(х) случайного процесса X(t) при заданных уровнях анализа (x0+k Δx). При этом соответствующим выбором величины А погрешность от смещенности оценки  может быть уменьшена и сведена к требуемому уровню.

может быть уменьшена и сведена к требуемому уровню.

Из приведенного описания видно, что по сравнению с устройством-прототипом предлагаемое устройство технически проще. Оно содержит один измерительный канал, и в нем используется только два компаратора, а устройство-прототип имеет два измерительных канала, в которых используется четыре амплитудных дискриминатора. При получении оценок  плотности распределения вероятностей исследуемого случайного процесса X(t) в предлагаемом устройстве учитывается информация о вспомогательном сигнале ξ (t). Соответствующим выбором величины А можно уменьшить погрешность от смещенности. Все это позволяет увеличить точность измерения плотности распределения вероятностей fx(х) случайного процесса X(t).

плотности распределения вероятностей исследуемого случайного процесса X(t) в предлагаемом устройстве учитывается информация о вспомогательном сигнале ξ (t). Соответствующим выбором величины А можно уменьшить погрешность от смещенности. Все это позволяет увеличить точность измерения плотности распределения вероятностей fx(х) случайного процесса X(t).

Технически предлагаемое устройство реализуется на стандартных элементах, широко известных и применяемых в современной технике. Более того при современном уровне развитии технологии производства интегральных микросхем в перспективе подобное устройство или отдельные его блоки целесообразно реализовать в виде интегральных схем.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 1999 |

|

RU2177637C2 |

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 1999 |

|

RU2174705C2 |

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2000 |

|

RU2182358C2 |

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2000 |

|

RU2182724C2 |

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 2002 |

|

RU2252450C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОЭФФИЦИЕНТА ВЗАИМНОЙ КОРРЕЛЯЦИИ СЛУЧАЙНЫХ СИГНАЛОВ | 2000 |

|

RU2181501C2 |

| ЦИФРОВОЙ КОРРЕЛЯТОР | 1991 |

|

RU2051413C1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ДВИЖЕНИЯ ПРОВОДОВ И КАБЕЛЕЙ | 1999 |

|

RU2170436C2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДВУМЕРНЫХ РАСПРЕДЕЛЕНИЙ СЛУЧАЙНЫХ ПРОЦЕССОВ | 2003 |

|

RU2253892C1 |

| УСТРОЙСТВО ИНДУКЦИОННОГО НАГРЕВА ПЛОСКИХ МЕТАЛЛИЧЕСКИХ ИЗДЕЛИЙ | 1992 |

|

RU2076466C1 |

Изобретение относится к измерительной технике и может быть использовано для анализа случайных процессов. Техническим результатом является повышение точности оценок случайного процесса. Устройство содержит генератор тактовых импульсов, двоичный счетчик, цифроаналоговый преобразователь, генератор вспомогательного случайного равномерно распределенного сигнала, компараторы, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, реверсивный счетчик, блок памяти, двоичный регистр, цифровой сумматор, элемент ИЛИ и блок управления. 2 ил.

Устройство для определения плотности распределения вероятностей случайного процесса, содержащее генератор тактовых импульсов, двоичный счетчик, цифроаналоговый преобразователь, генератор вспомогательного случайного равномерно распределенного сигнала, выход которого соединен с вторым входом аналогового сумматора, выход которого соединен с первым входом первого компаратора, выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к выходу второго компаратора, реверсивный счетчик, выход которого соединен с входом данных блока памяти, отличающееся тем, что в него введены двоичный регистр, цифровой сумматор, элемент ИЛИ и блок управления, причем первый вход аналогового сумматора является входом устройства, выход генератора вспомогательного случайного равномерно распределенного сигнала соединен с первым входом второго компаратора, второй вход которого подключен к шине нулевого потенциала, информационный вход двоичного регистра является входом здания начального уровня анализа, а выход соединен с первым входом цифрового сумматора, второй вход которого подключен к информационному выходу двоичного счетчика, выход цифрового сумматора соединен с входом цифроаналогового преобразователя, выход которого соединен с вторым входом первого компаратора, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом управления направлением счета реверсивного счетчика, тактовый вход двоичного регистра, вход обнуления двоичного счетчика, первый вход элемента ИЛИ и вход запуска блока управления объединены и подключены к входу "Пуск" устройства, выход признака переполнения двоичного счетчика соединен с входом сброса блока управления, выход генератора тактовых импульсов соединен с входом синхронизации блока управления, вход начальной установки которого является входом задания интервала времени анализа, а выход управления изменением уровня анализа соединен со счетным входом двоичного счетчика и с вторым входом элемента ИЛИ, выход которого соединен с входом обнуления реверсивного счетчика, счетный вход которого подключен к выходу выдачи последовательности счетных импульсов блока управления, выход управления записью которого соединен с входом разрешения записи блока памяти, адресный вход которого подключен к информационному выходу двоичного счетчика.

| Устройство для определения плотности распределения случайного сигнала | 1974 |

|

SU506867A1 |

| 1972 |

|

SU411458A1 | |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 1991 |

|

RU2015555C1 |

| Устройство для определения закона распределения | 1987 |

|

SU1520545A1 |

| Анализатор гистограммы отклонений напряжения | 1982 |

|

SU1104530A1 |

| US 4534041 A, 06.08.1985. | |||

Авторы

Даты

2001-10-10—Публикация

2000-02-01—Подача