Изобретение относится к автоматике и вычислительной технике и может быть использовано в радиотехнических и измерительных системах для определения коэффициентов Фурье при гармоническом анализе детерминированных и случайных сигналов в реальном масштабе времени.

Известно устройство для выполнения преобразования Фурье, содержащее блок задания входной информации, генератор тактовых импульсов, генератор псевдослучайных чисел, блок формирования стробимпульсов, блок памяти, две группы, каждая из которых содержит по М шифраторов и по М сумматоров-вычитателей, регистр промежуточных коэффициентов и вычислительный блок, причем информационный вход блока задания входной информации является информационным входом устройства, выход генератора тактовых импульсов подключен к входу генератора псевдослучайных чисел, выход которого подключен к адресному входу блока памяти и к входу блока формирования стробимпульсов, выход которого подключен к управляющему входу блока задания входной информации, выход знакового разряда которого подключен к первым входам всех шифраторов, вторые входы которых подключены к соответствующим выходам блока памяти, выходы шифраторов первой и второй групп подключены к управляющим входам соответствующих сумматоров-вычитателей первой и второй групп соответственно, информационные входы всех сумматоров-вычитателей подключены к информационному выходу блока задания входной информации, выходы сумматоров-вычитателей первой и второй групп подключены к входам соответственно первого и второго регистров промежуточных коэффициентов, выходы которых подключены к входам соответственно первого и второго вычислительных блоков, входы и выходы которых являются выходами устройства (авт. св. СССР 928363, МКИ G 06 F 15/332, Бюл. 18, 1982).

Недостатком данного устройства является низкая точность вычисления оценок коэффициентов Фурье. Это обусловлено необходимостью предварительного вычисления промежуточных значений коэффициентов Фурье с последующим их пересчетом в тригонометрическом базисе, что в свою очередь ведет к усложнению технической реализации устройства.

Известно устройство для выполнения преобразования Фурье, содержащее аналого-цифровой преобразователь, генератор тактовых импульсов, генератор псевдослучайных чисел, счетчик, блок постоянной памяти, две группы блоков сравнения и две группы накапливающих сумматоров-вычитателей, причем информационный вход аналого-цифрового преобразователя является информационным входом устройства, выход генератора тактовых импульсов подключен к тактовому входу генератора псевдослучайных чисел, к счетному входу счетчика и к входу синхронизации аналого-цифрового преобразователя, выход аналого-цифрового преобразователя подключен к информационным входам накапливающих сумматоров-вычитателей первой и второй групп, выходы которых являются информационными выходами устройства соответственно первой и второй групп, информационный выход счетчика подключен к адресному входу блока постоянной памяти, информационные выходы первой и второй групп которого подключены к первым входам блоков сравнения соответственно первой и второй групп, выходы которых подключены к входам выбора режима работы накапливающих сумматоров-вычитателей соответственно первой и второй групп, выход генератора псевдослучайных чисел подключен к вторым входам блоков сравнения первой и второй групп (авт. св. СССР 1177822, МКИ G 06 F 15/332, Бюл. 33, 1985).

Недостатком данного устройства является низкая точность вычисления оценок коэффициентов Фурье, так как в процессе вычисления используются приближенные фильтрующие функции. Кроме того, устройство является технически сложным. Оно содержит две группы в общем случае многоразрядных цифровых блоков сравнения.

Наиболее близким по технической сущности к предлагаемому изобретению является устройство для выполнения преобразования Фурье, содержащее аналого-цифровой преобразователь, генератор тактовых импульсов, генератор псевдослучайных чисел, счетчик, блок постоянной памяти, две группы, включающие по М блоков сравнения и по (M+R) накапливающих сумматоров-вычитателей, элемент задержки, группу из R делителей частоты и группу из R блоков синхронизации, причем информационный вход аналого-цифрового преобразователя является информационным входом устройства, а выход соединен с информационными входами (M+R) накапливающих сумматоров-вычитателей первой и второй групп, выход генератора тактовых импульсов подключен к тактовому входу генератора псевдослучайных чисел, входу синхронизации аналого-цифрового преобразователя и счетному входу счетчика, информационный выход которого подключен к адресному входу блока постоянной памяти, М информационных выходов первой и второй групп которого подключены к первым входам М блоков сравнения соответственно первой и второй групп, выходы которых подключены к входам выбора режима работы М накапливающих сумматоров-вычитателей соответственно первой и второй групп, выходы которых являются выходами первой и второй групп соответственно реальной и мнимой частей гармоник низкочастотной полосы спектра, выход генератора псевдослучайных чисел подключен к вторым входам М блоков сравнения первой и второй групп, выход генератора тактовых импульсов подключен к входу элемента задержки и тактовым входам R делителей частоты, выходы которого подключены к входам запуска соответствующих R блоков синхронизации, первый и второй выходы которых подключены к входам выбора режима работы R накапливающих сумматоров-вычитателей соответственно первой и второй групп, выходы которых являются выходами первой и второй групп соответственно реальной и мнимой частей гармоник высокочастотной полосы спектра, выход элемента задержки подключен к тактовым входам R блоков синхронизации (авт. св. СССР 1418747, МКИ G 06 F 15/332, Бюл. 31, 1988).

Недостатком данного устройства является низкая точность вычисления оценок коэффициентов Фурье. В частности, это объясняется тем, что оценки коэффициентов Фурье частично вычисляются с использованием приближенных фильтрующих функций, а частично вычисляются на основе деления частоты синхронизации опроса аналого-цифрового преобразователя и формирования периодически повторяющихся кодов, управляющих работой накапливающих сумматоров-вычитателей. Кроме того, утверждение о том, что если в фильтрующие функции алгоритмов вычисления оценок коэффициентов Фурье не входит число N, определяющее число выборок входного сигнала, то возможно исследовать реализации случайных процессов, представленных произвольным числом временных отсчетов, носит относительно условный характер. Известно, что случайная составляющая статистической погрешности обусловлена конечным объемом статистики и всегда зависит от числа выборок N. Следует отметить также то, что устройство является сложным в техническом отношении. Оно содержит две группы цифровых блоков сравнения, которые должны осуществлять операцию сравнения в общем случае многоразрядных отсчетов последовательности псевдослучайных чисел и числовых кодов, соответствующих значениям фильтрующих функций на выходах первой и второй групп блока постоянной памяти.

Целью изобретения является повышение точности вычисления оценок коэффициентов Фурье и упрощение устройства.

Цель достигается тем, что в устройство для выполнения преобразования Фурье, содержащее генератор тактовых импульсов, блок синхронизации, генератор вспомогательного случайного сигнала, выход которого соединен с вторым входом блока сравнения, двоичный счетчик, выход которого соединен с адресным входом блока постоянной памяти, первую и вторую группы накапливающих сумматоров-вычитателей, выходы которых являются выходами первой и второй групп устройства соответственно оценок âk и  (k=1,2,3,..., К) коэффициентов Фурье, введены формирователь коротких импульсов, первый и второй элементы И, Т-триггер и инвертор, причем первый вход блока сравнения является входом устройства, а выход соединен с входом формирователя коротких импульсов, с входами разрешения выполнения операций накапливающих сумматоров-вычитателей первой группы и с входом инвертора, выход которого соединен с входами разрешения выполнения операций накапливающих сумматоров-вычитателей второй группы, выход генератора тактовых импульсов соединен с тактовым входом блока синхронизации, выход счетных импульсов которого соединен со счетным входом двоичного счетчика, выход разрешения работы блока синхронизации соединен с вторым входом первого элемента И и с входами разрешения работы накапливающих сумматоров-вычитателей первой и второй групп, выход стробирующего импульса блока синхронизации соединен с вторым входом второго элемента И, выходы первой и второй групп блока постоянной памяти соединены с информационными входами накапливающих сумматоров-вычитателей соответственно первой и второй групп, выход формирователя коротких импульсов соединен с первым входом первого элемента И, выход которого соединен с Т-входом Т-триггера, прямой выход которого соединен с первым входом второго элемента И, выход которого соединен с входами увеличения на единицу накапливающих сумматоров-вычитателей второй группы, вход запуска блока синхронизации, вход сброса двоичного счетчика, вход сброса Т-триггера и входы сброса накапливающих сумматоров-вычитателей первой и второй групп объединены и подключены к входу "Пуск" устройства.

(k=1,2,3,..., К) коэффициентов Фурье, введены формирователь коротких импульсов, первый и второй элементы И, Т-триггер и инвертор, причем первый вход блока сравнения является входом устройства, а выход соединен с входом формирователя коротких импульсов, с входами разрешения выполнения операций накапливающих сумматоров-вычитателей первой группы и с входом инвертора, выход которого соединен с входами разрешения выполнения операций накапливающих сумматоров-вычитателей второй группы, выход генератора тактовых импульсов соединен с тактовым входом блока синхронизации, выход счетных импульсов которого соединен со счетным входом двоичного счетчика, выход разрешения работы блока синхронизации соединен с вторым входом первого элемента И и с входами разрешения работы накапливающих сумматоров-вычитателей первой и второй групп, выход стробирующего импульса блока синхронизации соединен с вторым входом второго элемента И, выходы первой и второй групп блока постоянной памяти соединены с информационными входами накапливающих сумматоров-вычитателей соответственно первой и второй групп, выход формирователя коротких импульсов соединен с первым входом первого элемента И, выход которого соединен с Т-входом Т-триггера, прямой выход которого соединен с первым входом второго элемента И, выход которого соединен с входами увеличения на единицу накапливающих сумматоров-вычитателей второй группы, вход запуска блока синхронизации, вход сброса двоичного счетчика, вход сброса Т-триггера и входы сброса накапливающих сумматоров-вычитателей первой и второй групп объединены и подключены к входу "Пуск" устройства.

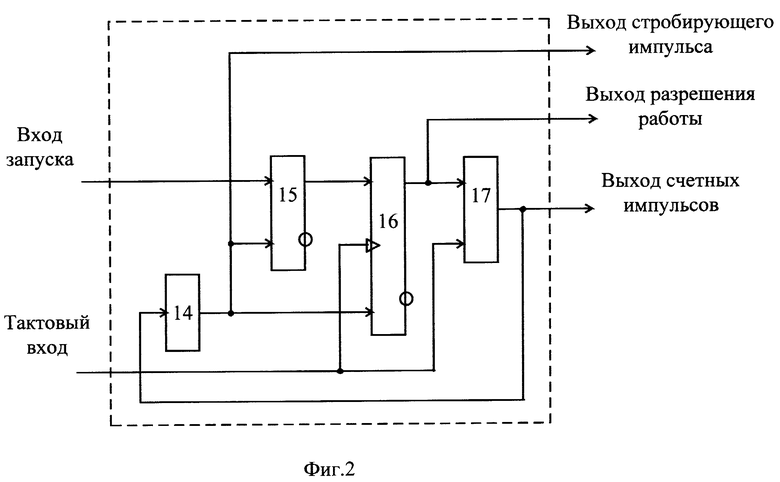

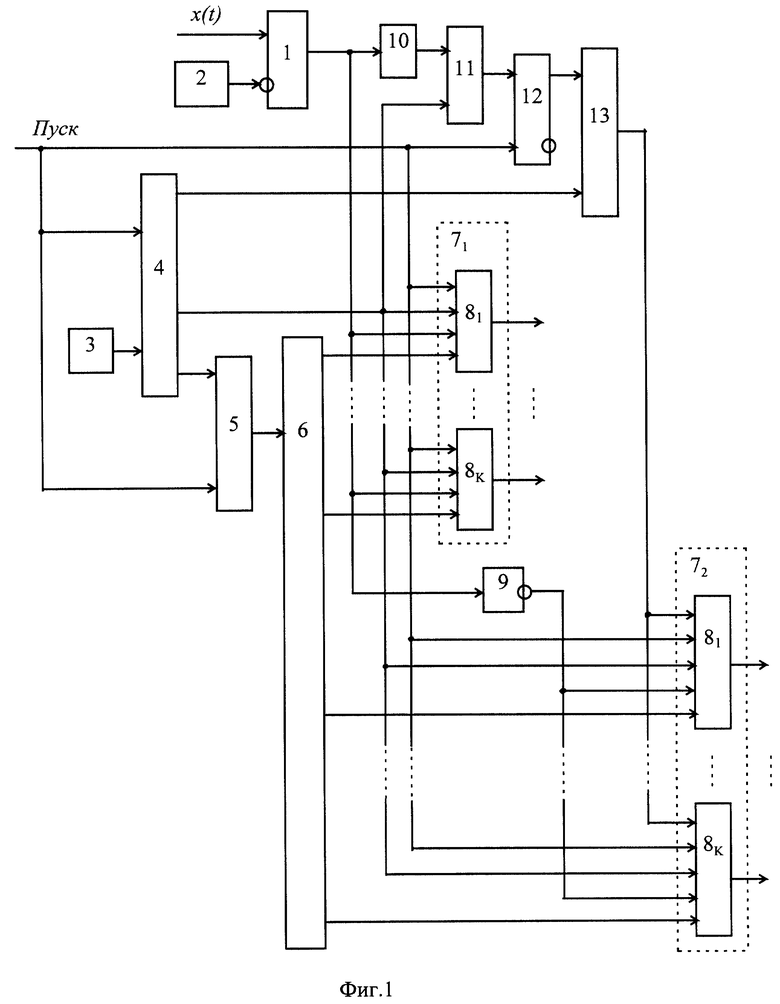

На фиг.1 представлена структурная схема устройства для выполнения преобразования Фурье; на фиг.2 - структурная схема блока синхронизации в одном из возможных вариантов его исполнения.

Устройство содержит блок 1 сравнения, генератор 2 вспомогательного случайного сигнала, генератор 3 тактовых импульсов, блок 4 синхронизации, двоичный счетчик 5, блок 6 постоянной памяти, первую 71 и вторую 72 группы, содержащие по К накапливающих сумматоров-вычитателей 81-8К каждая, инвертор 9, формирователь коротких импульсов 10, первый 11 и второй 13 элементы И и Т-триггер 12.

Блок 4 синхронизации содержит делитель 14, RS-триггер 15, D-триггер 16 и элемент И 17.

Первый вход блока 1 сравнения является входом устройства, а второй вход подключен к выходу генератора 2 вспомогательного случайного сигнала, выход блока 1 сравнения соединен с входом формирователя коротких импульсов 10, с входами разрешения выполнения операций накапливающих сумматоров-вычитателей 81-8К первой группы 71 и с входом инвертора 9, выход которого соединен с входами разрешения выполнения операций накапливающих сумматоров-вычитателей 81-8К второй группы 72, выход генератора 3 тактовых импульсов соединен с тактовым входом блока 4 синхронизации, выход счетных импульсов которого соединен со счетным входом двоичного счетчика 5, выход разрешения работы блока 4 синхронизации соединен с вторым входом первого 11 элемента И и с входами разрешения работы накапливающих сумматоров-вычитателей 81-8К первой 71 и второй 72 групп, выход стробирующего импульса блока 4 синхронизации соединен с вторым входом второго 13 элемента И, выход двоичного счетчика 5 соединен с адресным входом блока 6 постоянной памяти, выходы первой и второй групп которого соединены с информационными входами накапливающих сумматоров-вычитателей 81-8К соответственно первой 71 и второй 72 групп, выход формирователя коротких импульсов 10 соединен с первым входом первого 11 элемента И, выход которого соединен с Т-входом Т-триггера 12, прямой выход которого соединен с первым входом второго 13 элемента И, выход которого соединен с входами увеличения на единицу накапливающих сумматоров-вычитателей 81-8К второй 72 группы, вход запуска блока 4 синхронизации, вход сброса двоичного счетчика 5, вход сброса Т-триггера 12 и входы сброса накапливающих сумматоров-вычитателей 81-8К первой 71 и второй 72 групп объединены и подключены к входу "Пуск" устройства, выходы накапливающих сумматоров-вычитателей 81-8К первой 71 и второй 72 групп являются выходами первой и второй групп устройства соответственно оценок âk и  (k= 1,2,3,..., К) коэффициентов Фурье.

(k= 1,2,3,..., К) коэффициентов Фурье.

В блоке 4 синхронизации первый вход элемента И 17 и тактовый вход D-триггера 16 объединены и являются тактовым входом блока, S-вход, RS-триггера 15 является входом запуска блока, прямой выход RS-триггера 15 соединен с D-входом D-триггера 16, прямой выход которого соединен с вторым входом элемента И 17 и является выходом разрешения работы, выход элемента И 17 соединен с входом делителя 14 и является выходом счетных импульсов, выход делителя 14 соединен с R-входами RS-триггера 15 и D-триггера 16 и является выходом стробирующего импульса.

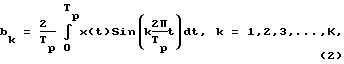

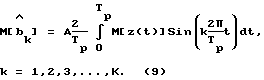

По определению для исследуемого сигнала x(t) коэффициенты Фурье аk и bk на интервале времени Тp определяются следующими интегралами:

где  и

и  косинусоидальные и синусоидальные фильтрующие функции, частоты которых меняются дискретно с шагом fo = 1/Tp.

косинусоидальные и синусоидальные фильтрующие функции, частоты которых меняются дискретно с шагом fo = 1/Tp.

Интегралы (1) и (2) хорошо известны. Однако непосредственная их техническая реализация затруднена.

Упростить процедуру анализа сигнала x(t) позволяет знаковый метод первичного преобразования с использованием вспомогательного случайного сигнала ξ(t). В общем случае такое преобразование имеет следующий вид

z(t) = Sgn{x(t)-ξ(t)}, (3)

где Sgn{...} - оператор знаковой функции.

Вспомогательный сигнал ξ(t) независим по отношению к исследуемому сигналу x(t). Мгновенные значения сигнала ξ(t) распределены равномерно внутри интервала от -А до +А. При этом величина А должна удовлетворять условию

|x(t)|max≤A, (4)

где |x(t)|max - максимально возможное абсолютное значение, которое может принять сигнал x(t).

В основе теоретического обоснования использования знакового преобразования вида (3) лежит известное соотношение (см. Мирский Г.Я. Характеристики стохастической взаимосвязи и их измерения - М.: Энергоиздат, 1982. - С. 194, соотношение (4.79))

M[x(t)]= A M [z(t)], (5)

где M[...] - оператор математического ожидания.

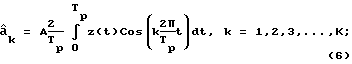

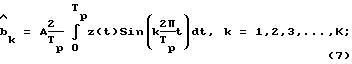

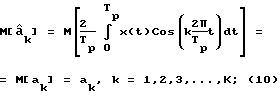

С учетом соотношения (5) оценки âk и  коэффициентов Фурье можно вычислять по формулам

коэффициентов Фурье можно вычислять по формулам

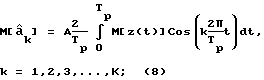

Математическое ожидание оценок (6) и (7) будет равно

Принимая во внимание соотношение (5), а также то, что операция нахождения математического ожидания и операция интегрирования являются линейными операциями, будем иметь

Из (10) и (11) нетрудно видеть, что оценки âk и  коэффициентов Фурье являются несмещенными.

коэффициентов Фурье являются несмещенными.

Обозначим через to и tQ моменты времени, соответствующие началу и концу процесса вычисления оценок âk и  В этом случае Tp=tQ-to. Пусть {t1, t2,.. ., tQ-1} моменты времени, в которые знаковый сигнал z(t) меняет свой знак на противоположенный на интервале времени t0≤t≤tQ. Тогда

В этом случае Tp=tQ-to. Пусть {t1, t2,.. ., tQ-1} моменты времени, в которые знаковый сигнал z(t) меняет свой знак на противоположенный на интервале времени t0≤t≤tQ. Тогда

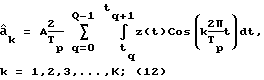

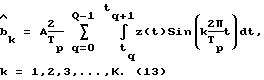

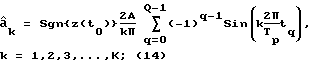

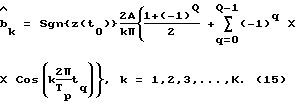

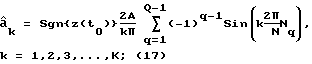

Вследствие того, что сигнал z(t) принимает значения, равные только "-1" или "+1", и остается постоянным в переделах интервала времени tq≤t≤tq+1, где q=0,1,2,3,...,Q-1, оценки (12) и (13) после интегрирования примут вид

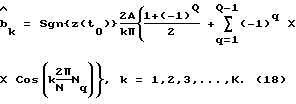

При дискретном представлении результата знакового преобразования, то есть при переходе к дискретному времени t=nТ0, где Т0 - интервал времени опроса (обычно он равен периоду следования тактовых импульсов), получаем, что моменты времени, соответствующие началу и концу процесса вычисления оценок âk и  будут равны t0=N0T0 и tQ=NQT0. В этом случае Тp=NQT0-N0T0= NT0, где N= NQ-N0. Кроме того моменты времени {t1,t2,...,tQ-1}, в которые знаковый сигнал z(t) меняет свой знак на противоположенный на интервале времени t0≤t≤tQ, можно записать следующим образом

будут равны t0=N0T0 и tQ=NQT0. В этом случае Тp=NQT0-N0T0= NT0, где N= NQ-N0. Кроме того моменты времени {t1,t2,...,tQ-1}, в которые знаковый сигнал z(t) меняет свой знак на противоположенный на интервале времени t0≤t≤tQ, можно записать следующим образом

tq = NqT0, q = 1,2,3,..., Q-1. (16)

Отметим, что полученное множество величин {N0, N1, N2,...,NQ} является цифровым эквивалентом моментов времени { t0,t1,t2,...,tQ} и представляет собой множество положительных целых чисел.

Отметим также то, что непрерывному интервалу времени t0≤t≤tQ вычисления оценок âk и  будет соответствовать его дискретное представление N0Т0≤nТ0≤NQT0 или просто N0≤n≤NQ. При этом общее число дискретных отсчетов времени на этом интервале, определяющее время вычисления Тр, будет равно N=NQ-N0.

будет соответствовать его дискретное представление N0Т0≤nТ0≤NQT0 или просто N0≤n≤NQ. При этом общее число дискретных отсчетов времени на этом интервале, определяющее время вычисления Тр, будет равно N=NQ-N0.

Таким образом окончательно получаем следующие алгоритмы дискретного вычисления оценок âk и  и коэффициентов Фурье

и коэффициентов Фурье

Из полученных выражений нетрудно видеть, что вся процедура вычисления оценок âk и  коэффициентов Фурье в конечном итоге сводится к выполнению простейших арифметических операций суммирования и вычитания дискретных значений фильтрующих функций

коэффициентов Фурье в конечном итоге сводится к выполнению простейших арифметических операций суммирования и вычитания дискретных значений фильтрующих функций  и

и  (где k=l,2,3,...,K), вычисленных в моменты времени, когда сигнал z(t) меняет свой знак на противоположенный на интервале времени вычисления t0≤t≤tQ. При этом в процессе вычисления оценок âk операция суммирования выполняется в моменты времени, когда знаковый сигнал z(t) меняет свое текущее значение с "+1" на "-1", а операция вычитания - в моменты времени, когда знаковый сигнал z(t) меняет свое текущее значение с "-1" на "+1". Что касается вычисления оценок

(где k=l,2,3,...,K), вычисленных в моменты времени, когда сигнал z(t) меняет свой знак на противоположенный на интервале времени вычисления t0≤t≤tQ. При этом в процессе вычисления оценок âk операция суммирования выполняется в моменты времени, когда знаковый сигнал z(t) меняет свое текущее значение с "+1" на "-1", а операция вычитания - в моменты времени, когда знаковый сигнал z(t) меняет свое текущее значение с "-1" на "+1". Что касается вычисления оценок  то здесь все происходит наоборот, то есть операция суммирования выполняется в моменты времени, когда знаковый сигнал z(t) меняет свое текущее значение с "-1" на "+1", а операция вычитания - в моменты времени, когда знаковый сигнал z(t) меняет свое текущее значение с "+1" на "-1".

то здесь все происходит наоборот, то есть операция суммирования выполняется в моменты времени, когда знаковый сигнал z(t) меняет свое текущее значение с "-1" на "+1", а операция вычитания - в моменты времени, когда знаковый сигнал z(t) меняет свое текущее значение с "+1" на "-1".

Важно отметить также то обстоятельство, что при четном Q, которое соответствует моменту времени tQ окончания процесса вычисления оценок (17) и (18), слагаемое  входящее в выражение (18) для вычисления оценок

входящее в выражение (18) для вычисления оценок  будет равно единице, и соответственно при нечетном Q это слагаемое будет равно нулю.

будет равно единице, и соответственно при нечетном Q это слагаемое будет равно нулю.

Выражения (17) и (18) непосредственно положены в основу работы устройства.

Устройство работает следующим образом.

Исследуемый сигнал x(t) поступает на вход устройства, то есть на первый вход блока 1 сравнения, на второй вход которого поступает сигнал ξ(t) с выхода генератора 2 вспомогательного случайного сигнала. В качестве вспомогательного сигнала ξ(t) допускается использовать линейно изменяющийся периодический сигнал (см. Мирский Г.Я. Характеристики стохастической взаимосвязи и их измерения - М.: Энергоиздат, 1982. С. 190). В частности можно использовать сигнал треугольной формы. (Схему генератора треугольной формы см. в книге: Применение прецизионных аналоговых микросхем / А.Г.Алексенко, Е.А.Коломбет, Г. И.Стародуб. - М.: Радио и связь, 1985. - С. 165-168, рис. 4.11-4.13.)

Блок 1 сравнения осуществляет сравнение сигналов x(t) и ξ(t). В результате выполнения этой операции на выходе блока 1 сравнения будет присутствовать знаковый сигнал z(t).

Поскольку на практике схемы сравнения всегда фиксируют нулевые значения знаковых сигналов с равной вероятностью либо как "-1", либо как "+1", при измерениях обычно используют знаковую функцию, которая принимает значения "-1" и "+1" (см. Мирский Г.Я. Характеристики стохастической взаимосвязи и их измерения - М. : Энергоиздат, 1982. С. 179). В соответствии с этим сигнал z(t) можно представить следующим образом

При технической реализации устройства в качестве блока 1 сравнения можно использовать интегральный компаратор (см. Нефедов А.В. Интегральные микросхемы и их зарубежные аналоги: Справочник. Т. 5. - М.: КУбК-а, 1997. - С. 113-119). В этом случае уровень логической единицы на выходе блока 1 сравнения будет соответствовать значению "+1" знакового сигнала z(t), а уровень логического нуля на выходе этого блока будет соответствовать значению "-1" знакового сигнала z(t).

Начало работы устройства осуществляется по сигналу "Пуск", который представляет собой короткий импульс.

Сигнал "Пуск" поступает на вход запуска блока 4 синхронизации, на вход сброса двоичного счетчика 5, на вход сброса Т-триггера 12 и на входы сброса накапливающих сумматоров-вычитателей 81-8К первой 71 и второй 72 групп.

В результате действия сигнала "Пуск" двоичный счетчик 5 и накапливающие сумматоры-вычитатели 81-8К первой 71 и второй 72 групп обнуляются, а на прямом выходе Т-триггера 12 устанавливается уровень логического нуля.

По сигналу "Пуск" на выходе счетных импульсов блока 4 синхронизации появляются счетные импульсы, которые поступают на счетный вход двоичного счетчика 5. Одновременно на выходе разрешения работы блока 4 синхронизации устанавливается уровень логической единицы, который поступает на второй вход первого 11 элемента И и на входы разрешения работы накапливающих сумматоров-вычитателей 81-8К первой 71 и второй 72 групп.

Рассмотрим более подробно работу блока 4 синхронизации на примере одного из возможных вариантов его исполнения (см. фиг.2).

В исходном состоянии на прямых выходах RS-триттера 15 и D-триггера 16 присутствуют уровни логического нуля. Уровень логического нуля с прямого выхода D-триггера 16 поступает на второй вход элемента И 17 и запрещает прохождение на выход этого элемента тактовых импульсов с его первого входа, который является тактовым входом блока 4 синхронизации и подключен к выходу генератора 3 тактовых импульсов. Сигнал "Пуск" поступает на вход запуска блока 4 синхронизации и далее поступает на S-вход RS-триггера 15, на прямом выходе которого устанавливается уровень логической единицы. Уровень логической единицы с прямого выхода RS-триггера 15 поступает на D-вход D-триггера 16, на тактовый вход которого поступают тактовые импульсы с тактового входа блока. При поступлении очередного тактового импульса по его переднему фронту на прямом выходе D-триггера 16 устанавливается уровень логической единицы, который поступает на выход разрешения работы, а также на второй вход элемента И 17 и разрешает прохождение тактовых импульсов на выход этого элемента с его первого входа. Тактовые импульсы с выхода элемента И 17 проходят на выход счетных импульсов, а также одновременно поступают на вход делителя 14. Момент времени появления счетных импульсов на выходе счетных импульсов блока 4 синхронизации и установления уровня логической единицы на выходе разрешения работы этого блока определяет начало процесса вычисления оценок âk и  коэффициентов Фурье и соответствует моменту времени t0, которое условно можно считать равным нулю. D-триггер 16 используется для синхронизации начала процесса вычисления с началом периода следования тактовых импульсов. (В качестве RS-триггера 10, D-триггера 11 и элемента И 12 могут быть использованы соответственно элементы К555ТМ2 и К555ЛИ1. См. Нефедов А.В. Интегральные микросхемы и их зарубежные аналоги: Справочник. Т.5. - М.: КУбК-а, 1997. - С.255, 281. В

коэффициентов Фурье и соответствует моменту времени t0, которое условно можно считать равным нулю. D-триггер 16 используется для синхронизации начала процесса вычисления с началом периода следования тактовых импульсов. (В качестве RS-триггера 10, D-триггера 11 и элемента И 12 могут быть использованы соответственно элементы К555ТМ2 и К555ЛИ1. См. Нефедов А.В. Интегральные микросхемы и их зарубежные аналоги: Справочник. Т.5. - М.: КУбК-а, 1997. - С.255, 281. В

качестве делителя 14 можно использовать, например, хорошо известную интегральную микросхему программируемого таймера К580ВИ53 или его аналоги. См. Алексенко А. Г. , Галицын А.А., Иванников А.Д. Проектирование радиоэлектронной аппаратуры на микропроцессорах: Программирование, типовые решения, методы отладки. - М.: Радио и связь, 1984. С. 65-72.)

Счетные импульсы с выхода счетных импульсов блока 4 синхронизации поступают на счетный вход двоичного счетчика 5, выход которого соединен с адресным входом блока 6 постоянной памяти. (В качестве двоичного счетчика можно использовать, например, счетчик К555ИЕ10. См. Нефедов А.В. Интегральные микросхемы и их зарубежные аналоги: Справочник. Т. 5. - М.: КУбК-а, 1997. - с. 166. Блок постоянной памяти может быть построен, например, на основе микросхем серии К573. См. Полупроводниковые БИС запоминающих устройств: Справочник / В.В.Баранов, Н.В.Бекин, А.Ю.Гордонов и др.; Под ред. А.Ю.Гордонова и Ю.Н.Дьякова. - М.: Радио и связь, 1987.-С. 305-312.)

Блок 6 постоянной памяти имеет две группы выходов по К выходов в каждой. На выходах первой группы блока 6 постоянной памяти формируются числовые последовательности, соответствующие значениям фильтрующих функций  (где k= 1,2,3,..., К) для первой 71 группы накапливающих сумматоров-вычитателей 81-8К, а на выходах второй группы блока 6 постоянной памяти формируются числовые последовательности, соответствующие значениям фильтрующих функций

(где k= 1,2,3,..., К) для первой 71 группы накапливающих сумматоров-вычитателей 81-8К, а на выходах второй группы блока 6 постоянной памяти формируются числовые последовательности, соответствующие значениям фильтрующих функций  (где k= 1,2,3,..., К) для второй 72 группы накапливающих сумматоров-вычитателей 81-8К. При этом значение п определяется текущим содержимым двоичного счетчика 5. Значения фильтрующих функций с выходов первой и второй групп блока 6 постоянной памяти поступают на информационные входы накапливающих сумматоров-вычитателей 81-8К соответственно первой 71 и второй 72 групп, на входы разрешения работы которых поступает уровень логической единицы с выхода разрешения работы блока 4 синхронизации. Данный сигнал разрешает работу накапливающим сумматорам-вычитателям 81-8К первой 71 и второй 72 групп, под управлением сигнала z(t). При этом сигнал z(t) с выхода блока 4 синхронизации поступает на входы разрешения выполнения операций накапливающих сумматоров-вычитателей 81-8К первой 71 группы непосредственно, а на входы разрешения выполнения операций накапливающих сумматоров-вычитателей 81-8К второй 72 группы - через инвертор 9.

(где k= 1,2,3,..., К) для второй 72 группы накапливающих сумматоров-вычитателей 81-8К. При этом значение п определяется текущим содержимым двоичного счетчика 5. Значения фильтрующих функций с выходов первой и второй групп блока 6 постоянной памяти поступают на информационные входы накапливающих сумматоров-вычитателей 81-8К соответственно первой 71 и второй 72 групп, на входы разрешения работы которых поступает уровень логической единицы с выхода разрешения работы блока 4 синхронизации. Данный сигнал разрешает работу накапливающим сумматорам-вычитателям 81-8К первой 71 и второй 72 групп, под управлением сигнала z(t). При этом сигнал z(t) с выхода блока 4 синхронизации поступает на входы разрешения выполнения операций накапливающих сумматоров-вычитателей 81-8К первой 71 группы непосредственно, а на входы разрешения выполнения операций накапливающих сумматоров-вычитателей 81-8К второй 72 группы - через инвертор 9.

Накапливающие сумматоры-вычитатели 81-8К первой 71 и второй 72 групп выполняют операции суммирования или вычитания только при наличии на их входах разрешения работы уровня логической единицы, поступающего с выхода разрешения работы блока 4 синхронизации, и только в моменты времени смены значения логического уровня сигнала z(t) для первой 71 группы и инверсного сигнала z(t) для второй 72 группы.

В моменты времени, когда сигнал z(t) меняет значение своего логического уровня с единицы на нуль, выполняется операция суммирования поступающих текущих значений фильтрующих функций  (где k=I,2,3,...,K) с содержимым накапливающих сумматоров-вычитателей 81-8К первой 71 группы. В моменты времени, когда сигнал z(t) меняет значение своего логического уровня с нуля на единицу, выполняется операция вычитания поступающих текущих значений фильтрующих функций

(где k=I,2,3,...,K) с содержимым накапливающих сумматоров-вычитателей 81-8К первой 71 группы. В моменты времени, когда сигнал z(t) меняет значение своего логического уровня с нуля на единицу, выполняется операция вычитания поступающих текущих значений фильтрующих функций  (где k=l,2,3,...,K) из содержимого накапливающих сумматоров-вычитателей 81-8К первой 71 группы. Работа накапливающих сумматоров-вычитателей 81-8К второй 72 группы аналогична работе накапливающих сумматоров-вычитателей 81-8К первой 71 группы с той лишь разницей, что на их входы разрешения выполнения операций поступает инверсный сигнал z(t) с выхода инвертора 9. Поэтому в этом случае операция суммирования поступающих текущих значений фильтрующих функций

(где k=l,2,3,...,K) из содержимого накапливающих сумматоров-вычитателей 81-8К первой 71 группы. Работа накапливающих сумматоров-вычитателей 81-8К второй 72 группы аналогична работе накапливающих сумматоров-вычитателей 81-8К первой 71 группы с той лишь разницей, что на их входы разрешения выполнения операций поступает инверсный сигнал z(t) с выхода инвертора 9. Поэтому в этом случае операция суммирования поступающих текущих значений фильтрующих функций  (где k= 1,2,3,..., К) с содержимым накапливающих сумматоров-вычитателей 81-8К второй 72 группы происходит в моменты времени смены значения логического уровня с единицы на нуль инверсным сигналом z(t). В моменты же времени, когда инверсный сигнал z(t) меняет значение своего логического уровня с нуля на единицу, выполняется операция вычитания поступающих текущих значений фильтрующих функций

(где k= 1,2,3,..., К) с содержимым накапливающих сумматоров-вычитателей 81-8К второй 72 группы происходит в моменты времени смены значения логического уровня с единицы на нуль инверсным сигналом z(t). В моменты же времени, когда инверсный сигнал z(t) меняет значение своего логического уровня с нуля на единицу, выполняется операция вычитания поступающих текущих значений фильтрующих функций  (где k=1,2,3,...,K) из содержимого накапливающих сумматоров-вычитателей 81-8К второй 72 группы.

(где k=1,2,3,...,K) из содержимого накапливающих сумматоров-вычитателей 81-8К второй 72 группы.

Сигнал z(t) с выхода блока 1 сравнения поступает также на вход формирователя коротких импульсов 10. В моменты времени, соответствующие переходу значения сигнала z(t) из логического нуля в логическую единицу или из логической единицы в логический нуль, на выходе формирователя коротких импульсов 10 появляются импульсы. Другими словами, формирователь коротких импульсов 10 осуществляет выделение фронтов и срезов сигнала z(t). (Одну из возможных схем технической реализации формирователя коротких импульсов с временными диаграммами его работы см. Цифровые интегральные микросхемы: Справочник / М. И.Богданович, И.Н.Грель, С.А. Дубина и др. - 2-е изд., перераб. и доп. - Мн. : Беларусь, Полымя. 1996. -С. 278. Рис. 2.205.) Импульсы с выхода формирователя коротких импульсов 10 поступают на первый вход первого 11 элемента И и проходят на его выход, так как на второй вход этого элемента после подачи сигнала "Пуск" с выхода разрешения работы блока 4 синхронизации поступает уровень логической единицы. Импульсы с выхода первого 11 элемента И поступают на Т-вход Т-триггера 12, который по сигналу "Пуск" был установлен в нулевое состояние. Смена состояний Т-триггера 12 происходит всякий раз, когда на его Т-вход поступает очередной импульс. Нетрудно видеть, что на прямом выходе этого триггера будет присутствовать уровень логической единицы, если к этому моменту времени на его Т-вход поступило нечетное общее количество импульсов. Если же на прямом выходе Т-триггера 12 будет присутствовать уровень логического нуля, то это означает, что к этому моменту времени на его Т-вход поступило четное общее количество импульсов. Прямой выход Т-триггера 12 соединен с первым входом второго 13 элемента И, второй вход которого подключен к выходу стробирующего импульса блока 4 синхронизации. (В качестве первого 11 и второго 13 элементов И и Т-триггера 12 могут быть использованы соответственно элементы К555ЛИ1 и К555ТВ6. См. Нефедов А.В. Интегральные микросхемы и их зарубежные аналоги: Справочник. Т.5. - М.: КУбК-а, 1997. - С. 255, 277.)

После прохождения N тактовых импульсов на выход счетных импульсов блока 4 синхронизации, которые одновременно поступают и на вход делителя 14 (см. фиг. 2), на выходе делителя 14 вырабатывается импульс. Этот момент времени соответствует времени tQ окончания процесса вычисления оценок âk и  Импульс с выхода делителя 14 поступает на R-входы RS-триггера 15 и D-триггера 16 и возвращает эти триггеры в исходное нулевое состояние, то есть на их прямых выходах устанавливаются уровни логического нуля. Уровень логического нуля с прямого выхода D-триггера 16 поступает на второй вход элемента И 17 и запрещает прохождение на выход этого элемента тактовых импульсов с его первого входа. Соответственно прекращается прохождение тактовых импульсов и на выход блока 4 синхронизации. Прямой выход D-триггера 16 является также выходом разрешения работы блока 4 синхронизации. Поэтому уровень логического нуля с выхода разрешения работы блока 4 синхронизации поступает на входы разрешения работы накапливающих сумматоров-вычитателей 81-8К первой 71 и второй 72 групп и запрещает им выполнение операций суммирования или вычитания под управлением соответственно сигнала z(t) и инверсного сигнала z(t). Уровень логического нуля с выхода разрешения работы блока 4 синхронизации поступает также на второй вход первого 11 элемента И и запрещает прохождение на выход этого элемента импульсов, поступающих на его первый вход с выхода формирователя коротких импульсов 10. Одновременно импульс с выхода делителя 14 (см. фиг. 2) проходит на выход стробирующего импульса блока 4 синхронизации и далее поступает на второй вход второго 13 элемента И. Отметим еще раз, что стробирующий импульс соответствует моменту времени tQ окончания вычисления оценок âk и

Импульс с выхода делителя 14 поступает на R-входы RS-триггера 15 и D-триггера 16 и возвращает эти триггеры в исходное нулевое состояние, то есть на их прямых выходах устанавливаются уровни логического нуля. Уровень логического нуля с прямого выхода D-триггера 16 поступает на второй вход элемента И 17 и запрещает прохождение на выход этого элемента тактовых импульсов с его первого входа. Соответственно прекращается прохождение тактовых импульсов и на выход блока 4 синхронизации. Прямой выход D-триггера 16 является также выходом разрешения работы блока 4 синхронизации. Поэтому уровень логического нуля с выхода разрешения работы блока 4 синхронизации поступает на входы разрешения работы накапливающих сумматоров-вычитателей 81-8К первой 71 и второй 72 групп и запрещает им выполнение операций суммирования или вычитания под управлением соответственно сигнала z(t) и инверсного сигнала z(t). Уровень логического нуля с выхода разрешения работы блока 4 синхронизации поступает также на второй вход первого 11 элемента И и запрещает прохождение на выход этого элемента импульсов, поступающих на его первый вход с выхода формирователя коротких импульсов 10. Одновременно импульс с выхода делителя 14 (см. фиг. 2) проходит на выход стробирующего импульса блока 4 синхронизации и далее поступает на второй вход второго 13 элемента И. Отметим еще раз, что стробирующий импульс соответствует моменту времени tQ окончания вычисления оценок âk и  Это означает, что к этому моменту времени на Т-вход Т-триггера 12 с момента времени t0 начала процесса вычисления поступило (Q-1) импульсов, соответствующих моментам времени {t1, t2,..., tQ-1}, в которые знаковый сигнал z(t) меняет свой знак на противоположенный на интервале времени t0≤t≤tQ.

Это означает, что к этому моменту времени на Т-вход Т-триггера 12 с момента времени t0 начала процесса вычисления поступило (Q-1) импульсов, соответствующих моментам времени {t1, t2,..., tQ-1}, в которые знаковый сигнал z(t) меняет свой знак на противоположенный на интервале времени t0≤t≤tQ.

Как было отмечено выше, Т-триггер 12 фактически выполняет операцию счета поступающих на его Т-вход импульсов с выхода формирователя коротких импульсов 10. Поэтому уровень логической единицы на прямом выходе этого триггера говорит о том, что число (Q-1) поступивших импульсов на его Т-вход является нечетным, и, следовательно, число Q, соответствующее моменту времени tQ окончания процесса вычисления оценок âk и  будет четным. В противном случае, то есть если на прямом выходе Т-триггера 12 будет присутствовать уровень логического нуля, то это означает, что число (Q-1) поступивших импульсов на его Т-вход является четным, и, следовательно, число Q, соответствующее моменту времени tQ окончания процесса вычисления оценок âk и

будет четным. В противном случае, то есть если на прямом выходе Т-триггера 12 будет присутствовать уровень логического нуля, то это означает, что число (Q-1) поступивших импульсов на его Т-вход является четным, и, следовательно, число Q, соответствующее моменту времени tQ окончания процесса вычисления оценок âk и  будет нечетным. Таким образом, если на прямом выходе Т-триггера 12 будет присутствовать уровень логической единицы, то число Q будет четным, то есть слагаемое

будет нечетным. Таким образом, если на прямом выходе Т-триггера 12 будет присутствовать уровень логической единицы, то число Q будет четным, то есть слагаемое  входящее в выражение (18), должно быть равным единице, и его необходимо учесть в конечном результате вычисления оценок

входящее в выражение (18), должно быть равным единице, и его необходимо учесть в конечном результате вычисления оценок  В соответствии с этим стробирующий импульс проходит на выход второго 13 элемента И и поступает на входы увеличения на единицу накапливающих сумматоров-вычитателей 81-8К второй 72 группы. В результате к содержимому этих накапливающих сумматоров-вычитателей добавляется единица. Если же на прямом выходе Т-триггера 12 присутствует уровень логического нуля, то это означает, что число Q будет нечетным, то есть слагаемое

В соответствии с этим стробирующий импульс проходит на выход второго 13 элемента И и поступает на входы увеличения на единицу накапливающих сумматоров-вычитателей 81-8К второй 72 группы. В результате к содержимому этих накапливающих сумматоров-вычитателей добавляется единица. Если же на прямом выходе Т-триггера 12 присутствует уровень логического нуля, то это означает, что число Q будет нечетным, то есть слагаемое  входящее в выражение (18), должно быть равным нулю, и оно не оказывает влияния на конечный результат вычисления оценок

входящее в выражение (18), должно быть равным нулю, и оно не оказывает влияния на конечный результат вычисления оценок  Практически это означает, что уровень логического нуля с прямого выхода Т-триггера 12 поступает на первый вход второго 13 элемента И и запрещает прохождение на его выход стробирующего импульса. В результате содержимое накапливающих сумматоров-вычитателей 81-8К второй 72 группы остается без изменения. (Накапливающие сумматоры-вычитатели могут быть реализованы, например, на основе арифметическо-логических схем К531ИК2 или 100ИМ180. При этом в качестве входа увеличения на единицу можно использовать, например, вход внешнего переноса. См. Цифровые интегральные микросхемы: Справочник / M-И.Богданович, И.Н.Грель, С.А.Дубина и др. - 2-е изд., перераб. и доп. -Мн. : Беларусь, Полымя. 1996. - С. 270, 431-432.)

Практически это означает, что уровень логического нуля с прямого выхода Т-триггера 12 поступает на первый вход второго 13 элемента И и запрещает прохождение на его выход стробирующего импульса. В результате содержимое накапливающих сумматоров-вычитателей 81-8К второй 72 группы остается без изменения. (Накапливающие сумматоры-вычитатели могут быть реализованы, например, на основе арифметическо-логических схем К531ИК2 или 100ИМ180. При этом в качестве входа увеличения на единицу можно использовать, например, вход внешнего переноса. См. Цифровые интегральные микросхемы: Справочник / M-И.Богданович, И.Н.Грель, С.А.Дубина и др. - 2-е изд., перераб. и доп. -Мн. : Беларусь, Полымя. 1996. - С. 270, 431-432.)

По окончании действия стробирующего импульса процесс вычисления оценок âk и  коэффициентов преобразования Фурье завершается. К этому моменту времени, который, подчеркнем еще раз, соответствует моменту времени tQ, в накапливающих сумматорах-вычитателях 81-8К первой 71 и второй 72 групп будут накоплены соответственно следующие результаты

коэффициентов преобразования Фурье завершается. К этому моменту времени, который, подчеркнем еще раз, соответствует моменту времени tQ, в накапливающих сумматорах-вычитателях 81-8К первой 71 и второй 72 групп будут накоплены соответственно следующие результаты

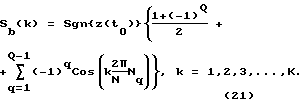

Полученные результаты Sa(k) и Sb(k) с точностью до постоянного множителя  совпадают с оценками âk и

совпадают с оценками âk и  коэффициентов Фурье, определяемых выражениями (17) и (18). Постоянный коэффициент

коэффициентов Фурье, определяемых выражениями (17) и (18). Постоянный коэффициент  может быть всегда учтен путем простого масштабирования, что не представляет особого труда.

может быть всегда учтен путем простого масштабирования, что не представляет особого труда.

Из приведенного описания видно, что в результате предварительно осуществленного интегрирования фильтрующих функций с учетом того, что знаковый сигнал z(t) строго последовательно принимает значения, равные только "-1" и "+1", вся процедура вычисления оценок âk и  коэффициентов Фурье сводится только к выполнению операций суммирования и вычитания соответствующих значений фильтрующих функций в моменты времени, определяемые сменой текущего значения сигнала z(t). Все это позволяет существенно повысить точность вычисления оценок âk и

коэффициентов Фурье сводится только к выполнению операций суммирования и вычитания соответствующих значений фильтрующих функций в моменты времени, определяемые сменой текущего значения сигнала z(t). Все это позволяет существенно повысить точность вычисления оценок âk и  коэффициентов Фурье и одновременно упростить устройство по сравнению с устройством-прототипом. При этом получаемые оценки âk и

коэффициентов Фурье и одновременно упростить устройство по сравнению с устройством-прототипом. При этом получаемые оценки âk и  коэффициентов Фурье являются несмещенными. Важным является и то обстоятельство, что устройство содержит только один блок сравнения.

коэффициентов Фурье являются несмещенными. Важным является и то обстоятельство, что устройство содержит только один блок сравнения.

Технически предлагаемое устройство реализуется на стандартных элементах, широко известных и применяемых в современной технике. Более того при современном уровне технологии разработки и производства интегральных микросхем в перспективе подобное устройство или отдельные его блоки могут быть реализованы в виде интегральных схем.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2000 |

|

RU2182724C2 |

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 1999 |

|

RU2174705C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПЛОТНОСТИ РАСПРЕДЕЛЕНИЯ ВЕРОЯТНОСТЕЙ СЛУЧАЙНОГО ПРОЦЕССА | 2000 |

|

RU2174706C1 |

| МНОГОКАНАЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 1999 |

|

RU2177637C2 |

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 2002 |

|

RU2252450C2 |

| ЦИФРОВОЙ РЕГУЛЯТОР ДЛЯ СИСТЕМЫ УПРАВЛЕНИЯ ЭЛЕКТРОМАГНИТНЫМ ПОДВЕСОМ РОТОРА | 2000 |

|

RU2181903C2 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ДВИЖЕНИЯ ОБЪЕКТОВ | 1994 |

|

RU2096927C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОЭФФИЦИЕНТА ВЗАИМНОЙ КОРРЕЛЯЦИИ СЛУЧАЙНЫХ СИГНАЛОВ | 2000 |

|

RU2181501C2 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

Изобретение относится к области вычислительной техники и может быть использовано при анализе случайных сигналов. Техническим результатом является повышение точности. Устройство содержит генератор тактовых импульсов, блок синхронизации, генератор вспомогательного случайного сигнала, блок сравнения, двоичный счетчик, блок постоянной памяти, накапливающие сумматоры-вычитатели, формирователь коротких импульсов, элементы И, Т-триггер и инвертор. 2 ил.

Устройство для выполнения преобразования Фурье, содержащее генератор тактовых импульсов, блок синхронизации, генератор вспомогательного случайного сигнала, выход которого соединен с вторым входом блока сравнения, двоичный счетчик, выход которого соединен с адресным входом блока постоянной памяти, первую и вторую группы накапливающих сумматоров-вычитателей, выходы которых являются выходами первой и второй групп устройства соответственно оценок  и

и  (k= l, 2,3, . . K) коэффициентов Фурье, отличающееся тем, что в него введены формирователь коротких импульсов, первый и второй элементы И, Т-триггер и инвертор, причем первый вход блока сравнения является входом устройства, а выход соединен с входом формирователя коротких импульсов, с входами разрешения выполнения операций накапливающих сумматоров-вычитателей первой группы и с входом инвертора, выход которого соединен с входами разрешения выполнения операций накапливающих сумматоров-вычитателей второй группы, выход генератора тактовых импульсов соединен с тактовым входом блока синхронизации, выход счетных импульсов которого соединен со счетным входом двоичного счетчика, выход разрешения работы блока синхронизации соединен с вторым входом первого элемента И и с входом разрешения работы накапливающих сумматоров-вычитателей первой и второй групп, выход стробирующего импульса блока синхронизации соединен с вторым входом второго элемента И, выходы первой и второй групп блока постоянной памяти соединены с информационными входами накапливающих сумматоров-вычитателей соответственно первой и второй групп, выход формирователя коротких импульсов соединен с первым входом первого элемента И, выход которого соединен с Т-входом Т-триггера, прямой выход которого соединен с первым входом второго элемента И, выход которого соединен с входами увеличения на единицу накапливающих сумматоров-вычитателей второй группы, вход запуска блока синхронизации, вход сброса двоичного счетчика, вход сброса Т-триггера и входы сброса накапливающих сумматоров-вычитателей первой и второй групп объединены и подключены к входу "Пуск" устройства.

(k= l, 2,3, . . K) коэффициентов Фурье, отличающееся тем, что в него введены формирователь коротких импульсов, первый и второй элементы И, Т-триггер и инвертор, причем первый вход блока сравнения является входом устройства, а выход соединен с входом формирователя коротких импульсов, с входами разрешения выполнения операций накапливающих сумматоров-вычитателей первой группы и с входом инвертора, выход которого соединен с входами разрешения выполнения операций накапливающих сумматоров-вычитателей второй группы, выход генератора тактовых импульсов соединен с тактовым входом блока синхронизации, выход счетных импульсов которого соединен со счетным входом двоичного счетчика, выход разрешения работы блока синхронизации соединен с вторым входом первого элемента И и с входом разрешения работы накапливающих сумматоров-вычитателей первой и второй групп, выход стробирующего импульса блока синхронизации соединен с вторым входом второго элемента И, выходы первой и второй групп блока постоянной памяти соединены с информационными входами накапливающих сумматоров-вычитателей соответственно первой и второй групп, выход формирователя коротких импульсов соединен с первым входом первого элемента И, выход которого соединен с Т-входом Т-триггера, прямой выход которого соединен с первым входом второго элемента И, выход которого соединен с входами увеличения на единицу накапливающих сумматоров-вычитателей второй группы, вход запуска блока синхронизации, вход сброса двоичного счетчика, вход сброса Т-триггера и входы сброса накапливающих сумматоров-вычитателей первой и второй групп объединены и подключены к входу "Пуск" устройства.

| Устройство для выполнения преобразования Фурье | 1987 |

|

SU1418747A1 |

| Устройство для выполнения преобразования Фурье | 1980 |

|

SU928363A1 |

| Устройство для выполнения преобразования фурье | 1984 |

|

SU1177822A1 |

| US 4904930 A, 27.02.1990 | |||

| US 4623980 А, 18.11.1986 | |||

| Способ получения кремнефторида щелочного металла | 1975 |

|

SU710915A1 |

Авторы

Даты

2002-05-10—Публикация

2000-02-28—Подача