Изобретение относится к области автоматики и вычислительной техники и может быть использовано в вычислительных машинах и устройствах, функционирующих в системе остаточных классов.

Известно устройство (аналог) для резервирования [1], содержащее в каждом из основных каналов резервированный блок, блок контроля, блок подключения резерва, управляемый переключатель и дополнительный резервируемый блок. Недостаток устройства - низкая отказоустойчивость.

Близким по технической сущности (аналогом) к предлагаемому изобретению является устройство для резервирования [2], содержащее первый и второй резервируемый блоки, первый и второй элементы И, элементы ИЛИ, схему сравнения, элемент задержки, формирователь импульса и триггер. Недостаток устройства - низкая отказоустойчивость.

Наиболее близким по технической сущности (прототипом) к предполагаемому изобретению является устройство [3], содержащее n информационных (n - количество оснований системы остаточных классов) и один контрольный тракты, блок контроля, группу элементов И, группу элементов ИЛИ, дешифратор, четыре элемента ИЛИ.

Недостаток прототипа - низкая отказоустойчивость. Это обстоятельство связано с тем, что при возникновении единичного отказа в любом вычислительном (информационном или контрольном) тракте он становится неработоспособным, что существенным образом сказывается на общей отказоустойчивости устройства. При использовании фибоначчивой системы счисления данный недостаток устраняется путем маскирования отказавших разрядов, ввиду возможности многозначного представления операндов. Переход тракта в неработоспособное состояние происходит лишь при полном исчерпании ресурсов маскирования.

Задача, на решение которой направлено заявляемое устройство, состоит в улучшении основных характеристик перспективных образцов вычислительной техники.

Технический результат состоит в повышении отказоустойчивости вычислительных структур.

Поставленная цель достигается тем, что в устройство для резервирования, содержащее n информационных (n - количество оснований системы остаточных классов) и один контрольный тракты, блок контроля, группу элементов ИЛИ, дешифратор, четыре элемента ИЛИ, причем контрольные выходы информационных и контрольного трактов соединены соответственно с входами блока контроля, выходы группы элементов И соединены с первыми входами группы элементов ИЛИ соответственно, n - выходов блока контроля соединены с соответствующими входами дешифратора и с первыми входами группы элементов И соответственно, вторые входы которых соединены с тактовым входом устройства, выходы группы элементов И соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с входом пуска контрольного тракта, первая и вторая группы выходов дешифратора соединены соответственно с входами второго и третьего элементов ИЛИ, выходы которых соединены соответственно с выходом "Исправно" устойчива и первым входом четвертого элемента ИЛИ, второй вход которого соединен с (n+1)-м выходом блока контроля, выход четвертого элемента ИЛИ соединен с входом "Останов" контрольного тракта и вторыми входами элементов ИЛИ группы, выходы которых соединены с входами "Останов" соответствующих информационных трактов, отличающееся тем, что в него введены группа преобразователей позиционного кода в p-код Фибоначчи и группа преобразователей p-кода Фибоначчи в позиционный код, причем выходы группы преобразователей позиционного кода в p-код Фибоначчи соединены соответственно с информационными входами информационных и контрольного трактов, а входы являются входом устройства, входы группы преобразователей p-кода Фибоначчи в позиционный код соединены соответственно с выходами информационных и контрольного трактов, а выходы являются выходом устройства, управляющие выходы блока контроля соединены с соответствующими управляющими входами группы преобразователей позиционного кода в p-код Фибоначчи.

Сущность изобретения состоит в использовании маскирования отказавших разрядов в каждом вычислительном тракте, ввиду чего увеличивается количество допустимых отказов устройства при сохранении его полной работоспособности.

Применение p-кодов Фибоначчи (для маскирования отказов типа константы 1 или константы 0 по каждому основанию) позволяет использовать меньшее количество двоичных разрядов для одного и того же диапазона представления чисел по сравнению с кодом золотой пропорции. Существенным фактом также является то обстоятельство, что схема контроля параллельного кода предельно проста (один логический элемент И на каждый разряд и один собирающий элемент ИЛИ), ввиду чего, в отличие от обычной системы остаточных классов (СОК), упрощается построение блока контроля. Он по каждому основанию СОК должен обнаруживать только наличие двух рядом стоящих единиц [4]. В условиях применения подобной комбинированной системы могут быть неисправны n разрядов (n - количество оснований СОК), по одному в каждом вычислительном тракте, при которых устройство сохраняет полную работоспособность, не требуя включения резервного тракта. Маскирование отказавших разрядов сводится к кодированию операндов таким образом, чтобы на месте константы 1 или 0 стояли соответствующие символы. Это возможно ввиду множественности представления числа в p-коде Фибоначчи.

Данный подход является синтезом двух перспективных направлений в области построения отказоустойчивых высокопроизводительных структур (использование кодов в классе вычетов и кодов с иррациональными основаниями). В многоустойчивой СОК количество неисправных разрядов может превышать число вычислительных трактов в два и более раз при нормальном функционировании устройства и отсутствии резервирования.

Дополнительным положительным фактором предлагаемой идеи является повышение быстродействия выполнения арифметических операций ввиду возможности применения табличной арифметики.

Выходной сигнал блока 2 контроля образуется в том случае, когда возможности маскирования отказавших разрядов уже исчерпаны. В противном случае с управляющего выхода блока 2 контроля поступают сигналы для проведения операции маскирования отказавших разрядов в соответствующих вычислительных 11-15 трактах устройства.

Основная идея прототипа состоит в том, что используется возможность заменить одним исправным контрольным трактом по основанию mn+1 СОК не один отказавший информационный тракт, а одновременно несколько отказавших. Это свойство сохранено в заявленном устройстве, дополнительно повышая его отказоустойчивость.

Пусть задана СОК информационными m1, m2, ..., mn и контрольным mn+1 основаниями, тогда условие замены одним исправным контрольным трактом одновременно r неисправных информационных трактов (условие перекрытия) представится в виде (1)

В таблице приведен пример образования кода выходных шин блока 2 контроля для СОК, заданной информационными основаниями m1= 3, m2=4, m3=5, m4=7 и контрольным основанием, равным m5=23

Присутствие единиц на определенных позициях кода выходных шин блока 2 контроля соответствует отказу трактов с номерами, соответствующими номерами позиций этих единиц. В таблице, в графе "Работоспособность" знаком "+" отмечено работоспособное состояние, а знаком "-" неработоспособное состояние устройства. Дешифратор 5 служит для преобразования кода числа из двоичного в десятичный. Первая группа дешифратора 5 объединяет выходные шины, для которых соответствующий двоичный код свидетельствует о работоспособности устройства. Вторая группа выходов дешифратора 5 объединяет выходные шины, для которых соответствующий двоичный код свидетельствует о неработоспособности устройства. Для приведенной СОК первая группа выходов дешифратора 5 объединяет 0, 1, 2, 4, 6, 8, 9, 10 и 12-выходные шины. Вторая группа выходов - 3, 5, 7, 11, 13, 14 и 15-выходные шины.

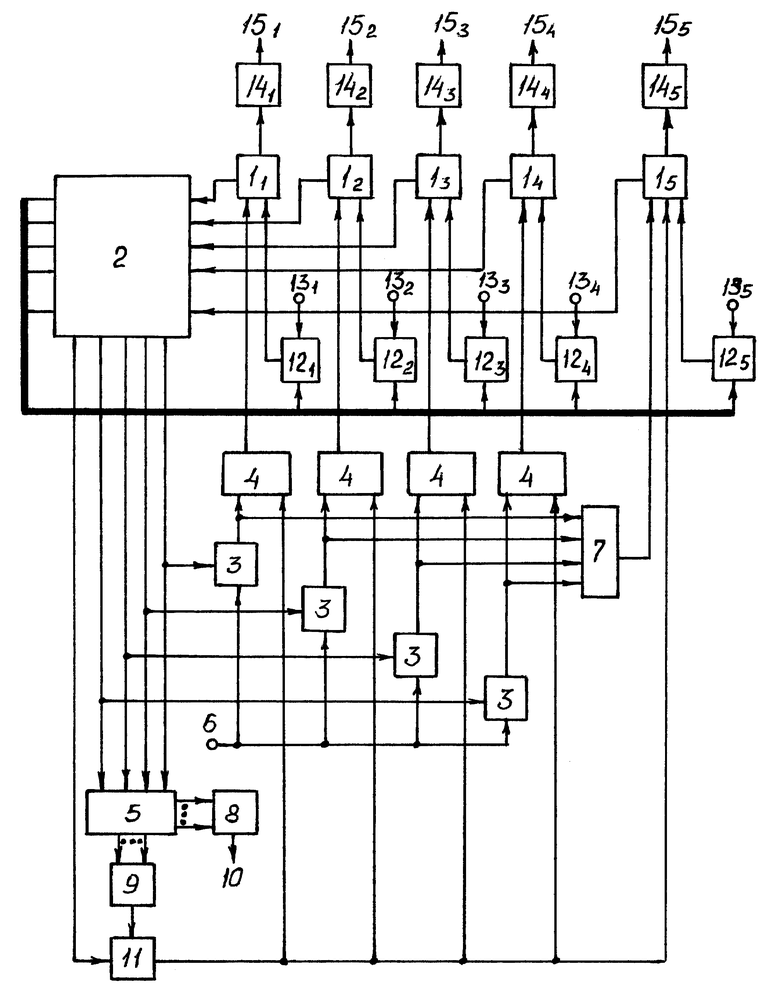

На чертеже представлена структурная схема, где  информационные и 15 - контрольный тракты, 2 - блок контроля, 3 - группа элементов И, 4 - группа элементов ИЛИ, 5 - дешифратор, 6 - тактовый вход устройства, 7 - первый элемент ИЛИ, 8 - второй элемент ИЛИ, 9 - третий элемент ИЛИ, 10 - выход "Исправно" устройства, 11 - четвертый элемент ИЛИ, 12j (j=1,5) - группа преобразователей позиционного кода в p-код Фибоначчи, 13j - вход устройства, 14j - группа преобразователей p-кода Фибоначчи в позиционный код, 15j - выход устройства.

информационные и 15 - контрольный тракты, 2 - блок контроля, 3 - группа элементов И, 4 - группа элементов ИЛИ, 5 - дешифратор, 6 - тактовый вход устройства, 7 - первый элемент ИЛИ, 8 - второй элемент ИЛИ, 9 - третий элемент ИЛИ, 10 - выход "Исправно" устройства, 11 - четвертый элемент ИЛИ, 12j (j=1,5) - группа преобразователей позиционного кода в p-код Фибоначчи, 13j - вход устройства, 14j - группа преобразователей p-кода Фибоначчи в позиционный код, 15j - выход устройства.

Контрольные выходы  информационных и контрольного 1n+1 трактов соединены соответственно с входами блока 2 контроля, выходы группы элементов И 3 соединены с первыми входами группы элементов ИЛИ 4 соответственно, n-выходов блока 2 контроля соединены с соответствующими входами дешифратора 5 и с первыми входами группы элементов И 3 соответственно, вторые входы которых соединены с тактовым входом 6 устройства, выходы группы элементов И 3 соединены с соответствующими входами первого 7 элемента ИЛИ, выход которого соединен с входом пуска контрольного 1n+1 тракта, первая и вторая группы выходов дешифратора 5 соединены соответственно с входами второго 8 и третьего 9 элемента ИЛИ, выходы которых соединены соответственно с выходом 10 "Исправно" устройства и с первым входом четвертого 11 элемента ИЛИ, второй вход которого соединен с (n+1)-м выходом блока 2 контроля, выход четвертого 11 элемента ИЛИ соединен с входом "Останов" контрольного 1n+1 тракта и вторыми входами элементов ИЛИ 4 группы, выходы которых соединены с входами "Останов" соответствующих информационных 1i трактов, выходы группы преобразователей 12j

информационных и контрольного 1n+1 трактов соединены соответственно с входами блока 2 контроля, выходы группы элементов И 3 соединены с первыми входами группы элементов ИЛИ 4 соответственно, n-выходов блока 2 контроля соединены с соответствующими входами дешифратора 5 и с первыми входами группы элементов И 3 соответственно, вторые входы которых соединены с тактовым входом 6 устройства, выходы группы элементов И 3 соединены с соответствующими входами первого 7 элемента ИЛИ, выход которого соединен с входом пуска контрольного 1n+1 тракта, первая и вторая группы выходов дешифратора 5 соединены соответственно с входами второго 8 и третьего 9 элемента ИЛИ, выходы которых соединены соответственно с выходом 10 "Исправно" устройства и с первым входом четвертого 11 элемента ИЛИ, второй вход которого соединен с (n+1)-м выходом блока 2 контроля, выход четвертого 11 элемента ИЛИ соединен с входом "Останов" контрольного 1n+1 тракта и вторыми входами элементов ИЛИ 4 группы, выходы которых соединены с входами "Останов" соответствующих информационных 1i трактов, выходы группы преобразователей 12j позиционного кода в p-код Фибоначчи соединены соответственно с информационными входами информационных 1i и контрольного 1n+1 трактов, а входы являются входом 13j устройства, входы группы преобразователей 14j p-кода Фибоначчи в позиционный код соединены соответственно с выходами информационных 1i и контрольного 1n+1 трактов, а выходы являются выходом 15j устройства, управляющие выходы блока 2 контроля соединены с соответствующими управляющими входами группы преобразователей 12j позиционного p-код Фибоначчи.

позиционного кода в p-код Фибоначчи соединены соответственно с информационными входами информационных 1i и контрольного 1n+1 трактов, а входы являются входом 13j устройства, входы группы преобразователей 14j p-кода Фибоначчи в позиционный код соединены соответственно с выходами информационных 1i и контрольного 1n+1 трактов, а выходы являются выходом 15j устройства, управляющие выходы блока 2 контроля соединены с соответствующими управляющими входами группы преобразователей 12j позиционного p-код Фибоначчи.

Рассмотрим работу устройства. Все основные тракты 11-1n исправны. В этом случае с выхода блока 2 контроля код 000...0 поступает на вход дешифратора 5, с выхода которого сигнал по нулевой шине через элемент ИЛИ 8 поступает на выход 10 "Исправно". Непосредственно сам процесс обработки информации производится в p-коде Фибоначчи. Если неисправно по одному разряду в вычислительных трактах 11-1n+1 (включая и контрольный), то единственным отличием от предыдущего случая является то, что с соответствующих выходов блока 2 контроля поступают сигналы на соответствующие входы управления маскированием группы преобразователей позиционного кода в p-код Фибоначчи с целью маскирования соответствующих разрядов, возможно различных в каждом из вычислительных трактов. Все вычислительные 11-1n+1 тракты, несмотря на неисправность в каждом из них сохраняют полную работоспособность.

В том случае, если произошло несколько различных отказов в одном информационном тракте, то в коде соответствующего 1i тракта на выходе блока 2 контроля будет единица и поступит на вход дешифратора 5, с выхода которого сигнал по соответствующей шине через элемент ИЛИ 8 поступает на выход 10 "Исправно", а сигнал с выхода 6 через соответствующий i-й элемент ИЛИ группы 4 поступает на входы "Останов" соответствующего i-го тракта, через элемент ИЛИ 7 поступает на вход "Пуск" контрольного тракта 1n+1. Таким образом устройство работоспособно и информация обрабатывается всеми трактами, кроме i-го. Подобным образом устройство работает и в том случае, когда полностью отказали несколько трактов (невозможно проведение маскирования, исчерпаны его возможности), но выполняется условие (1) перекрытия.

Если же отказали один или несколько произвольных информационных 1i трактов и контрольный тракт 1n+1, то в этом случае сигнал (n+1)-й выходной шины блока 2 через элемент ИЛИ 11 запрещает работу всех трактов 11-1n+1 устройства. Следует отметить, что под отказом тракта понимается такой случай, когда все возможности маскирования неисправных его разрядов исчерпаны.

Рассмотрим примеры работы устройства при n=4, а система остаточных классов задана информационными основаниями m1=3, m2=4, m3=5, m4=7 и контрольным основанием, равным m5=23.

Пример 1.

Все основные тракты 11-14 работоспособны, но имеется неисправность в каждом из них, включая и контрольный 15, возможности маскирования отказавших разрядов в вычислительных трактах не исчерпаны. В этом случае устройство прототипа полностью неработоспособно. В выхода блока 2 контроля код 0000 поступает на вход дешифратора 5, с которого сигнал по нулевой шине через элемент ИЛИ 8 поступает на выход 10 "Исправен". С соответствующих управляющих выходов блока 2 контроля поступают сигналы на соответствующие входы управления маскированием группы 121-125 преобразователей позиционного кода в p-код Фибоначчи для маскирования соответствующих отказавших разрядов.

Пример 2. Часть информационных трактов неработоспособна, полностью исчерпаны возможности маскирования. Пусть отказали тракты по основаниям m1 и m2, т.е. тракты 11 и 12. С выхода блока 2 код 1100 поступает на вход дешифратора 5, с выхода которого сигнал по двенадцатой шине Элемент ИЛИ 8 поступает на выход 10 "Исправно". Одновременно код 1100 открывает первый и второй элементы И группы 3 (единицы на первой и второй позициях кода 1100) и сигнал с выхода 6 через первый и второй элементы ИЛИ группы 4 поступает на входы "Останов" соответственно первого 11 и второго 12 трактов; через элемент ИЛИ 7 поступает на вход "Пуск" контрольного тракта. Таким образом, устройство работоспособно и информация обрабатывается трактами 13-15 (тракты 11 и 12 отключены). Следует отметить, что в этом случае в трактах 13-15 возможны единичные неисправности, которые устраняются маскированием соответствующих разрядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ N ЧИСЕЛ ПО МОДУЛЮ P | 2000 |

|

RU2188448C2 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1998 |

|

RU2143723C1 |

| СПОСОБ МАГНИТНОЙ ЗАПИСИ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2082222C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ N ЧИСЕЛ ПО МОДУЛЮ | 1997 |

|

RU2131618C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1998 |

|

RU2145112C1 |

| Микропрограммное устройство управления | 1983 |

|

SU1133595A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИТАНИЯ ПО МОДУЛЮ | 1997 |

|

RU2133495C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1999 |

|

RU2156998C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО МОДУЛЮ ОТ ЧИСЛА | 1996 |

|

RU2110147C1 |

| СПОСОБ МАГНИТНОЙ ЗАПИСИ ЦИФРОВОЙ ИНФОРМАЦИИ | 1991 |

|

RU2029383C1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в вычислительных машинах и устройствах, функционирующих в системе остаточных классов. Технический результат заключается в повышении отказоустойчивости устройства. Устройство содержит информационные и контрольной тракты, блок контроля, группу элементов ИЛИ, дешифратор и четыре элемента ИЛИ. Дополнительно устройство снабжено группой преобразователей позиционного кода в p-код Фибоначчи и группой преобразователей p-кода Фибоначчи в позиционный код. Сущность изобретения состоит в использовании маскирования отказавших разрядов в каждом вычислительном тракте, ввиду чего увеличивается количество допустимых отказов устройства при сохранении его полной работоспособности. 1 ил., 1 табл.

Устройство для резервирования, содержащее n информационных (n - количество оснований системы остаточных классов) и один контрольный тракты, блок контроля, группу элементов ИЛИ, дешифратор, четыре элемента ИЛИ, причем контрольные выходы информационных и контрольного трактов соединены соответственно с входами блока контроля, выходы группы элементов И - с первыми входами группы элементов ИЛИ соответственно, n выходов блока контроля соединены с соответствующими входами дешифратора и с первыми входами группы элементов И соответственно, вторые входы которых соединены с тактовым входом устройства, выходы группы элементов И соединены с соответствующими входами первого элемента ИЛИ, выход которого соединен с входом пуска контрольного тракта, первая и вторая группы выходов дешифратора соединены соответственно с входами второго и третьего элементов ИЛИ, выходы которых соединены соответственно с выходом "Исправно" устройства и первым входом четвертого элемента ИЛИ, второй вход которого соединен с (n + 1)-м выходом блока контроля, выход четвертого элемента ИЛИ соединен с входом "Останов" контрольного тракта и вторыми входами элементов ИЛИ группы, выходы которых соединены с входами "Останов" соответствующих информационных трактов, отличающееся тем, что в него введены группа преобразователей позиционного кода в p-код Фибоначчи и группа преобразователей p-кода Фибоначчи в позиционный код,

причем выходы группы преобразователей позиционного кода в p-код Фибоначчи соединены соответственно с информационными входами информационных и контрольного трактов, а входы являются входом устройства, входы группы преобразователей p-кода Фибоначчи в позиционный код соединены соответственно с выходами информационных и контрольного трактов, а выходы являются выходом устройства, управляющие выходы блока контроля соединены с соответствующими управляющими входами группы преобразователей позиционного кода в p-код Фибоначчи.

| Устройство для резервирования | 1983 |

|

SU1168947A1 |

| Резервированное устройство | 1989 |

|

SU1608669A1 |

| Резервированное устройство | 1974 |

|

SU551644A1 |

| Помехоустойчивые коды (Компьютер Фибоначчи) | |||

| Новое в жизни, науке и технике | |||

| Серия: Радиоэлектроника и связь.-М.: Знание, 1989, N 9, с.64. | |||

Авторы

Даты

1998-12-10—Публикация

1997-12-04—Подача