в код номера модуля, группа тригге.ров отказов, второй и третий элемент ИЛИ и одновибратор, причем выход код логических условий, выходы немодифицируем1)1х разрядов адреса и выход микроопераций регистра микрокоманд соединены с входом блока контроля на четность, выход контрольного признака четности регистра микрокоманд соединен с вторым входом блока контроля на четность, выход которого соединен с D-входом первого триггера отказа группы, прямой выход которого соединен с выходом отказа устройства и пербым входом второго элемента ИЛИ выход которого соединен с R-входом триггера пуска, выход регистра адреса соединен с третьим входом блоКа контроля на четность, выход контрольного признака четности регистра адреса соединен с четверть1м входом блока контроля на четность, вход пуск устройства соединен с входом первого элемента ИЛИ, выход блока элементов ИЛИ соединен с группой входов первого элемента ИЛИ. входы

отказа устройства соединены с S-входами соответствующих триггеров отказа группы, начиная со второго, прямые выходы которых соединены с первой группой входов блока элементов И, выходы блока элементов И соединены с первой группой преобра.зователя кода отказа в код номера модуля, выходы регистра команд соединены с второй группой входов преобразователя кода отказа в код номера модуля, вьпсоды которого соединены с второй группой управляющих входов блока коммутаторов и входами третьего элемента ИЛИ, йыходы дешифратора соединены с второй группой входов блока элементов ИЛИ, выход третьего элемента ИЛИ соединен с третьей группой управляющих вхо,дов блока коммутаторов, выход признака конца команды регистра микрокоманд соединен с четвертой группой управляющих входов блока коммутаторо управляющим входом дешифратора и вхо-дом одновибратора,выход которого соеднен с вторым входом второго элемента ИЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный модуль микропрограммного устройства управления | 1984 |

|

SU1273926A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1310818A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1140121A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

| Микропрограммное устройство управления с контролем | 1986 |

|

SU1305679A1 |

| Микропрограммное устройство с контролем | 1984 |

|

SU1208556A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1179338A1 |

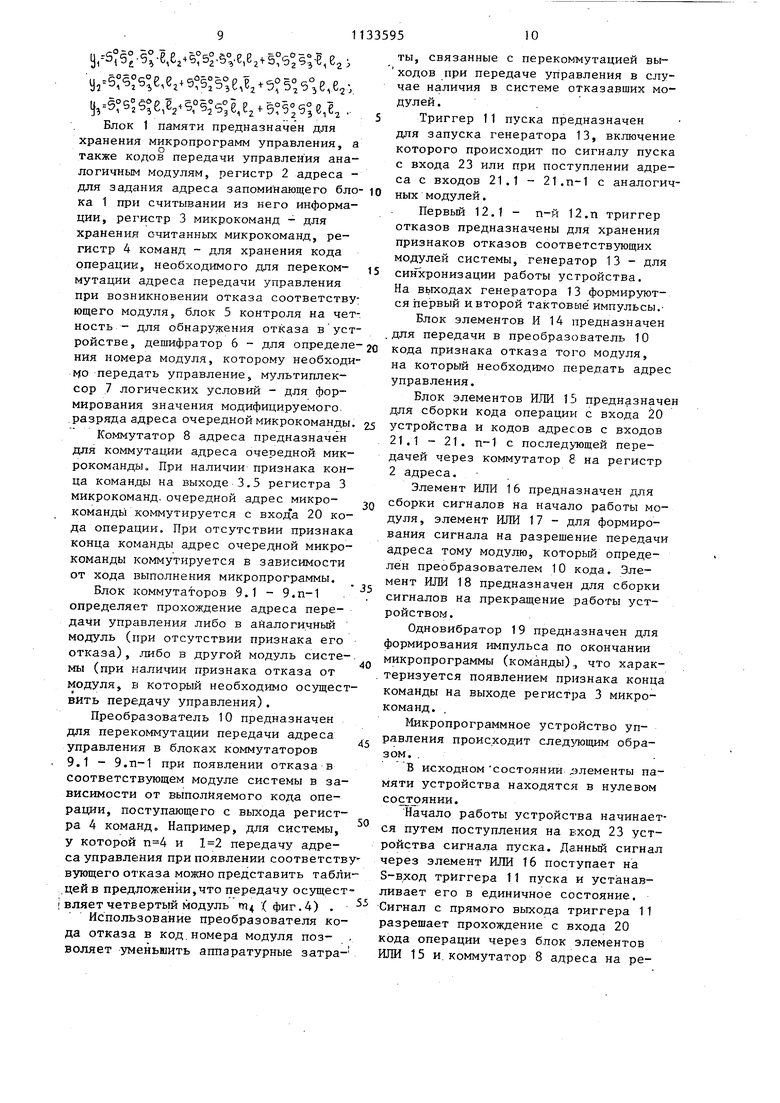

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок памяти, регистр адреса, регистр команд, .регистр микрокоманд, дешифратор, мультиплексор логических условий, коммутатор адреса, триггер пуска, генератор тактовых импульсов, блок коммутаторов, блок элементов И, блок элементов ИЛИ, первый элемент ИЛИ, причем выход коммутатора адреса соединен с информационным входом регистра адреса, выход которого соединен с входом блока памяти, выход блока памяти соединен с информационным входом регистра микрокоманд, выход кода логических условий регистра микрокоманд соединен с управляющим входом мультиплексора логических условий и входом дещифратора, выход модифицируемого разряда адреса регистра микрокоманд соединен с первым информационным входом мультиплексора логических условий, выходы немодифицируемых разрядов адреса регистра микрокоманд соединены с первым информационным входом коммутатора адреса и группой информационных,, входов блока коммутаторов, выход микроопераций регистра микрокоманд является управляющим В1гхбдом устройства, выходы дешифратора соединены с первой группой управляющих входов блока коммутаторов, выходы которых являются информационными выходами устройства, выход мультиплексора логических условий соединен с входом модифицируемого разряда адреса первого информационного входа коммутатора адреса и входами немодифицируемых разрядов адреса адресных входов блока коммутаторов, прямой выход триггера пуска соединен с входом генератора тактовых импульi сов, первый выход которого соединен с входом синхронизации регистра ад(Я С реса и регистра команд, вход логических условий устройства соединен :с вторым 1шформационным входом муль.типлексора логических условийs второй выход генератора тактовых импульсов соединен с входом синхрони1 зации регистра микрокоманд, вход кода операции устройства соединен с оо оо ел со ел информационным Входом регистра команд и входом блока элементов ИЛИ, входы адреса устройства соединены с группой входов блока, элементов , ИЛИ, выход которого соединен с вторым информационным входом коммутатора адреса, прямой.выход триггера пуска соединен с прямым управляющим входом коммутатора адреса, выход конца команды регистра микрокоманд соединен с.инверсным управляющим входом коммутатора адреса, отличающетем, что, с целью расширее с я ния области применения, в устройство введены преобразователь кода отказа

Изобретение относится к автоматик и вычислительной технике и может быть использовано при построении реконфигурируемых управляющих и вычислительных систем с использованием множества однотипных микропрограммных устройств управления.

Известно микропрограммное устройство, содержащее запоминающий блок, регистры, дещйфраторы, блок распределения элементарных операций, элементы И ij .

Недостатком устройства являются

больщие аппаратурные затраты и отсутствие возможности передачи управления аналогичному устройству, что, в свою очередь, ограничивает функциональные возможности устройства,

Известно устройство микропрограммного управления, содержащее счетчий команд,.регистр, дешифратор, матрицу микроопераций , арифметическое устройство, регистр микроопераций 2j

Недостатками устройства являются отсутствие возможности передачи

управления с одного микропрограммного устройства на другое, отсутствие возможности наращивания объема и количества микропрограмм, а также сложность в создании унифицированных блоков микропрограммных устройств и систем управления.

Наиболее близким по технической сущности и достигаемому положительному эффекту к изобретению является микропрограммное устройство управления, которое содержит запоминающий блок, регистр адреса, регистр команд,

регистр микрокоманд, мультиплексор логических условий, коммутатор адреса, триггер пуска, генератор тактовых импульсов, блок коммутаторов, блок элементов И, блок элементов

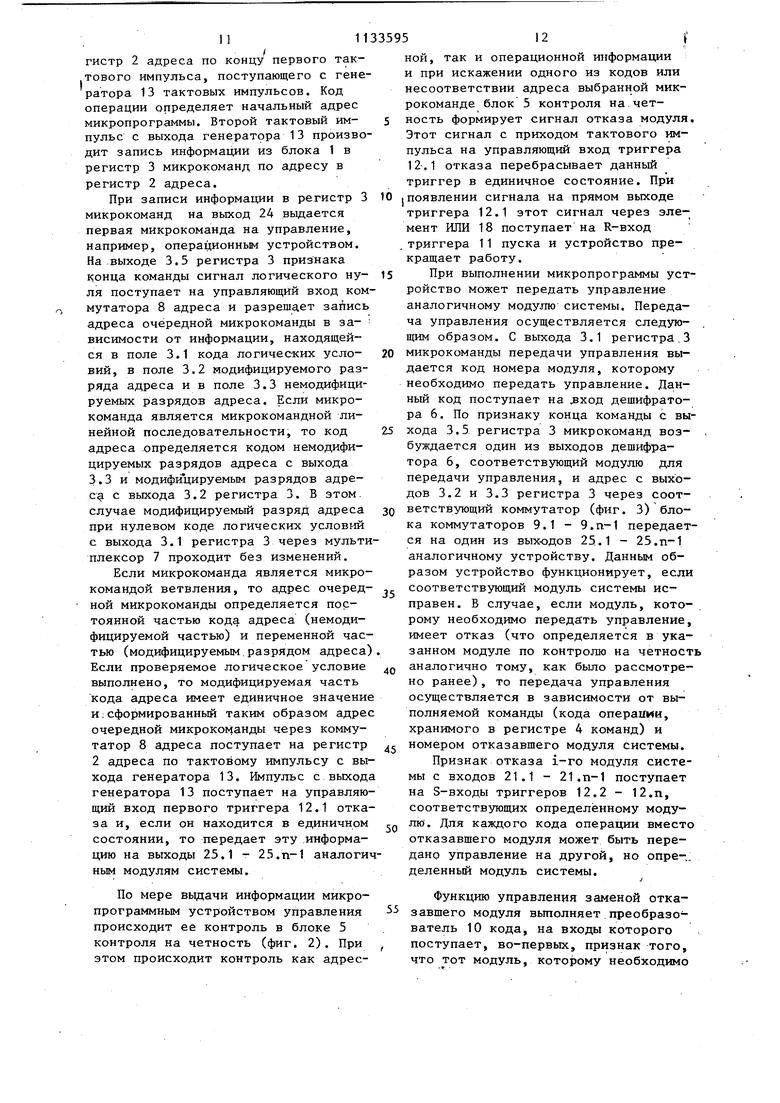

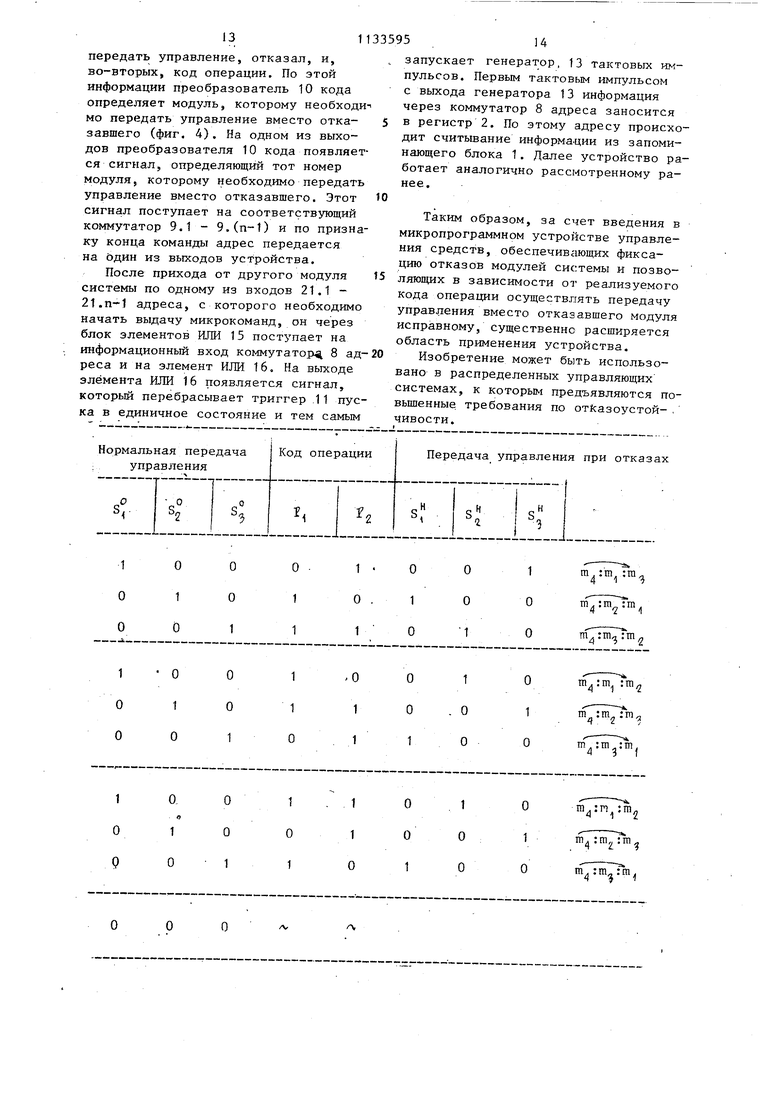

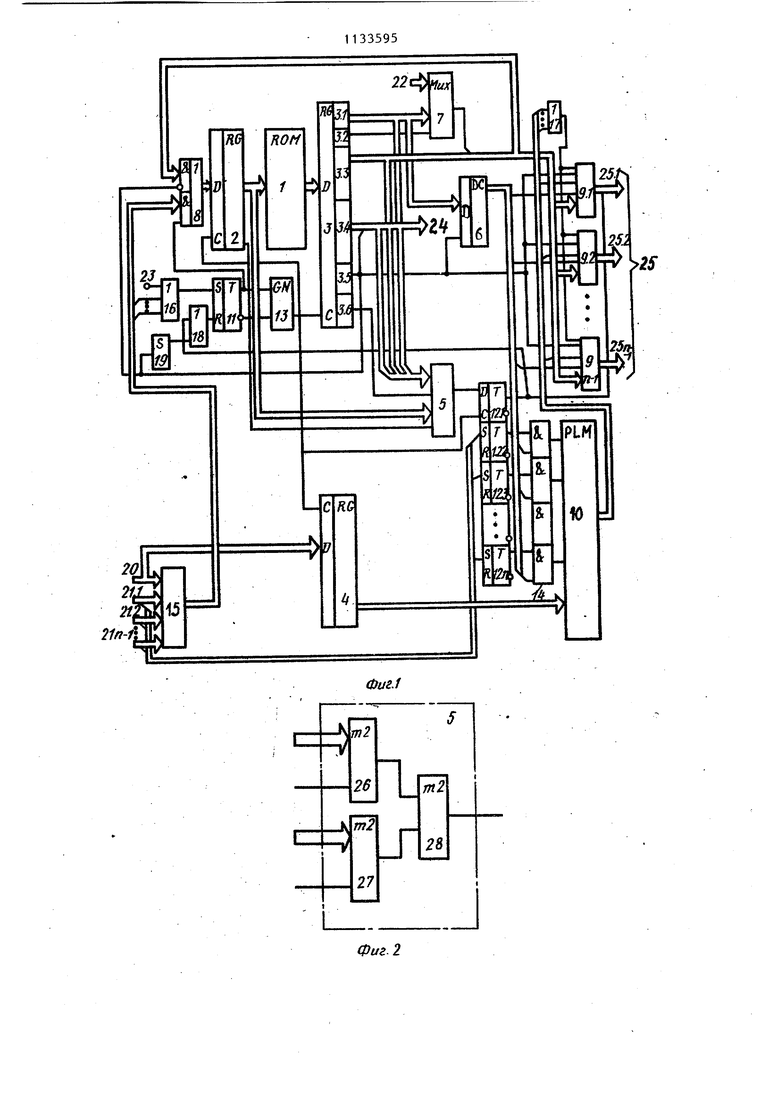

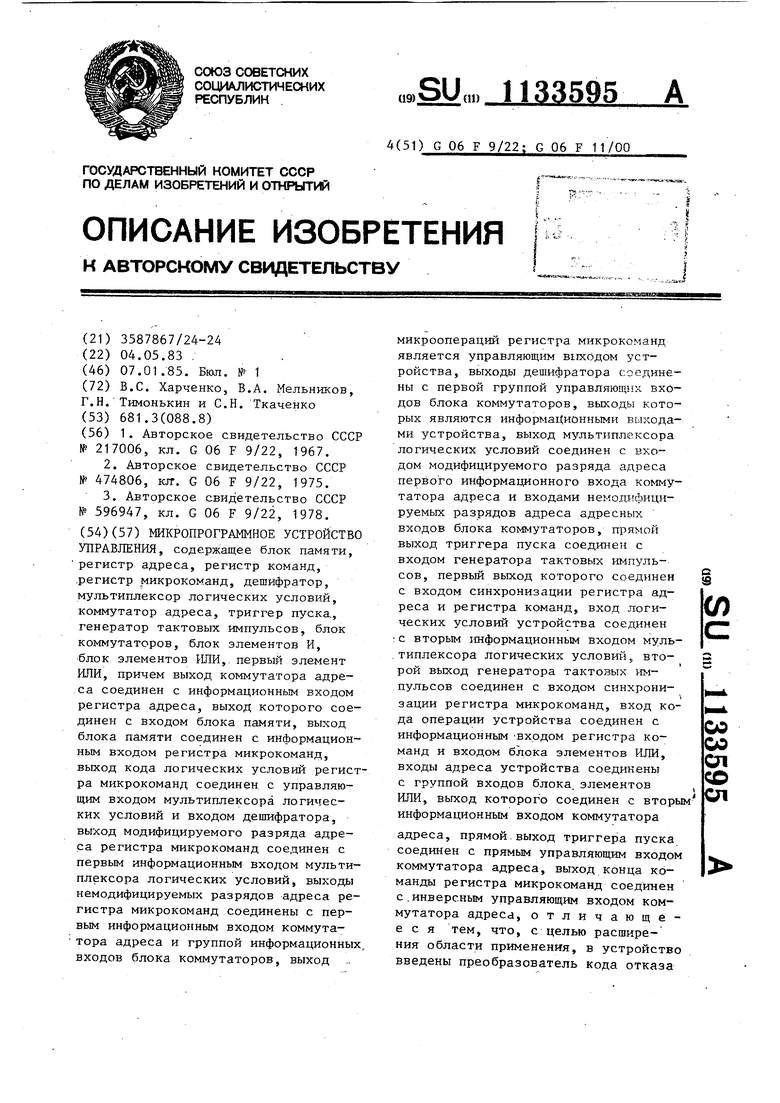

ИЛИ, первьй элемент ИЛИ, причем выход коммутатора адреса соединен с информационным входом регистра адреса, выход которого соединен с входом запоминающего блока, выход кода логических условий запоминающего блока 34 соединен с управляющим входом мульти плексора логических условий и входом дешифратора, выход модифицируемого разряда адреса запоминающего блока соединен с первым информационным входом мультиплексора логических условий, выход немодифицируемых разрядов адреса запоминающего блока сое динен с входами немодифицируемых разрядов адреса первого информационного входа коммутатора адреса и входами немодифицируемых разрядов адреса адресных входов блока коммутаторов, выходы микроопераций запоминающего блока являются первыми выходами устройства,выходы дешифратора соединены с первыми управляющими входами блока коммут.аторов, выходы которых являются адресными выходами вторых выходов устройства, выход мультиплексора логических условий соединен с входом модифицируемого разряда адреса первого информационного входа коммутатора адреса .и входами немодифицируемых разрядов Адреса адресных входов блока коммутаторов, прямой выход триггера пуска соединен t входом генератора тактовых импульсов, первый выход котор го соединен с синхронизирующим входом регистра адреса и синхронизирующим входом регистра команд, вход логических условий устройства соеди нен с вторым информационным входом мультиплексора логических условий, второй выход генератора тактовых импульсов соединен с синхронизирующим входом регистра микрокоманд, вход кода операции устройства соеди нен с информационным входом регистр команд и первым входом блока элемен тов ИЛИ, первый - (п-1)-й входы адреса устройства соединены с вторым п-м входами блока элементов ИЛИ, вы ход которого соединен с вторым информационным входом коммутатора адр са, прямой выход триггера пуска соединен с прямым управляющим входо коммутатора адреса, выход признака конца команды регистра микрокоманд соединен с инверсным управляющим входом коммутатора адреса з . Недостатком известного устройств является узкая область применения, что обусловлено отсутствием средств позволяющих осуществить реконфигура цию системы, построенной из однотип ных микропрограммных устройств упра 54 ления, при отказе одного из этих устройств, а это приводит к отказу всей системы. В модулях распределенных управляющих систем имеется естественная избыточность, обусловленная тем, что часть микропрограммно-аппаратурных ресурсов повторяется в нескольких модулях в целях оптимизации общего времени решения задачи (сокраще :ия числа пересьток), Следовательно, эта избыточность является важньм резервом повьшения отказоустойчивости системы. Однако этот резерв не реализуется, что снижает надежность распределенной управляющей системы в целом и ограничивает область применения устройства классом систем, к которым не предъявляются высокие требования по отказоустойчивости, Друг1- М дополнительным резервом повьшения отказоустойчивости распределенных управляющих систем явлйется тот факт, что при закреплении микропрограмм между модулями, как правило, остается свободной часть микропрограммной памяти. Свободные линейки могут быть использованы для хранения дублей коротких микропрограмм или дпя хранения укороченных микропрограмм, по которым производятся вычисления при отказе основных, что, в свою очередь, может .повысить надежность системы в целом. Однако эта возможность в устройстве также не реализована. Указанные обстоятельства существенно ограничивают область применения известного устройства. Целью изобретения является расширение области применения за счет введения технических средств, позволяющих осзпцествлять реконфигурации программного и аппаратного обеспечения распределенной системы, построенной на унифицированных микропрограммных модулях при возникновении в них отказов. Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее блок памяти, регистр адреса, регистр команд, регистр микрокоманд, дешифратор, мультиплексор логических условий, коммутатор адреса, триггер пуска, генератор тактовых импульсов, блок коммутаторов, блок элементов И, блок элементов ИЛИ, первый элемент ИЛИ, причем выход коммутатора адреса соединен с информационным входом регистра адреса, выход которого сое динен с входом блока памяти, выход блока памяти соединен с информацион ным входом регистра микрокоманд, выход кода логических условий регис ра микрокоманд соединен с управляющ входом иультигшексора логических ус ловий и входом дешифратора, выход модифицируемого разряда адреса реги стра микрокоманд соединен с первым информационным входом мультиплексора логических УСЛОВИЙ, выходы немодифицируемых разрядов адреса регистра микрокоманд соединены с первым и формационным входом коммутатора адр са и группой информационных входов блока коммутаторов, выход микроопер ций регистра микрокоманд является управляющим выходом устройства, выходы дешифратора соединены с первой группой управляющих входов блока ком мутаторов, выходы которых являются информационными выходами устройства выход мультиплексора логических условий соединен с входом модифицируемого разряда адреса первого информационного входа коммутатора адреса и входами, немодифицируемых разрядов адреса адресных входов блока коммутаторов, прямой выход триггера пуска соединен с входом генератора тактовых импульсов, первьй выход которо ГО- соединен с входом синхронизации регистра адреса и регистра команд, вход логических условий устройства соединен с вторым информационным входом мультиплексора логических условий, втьрой выход генератора так товых импульсов соединен с входом синхронизации регистра микрокоманд, вход кода операции устройства соединен с информационным входом регистра команд и входом блока элементов ИЛИ, в-ходы адреса устройства соединены с группой входов блока элементов ИЛИ, выход которого соединен с вторым информационным входом коммутатора адреса, прямой выход триггера пуска соединен с прямым управляющим входом,коммутатора адреса, выход конца команды регистра микрокоманд соединен с инверсным управляющим входом коммутатора адреса, дополнительно введены преобразователь кода отказа в код номера модуля, блок контроля на четность, группа тригге956ров отказов, второй и третий элементы ИЛИ и одновибратор, причем выход кода логических условий, выходы немодифицируемых разрядов адреса и выход микроопераций регистра микрокоманд соединены с первым входом блока контроля на четность, выход контрольного признака четности регистра микрокоманд соединен с вторым входом блока контроля на четность, выход которого соединен с Ь-входом первого триггера отказа группы,прямой выход которого соединен с выходом отказа устройства и первым входом второго элемента РШИ, выход которого соединен с R-входом триггера пуска, выход регистра адреса соединен с третьим входом блока контроля на четность, выход контрольного признака четности регистра адреса соединен с четвертым входом блока контроля на четность, вход пуска устройства соединен с входом первого элемента ИЛИ, выход блока элементов ИЛИ соединен с группой входов первого элемента ИЛИ, входы отказа устройства соединены с S-входами Соответствующих триггеров отказа группы, начиная с второго, прямые выходы которых соединены с первой группой входов блока элементов И, выходы блока элементов И соединены с первой группой входов преобразователя кода отказа в код номера модуля, выходы регистра команд соединены с второй группой входов преобразователя кода отказа в код номера модуля, выходы которого соединены с второй группой управляющих входов блока коммутаторов и входами третьего элемента ИЛИ,, выходы дешифратора соединены с второй группой блока элементов ИЛИ, выход третьего элемента- ИЛИ соединен с третьей группой управляющих входов блока коммутаторов, выход признака конца команды регистра микрокоманд соединен с четвертой группой управляющих входов блока коммутаторов, управляющим входом дешифратора и входом одновибратора, выход которого соединен с вторым входом второго элемента ИЛИ. Сущность изобретения заключается в расширении области применения путем введения средств, обеспечивающих передачу управления устройству, в котором хранится полная или усеченная копия микропрограммы отказавше7113го устройства. Возможность передачи управления при отказе устройства аналогичному микропрограммному устройству позволяет повысить отказоустойчивость системы, построенной на основе однотипных устройств.. Повышение отказоустойчивости достигается путем контроля отдельных устройств системы и осуществлений ее реконфигурации в случае отказа на основе использования естественной избыточности, обусловленной, во-пераппаратных ресурсов повторяется в нескольких модулях в целях оптимизации общего времени решения задачи (сокращения числа пересылок) и, вовторых, тем, что при закреплении микропрограмм между модулями остается свободной часть микропрограммной памяти. Свободное пространство памяти используется для хранения дублей коротких микропрограмм или для хранения укороченных микропрограмм, по которым производятся вычисления при отказе основных микропрограм мных устройств управления. Введение -узла контроля на четност позволяет осуществлять контроль устройства и формировать признак отказа с целью последующего исключения отказавшего устройства из работы системы. Введение первого - п-го триггеров отказа (где п - количество модулей в системе) позволяет хранить информацию об отказавших модулях системы. Введение преобразователя кода отказа в код номера модуля необходимо для перекоммутации передачи управления в зависимости от выполняемой команды на один из исправных модулей системы. Введение второго элемента ИЛИ необходимо для сборки сигналов на обнуление триггера пуска при окончани работы модуля или его отказе. Ввдение третьего элемента ИЛИ не обходимо для формирования сигнала о том, что модуль, на который должн быть осуществлена передача управления, подлежит замене. Введение одновибратора необходим для формирования импульса на обнуле ние триггера пуска после выполнения микропрограммы. На фиг, 1 представлена функциональная схема микропрограммного устройства управления; на фиг. 2 - функциональная схема узла контроля на четность; на фиг. 3 - функциональная схема коммутатора блока коммутаторов; на фиг. 4 - функциональная схема преобразователя кода отказа в код номера модуля для и , где п - количество модулей в системе, 1 - количество кодов операций. Микропрограммное устройство управления (фиг. 1) содержит блок 1 памяти, регистр 2 адреса, регистр 3 микрокоманд с полями;3.1 - кода логических условий, 3.2 - модифицируемого разряда адреса, 3.3 - немодифицируемых разрядов адреса, 3.4 - кода микроопераций, 3.5 - признака конца команды, 3.6 - контрольного признака четности; регистр 4 команд, блок 5 контроля на, четность, дешифратор 6, мультиплексор 7 логических условий, коммутатор 8 адреса, блок коммутаторов 9.1 - 9(п-1), преобразователь 10 кода отказа в код номера модуля, триггер 1 пуска, первый 12.1 - (п-й) 12.Т1 триггеры отказов, генератор 13 тактовых импульсов, блок 14 элементов И, блок 15 элементов ИЛИ, первый элемент ИЛИ 16, третий элемент ИЛИ 17, второй элемент ИЛИ 18, одновибратор 19, входы 20 кода операции, входы 21.1 - 21 (п-1) адреса, вход 22 логических условий, вход 23 пуска, управлянщие 24 и 25 и информационные 25.2 - 25 (п-1) выходы устройства. Блок 5 контроля на четность (фиг. 2) содержит первый- 26 и второй 27 блоки элементов суммы по модулю два, элемент 28 суммы по модулю два. Коммутатор 9.1 (, п-1) блока коммутаторов 9.1 - 9.п-1 (фиг. 3) содержит элемент 2И- ИЛИ 29.1 и блок элементов И 30.1. Преобразователь кода отказа в код номера модуля (фиг. 4).для , где п - число модулей в системе, и (1 - число команд) содержит блок элементов НЕ 31.1 - 31.5, два блока сопротивлений и соответственно первую 32 и вторую 33 матрицы. Sj - сигнал с 1-го Элемента (, п-1)И блока элементов И 14, 1 - сигнал кода операции с регистра 4 команд. На выходе преобразователя 10 для рассматриваемого примера формируются логические функции ij,5t5°5°-e,e,.s°.e,e,.5°6°5;-e,e2i у,5:5°5°е,е,.5 5°5°еЛ-5°5°5°ел-. II -aocOqOp ё +Ц°Ч°с;р P 4.ё,°с.о а° р Блок 1 памяти предназначен для хранения микропрограмм управления, а также кодов передачи управления аналогичным модулям, регистр 2 адреса для задания адреса запоминающего бло ка 1 при считывании из него информации, регистр 3 микрокоманд - для хранения считанных микрокоманд, регистр 4 команд для хранения кода операции, необходимого для перекоммутации адреса передачи управления при возникновении отказа соответству ющего модуля, блок 5 контроля на чет ность - для обнаружения отказа в уст ройстве, дешифратор 6 - для определе ния номера модуля, которому необходи bfo передать управление, мультиплексор 7 логических условий - для формирования значения модифицируемого, .разряда адреса очередной микрокоманды Коммутатор 8 адреса предназначен для коммутации адреса очередной микрокоманды При наличии признака конца коман,цы на выходе 3.5 регистра 3 микрокоманд, очередной адрес микрокоманды коммутируется с входа 20 кода операции. При отсутствии признака конца команды адрес очередной микрокоманды коммутируется в зависимости от хода выполнения микропрограммы. Блок коммутаторов 9.1 - 9.П-1 определяет прохождение адреса передачи управления либо в айалогичный модуль (при отсутствии признака его отказа), либо в другой модуль системы (при наличии признака отказа от модуля, в который необходимо осущест вить передачу управления). Преобразователь 10 предназначен для перекоммутации передачи адреса управления в блоках коммутаторов 9.1 - 9.П-1 при появлении отказа в соответствующем модуле системы в зависимости от выполняемого кода операции, поступающего с выхода регистра 4 команд„ Например, для системы, у которой и передачу адреса управления при появлении соответств вующего отказа можно представить табли .цейв предложении,что передачу I вляет четвертый модуль ni4 (фиг. 4) . Использование преобразователя кода отказа в код.номера модуля позволяет уменьшить аппаратурные затраты, связанные с перекоммутацией выходов при передаче управления в случае наличия в системе отказавших модулей . Триггер 11 пуска предназначен для запуска генератора 13, включение которого происходит по сигналу пуска с входа 23 или при поступлении адреса с входов 21.1 - 21.П-1 с аналогичных модулей. Первьй 12.1 - п-й 12.П триггер отказов предназначены для хранения признаков отказов соответствующих модулей системы, генератор 13 - для синосронизации работы устройства. На вьтходах генератора 13 формируются первый ивторой тактовые импульсы.Блок элементов И 14 предназначен для передачи в преобразователь 10 кода признака отказа того модуля, на который необходимо передать адрес управления. Блок элементов ИЖ 15 предназначен для сборки кода операции с входа 20 устройства и кодов адресов с входов 21,1 - 21. п-1 с последующей передачей через коммутатор 8 на регистр 2 адреса. Элемент ИЛИ 16 предназначен для сборки сигналов на начало работы модуля, элемент ИЛИ 17 - для формирования сигнала на разрешение передачи адреса тому модулю, который определен преобразователем 10 кода. Элемент ИЖ 18 предназначен для сборки сигналов на прекращение работы устройством. Одновибратор 19 предназначен для формирования импульса по окончании микропрограммы (команды),, что характеризуется появлением признака конца команды на выходе регистра 3 микрокоманд. Микропрограммное устройство управления происходит следзтощим образом. . В исходномСОСТОЯНИИ ; лементы памяти устройства находятся в нулевом состоянии. Начало работы устройства начинается путем поступления на Е:ХОД 23 устройства сигнала пуска. Данный сигнал через элемент ИЛИ 16 поступает на S-вход триггера 11 пуска и устанавливает его в единичное состояние. Сигнал с прямого выхода триггера 11 разрешает прохождение с входа 20 кода операции через б.пок элементов ИЛИ 15 и. коммутатор 8 адреса на регистр 2 адреса по концу первого тактового импульса, поступающего с генератора 13 тактовых импульсов. Код операции определяет начальный адрес микропрограммы. Второй тактовый импульс с выхода генератора 13 произво дит запись информации из блока 1 в регистр 3 микрокоманд по адресу в регистр 2 адреса. При записи информации в регистр 3 микрокоманд на выход 24 вьздается первая микрокоманда на управление, например, операционным устройством. На .выходе 3.5 регистра 3 признака конца команды сигнал логического нуля поступает на управляющий вход ком мутатора 8 адреса и разрешает запись адреса очередной микрокоманды в зависимости от информации, находящейся в поле 3,1 кода логических уелоВИЙ, в поле 3.2 модифицируемого разряда адреса и в поле 3,3 немодифицируемых разрядов адреса. Если микрокоманда является микрокомандной линейной последовательности, то код адреса .определяется кодом немодифицируемых разрядов адреса с выхода 3.3 и модифицируемым разрядов адресу с выхода 3.2 регистра 3, В этом, случае модифицируемый разряд адреса при нулевом коде логических условий с выхода 3.1 регистра 3 через мульти плексор 7 проходит без изменений. Если микрокоманда является микрокомандой ветвления, то адрес очередной микрокоманды определяется постоянной частью кода адреса (немодифицируемой частью) и переменной частью (модифицируемым.разрядом адреса Если проверяемое логическое условие выполнено, то модифицируемая часть кода адреса имеет единичное значени и;сформированный таким образом адре очередной микрокоманды через коммутатор 8 адреса поступает на регистр 2 адреса по тактовому импульсу с вы хода генератора 13. Импульс с выход генератора 13 поступает на управляю щий вход первого триггера 12.1 отка за и, если он находится в единичном состоянии, то передает эту .информацию на выходы 25,1 - 25.П-1 аналоги ным модулям системы. По мере вьщачи информации микропрограммным устройством управления происходит ее контроль в блоке 5 контроля на четность (фиг, 2), При этом происходит контроль как адресной, так и операционной информации и при искажении одного из кодов или несоответствии адреса выбранной микрокоманде блок 5 контроля на четность формирует сигнал отказа модуля. Этот сигнал с приходом тактового импульса на управляющий вход триггера 12.1 отказа перебрасывает данный триггер в единичное состояние. При появлении сигнала на прямом выходе триггера 12.1 этот сигнал через элемент ИЛИ 18 поступает на R-вход триггера 11 пуска и устройство прекращает работу. При выполнении микропрограммы устройство может передать управление аналогичному модулю системы. Передача управления осуществляется следующим образом, С выхода 3.1 регистра.3 микрокоманды передачи управления выдается код номера модуля, которому необходимо передать управление. Данный код поступает на ход дешифратора 6. По признаку конца команды с выхода 3.5 регистра 3 микрокоманд воз- , буждается один из выходов дешифратора 6, соответствующий модулю для передачи управления, и адрес с выходов 3.2 и 3.3 регистра 3 через соответствующий коммутатор (фиг. 3) блока коммутаторов 9.1 - 9.п-1 передается на один из выхчэдов 25.1 - 25,п-1 аналогичному устройству. Данным образом устройство функционирует, если соответствующий модуль системы исправен. В случае, если модуль, которому необходимо переда:ть управление, имеет отказ (что определяется в указанном модуле по контролю на четность аналогично тому, как было рассмотрено ранее), то передача управления осуществляется в зависимости от выполняемой команды (кода операции, хранимого в регистре 4 команд) и номером отказавшего модуля системы. Признак отказа i-го модуля системы с входов 21.1 - 21.П-1 поступает на S-входы триггеров 12.2 - 12,п, соответствзгющих определённому модулю. Для каждого кода операции вместо отказавшего модуля может быть передано управление на другой, но опре-,: деленный модуль системы. Функцию управления заменой отказавшего модуля вьтолняет.преобразователь 10 кода, на входы которого поступает, во-первых, признак того, что тот модуль, которому необходимо

передать управление, отказал, и, во-вторых, код операции. По этой информации преобразователь 10 кода определяет модуль, которому необходиМО передать управление вместо отказавшего (фиг. 4). На одном из выходов преобразователя 10 кода появляется сигнал, определяющий тот номер модуля, которому необходимо передать управление вместо отказавшего. Этот сигнал поступает на соответствующий коммутатор 9.1 - 9.(п-1) и по признаку конца команды адрес передается на Ьдин из вь ходов устройства.

После прихода от другого модуля системы по одному из входов 21.1 - 21.П адреса, с которого необходимо начать выдачу микрокоманд, он через блок элементов ИЛИ 15 поступает на информационный вход коммутатору 8 адреса и на элемент ИЛИ 16. На выходе элемента ИЛИ 16 появляется сигнал, который перебрасывает триггер 11 пуска в единичное состояние и тем самым

запускает генератор, 13 тактовых импульсов. Первым тактовым импульсом с выхода генератора 13 информация через коммутатор 8 адреса заносится в регистр 2. По этому адресу происходит считывание информации из запоминающего блока 1. Лалее устройство работает аналогично рассмотренному ранее.

Таким образом, за счет введения в микропрограммном устройстве управления средств, обеспечивающих фиксацию отказов модулей системы и позволяющих в зависимости от реализуемого кода операции осуществлять передачу управления вместо отказавшего модуля исправному, существенно расширяется область применения устройства.

Изобретение может быть использовано в распределенных управляющих системах, к которым предъявляются повышенные требования по от1 :азоустой- , чивости.

Т|

т2

J

28

Фиг. 2

шт

&

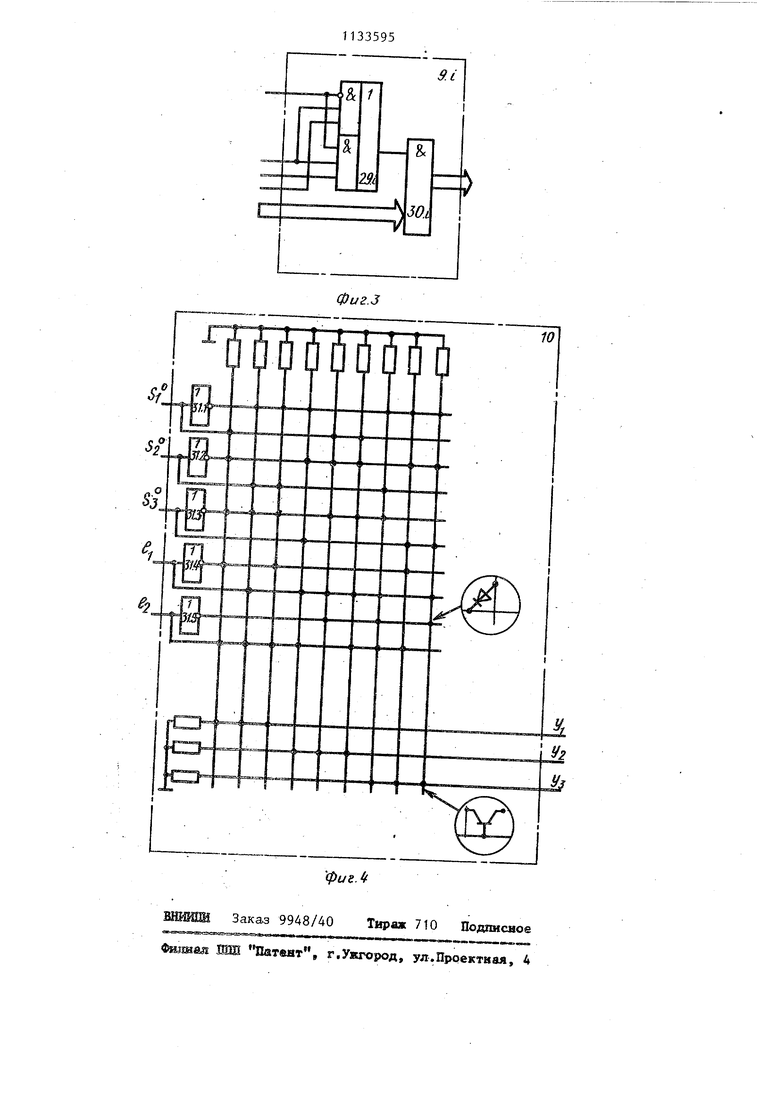

фиг.З

10

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| РАЗДЕЛЬНО-СОВМЕЩЕННАЯ ИСКАТЕЛЬНАЯ ГОЛОВКА | 0 |

|

SU217006A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-07—Публикация

1983-05-04—Подача