(54) РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО

держкой, что приводит к появлению ложного СкГГнала на Быходе устройства в течение времени задержки.

Наиболее близким к изобретению является разервированное устройство, которое со- держит в каждом из основных каналов резервируемый блок, блок контроля, блок подключения резерва и управляемый переключатель первый информационный вход которого соединен с выходом данного резервируемого блока, а первый управляющий вход - с первым управляющим выходом блока подключения резерва, управляющий вход которого соединен с выходом блока контроля.

Однако при резервировании блоков, формируюших аналоговые сигналы, возможности его ограничены. Так, например, при резервировании блоков питания использование на его выходах восстанавливающих органов представляет значительные трудности, что обусловлено появлением дополнительных падений напряжений в выходных элементах; неполностью использованы структурные возможности для повышения надежности, поскольку устройство сохраняет работоспособность только при двух оставшихся исправных резервируемых блоках и не сохраняет при одном исправном блоке.

Цель изобретения - расширение области применения и повышение надежности устройства.

Достигается это благодаря тому, что предлагаемое устройство содержит дополнительный резервируемый блок, выход которого соединен с вторыми информационными входами управляемых переключателей, выход каждого из которых соединен с выходом данного канала и с одним из двух дополнительных информационных входов блока контроля в смежных каналах, а второй управлякяций выход блока подключения резерва в каждом кавале соединен с вторым управляющим входом управляемого переключателя Б данном канале.

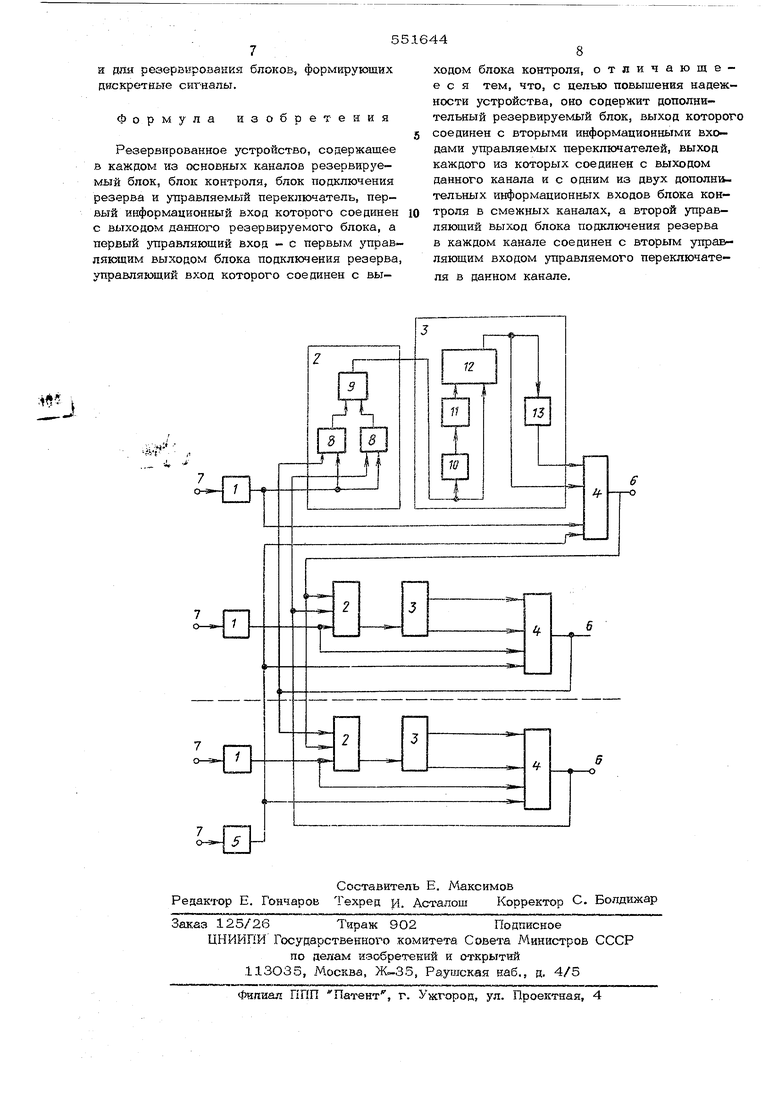

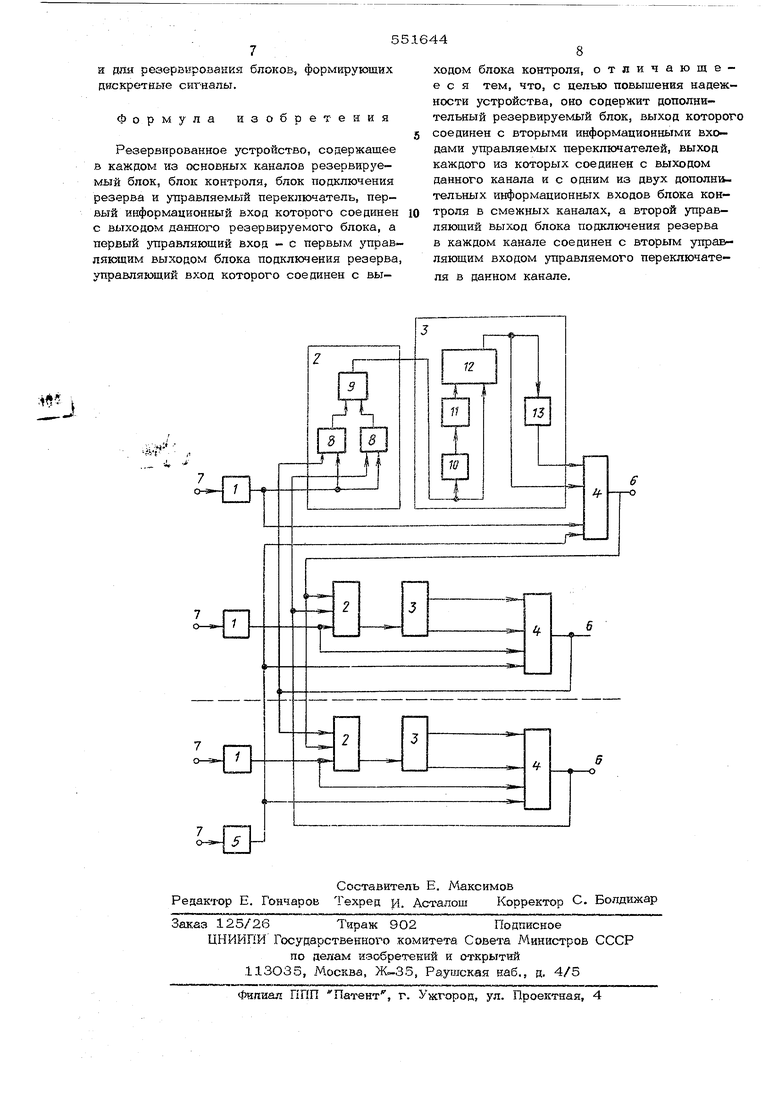

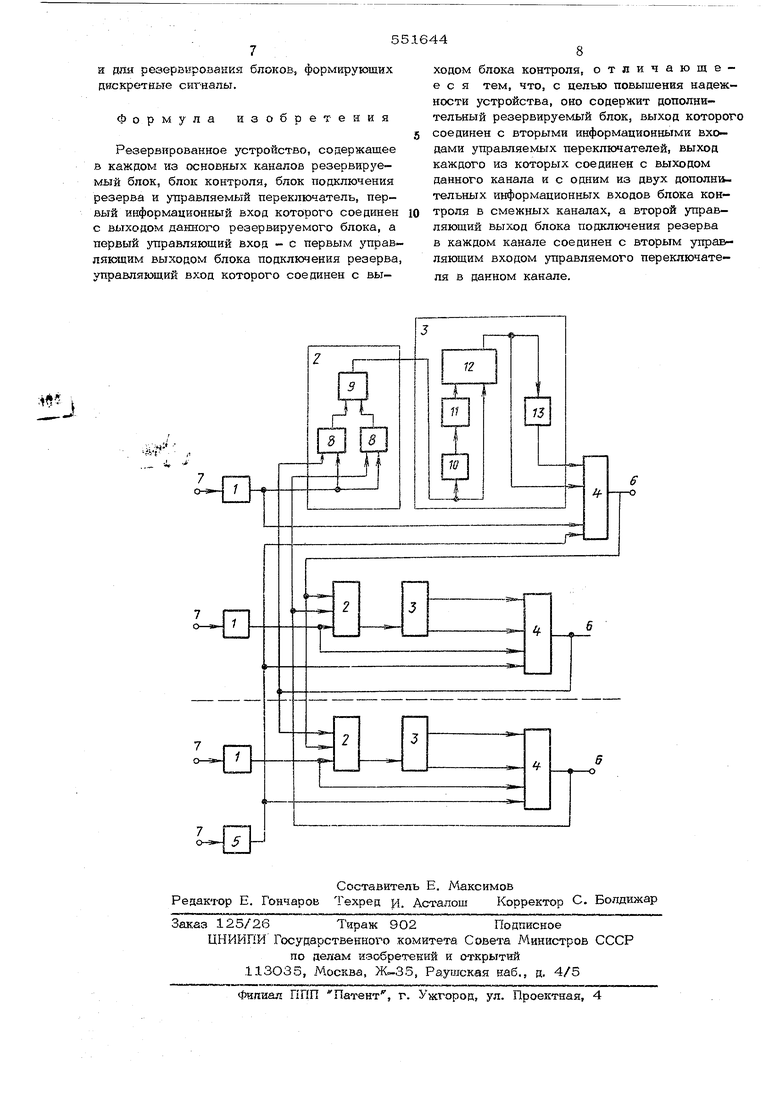

На чертеже изображена блок-схема ре- зервирозанного устройства.

Устройство содержит в каждом из основных каналов резервируемый блок 1, блок контроля 2, блок подключения резерва 3 и управляемый переключатель 4, кроме того, устройство содержит дополнительный резер-. вируемый блок 5.

Выход резервируемого блока 1 в каждом из осконых каналов соединен с первым информациоквым входом блока контроля 2 и с первы 1 информационным входом упрагляемого переключателя 4.

Выход блока контроля 2 соединен с управляющим входом блока подключения резерва 3, первый и второй управляющие выХоды которого соединены соответственно с первым и вторым управляющими входами управляемого переключателя 4.

Второй информационный вход управляемого переключателя 4 в каждом из основных каналов соединен с выходом дополнительного резервируемого блока 5, а выход управляемого переключателя 4 соединен с выходом 6 данного канала и с одним из двух информационных входов блока контроля 2 в смежных каналах. Выходами предлагаемого устройства являются выходы 6 управляемых переключателей 4, а входами входы 7 резервируемых блоков 1, 5.

Блок контроля 2 в каждом канале содержит два элемента сравнения 8 и элемент И 9, входы которого соединены с выходами обеих схем сравнения.

Блок подключения резерва 3 в каждом из основных каналов содержит последовательно соединенные элемент задержки 1О и первый инвертор 11, выход которого соединен с нулевым входом элемента памяти 12. Кроме того, блок подключения резерва 3 содержит второй инвертор 13, соединенный с единичным выходом элемента памяти 12.

Устройство работает следующим образом. При включении устройства элемент памяти 12 в блоке подключения резерва 3 каждого канала удерживается в состоянии О сигналом, поступающим с выхода блока контроля 2 на управляющий вход блока подключения резерва 3.

Управляющий сигнал с единичного выхода элемента памяти 12 поступает на первый управляющий вход управляемого переключателя 4, а с выхода инвертора 13 - на второй управляющий вход этого переключателя. Тем самым разрешается при правильной работе резервируемых блоков 1 в основных каналах поступления напряжения с выхода резервуемого блока 1 в каждом из основных каналов на выход б устройства и запрещается поступление напряжения с выхода дополнительного блока 5.

Отказ какого-либо резервируемого блока 1 или кратковременное отклонение напряжения на его выходе обнаруживается с помощью

блока контроля 2. При этом на выходе блока контроля 2 в данном канале формируется управляющий сигнал, который устанавливает в состояние 1 элемент памяти 12.

Управляющий сигнал с единичного выхода элемента памяти 12 поступает на первый управляющий вход управляемого переключателя 4, а после инвертирования - на второй управляющий вход этого переключателя. При этом запрещается поступление напряжения с выхода блока 1 в отказавшем какале на выход 6 устройства и разрешается поступлени напряжения с выхода дополнительного блока Если обшее число каналов в устройстве равно, например , 4, то устройство сохраняет правильные напряжения на двух выходах 6 при отказе резервируемого блока 1 в одном из основных каналов и дополнительного резервируемого блока 5. Если же дополнительный резервируемый блок 5 исправен и по нагрузке рассчитан для работы на гри выхода 6 устройства, то правильные напряжения сохраняются на всех выходах 6 устройства при последовательных отказах трех резервируемых блоков 1. В этом случае устройство продолжает работать при одном оставшемся исправном резервируемом блоке 5. Если элемент памяти 12 срабатывает вследствие кратковременного снятия напряжения на выходе какого-либо резервируемого блока 1, а не вследствие его окончатель ного отказа, то при формировании этим блоком нормального напряжения, отключенный канал вновь включается в схему устройства Происходит это следуюшим образом.; при восстановлении нормального значения напряжения на выходе ранее отказавшего резервируемого блока 1 управляющий сигнал на выходе блока контроля 2 снимается, и элемент памяти 12 в этом канале возвращается в исходное состояние. Тем самым разрешается прохождение напряжения с выхода блока 1 на выход 6 устройства и запрещается поступление напряжения с выхода дополнительного резервируемого блока 5. Измерение напряжений в блоке контроля 2 осуществляется с помощью элемента сравнения 8, сигналы с выхода которого поступают на входы элемента И 9. Каждый из элементов сравнения 8, может быть рассчитан, например для контроля верхнего и нижнего уровня напряжения, при этом в качестве эталонного используется напряжение, поступающее из соседнего канала. Для дискретных сигналов потенциального типа требуется только определение факта наличия или отсутствия сигнала, в связи с этим элемент сравнения 8 может быть выполнен в виде схемы неравнозначности. При отказе блока 1 на выходе обоих элементов сравнения S, а следовательно, и на выходе элемен та И 9 формируется сигнал, поступающий на выход блока контроля 2 для установки элемента памяти 12 в единичное состояние. За тем с задержкой, формируемой элементом задержки 10, снимается сигнал на выходе инвертора 11, и элемент памяти 12 продол жает удерживаться в состоянии i сигнал с выхода блока контооля 2. Если же установка элемента памяти 12 произошла вследствие кратковременного отказа резервируемого блока 1, то при восстановлении работоспособности блока снг- нал с единичного входа элемента памяти 12 снимается, и с задержкой, формируемой элементом 10, появляется сигнал на к л&вом входе элемента памяти 12 для его установки в нулевое состояние. Элемент задержки 10, который может быть выполнен, например, в виде интегрирующей RC - цепочки, исключает формирование на нулевом входе элемента памяти 12 ложных сигналов, обусловленных кратковременным сня- тием напряжений, поступающих яз соседних каналов на входы элементов сравнения 8, при отключении отказавшего канала и под-ключении дополнительного резервируемого блока 5. Время задержки этого элемента должно превышать время сравнения сигналов в элементах 8 и время переключения элементов 9 - 13 и 4, Использование элемента памяти 12 цля переключения на резерв позволяет обеспечить минимальную задержку при подключении блока 5 вместо любого отказави1его и в то же время с помощью элемента задержки 10 исключить ложное включение в схему устройства, ранее отказавшего резервируемого блока 1 при последующих переключениях в устройстве. При этом время задержки элемента 10 не сказывается на времени подключения резервируемого блока 5 вместо любого отказавшего блока 1, тем самым уменьшаются пульсации сигнала на выходах 6 устройства. Управляемый переключатель 4 может быть выполнен, например, в вида двух элементов И, соединенных по схеме ИЛИ. При этом управляющими входами данного переключателя являются, например, первые входы элементов И, а информационными - вторые входы элементов И. Для устранения пульсаций на выходе элемента ИЛИ может быть установлен фильтр для исключения пульсаций на выходах б устройства. Таким образом, в предложенном устройстве сохраняется работоспособность при одном исправном резервируемом блоке 5. Кроме того, в предложенном устройстве возможно сохранение работоспособности устройства как при последовательных отказах резервируемых блоков 1, так; п при одновременном отказе двух или трех этих блоков в основных каналах. Предложенное устройство может быть использовано как для резервирования бло-ков, формирующих анайого&ые сигнальт, так

а для резервирования блоков, формирующих дискретные сигналы.

Формула изобретения

Резервированное устройство, содержащее в кaждo г из основных каналов резервируемый блок, блок контроля, блок подключения резерва и управляемый переключатель, первый информационный вход которого соединен с выходом данного резервируемого блока, а первый управляющий вход - с первым управляющим выходом блока подключения резерва, управляющий вход которого соединен с вы-

ходом блока контроля, отличающееся тем, что, с целью повышения надежности устройства, оно содержит дополнительный резервируемый блок, выход которого соединен с вторыми информационными входами управляемых переключателей, выход каждого из которых соединен с выходом данного канала и с одним из двух дополн1ьтельных информационных входов блока контроля в смежных каналах, а второй управляющий выход блока подключения резерва в каждом канале соединен с вторым управляющим входом управляемого переключателя в данном канале.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное резервированное устройство | 1974 |

|

SU550638A1 |

| Резервированное устройство | 1980 |

|

SU928685A1 |

| Резервированное устройство | 1978 |

|

SU805319A2 |

| Резервированное многокаскадное устройство | 1981 |

|

SU1069203A1 |

| Резервированная вычислительная система | 1990 |

|

SU1755400A1 |

| Устройство для управления реконфигурацией резервированного вычислительного комплекса | 1983 |

|

SU1149449A1 |

| Резервированное устройство | 1982 |

|

SU1102068A1 |

| Резервированное устройство | 1981 |

|

SU982006A1 |

| Устройство для регулирования температуры | 1978 |

|

SU841128A1 |

| Адаптивное резервированное устройство | 1981 |

|

SU962959A1 |

:i

Авторы

Даты

1977-03-25—Публикация

1974-09-09—Подача