Изобретение относится к области радиотехники, а именно к области контроля технического состояния аппаратуры связи, в частности заявленное устройство диагностики состояния аппаратуры связи предназначено для повышения достоверности диагностирования аппаратуры связи, работающей в симплексном режиме, не находящейся на связи.

Известны устройства диагностирования - см. изобретение "Устройство для контроля работоспособности радиоприемника". (51)4 H 04 B 17/00, опубликованное 22.02.90, выпуск N 134; изобретение "Автоматизированная система контроля" (51)5 H 04 B 17/00 // H 04 B 3/46, опубликованное 30.06.94, бюллетень N 12. Они содержат устройства формирования тестовой псевдослучайной последовательности (ПСП), устройство сравнения тестовых последовательностей, счетчик ошибок. Данные устройства позволяют диагностировать системы связи по коэффициенту ошибки.

Общим недостатком аналогов является низкая достоверность диагностирования аппаратуры связи, работающей в симплексном режиме, так как при контроле симплексной аппаратуры связи необходимо использовать вторую дополнительную аппаратуры связи, а это снижает достоверность диагностирования из-за неопределенности, вносимой второй дополнительной аппаратурой связи.

Из известных устройств наиболее близким к заявленному устройству (прототипом) по своей технической сущности является устройство диагностики на основе измерения коэффициента ошибок, описанное в изобретении "Устройство диагностики состояния аппаратуры цифровых систем передачи" (51)5 H 04 B 3/46, опубликованное 15.05.92, бюллетень N 018. Устройство-прототип состоит из контролируемой аппаратуры связи, генератора псевдослучайной последовательности, линии задержки, блока регистрации ошибок, блока подсчета ошибок, блока коммутации соединений, блока управляющих сигналов, генератора шума, аттенюатора.

При этом выход генератора псевдослучайной последовательности подключен к первому входу линии задержки и второму входу блока коммутации соединений, первый выход и четвертый вход которого подключены к соответствующим входу и выходу тракта передачи, третьей выход блока коммутации соединений подключен к входу аттенюатора, выход которого и выход генератора шума подключены к первому входу блока коммутации соединений, четвертый выход и третьей вход которого подключены соответственно к входу и выходу тракта приема, группа выходов блока управляющих сигналов подключена к группе входов блока коммутации соединений, второй выход которого подключен ко второму входу блока регистрации ошибок, выход которого подключен к входу блока подсчета ошибок, выход линии задержки подключен к третьему входу блока регистрации ошибок.

Это устройство является оптимальным, по сравнению с аналогами, так как диагностируя аппаратуру связи по коэффициенту ошибок при прохождении контрольного теста псевдослучайной последовательности через контролируемую аппаратуру, повышается достоверность и уменьшаются временные затраты за счет изменения соотношения сигнал/шум.

Однако, данное устройство не обеспечивает достаточную достоверность диагностирования, так как при проверке тракта передачи контролируемой аппаратуры связи в качестве приемного тракта необходимо использовать тракт приема второй аппаратуры связи, а при проверке приемного тракта контролируемой аппаратуры связи в качестве передающего тракта необходимо использовать тракт передачи второй аппаратуры связи.

Целью настоящего изобретения является разработка устройства диагностики состояния аппаратуры связи, обеспечивающего повышение достоверности диагностирования состояния аппаратуры связи, работающей в симплексном режиме.

Поставленная цель достигается тем, что известно устройство диагностики на основе измерения коэффициента ошибок, содержащее генератор псевдослучайной последовательности, линию задержки, блок регистрации ошибок, блок подсчета ошибок, блок управляющих сигналов, блок коммутации соединений, аттенюатор, генератор шума. При этом выход генератора псевдослучайной последовательности подключен к линии задержки, выход которой подключен к входу блока регистрации ошибок. Выход блока регистрации ошибок подключен к входу блока подсчета ошибок. Первый выход блока управляющих сигналов подключен к управляющему входу блока коммутации соединений, к выходу которого подключен аттенюатор, а к входу - генератор шума. Дополнительно введены следующие элементы: блок согласования, управляемый делитель, первый и второй полосовые фильтры, цифроаналоговый и аналого-цифровой преобразователи, запоминающий блок. При этом выход и вход блока согласования являются низкочастотными выходом и входом устройства. Выход аттенюатора подключен к входу второго полосового фильтра, выход которого подключен к входу аналого-цифрового преобразователя. Выход аналого-цифрового преобразователя подключен к входу запоминающего блока, выход которого подключен к входу цифроаналогового преобразователя. Выход цифроаналогового преобразователя подключен к входу первого полосового фильтра, выход которого подключен к информационному входу управляемого делителя, выход которого подключен к входу блока коммутации соединений. Выход переключение и высокочастотный вход/выход которого являются выходами и входом устройства. Второй, третий, четвертый, пятый, шестой и седьмой выходы блока управляющих сигналов подключены соответственно к управляющим входам блока согласования, управляемого делителя, цифро-аналогового преобразователя, запоминающего устройства, аналого-цифрового преобразователя. Шина данных от блока управляющих сигналов подключена к входам данных генератора псевдослучайной последовательности, блока регистрации ошибок, блока согласования, блока коммутации соединений, управляемого делителя.

Блок коммутации соединений состоит из D-триггера, транзистора, реле, делителя мощности. При этом высокочастотный вход/выход подключен к первому контакту первой группы контактов реле и к входу делителя мощности. Выход делителя мощности подключен к первому контакту второй группы контактов реле. Второй контакт второй группы контактов реле является выходом блока. Второй контакт первой группы контактов реле является входом рассматриваемого блока. Третья группа контактов реле одним контактом подключена к выходу переключения блока, а другим контактом - к корпусу. Шина данных подключена к информационному входу D-триггера. Вход синхронизации которого является управляющим входом блока. Выход D-триггера подключен к базе транзистора. Эмиттер которого подключен к корпусу, а коллектор подключен к управляющей обмотке реле. Второй конец которой подключен к питающему напряжению.

Блок согласования состоит из сдвоенного усилителя-формирователя, D-триггера, элемента ИЛИ-НЕ, первого и второго преобразователя уровня. При этом низкочастотный вход блока подключен к входу второго преобразователя уровня. Выход которого подключен к входу элемента ИЛИ-НЕ. Выход которого подключен к информационному входу сдвоенного усилителя-формирователя. К входу данных которого подключена шина данных устройства. К сдвоенному усилителю-формирователю подключены вход управления передачей и вход управления приемом рассматриваемого блока. Вход управления передачей параллельно подключен к входу синхронизации D-триггера. Информационный вход которого подключен к информационному выходу сдвоенного усилителя-формирователя. Выход D-триггера подключен к входу первого преобразователя уровня. Выход которого является низкочастотным выходом блока.

Управляемый делитель состоит из буферного усилителя-формирователя, параллельного регистра, цифроаналогового преобразователя, усилителя радиочастоты с системой автоматической регулировки усиления. При этом вход и выход усилителя радиочастоты являются соответственно информационным входом и информационным выходом управляемого делителя. Шина данных устройства подключена к входам буферного усилителя-формирователя. Выходы которого подключены к входам параллельного регистра. Выходы которого подключены к входам цифроаналогового преобразователя. Выход которого подключен к входу системы автоматической регулировки усиления усилителя радиочастоты. Управляющий вход рассматриваемого блока подключен к входу синхронизации параллельного регистра и входу разрешения буферного усилителя-формирователя.

Предлагаемое устройство позволяет определять техническое состояние аппаратуры связи, работающей в симплексном режиме. За счет того, что были введены новые блоки (управляемый делитель, цифроаналоговый и аналого-цифровой преобразователи, запоминающий блок), появилась возможность запоминания тестовой псевдослучайной последовательности, прошедшей по тракту передачи контролируемой аппаратуры связи, на время передачи всей последовательности. После окончания передачи прием последовательности по тракту приема и сравнения с исходной для определения технического состояния по коэффициенту ошибок. При этом повышается достоверность диагностирования за счет исключения второй (дополнительной) аппаратуры связи.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественными всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного изобретения условию патентоспособности "новизна".

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

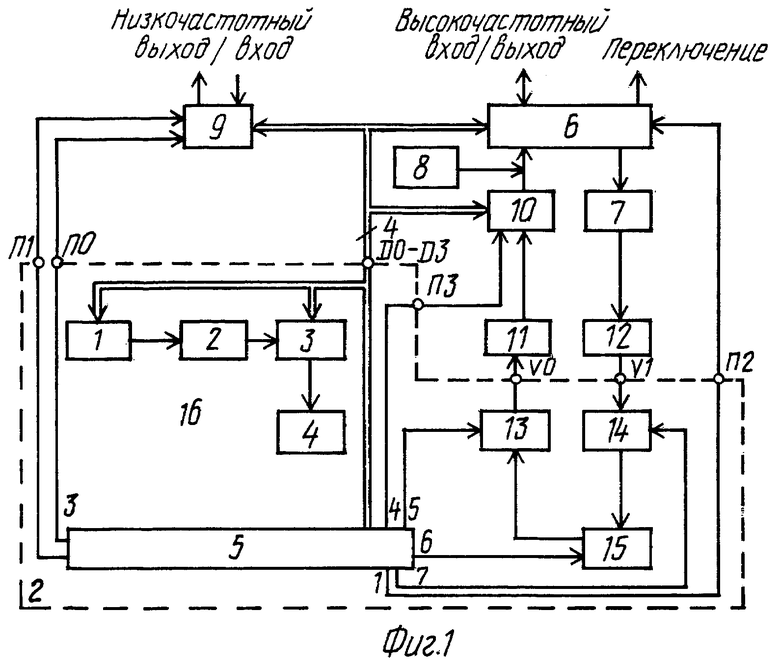

Заявленное устройство поясняется чертежами, на которых показаны:

- фиг. 1 - структурная схема заявленного устройства диагностики состояния аппаратуры связи;

- фиг. 2 - структурная схема блока коммутации соединений;

- фиг. 3 - структурная схема блока согласования;

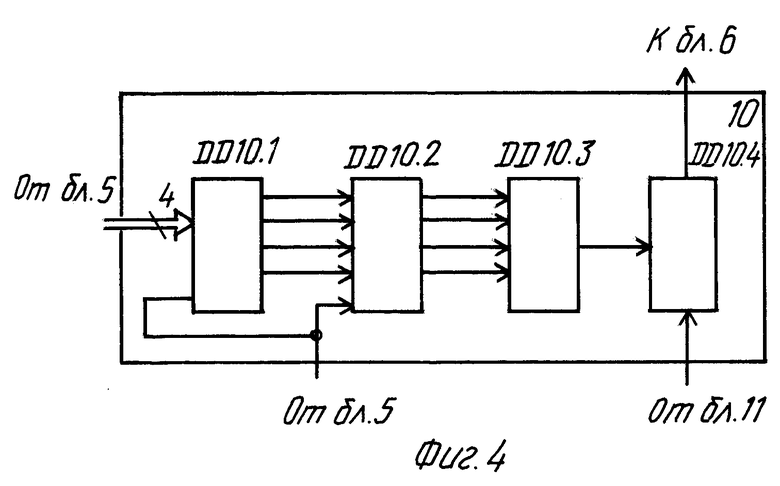

- фиг. 4 - структурная схема управляемого делителя;

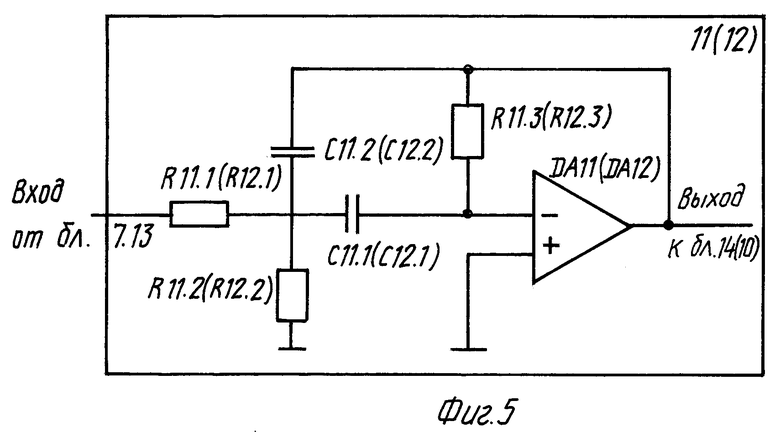

- фиг. 5 - структурная схема полосового фильтра;

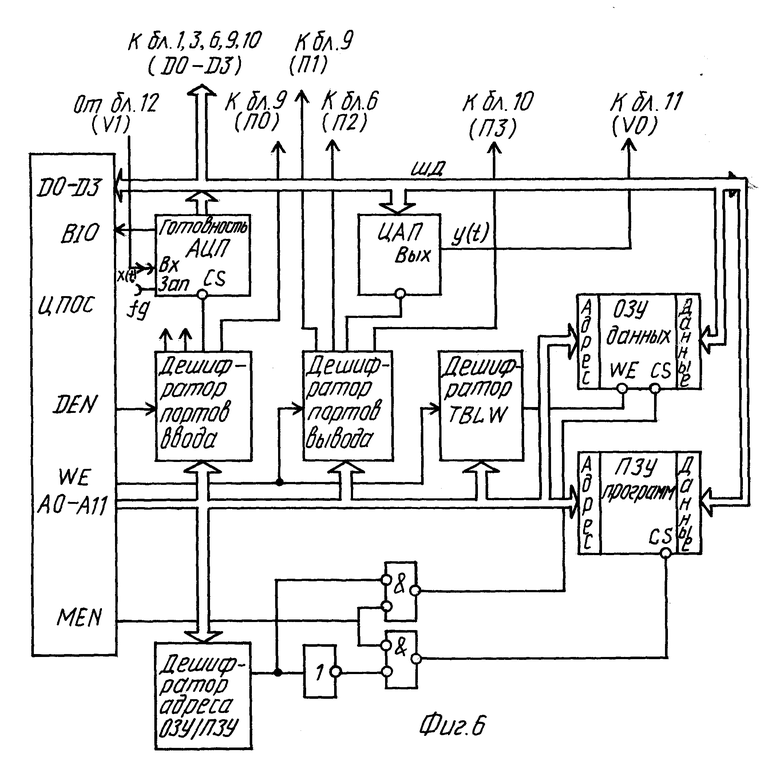

- фиг. 6 - структурная схема системы цифровой обработки сигналов;

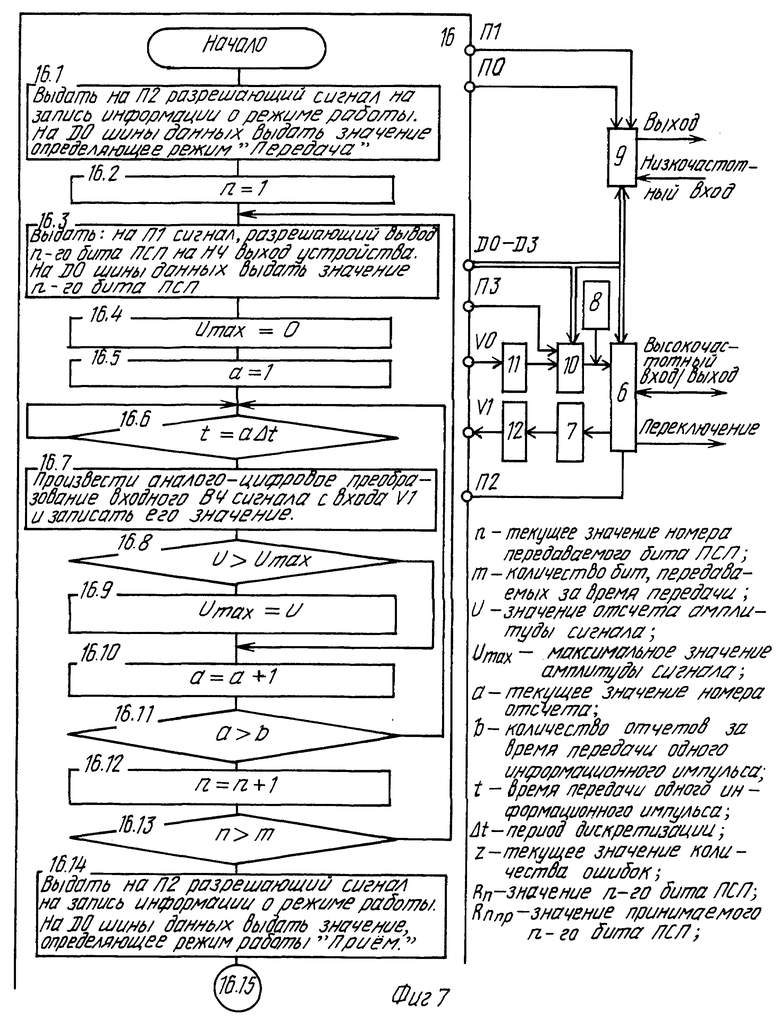

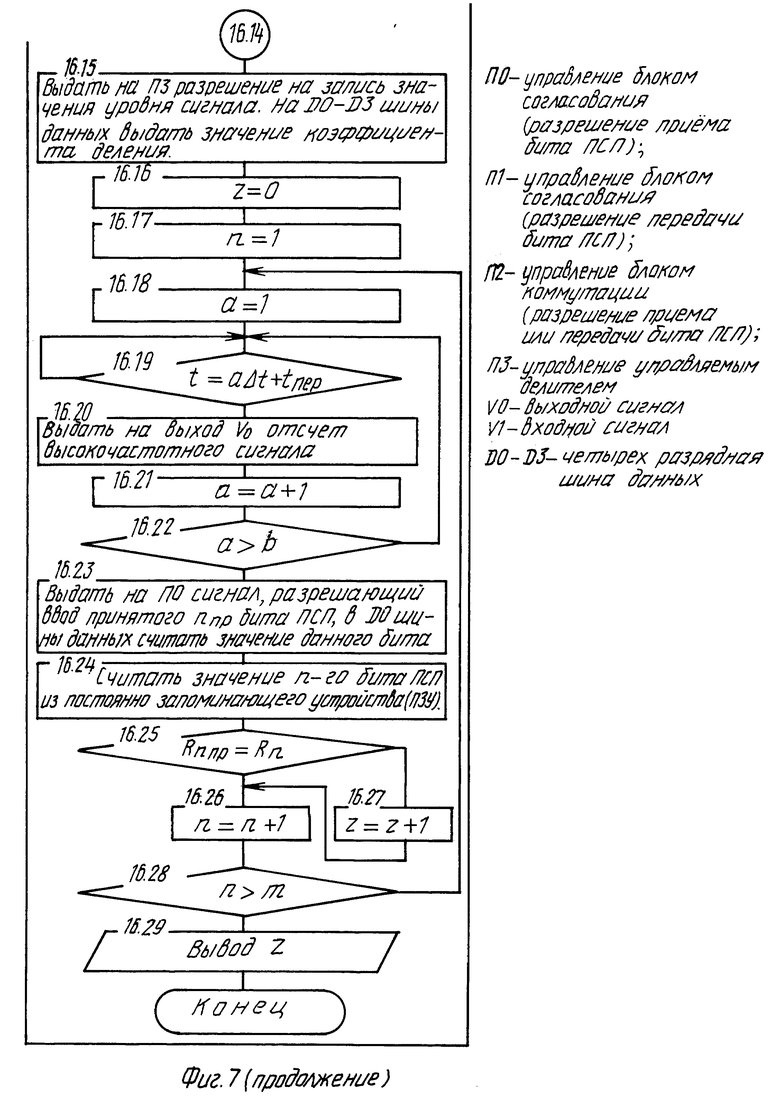

- фиг. 7 - алгоритм работы системы цифровой обработки сигналов;

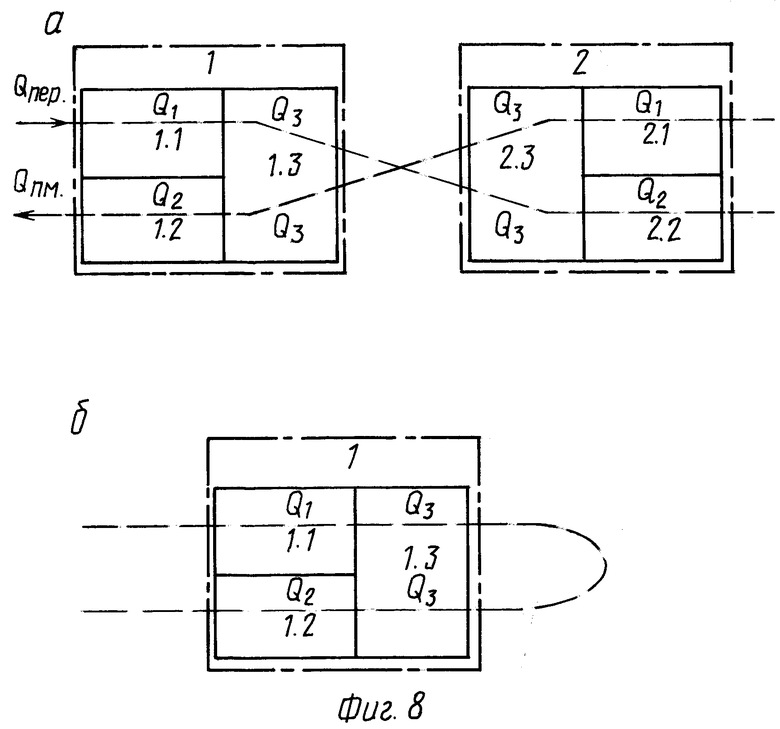

- фиг. 8 - оценка эффективности заявленного устройства.

Устройство диагностики состояния аппаратуры связи, показанное на фиг.1, состоит из генератора псевдослучайной последовательности 1, линии задержки 2, блока регистрации ошибок 3, блока подсчета ошибок 4, блока управляющих сигналов 5, блока коммутации соединений 6, аттенюатора 7, генератора шума 8, блока согласования 9, управляемого делителя 10, первого 11 и второго 12 полосовых фильтров, цифроаналогового 13 и аналого-цифрового 14 преобразователей, запоминающего блока 15. Выход генератора псевдослучайной последовательности 1 подключен к линии задержки 2, выход которой подключен к входу блока регистрации ошибок 3. Выход которого подключен к входу блока подсчета ошибок 4. Первый выход блока управляющих сигналов 5 подключен к управляющему входу блока коммутации соединений 6. К выходу блока коммутации соединений 6 подключен аттенюатор 7, а к входу -генератор шума 8. Выход и вход блока согласования 9 являются низкочастотными выходом и входом заявляемого устройства. Выход аттенюатора 7 подключен к входу второго полосового фильтра 12, выход которого подключен к входу аналого-цифрового преобразователя 14. Выход аналого-цифрового преобразователя 14 подключен к входу запоминающего блока 15, выход которого подключен к входу цифроаналогового преобразователя 13. Выход цифроаналогового преобразователя 13 подключен к входу первого полосового фильтра 11, выход которого подключен к информационному входу управляемого делителя 10. Информационный выход управляемого делителя 10 подключен к входу блока коммутации соединений 6, выход переключение и высокочастотный вход/выход которого являются соответственно выходами и входом устройства. Второй, третий, четвертый, пятый, шестой и седьмой выходы блока управляющих сигналов 5 подключены соответственно к управляющим входам блока согласования 9, управляемого делителя 10, цифроаналогового преобразователя 13, запоминающего устройства 15, аналого-цифрового преобразователя 14. Шина данных от блока управляющих сигналов 5 подключена к входам данных генератора псевдослучайной последовательности 1, блока регистрации ошибок 3, блока коммутации соединений 6, блока согласования 9, управляемого делителя 10.

Блок коммутации соединений 6, показанный на фиг. 2, состоит из D-триггера D6, транзистора VT6, реле Р6, делителя мощности (напряжения) R6.1, R6.2. Высокочастотный вход/выход заявляемого устройства подключен к первому контакту первой группы контактов реле Р6 и к входу делителя мощности R6.1, R6.2. Выход которого подключен к первому контакту второй группы контактов реле Р6. Второй контакт второй группы контактов реле Р6 является выходом блока к Бл.7, а второй контакт первой группы контактов является входом блока от Бл.8, Бл.10. Третья группа контактов реле Р6 одним контактом подключена к выходу переключение устройства, а другим контактом - к корпусу. Вход шины данных от Бл. 5 подключен к информационному входу D-триггера D6 (вход D). Вход синхронизации (вход C) D-триггера D6 от Бл.5 является управляющим входом блока коммутации соединений 6. Выход D-триггера D6 подключен к базе транзистора VT6, эмиттер которого подключен к корпусу, а коллектор подключен к управляющей обмотке реле Р6. Второй конец обмотки реле Р6 подключен к питающему напряжению Uпит.

Блок коммутации соединений предназначен:

а) для подключения высокочастотного входа/выхода устройства к входу аттенюатора при работе на передачу или к выходам управляемого делителя и генератора шума при работе на прием;

б) для переключения контролируемой аппаратуры из режима прием в режим передача и обратно.

D-триггер D6 предназначен для сохранения бита информации, определяющего режим работы устройства (режим передачи или приема) на время прохождения контрольного теста. Транзистор VT6 предназначен для подключения питающего напряжения к управляющей обмотке реле. Делитель мощности R6.1, R6.2 предназначен для уменьшения уровня высокочастотного сигнала при работе контролируемой аппаратуры на передачу до величины, обеспечивающей нормальную работу реле.

Блок коммутации соединений 6, показанный на фиг. 2, может быть реализован на следующей элементной базе:

D-триггер D6 - схема построения известна, в частном случае может быть реализован на микросхеме типа ТМ, см.: Цифровые интегральные микросхемы: Справочник. / М.И. Богданов, И.Н. Грель, В.А. Прохоренко, В.В. Шалимо. - Мн. Беларусь, 1991. - стр. 104-112 (рис. 2.46);

транзистор VT6 - известный элемент, работает в режиме ключа, может быть реализован на транзисторе (как показано на фиг. 2) или на микросхеме типа КН (КТ). Выбираются с учетом коммутируемого тока, напряжения и времени переключения, см.: Справочник разработчика и конструктора РЭА./ М.Ю. Масленников, Е. А. Соболев, Л.Ф. Соловейчик и др. - М.: ТОО Прибор, 1993, книга 2, стр. 247-275; см.: Цифровые и аналоговые интегральные микросхемы: Справочник./С. В. Якубовский, Л. Н. Ниссельсон, В.И. Кулешова и др. - М.: Радио и связь, 1989. - стр. 447-455;

реле Р6 - схема построения известна, выбирается с учетом режима коммутации, частоты коммутируемого сигнала, см.: Справочник разработчика и конструктора РЭА. / М.Ю. Масленников, Е.А. Соболев, Л.Ф. Соловейчик и др. - М.: ТОО Прибор, 1993, книга 1, стр. 36-46;

делитель мощности (напряжения) R6.1 и R6.2 - схема построения известна, в частном случае может быть реализован на резисторах с учетом мощности сигнала подаваемого на его вход, см.: Справочник разработчика и конструктора РЭА. / М.Ю. Масленников, Е.А. Соболев, Л.Ф. Соловейчик и др. - М.: ТОО Прибор, 1993, книга 2, стр. 219-223.

Блок согласования 9, показанный на фиг. 3, состоит из сдвоенного усилителя-формирователя DD9.1, D-триггера D9.2, элемента ИЛИ-НЕ D9.3, первого D9.4 и второго D9.5 преобразователей уровня. Низкочастотный вход заявляемого устройства является низкочастотным входом блока согласования 9 и подключен к входу второго D9.5 преобразователя уровня. Выход второго D9.5 преобразователя уровня подключен к входу элемента ИЛИ-НЕ D9.3, выход которого подключен к информационному входу Bо сдвоенного усилителя-формирователя DD9.1. К входу данных Wo сдвоенного усилителя-формирователя DD9.1 подключена шина данных от Бл. 5 заявляемого устройства. К управляющим входам СА и СВ сдвоенного усилителя-формирователя DD9.1 подключены вход управления передачей от Бл.5 и вход управления приемом от Бл.5. Вход управления передачей от Бл.5 параллельно подключен к входу синхронизации (вход C) D-триггера D9.2, информационный вход D которого подключен к информационному выходу АО сдвоенного усилителя-формирователя DD9.1. Выход D-триггера D9.2 подключен к входу первого D9.4 преобразователя уровня, выход которого является низкочастотным выходом блока и заявляемого устройства.

Блок согласования 9 предназначен для согласования шины данных с низкочастотным выходом и входом контролируемой аппаратуры связи.

Сдвоенный усилитель-формирователь DD9.1 предназначен для формирования и усиления цифровых сигналов при взаимодействии устройства согласования с шиной данных системы цифровой обработки сигнала. D-триггер D9.2 предназначен для сохранения значения бита, передаваемой информации, в течение времени передачи одного информационного импульса. Элемент ИЛИ-НЕ D9.3 предназначен для инверсии сигнала, который необходим из-за подключения низкочастотного входа блока к инверсному входу сдвоенного усилителя-формирователя. Преобразователи уровня D9.4, D9.5 предназначены для согласования по уровню устройства диагностики состояния аппаратуры связи с низкочастотным входом и выходом контролируемой аппаратуры, если их элементная база различна. Если низкочастотные вход и выход контролируемой аппаратуры имеют уровень транзисторно-транзисторной логики, то преобразователи уровня в блоке согласования не нужны.

Блок согласования 9 (см. фиг.3) может быть реализован на следующей элементной базе:

сдвоенный усилитель-формирователь DD9.1 - буферный элемент, схема построения известна, в частности может быть реализован на микросхеме типа АП, см. : Цифровые интегральные микросхемы: Справочник./ М.И. Богданов, И.Н. Грель, В. А. Прохоренко, В.В. Шалимо. - Мн. Беларусь, 1991. - стр. 125-130 (рис. 2.59);

D-триггер D9.2 - схема построения известна, в частном случае может быть реализован на микросхеме типа ТМ, см.: Цифровые интегральные микросхемы: Справочник. / М.И. Богданов, И.Н. Грель, В.А. Прохоренко, В.В. Шалимо. - Мн. Беларусь, 1991. - стр. 104-112 (рис. 2.46);

элемент ИЛИ-НЕ D9.3 - микросхема типа ЛЕ, см.: Цифровые интегральные микросхемы: Справочник. / М. И. Богданов, И.Н. Грель, В.А. Прохоренко, В.В. Шалимо. - Мн. Беларусь, 1991. - стр. 60-66 (рис. 2.15);

первый D9.4 и второй D9.5 преобразователи уровня - схема построения известна, выбираются в зависимости от вида электрического согласования, в частном случае могут быть реализованы на микросхемах типа ПУ, см.: Цифровые интегральные микросхемы: Справочник./ М.И. Богданов, И.Н. Грель, В.А. Прохоренко, В.В. Шалимо. - Мн. Беларусь, 1991. - стр. 362-366 (рис. 3.88).

Управляемый делитель 10, представленный на фиг. 4, состоит из буферного усилителя-формирователя DD10.1, параллельного регистра DD10.2, цифроаналогового преобразователя DD10.3, усилителя радиочастоты DD10.4 с системой автоматической регулировки усиления. Вход и выход усилителя радиочастоты DD10.4 являются соответственно информационным входом от Бл.11 и информационным выходом к Бл. 6 блока. Шина данных от Бл.5 подключена к входам буферного усилителя-формирователя DD10.1, выходы которого подключены к входам параллельного регистра DD10.2. Выходы параллельного регистра DD10.2 подключены к входам цифроаналогового преобразователя DD10.3, выход которого подключен к входу системы автоматической регулировки усиления усилителя радиочастоты DD10.4. Управляющий вход от Бл.5 блока подключен к входу разрешения буферного усилителя-формирователя DD10.1 и к входу синхронизации параллельного регистра DD10.2.

Управляемый делитель 10 предназначен для установки уровня радиосигнала на входе приемника пропорционально уровню выходного радиосигнала передатчика.

Буферный усилитель-формирователь DD10.1 предназначен для усиления кодовой комбинации, поступающей с шины данных, и выдачи ее на вход параллельного регистра с приходом управляющего сигнала. Параллельный регистр DD10.2 предназначен для хранения кодовой комбинации и выдачи ее на вход цифроаналогового преобразователя с получением управляющего сигнала. Цифроаналоговый преобразователь DD10.3 предназначен для преобразования цифрового кода в аналоговый сигнал, который подается на вход управления системой автоматической регулировки усиления усилителя радиочастоты. Усилитель радиочастоты с системой автоматической регулировки усиления DD10.4 предназначен для задания уровня высокочастотного сигнала пропорционально уровню высокочастотного сигнала, поступающего с тракта передачи.

Управляемый делитель 10, представленный на фиг. 4, может быть реализован на следующей элементной базе:

буферный усилитель-формирователь DD10.1 - буферный элемент, схема построения известна, в частности может быть реализован на микросхеме типа АП, см.: Цифровые интегральные микросхемы: Справочник./ М.И. Богданов, И.Н. Грель, В. А. Прохоренко, В.В. Шалимо. - Мн. Беларусь, 1991. - стр. 125-130 (рис. 2.61);

параллельный регистр DD10.2 - схема построения известна, в частности может быть реализован на микросхеме типа ИР (сдвигающий регистр) см.: Цифровые интегральные микросхемы: Справочник./ М.И. Богданов, И.Н. Грель, В.А. Прохоренко, В.В. Шалимо. - Мн. Беларусь, 1991. - стр. 366-377 (рис. 3.96);

цифроаналоговый преобразователь DD10.3 - схема построения известна, в частности может быть реализован на микросхеме типа ПА, см.: Цифровые и аналоговые микросхемы: Справочник./ С.В. Якубовский, Л.И. Ниссельсон, В.И. Кулешова и др. - М.: Радио и связь, 1989. - стр. 422 (рис. 5.130);

усилитель радиочастоты DD10.4 с системой автоматической регулировки усиления - схема построения известна, см.: Микросхемы и их применение: Справочное пособие./ В.Н. Вениаминов, О.Н. Лебедев, А.И. Мирошниченко. - М.: Радио и связь, 1989. - стр. 71 (рис.2.29).

Генератор псевдослучайной последовательности 1 предназначен для выработки псевдослучайной последовательности заданной длины, определяемой скоростью передачи контролируемой аппаратуры связи. Линия задержки 2 предназначена для задержки элементов псевдослучайной последовательности на время, необходимое для передачи элементов псевдослучайной последовательности. Блок регистрации ошибок 3 предназначен для сравнения переданных и принятых элементов псевдослучайной последовательности, выявления ошибок и передачи информации о них в блок подсчета ошибок. Блок подсчета ошибок 4 предназначен для запоминания количества ошибок и выдачи информации о них. Блок управляющих сигналов 5 предназначен для выработки сигналов, управляющих режимами работы устройства и выдачи элементов псевдослучайной последовательности в шину данных. Цифроаналоговый преобразователь 13 предназначен для преобразования цифрового сигнала в аналоговый при выдаче его в тракт приема контролируемой аппаратуры связи. Аналого-цифровой преобразователь 14 предназначен для преобразования аналогового сигнала в цифровой при обеспечении хранения информационного сигнала в запоминающем блоке. Запоминающий блок 15 предназначен для хранения информационного сигнала в цифровом виде в течение времени, необходимого для передачи всей тестовой псевдослучайной последовательности.

Генератор псевдослучайной последовательности 1, линия задержки 2, блок регистрации ошибок 3, блок подсчета ошибок 4, блок управляющих сигналов 5, цифроаналоговый преобразователь 13, аналого-цифровой преобразователь 14, запоминающий блок 15 технически можно реализовать в виде системы цифровой обработки сигналов (ЦОС) 16 на основе микропроцессора. При этом генератор псевдослучайной последовательности 1, линия задержки 2, блок регистрации ошибок 3, блок подсчета ошибок 4 реализуются программно с использованием постоянного запоминающего устройства (ПЗУ программ) системы ЦОС (см. фиг. 6). В постоянном запоминающем устройстве хранятся элементы псевдослучайной последовательности, которые по команде системы ЦОС поступают в систему. Запоминающий блок 15 реализуется на базе оперативного запоминающего устройства (ОЗУ данных) системы ЦОС (см. фиг. 6). Повышенные требования предъявляются к аналого-цифровому преобразователю 14, который должен быть высокоскоростным с учетом скорости передачи псевдослучайной последовательности и диапазона частот, в котором будет работать контролируемая аппаратура связи. Современная элементная база позволяет это реализовать, например микросхема MAX100 работает до 125 МГц (см. Каталог фирмы MAXIM 1996 г. NEW RELEASES DATA BOOK Volume V раздел 7 стр.9). Требования к цифроаналоговому преобразователю 13 менее высокие. Он может быть реализован, например на микросхеме МАХ 555 (см. Каталог фирмы MAXIM 1996 г. NEW RELEASES DATA BOOK Volume V раздел 9 стр. 82).

Принцип работы системы ЦОС описан во многих источниках: см. Справочник. С. Т. Хвощ, Н.Н. Варлинский, Е.А. Попов "Микропроцессоры и микроЭВМ в системах автоматического управления", стр. 394-410. Наиболее близкой по своей технической сущности является система цифровой обработки сигналов, описанная в книге А. А. Ланнэ "Цифровой процессор обработки сигналов TMS 32010 и его применение" издательства Военной академии связи, Ленинград, 1990 г., стр. 102-109, рис. 3.34, схема которой представлена на фиг. 6.

Вместо детального раскрытия конструктивного выполнения системы цифровой обработки сигналов приведем блок-схему реализуемого им алгоритма работы, например в виде, представленном на фиг. 7, внутри прямоугольника, изображающего систему цифровой обработки сигналов. Через П0-П3 обозначены управляющие вводы-выводы микропроцессорной системы, через V0-V1 - выход и вход для передачи и приема информационных сигналов. Такой информации о блоке достаточно для его осуществления, поскольку в данном случае по приведенной блок-схеме может быть произведено программирование известной системы ЦОС с использованием известных приемов.

Аттенюатор 7 предназначен для уменьшения уровня мощности, поступающего на вход полосового фильтра, и представляет собой известное устройство (см. "Измерения в электронике: Справочник. В.А. Кузнецов, В.А. Долгов и др. - М.: Энергоатомиздат, 1987, стр. 353-355). В зависимости от подводимой мощности возможно использование аттенюаторов различного типа. При подводимой мощности до 3 Ватт целесообразно применение резистивных ступенчатых аттенюаторов, до 10 Ватт - предельных аттенюаторов, основанных на явлении затухания электромагнитной энергии в запредельном волноводе.

Генератор шума 8 предназначен для вырабатывания шумовых радиотехнических сигналов для обеспечения требуемого соотношения сигнал/шум на выходе устройства. Данное устройство, основанное на использовании вакуумного диода, описано в кн. "Техническая эксплуатация, надежность средств связи и автоматизированных систем". Ч. I./Л.В. Жих. - М.: Военное издательство, 1992, стр. 261, рис. 113(а). Генератор шума основан на использовании дробового эффекта в температурно-насыщенном вакуумном диоде с прямым накалом. В анодном токе такого диода присутствует переменная составляющая. Действующее значение тока диода в режиме насыщения определяется формулой Шоттки

где e - заряд электрона;

I0 - анодный ток диода

Δf - полоса шумов.

Вакуумные диоды V (например, типа 2Д2С) позволяют генерировать шумовой сигнал в диапазоне от 1 до 600 МГц. На основе этого диода создан генератор шума Г2-32, см. : Измерения в электронике: Справочник./В.А. Кузнецов, В.А. Долгов и др. - М. : Энергоатомиздат, 1987, стр. 423-425. Он представляет собой коаксиальную линию с включенным в нее диодом, работающим в режиме насыщения.

Первый 11 и второй 12 полосовые фильтры предназначены для выделения полосы частот сигнала, поступающего на вход запоминающего устройства и управляемого делителя. Состоят из операционного усилителя и набора дискретных элементов, номиналы которых зависят от полосы частот, которую необходимо отфильтровать. Схема полосового фильтра представлена на фиг. 5, см.: Аналоговая электроника на операционных усилителях. А.Дж. Пейтон, Бином. - М., 1994, стр. 125. Ширина полосы пропускания фильтров зависит от скорости передачи информации и определяется соотношением .

.

Для выбора номинала элементов необходимо задаться значениями добротности Q и коэффициента передачи K. Тогда, полагая C1=C2=C, получим аналитические выражения для расчета

Центральную частоту настройки фильтра можно изменять независимо от Δω с помощью R1 или R2, но при этом будет изменяться коэффициент передачи K.

Устройство работает следующим образом.

Сигналы псевдослучайной последовательности через блок согласования 9 поступают на низкочастотный вход диагностируемой аппаратуры связи, которая при помощи управляющего сигнала с выхода переключения переводится в режим передачи. Пройдя тракт передачи с высокочастотного выхода аппаратуры связи, высокочастотный сигнал поступает на высокочастотный вход устройства в блок коммутации соединений 6, где происходит преобразование уровня этого сигнала. Высокочастотный сигнал передается через аттенюатор 7 и второй полосовой фильтр 12 на вход аналого-цифрового преобразователя 14, с выхода которого сигнал в цифровом виде поступает в запоминающий блок 15, где хранится до окончания передачи всей псевдослучайной последовательности. Для уменьшения объема памяти запоминающего блока 15 используется децимация, то есть снижение частоты дискретизации аналого-цифрового преобразователя, которая в этом случае выбирается из условия

где fд - частота дискретизации;

fв - верхняя частота спектра сигнала, ограниченная полосовым фильтром;

fн - нижняя частота спектра сигнала, ограниченная полосовым фильтром;

n - коэффициент децимации, n=1,2,3....

За счет снижения fд количество отчетов, которое необходимо запомнить, снижается в n раз, однако при этом теряется информация об уровне сигнала, что приводит к необходимости запоминания в запоминающем блоке 15 (в ОЗУ системы цифровой обработки сигналов) величины Umax (амплитуды сигнала) и воспроизведения ее кратной части с помощью управляемого делителя 10. После окончания передачи всей псевдослучайной последовательности диагностируемая аппаратура связи при помощи управляющего сигнала с выхода переключения блока коммутации соединений 6 переводится в режим приема. Из блока запоминания 15 сигнал в цифровой форме поступает на вход цифроаналогового преобразователя 13 и через первый полосовой фильтр 11, высокочастотный сигнал, приведенный к требуемому уровню в управляемом делителе 10, смешивается с сигналом шума генератора шума 8. Полученный сигнал с высокочастотного входа/выхода устройства поступает на высокочастотный вход диагностируемой аппаратуры связи в тракт приема. С низкочастотного выхода аппаратуры связи сигналы псевдослучайной последовательности через низкочастотный вход устройства поступают в блок регистрации ошибок 3, где происходит сравнение переданной и принятой псевдослучайной последовательности. В блоке подсчета ошибок 4 вычисляется коэффициент ошибок, на основании которого делается вывод о техническом состоянии аппаратуры связи.

Алгоритм работы генератора псевдослучайной последовательности 1, линии задержки 2, блока регистрации ошибок 3, блока подсчета ошибок 4, блока управляющих сигналов 5, цифроаналогового преобразователя 13, аналого-цифрового преобразователя 14, запоминающего блока 15 можно реализовать на основе алгоритма работы системы цифровой обработки сигналов 16, который представлен внутри прямоугольника на фиг. 7. Блоки алгоритма с 16.1 по 16.13 показывают управление устройством в режиме передача, а с 16.14 по 16.29 - в режиме приема. Алгоритм работает следующим образом. Для начала диагностирования на выход П2 управления блоком коммутации соединений подается разрешающий сигнал на запись информации о режиме работы, а на D0 шины данных подается значение информации, определяющее режим передачи системы цифровой обработки сигналов Бл. 16.1. Задается значение передаваемого бита псевдослучайной последовательности n, начиная с первого (n=1) Бл.16.2. Считывание n-го бита псевдослучайной последовательности из памяти и подача его через блок согласование 9 на низкочастотный выход устройства по D0 шины данных происходит при подаче разрешающего сигнала на выход П1 управления блоком сопряжения Бл.16.3. Устанавливается начальное значение параметра амплитуды входного сигнала Umax (Umax= 0) для осуществлении аналого-цифрового преобразования Бл.16.4. На следующем шаге устанавливается начальное значение текущего номера отсчета амплитуды сигнала (параметра a), начиная с первого Бл.16.5. На следующем шаге производится сравнение времени передачи одного информационного импульса t с периодом дискретизации Δt, через которое производится аналого-цифровое преобразование входного сигнала Бл.16.6. При t = aΔt производятся аналого-цифровое преобразование сигнала, поступающего на вход V1, и запись полученного значения в память Бл.16.7. В противном случае цикл повторяется до выполнения данного равенства. На следующем шаге сравнивается текущее значение амплитуды сигнала U с определенным ранее максимальным значением амплитуды сигнала Umax Бл.16.8. Если U>Umax, то запоминается новое максимальное значение амплитуды сигнала Бл.16.9, если - нет, то не запоминается. В обоих случаях осуществляется переход к следующему отсчету, a с увеличением этого параметра - на единицу Бл. 16.10. Далее проверяется условие окончания передачи информационного импульса a>b (сравнение с количеством отсчетов за время передачи одного информационного импульса b) Бл.16.11. При превышении данного параметра осуществляется переход к передаче следующего бита псевдослучайной последовательности (n= n+1) Бл.16.12. В противном случае осуществляется следующий отсчет данного информационного импульса. На следующем шаге проверяется условие окончания передачи тестовой псевдослучайной последовательности - сравнение текущего значения номера передаваемого бита псевдослучайной последовательности с общим количеством бит m, передаваемых за время передачи Бл.16.13. Если n<m, то осуществляется передача следующего импульса псевдослучайной последовательности. Если n>m, то осуществляется перевод устройства в режим приема путем выдачи разрешающего сигнала на выход П2 управления блоком коммутации соединений и на D0 шины данных значения информации, определяющего режим приема Бл.16.14. Установка требуемого коэффициента деления управляемого делителя осуществляется путем выдачи разрешающего сигнала на выход П3 управления управляемым делителем, а на D0-D3 шины данных - значение коэффициента деления Бл.16.15. Начальное значение количества ошибок z, возникающих при приеме псевдослучайной последовательности, принимается равным нулю (z= 0) Бл.16.16. На следующих двух шагах происходят установка начального значения параметра n (номера принятого бита n= n+1 псевдослучайной последовательности), установка начального значения параметра a (текущего значения номера отсчета) Бл.16.17, Бл.16.18. На следующем шаге проверяется условие, по выполнению которого производятся считывание значения a-го отсчета и цифроаналоговое преобразование высокочастотного сигнала с выхода V0 Бл.16.19, Бл.16.20. Данная операция происходит до тех пор, пока не будут переданы все отсчеты текущего элемента псевдослучайной последовательности Бл. 16.21. После проверки условия окончания передачи информационного импульса Бл. 16.22 происходит считывание значения n-го бита псевдослучайной последовательности с D0 шины данных с приходом разрешающего сигнала на выход П0 управления блоком согласования Бл.16.23. Считываются значения n-го бита из памяти и происходит сравнение значений принятого бита и считанного из памяти Бл.16.24, Бл.16.25. Если значения различны, то количество ошибок z увеличивается на одно значение Бл.16.27. Если значения одинаковы, то значение параметра z остается неизменным, и осуществляется прием следующего бита псевдослучайной последовательности Бл.16.26. При удовлетворении условия окончания приема псевдослучайной последовательности (n>m) Бл. 16.28 осуществляется вывод количества ошибок z Бл.16.29, и алгоритм считается выполненным полностью.

Блок коммутации соединений 6 работает следующим образом. По шине данных от Бл.5 на информационный вход D-триггера (вход D) подается сигнал, определяющий режим передачи, на вход синхронизации D-триггера (вход C) D6 подается управляющий сигнал от Бл. 5, разрешающий запись информационного сигнала в D-триггер D6. В результате на выходе D-триггера D6 появляется сигнал, обеспечивающий открытие транзистора VT6. Тем самым осуществляется подключение источника питания Uпит к управляющей обмотке реле Р6, которое своими контактами второй и третьей групп подключает соответственно выход делителя мощности R1, R2 к Бл.7, а корпус - к выходу переключения. Первая группа контактов размыкается, отключая тем самым приемный тракт устройства диагностирования. Для обеспечения режима приема по шине данных подается сигнал от Бл. 5, определяющий режим приема, на вход синхронизации D-триггера (вход C) D6 подается управляющий сигнал от Бл.5 с управляющего входа блока, разрешающий запись информационного сигнала в D-триггер D6, в результате на выходе D-триггера D6 сигнал отсутствует, транзистор VT6 закрыт, управляющая обмотка реле Р6 обесточена, вторая и третья рабочие группы контактов разомкнуты, первая группа контактов замкнута и через нее высокочастотный сигнал поступает от Бл.8, Бл.10 на высокочастотный выход блока.

Блок согласования 9 работает следующим образом. Для передачи контрольной псевдослучайной последовательности на низкочастотный выход блока по шине данных от Бл. 5 поступают элементы псевдослучайной последовательности, на вход данных сдвоенного усилителя-формирователя DD9.1, с входа управления передачей блока на управляющий вход CA сдвоенного усилителя-формирователя DD9.1 подается управляющий сигнал, разрешающий коммутацию входа данных Wo сдвоенного усилителя-формирователя с информационным выходом Ao сдвоенного усилителя-формирователя. Элементы псевдослучайной последовательности с выхода Ao сдвоенного усилителя-формирователя DD9.1 подаются на информационный вход (вход D) D-триггера D9.2 и с приходом управляющего сигнала на вход синхронизации (вход C) D-триггера D9.2 передаются через первый преобразователь уровня D9.4 на низкочастотный выход. Для приема контрольной псевдослучайной последовательности с входа управления приемом от Бл.5 на управляющий вход CB сдвоенного усилителя-формирователя DD9.1 передается управляющий сигнал, разрешающий подключение информационного входа Bо сдвоенного усилителя-формирователя DD9.1 к входу данных Wo сдвоенного усилителя-формирователя DD9.1. С низкочастотного входа элементы псевдослучайной последовательности через второй преобразователь уровня DD9.5 и элемент ИЛИ-НЕ DD9.3 поступают на информационный вход Bо сдвоенного усилителя-формирователя DD9.1 и далее в шину данных.

Управляемый делитель 10 работает следующим образом. На вход усилителя радиочастоты DD10.4 поступает сигнал с выхода первого полосового фильтра от Бл.11. С шины данных поступает информация в параллельном коде об уровне входного сигнала. По поступлению управляющего (разрешающего) сигнала от Бл.5 информация через буферный усилитель-формирователь DD10.1 записывается в параллельном регистре DD10.2. Эта информация сохраняется в течение времени приема псевдослучайной последовательности. Цифроаналоговый преобразователь DD10.3, подключенный к выходам параллельного регистра DD10.2, выдает постоянный уровень на систему автоматической регулировки усиления усилителя радиочастоты DD10.4 в соответствии со значением числа записанного в двоичном коде в параллельном регистре DD10.2.

Оценка эффективности заявленного технического решения.

1. Отличительной особенностью симплексных средств связи является то, что часть элементов используется как в режиме передачи, так и в режиме приема. Условно их можно представить в виде, показанном на фиг. 8.

Рассчитаем суммарную погрешность определения технического состояния QΣ при диагностике состояния аппаратуры связи с использованием прототипа и заявленного устройства. В первом случае, полагая погрешность определения технического состояния, вносимую обеими средствами связи одинаковой, получим (фиг.8,а):

Qпер. = Q1 + Q3 + Q3 + Q2;

Qпр. = Q2 + Q3 + Q3 + Q1;

QΣ = = 2Q1 + 2Q2 + 4Q3 = 2(Q1+ Q2 + 2Q3),

где Q1 - погрешность, вносимая элементами тракта передачи;

Q2 - погрешность, вносимая элементами тракта приема;

Q3 - погрешность, вносимая общими элементами тракта передачи и приема.

Во втором случае при использовании предлагаемого устройства получим (фиг. 8,б):

QΣ = = Q1 + Q2 + 2Q3.

Таким образом, суммарная погрешность уменьшается в два раза при использовании заявленного устройства.

2. Сокращается время диагностирования за счет введения генератора шума по методике, заложенной в прототипе.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ДИАГНОСТИКИ СОСТОЯНИЯ АППАРАТУРЫ ЦИФРОВЫХ СИСТЕМ ПЕРЕДАЧИ | 1998 |

|

RU2132594C1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧИХ ЧАСТОТ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1994 |

|

RU2097923C1 |

| УСТРОЙСТВО ДИАГНОСТИКИ СОСТОЯНИЯ СИСТЕМ СВЯЗИ | 1996 |

|

RU2103819C1 |

| УСТРОЙСТВО ДИАГНОСТИРОВАНИЯ СОСТОЯНИЯ АППАРАТУРЫ СВЯЗИ | 2005 |

|

RU2289209C1 |

| ГЕНЕРАТОР БЕЛОГО ШУМА (ВАРИАНТЫ) | 1997 |

|

RU2120179C1 |

| ЧАСТОТНО-АДАПТИВНАЯ РАДИОЛИНИЯ ДЛЯ ПЕРЕДАЧИ СРЕДНЕСКОРОСТНЫХ ПОТОКОВ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1998 |

|

RU2142200C1 |

| СИНХРОННЫЙ ДЕТЕКТОР | 1997 |

|

RU2124804C1 |

| СПОСОБ СКРЕМБЛИРОВАНИЯ АНАЛОГОВОГО СИГНАЛА И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1997 |

|

RU2123764C1 |

| РАДИОЛИНИЯ С АМПЛИТУДНО-ФАЗОМАНИПУЛИРОВАННЫМИ ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1996 |

|

RU2101871C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

Изобретение относится к радиотехнике. Устройство диагностики позволяет оценить техническое состояние аппаратуры связи, работающей в симплексном режиме, за счет сохранения тестовой псевдослучайной последовательности в элементе памяти на время прохождения псевдослучайной последовательности по тракту передачи и выдачи ее в тракт приема после окончания передачи. Устройство включает генератор псевдослучайной последовательности (1), линию задержки (2), блок регистрации ошибок (3), блок подсчета ошибок (4), блок управляющих сигналов (5), блок коммутации соединений (6), аттенюатор (7), генератор шума (8), блок согласования (9), управляемый делитель (10), первый (11) и второй (12) полосовые фильтры, цифроаналоговый преобразователь (13), аналого-цифровой преобразователь (14), запоминающий блок (15). С помощью (15) сигналы псевдослучайной последовательности, прошедшие по тракту передачи диагностируемой аппаратуры связи, хранятся до момента окончания передачи всей последовательности. После окончания передачи псевдослучайная последовательность из (15) поступает в приемный тракт аппаратуры связи и передается в обратном направлении. Сравнивается с исходной и по коэффициенту ошибок определяется техническое состояние аппаратуры связи. Технический результат: повышение достоверности диагностирования состояния аппаратуры связи, работающей в симплексном режиме. 3 з.п.ф-лы, 8 ил.

| Устройство диагностики состояния аппаратуры цифровых систем передачи | 1990 |

|

SU1734219A1 |

| Устройство контроля качества канала связи | 1990 |

|

SU1778911A1 |

| Метрология, стандартизация и измерения в технике связи./Под ред | |||

| Б.П | |||

| Хромого | |||

| - М.: Радио и связь, 1986, с | |||

| Прибор для корчевания пней | 1921 |

|

SU237A1 |

Авторы

Даты

1998-12-27—Публикация

1997-06-19—Подача