Предлагаемые технические решения объединены единым изобретательским замыслом и относятся к области радиотехники, а именно к области диагностики технического состояния аппаратуры цифровых систем передачи и, в частности, могут использоваться при определении вида технического состояния аппаратуры цифровых систем передачи с обнаружением и локализацией различных дефектов.

Толкование терминов, используемых в заявке: - отказ - событие, заключающееся в нарушении работоспособного состояния объекта (ГОСТ 27.002-89. Надежность в технике. Основные понятия. Термины и определения.); сбой - самоустраняющийся отказ или однократный отказ, устраняемый незначительным вмешательством оператора (ГОСТ 27.002- 89); перемежающийся отказ - многократно возникающий самоустраняющийся отказ одного и того же характера (ГОСТ 27.002- 89); решетчатое распределение - величина, ξ имеет решетчатое распределение, если она дискретна и все ее возможные значения имеют вид a+k•h, k = 0, ±1,.. . . Величина h называется шагом распределения (Справочник по теории вероятностей и математической статистике / В.С.Королюк. Н.И.Портенко, А.В.Скороход, А. Ф.Турбин. - М.: Наука. Главная редакция физико-математической литературы, 1985. - стр. 20-21).

Известны способы диагностирования, описанные, например, в книге: Автоматизация диагностирования электронных устройств / Ю.В.Малышенко, В.П.Чипулис. С.Г.Шаршунов / Под ред. В.П.Чипулиса - М.: Энергоатомиздат. 1986. -216 с. . включающие формирование тестовой последовательности, ее преобразование по установленному закону, запоминание преобразованной последовательности и сравнение ее с рассчитанной ранее. Отличие в преобразованной и рассчитанной последовательности свидетельствует об отказе или сбое. Однако известные способы- аналоги не позволяют обнаруживать перемежающиеся одиночные и кратные отказы (сбои).

Известные устройства диагностирования - см. изобретение "Устройство для контроля работоспособности радиоприемника" (51) 4 H 04 В 17/00, опубликованное 22.02.90. , выпуск N 134; изобретение "Автоматизированная система контроля" (51)5 H 04 В 17/00 // H 04 В 3/46, опубликованное 30.06.94., бюллетень N 12. Они содержат устройства формирования тестовых последовательностей, устройство сравнения тестовых последовательностей, счетчик ошибок. Данные устройства позволяют диагностировать системы передачи по коэффициенту ошибок.

Общим недостатком аналогов является низкая достоверность диагностирования аппаратуры цифровых систем передачи, невозможность обнаружения перемежающихся одиночных и кратных отказов (сбоев), невозможность получения требуемой точности в реальном масштабе времени.

Наиболее близким по своей технической сущности к заявленному способу диагностики состояния аппаратуры цифровых систем передачи является способ, реализованный в устройстве диагностики состояния аппаратуры цифровых систем передачи по авторскому свидетельству СССР N 1734219, заявленному 6.08.90, опубликованное 15.05.92, бюллетень N 18. Способ-прототип заключается в формировании тестовой псевдослучайной последовательности длительностью 158400 тактовых импульсов и подаче ее на вход передающего тракта, ее преобразовании по установленному алгоритму преобразования сигнала, последующем ослаблении и смешивании с сигналом шума, коммутации на вход приемного тракта, ее обратном преобразовании, выделении переданной псевдослучайной последовательности на выходе приемного тракта, ее сравнении с исходным тестом путем подсчета искаженных импульсов. По заранее установленному алгоритму, при превышении допустимой величины искаженных импульсов N > Nдоп, где N - число искаженных импульсов, Nдоп - допустимое число искаженных импульсов, производится повторная передача тестовой псевдослучайной последовательности, при этом могут вводиться новые и (или) исключаться ранее установленные преобразования псевдослучайной последовательности в зависимости от соотношения N и Nдоп, до тех пор, пока не будет определен неисправный блок аппаратуры цифровых систем передачи. Однако способ-прототип имеет недостатки, заключающиеся в отсутствии возможности идентифицировать сбои и перемежающиеся одиночные и кратные отказы.

Из известных наиболее близким к заявленному (прототипом) по своей технической сущности является устройство диагностики состояния аппаратуры цифровых систем передачи по авторскому свидетельству СССР N 1734219, заявленному 6.08.90, опубликованное 15.05.92, бюллетень N 18. Устройство-прототип состоит из передающего и приемного трактов диагностируемой аппаратуры цифровых систем передачи, каждый из которых включает в себя блоки преобразования сигналов, такие как кодер передающего тракта, модулятор передающего тракта, преобразователь частоты передающего тракта, усилитель мощности передающего тракта, блок входных цепей и усилителя высокой частоты приемного тракта, преобразователя частоты приемного тракта, демодулятор приемного тракта, декодер приемного тракта, генератора псевдослучайной последовательности, линии задержки, блока регистрации ошибок, блока подсчета ошибок, блока коммутации соединений, блока управляющих сигналов, генератора шума, аттенюатора.

При этом генератор псевдослучайной последовательности подключен к первому входу линии задержки и второму входу блока коммутации соединений, первый выход и четвертый вход которого подключены к соответствующим входу и выходу тракта передачи, третий выход блока коммутации соединений подключен к входу аттенюатора, выход которого и выход генератора шума подключены к первому входу блока коммутации соединений, четвертый выход и третий вход которого подключены соответственно к входу и выходу тракта приема, группа выходов блока управляющих сигналов подключена к группе входов блока коммутации соединений, второй выход которого подключен к второму входу блока регистрации ошибок, выход которого подключен к входу блока подсчета ошибок, выход линии задержки подключен к третьему входу блока регистрации ошибок.

Это позволяет, по сравнению с устройствами-аналогами, существенно сократить время и повысить достоверность оценки состояния диагностируемой аппаратуры цифровых систем передачи за счет использования механизма "усиления" количества неправильно принятых импульсов.

Однако устройство-прототип имеет недостатки: не позволяет идентифицировать кратные отказы, так как оценка состояния диагностируемой аппаратуры цифровых систем передачи осуществляется только по одному параметру - коэффициенту ошибок, который не несет в себе информации о характере и кратности отказа, а свидетельствует только о наличии неисправности, что, в свою очередь, увеличивает время локализации неисправного (неисправных) элемента (элементов); относительно невысокая надежность из-за необходимости введения между соответствующими блоками преобразования сигналов передающего и приемного трактов диагностируемой аппаратуры управляемых электронных ключей.

Целью изобретения заявленных технических решений является разработка способа диагностирования состояния аппаратуры цифровых систем передачи и устройства, его реализующего, позволяющих обнаруживать одиночные и кратные отказы аппаратуры цифровых систем передачи.

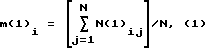

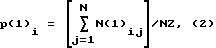

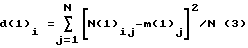

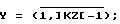

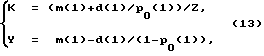

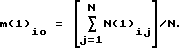

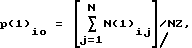

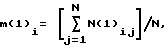

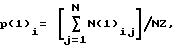

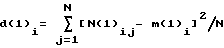

Поставленная цель достигается тем, что в известном способе диагностирования состояния аппаратуры цифровых систем передачи, заключающемся в формировании псевдослучайной последовательности, подаче ее на вход передающего тракта, ее преобразовании по установленному алгоритму преобразования сигнала, последующем ослаблении и смешивании ее с сигналом шума, коммутации на вход приемного тракта, ее обратном преобразовании, выделении восстановленной псевдослучайной последовательности, дополнительно сигналы псевдослучайной последовательности Fi(t) выделяют после каждого ее i-го преобразования. Где Fi(t) - выделенная псевдослучайная последовательность после i-го преобразования, i = 1, 2, 3, ...R, R - число преобразований псевдослучайной последовательности согласно установленному алгоритму преобразования. После чего для каждого i-го преобразования вычисляют математическое ожидание числа единичных символов m(1)i, дисперсию числа появления единичных символов d(1)i, и вероятность появления единичного символа p(1)i, по формулам

и по полученным результатам определяют параметры возможных технических состояний аппаратуры цифровых систем передачи.

Поставленная цель достигается тем, что в известном устройстве диагностики состояния аппаратуры цифровых систем передачи, содержащем передающий и приемный тракты диагностируемой аппаратуры цифровых систем передачи, которые включают блоки преобразования сигналов, блок управления, генератор псевдослучайной последовательности, аттенюатор и генератор шума, выход которого подключен к выходу аттенюатора, дополнительно введены блоки анализа, памяти, сравнения и отображения состояния. Выход генератора псевдослучайной последовательности подключен к входу передающего тракта диагностируемой аппаратуры цифровых систем передачи. Выход передающего тракта диагностируемой аппаратуры цифровых систем передачи подключен к входу аттенюатора. Выход аттенюатора подключен к входу приемного тракта диагностируемой аппаратуры цифровых систем передачи. Выходы блоков преобразования сигналов передающего и приемного трактов диагностируемой аппаратуры цифровых систем передачи подключены к i-м информационным входам блока анализа, где i = 1, 2, 3, ....R, R - число контролируемых блоков преобразования сигналов диагностируемой аппаратуры цифровых систем передачи. К информационному входу блока памяти подключены информационные выходы блоков анализа, определения параметров и сравнения, а его информационный выход подключен к информационным входам блоков определения параметров, сравнения и отображения состояния. Причем управляющие входы генератора псевдослучайной последовательности, блоков анализа, определения параметров, памяти, сравнения и отображения состояния подключены к соответствующим выходам блока управления.

Проведенный заявителем анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностями признаков, тождественным всем признакам заявленных способа и устройства диагностики состояния аппаратуры цифровых систем передачи, отсутствуют. Следовательно, каждое из заявленных изобретений соответствует условию патентоспособности "Новизна".

Результаты поиска известных решений в данной и смежной областях техники с целью выявления признаков, совпадающих с отличительными от прототипов признаками каждого заявленного изобретения, показали, что они не следуют явным образом из уровня техники. Из определенного заявителем уровня техники не выявлена известность влияния предусматриваемых существенными признаками каждого из заявленных изобретений на достижение указанного технического результата. Следовательно, каждое из заявленных изобретений соответствует условию патентоспособности "Изобретательский уровень".

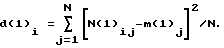

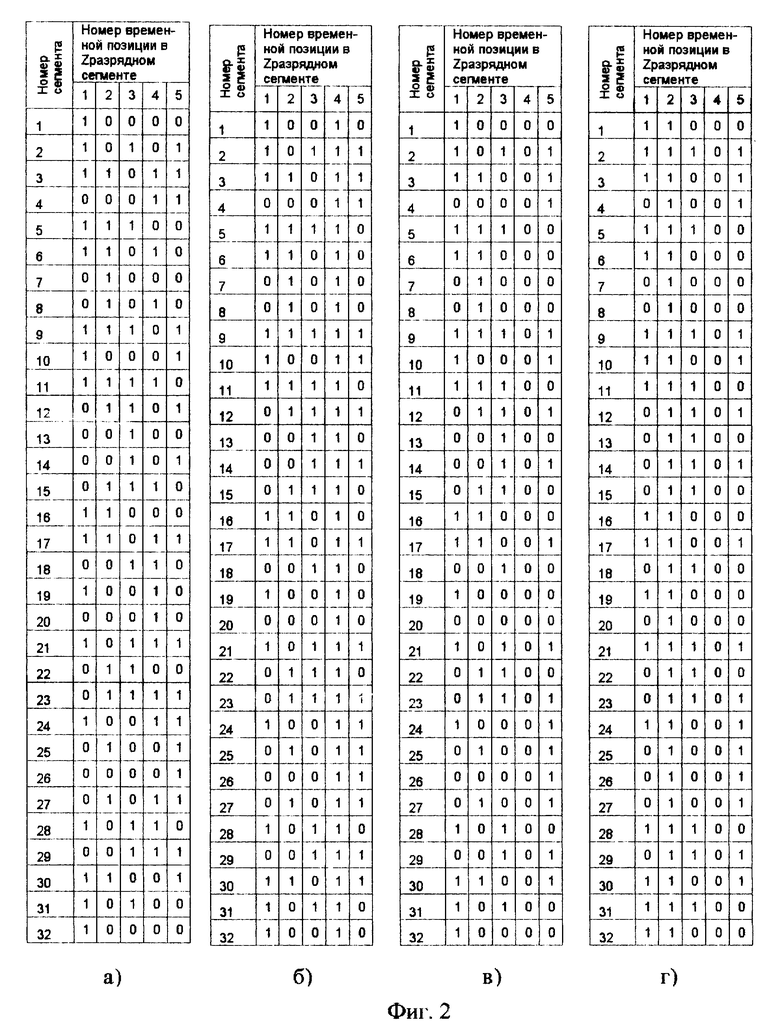

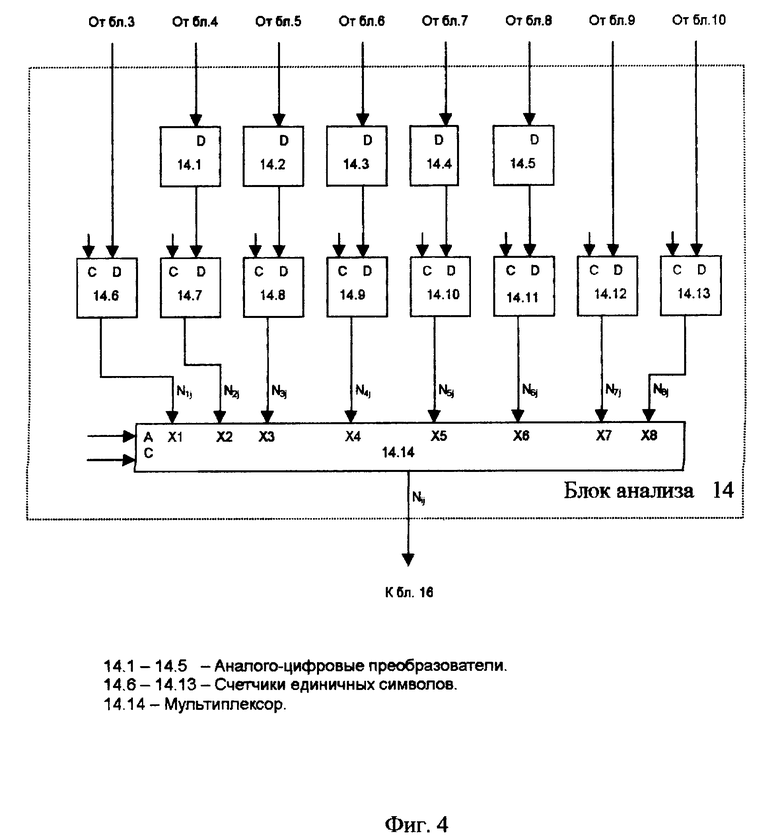

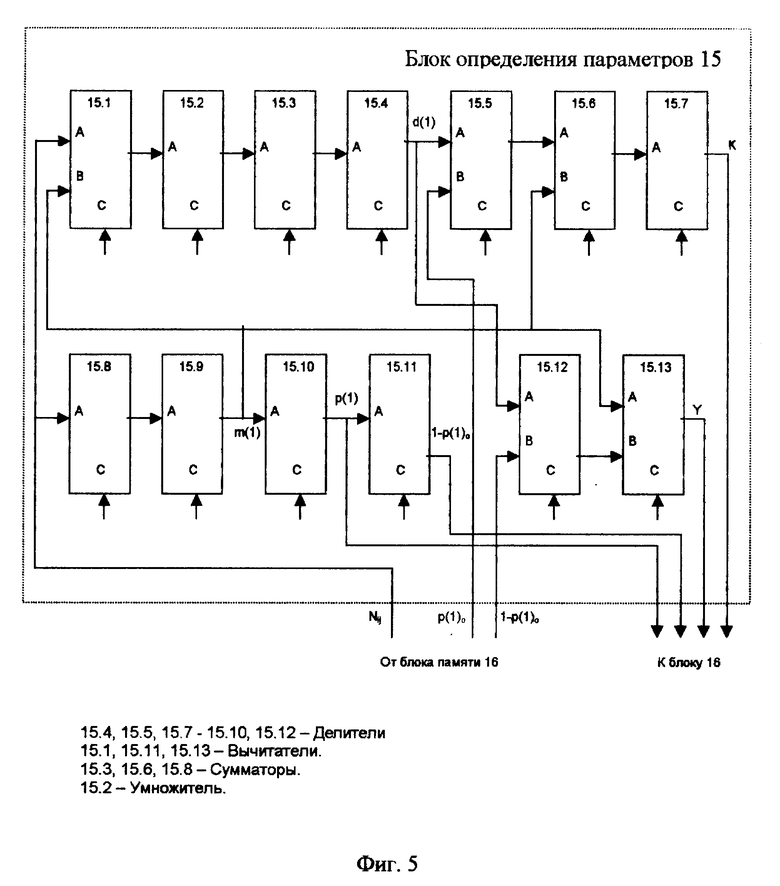

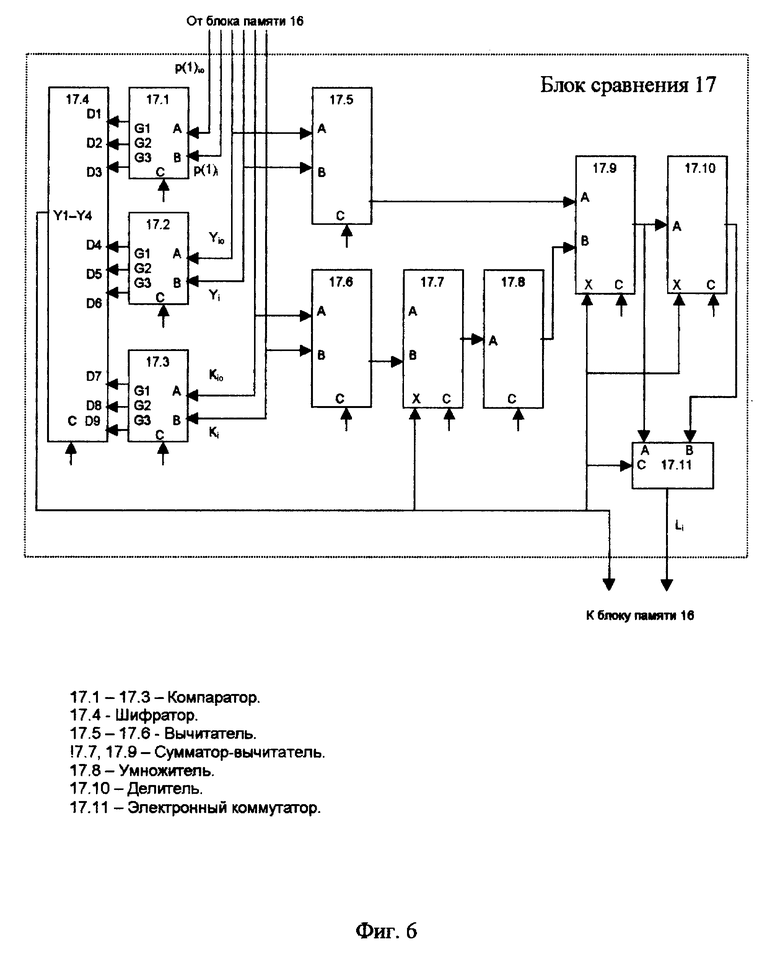

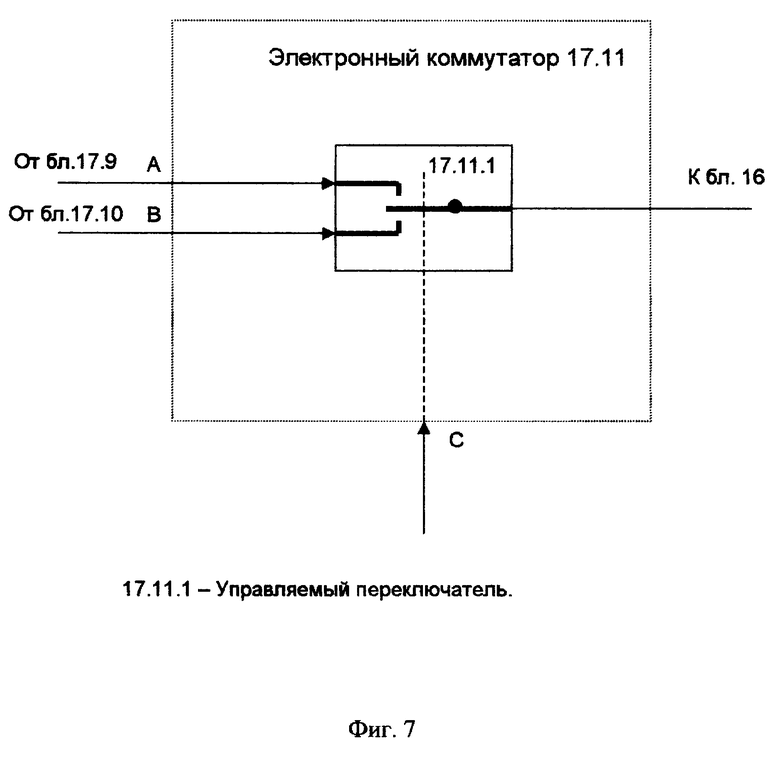

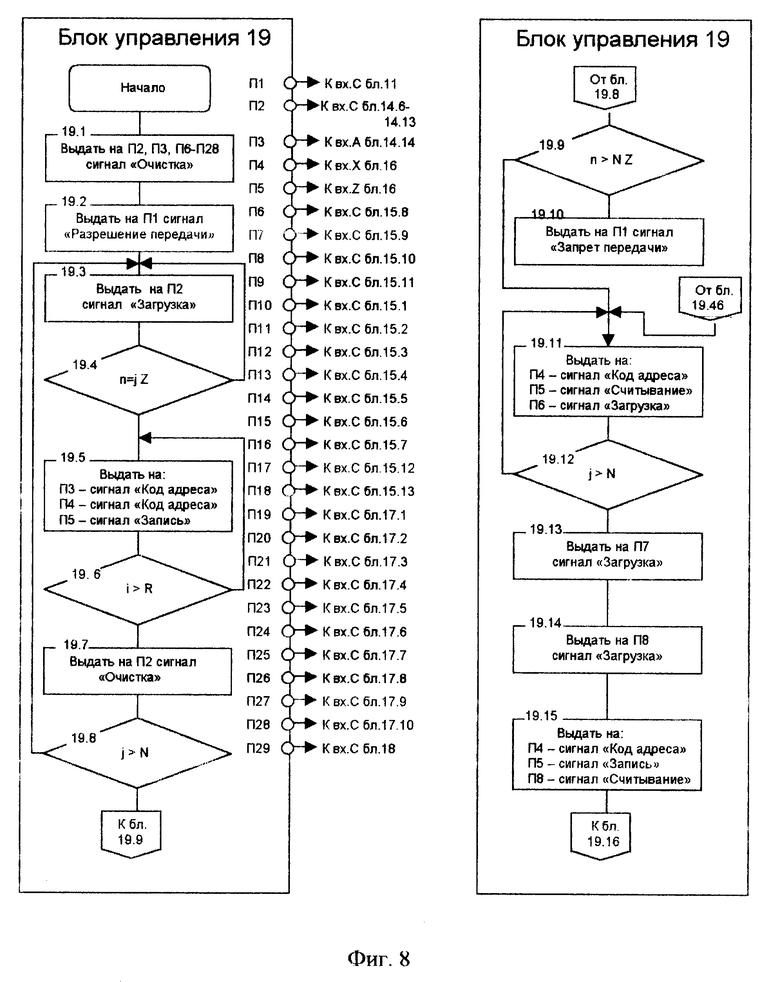

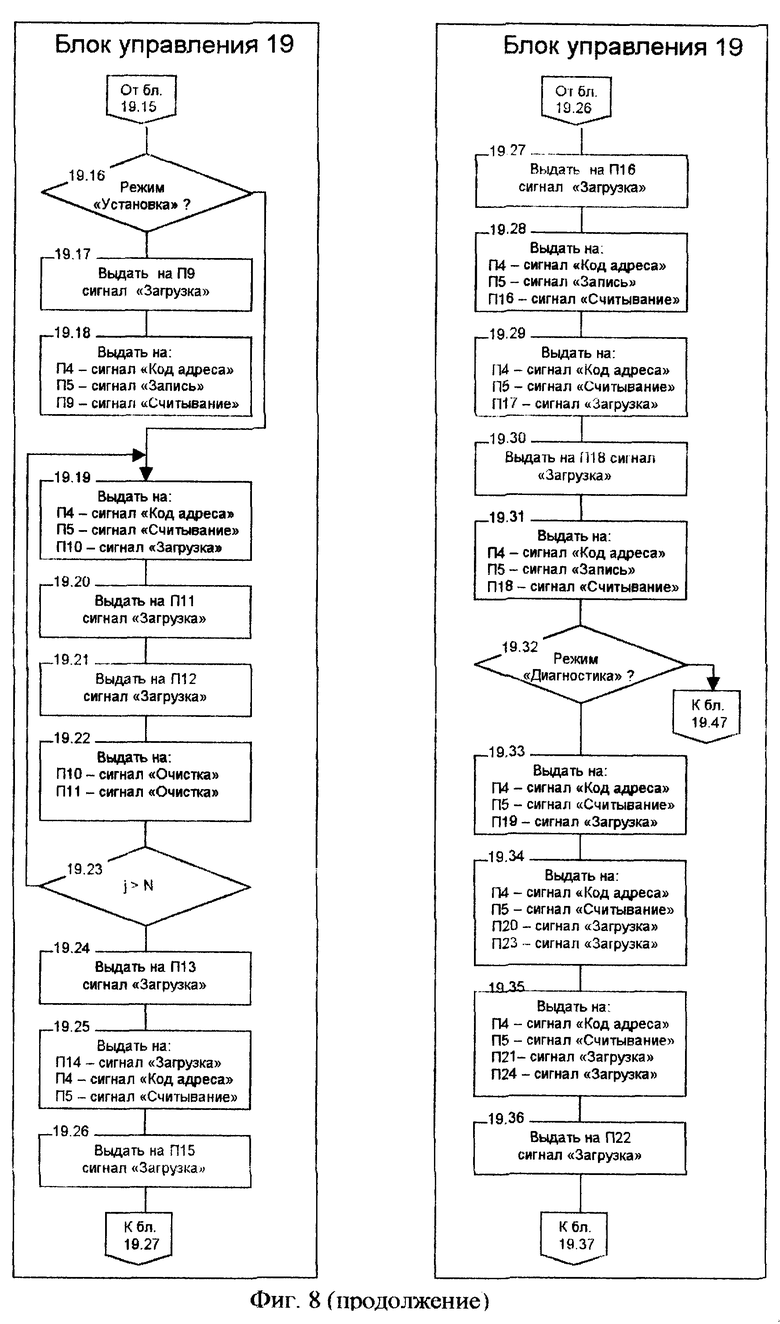

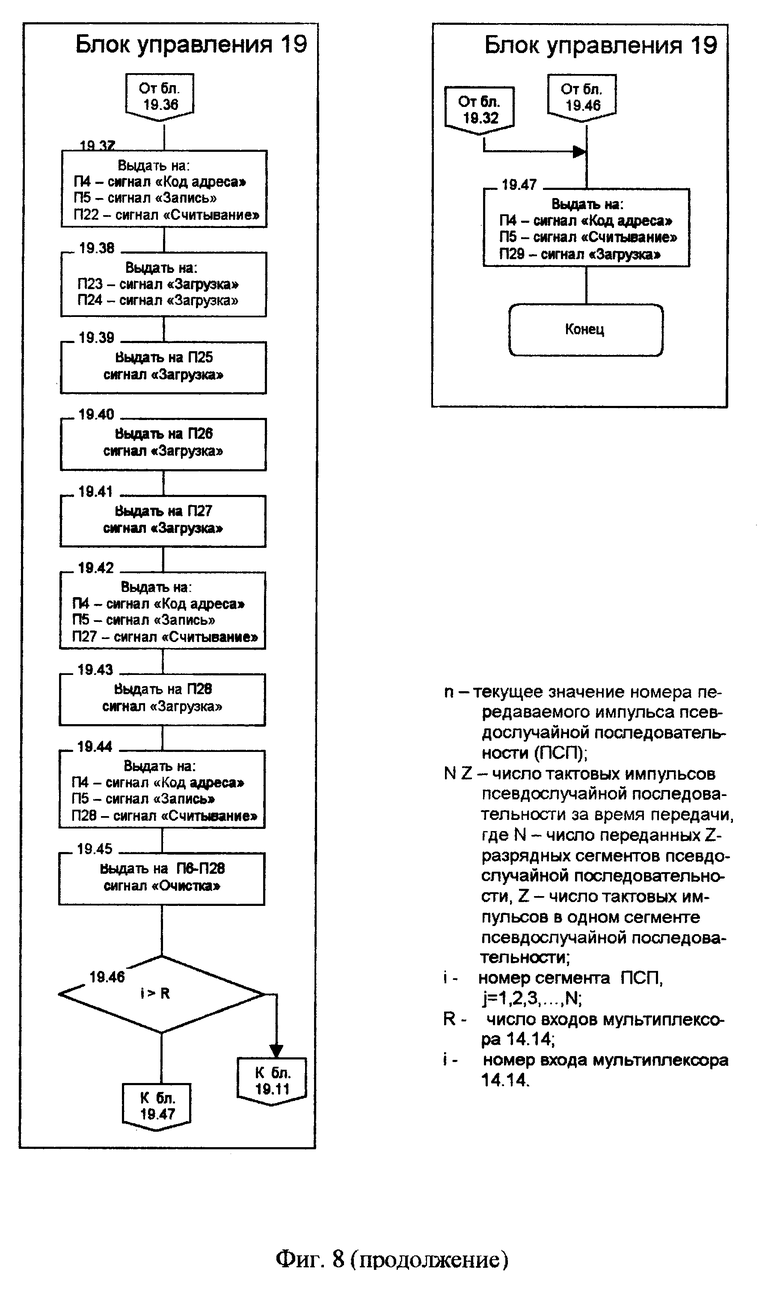

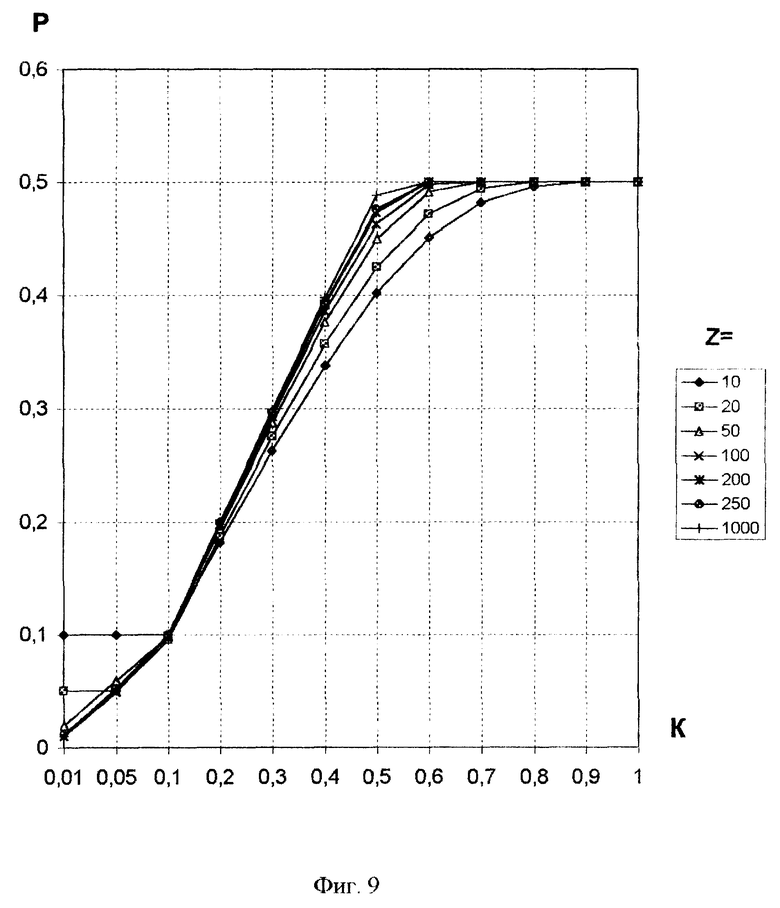

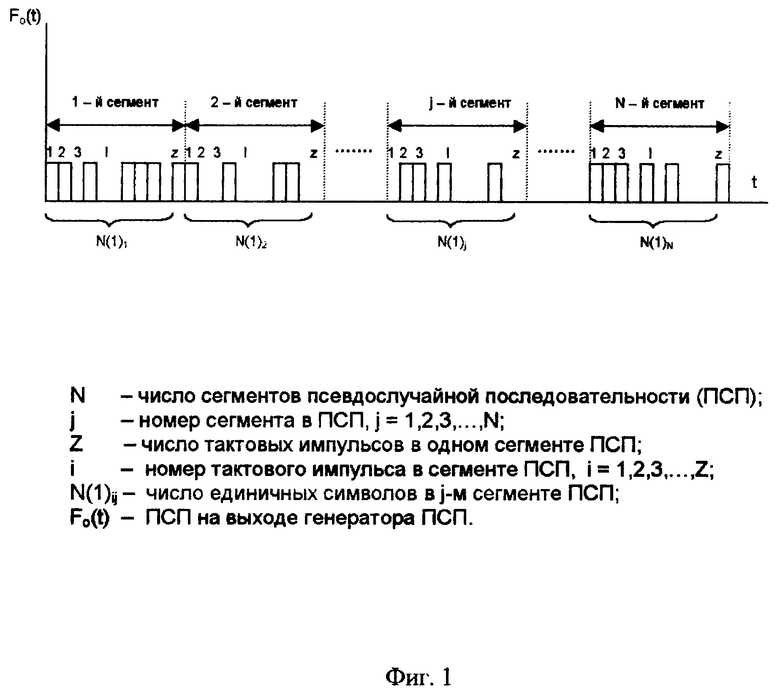

Заявленные объекты изобретения поясняются чертежами, на которых на фиг. 1 - структура псевдослучайной последовательности; на фиг. 2 - таблица состояний временных позиций в Z-разрядных сегментах принятой псевдослучайной последовательности: а - при исправном состоянии диагностируемой аппаратуры цифровых систем передачи; б, в, г - при неисправном состоянии диагностируемой аппаратуры цифровых систем передачи; на фиг. 3 - структурная схема устройства диагностики технического состояния аппаратуры цифровых систем передачи; на фиг. 4 - структурная схема блока анализа; - на фиг. 5 - структурная схема блока определения параметров; на фиг. 6 - структурная схема блока сравнения; на фиг. 7 - структурная схема электронного коммутатора; на фиг. 8 - алгоритм работы блока управления; на фиг. 9 - результаты расчета необходимого значения Z.

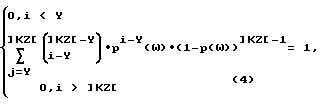

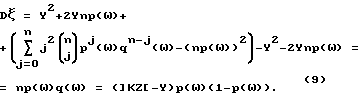

Реализация заявленного способа заключается в следующем. Для различных видов диагностирования могут быть применены схемы независимых испытаний на основе усеченных биномиальных распределений, функция распределения которых имеет вид

где p(ω) - вероятность появления единичных символов в любом разряде на выходе аппаратуры цифровых систем передачи, ω ⊂ Ω, Ω - пространство элементарных событий мощностью Z, представляющей разрядность выходной цифровой последовательности единичных и нулевых символов (ω1,ω2,...,ωz);

К - коэффициент, характеризующий допустимую кратность единичных сигналов на выходе аппаратуры цифровых систем передачи в Z-разрядных последовательностях при N испытаниях; при этом 0 < К ≤ 1;

Y - минимально допустимое количество единичных символов на выходе аппаратуры цифровых систем передачи в Z-разрядных последовательностях при N испытаниях; при этом

]*[ - "антье", наибольшее целое.

Под усеченным биномиальным распределением понимается закон распределения вероятности появления случайной величины при ограничении на число появлений случайной величины (например, запрет на появление длинных серий единичных и нулевых символов) в некотором количестве независимых испытаний. Частным случаем усеченного биномиального распределения при начальных параметрах усечения Y= 0 и К=1 является биномиальное распределение, описанное, например, в кн. : Справочник по математике (для научных работников и инженеров). Г.Корн, Т. Корн. - М. : Наука, Главная редакция физико-математической литературы, 1978, стр.572 - 573.

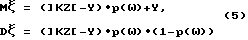

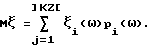

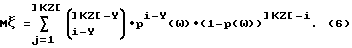

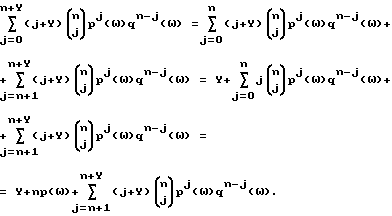

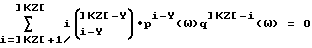

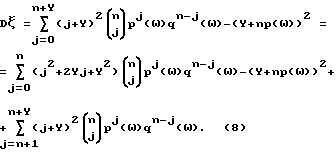

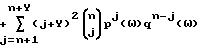

Тогда при N испытаниях аппаратуры цифровых систем передачи на ее выходе возникают последовательности (ω1,ω2,..,ωz), содержащие различное количество единичных символов Y ≤ ξ(ω) ≤ ]KZ[ в каждом испытании, а вероятность возникновение ξ(ω) полностью будет определяться выражением (4). Для решения задачи идентификации технического состояния аппаратуры цифровых систем передачи необходимо определить числовые характеристики усеченного биномиального распределения, описывающего статистические характеристики сигналов на ее выходе. Поскольку случайная величина ξ(ω) является дискретной, имеет решетчатое распределение, то ее математическое ожидание и дисперсия, обозначаемые соответственно Mξ и Dξ, находятся с помощью формул

Доказательство соотношений (5) приведено, например, в статье А.М.Лихачев. В.Е.Кузнецов. И.А.Дроздов и др. "Асимптотическое приближение усеченного биномиального распределения"// Сборник научных трудов ученых Орловской области. Выпуск 3. Орел: ОГТУ. 1997, стр. 134-138 и основано на том, что математическое ожидание любой дискретной величины определяется как сумма  Тогда его значение для выражений (5) примет вид

Тогда его значение для выражений (5) примет вид

Положим, что q(ω = 1-p(ω)), n = ]KZ[-Y, j = i-Y. Тогда правая часть (6) примет вид

Произведем в (6) обратную замену переменных. Тогда

по определению из (4), а выражение (6) примет вид Mξ = (]KZ[-Y)p(ω+Y).

В соответствии со свойствами дисперсия Dξ = Mξ2-(Mξ)2. Тогда ее нахождения связано с определением второго начального момента ξ(ω). Произведем замену переменных и получим

Учитывая, что  по определению (4) после подстановки переменных равна 0, выражение (8) примет вид

по определению (4) после подстановки переменных равна 0, выражение (8) примет вид

Таким образом, справедливость выражений (5) доказана.

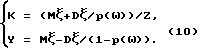

Тогда на основе решения системы уравнений, построенной на основе выражений (5), относительно неизвестных параметров усечения K и Y методом подстановки получим следующие выражения:

где Mξ = m(1), Dξ = d(1), p(ω = d(1)).

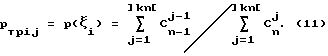

Выбор Z определяется требуемой точностью оценки вероятности появления единичного символа p(1) в каждой временной позиции. Проведенные исследования оценки показывают, что, поскольку такая вероятность может быть вычислена в полной группе событий реализации различных векторов двоичных последовательностей, то данная величина может быть определена как отношение числа комбинаций, в котором участвуют сигнальные единицы данной временной позиции к общему числу возможных реализаций комбинаций (см., например, Б.А.Севастьянов "Теории вероятностей и математической статистики. - М.: Наука, 1982. -256 с.):

Проведенные расчеты, приведенные на фиг. 9, показывают, что для того, чтобы погрешность измерения вероятности появления единичного символа не превышала 10%, Z должно быть не менее 20.

Второй составляющей является выбор необходимого числа сегментов N. Значение N выбирается исходя из требований метрологической точности измерений математического ожидания и дисперсии числа единичных символов в Z-разрядных сегментах тестовой последовательности (см., например, Б.А.Севастьянов "Теории вероятностей и математической статистики. -М.: Наука, 1982. - 256 с.). Для обеспечения требуемой точности N должно быть не менее 10.

Возможность реализации заявляемого способа диагностирования аппаратуры цифровых систем передачи объясняется следующим. Изменение вероятности появления единичных символов p(1), параметров усечения K и Y говорит об изменении состояния аппаратуры цифровых систем передачи и характере его изменения, а именно:

увеличение величины p(1) относительно значения po(1) говорит о преобладании отказов, проявляющихся в наличии единичных символов, а уменьшение - о преобладании отказов, проявляющихся в наличии нулевых символов;

увеличение значения Y относительно значения Yo свидетельствует об уменьшении числа комбинаций снизу, то есть о появлении отказов или сбоев, проявляющихся в появлении фиксированного единичного символа;

уменьшение значения K относительно значения Ko говорит о наличии в комбинациях фиксированных нулевых символов;

одновременное изменение значений Y и K свидетельствует о кратном отказе или сбое.

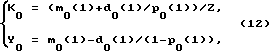

При этом, значения Y, Yo, K и Кo определяются по формулам

где mo(1), do(1), po(1), Ko, Yo - значения математического ожидания, дисперсии и вероятности появления единичных символов, параметров усечения соответственно при работоспособном состоянии диагностируемой аппаратуры цифровых систем передачи.

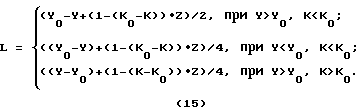

Для аппаратуры цифровых систем передачи, реализующей полную группу векторов (ω1,ω2,...,ωz) кратность отказов (то есть число отказавших блоков) определяется по формуле

L = Y+(1-K)•Z

Для аппаратуры цифровых систем передачи, у которой в рабочем режиме имеется запрет на определенные комбинации единичных и нулевых символов, кратность отказов определяется по формуле

Суть заявляемого способа поясняется следующим образом.

На вход диагностируемой аппаратуры цифровых систем передачи подаются N раз Z-разрядные сегменты псевдослучайной последовательности. В качестве псевдослучайной последовательности могут использоваться специально сгенерированные сигналы на основе генератора псевдослучайных импульсов, построенном на рекурентной линии задержки (описан, например, в кн. Бобнев М.П. Генерирование случайных сигналов. Изд. 2-е перераб. и доп. М.: Энергия, 1971. - 240 с.). Примем, что число тактовых импульсов в одном сегменте Z=5, а число передачи сегментов псевдослучайной последовательности N=32. Вид фрагмента переданной тестовой псевдослучайной последовательности показан на фиг. 1.

Сформированная псевдослучайная последовательность Fo(t) подается на вход передающего тракта, где происходит ее преобразование по установленному алгоритму (кодирование, модуляция, перенос в область высоких частот, усиление). Затем псевдослучайная последовательность ослабляется аттенюатором и смешивается с сигналом шума с целью "усиления" количества искаженных импульсов. После этого псевдослучайная последовательность подается на вход приемного тракта, где осуществляется ее обратное преобразование по установленному алгоритму (усиление, перенос в область низких частот, демодуляция, декодирование).

Сигналы псевдослучайной последовательности Fi(t) выделяют после каждого преобразования в блоках преобразования сигналов передающего и приемного трактов, как показано на фиг. 3. Из каждой псевдослучайной последовательности Fi(t) выделяют Z-разрядные сегменты. В каждом j-м Z-разрядном сегменте каждой i-й псевдослучайной последовательности Fi(t) вычисляют число единичных символов N(1)ij. Таблица состояний временных позиций Z-разрядных сегментов выделенной псевдослучайной последовательности Fi(t), при исправном состоянии диагностируемой аппаратуры цифровых систем передачи, показана на фиг. 2, а.

Затем по формулам (1), (2), (3) для каждой i-й псевдослучайной последовательности Fi(t) вычисляют, соответственно, значения математического ожидания числа единичных символов в одном сегменте псевдослучайной последовательности m(1)io, дисперсии числа появления единичных символов d(1)io и вероятности появления единичного символа p(1)io Таким образом, получают m(1)io=2.5, d(1)io=1, p(1)io=0.5.

Далее по формуле (12) вычисляют значения параметров усечения Yio и Кio, где Yio=0.5 и Кio=0.9.

Таким образом, получают R значений для каждой i-й псевдослучайной последовательности Fi(t): m(1)io, d(1)io, p(1)io, Yio и Кio, которые соответствуют параметрам исправных контролируемых блоков диагностируемой аппаратуры цифровых систем передачи.

При нарушении работоспособности i-го блока диагностируемой аппаратуры цифровых систем передачи, и, как следствие, изменения его технического состояния, на его выходе может быть получена группа событий, показанная на фиг. 2, б. Согласно вышеизложенному алгоритму вычисляют значения m(1)i = 3, d(1)i = 0.81, p(1)i = 0,6 по формулам (1), (2) и (3). Используя значение p(1)io = 0,5 по формуле (13) вычисляют значения параметров усечения Yi = 1.38 и Ki = 0.93. При этом кратность отказа (при Yi > Yio, Ki > Kio) вычисляют по формуле (15) Li=1.

Таким образом, увеличение p(1)i = 0,6 относительно значения p(1)io=0.5 и значения Yi = 1.38 относительно значения Yio = 0.5 свидетельствуют о том, что характер неисправности будет проявляться в появлении либо фиксированного единичного символа, либо перемежающего отказа в виде скользящего единичного символа, либо появлении периодического сбоя. Значение Li=1 говорит о том, что отказ не является кратным.

При нарушении работоспособности i-го блока диагностируемой аппаратуры цифровых систем передачи и, как следствие, изменении его технического состояния, на его выходе может быть получена группа событий, показанная на фиг.2, в. Согласно вышеизложенному алгоритму вычисляют значения m(1)i = 2, d(1)i = 0.81, p(1)i = 0,4 по формулам (1), (2) и (3). Используя значение p(1)io = 0,5 по формуле (13) вычисляют значения параметров усечения Yi = 0.38 и Кi = 0.73. При этом кратность отказа (при Yi < Yio, Кi < Кio) вычисляют по формуле (15) Li=1.

Таким образом, уменьшение p(1)i = 0,4 относительно значения p(1)io=0.5 и значения Кi=0.73 относительно значения Kio = 0.9 свидетельствуют о том, что характер неисправности будет проявляться в появлении либо фиксированного нулевого символа, либо перемежающего отказа в виде скользящего нулевого символа, либо появлении периодического сбоя. Значение Li=1 говорит о том, что отказ не является кратным.

При нарушении работоспособности i-го блока диагностируемой аппаратуры цифровых систем передачи и, как следствие, изменения его технического состояния, на его выходе может быть получена группа событий, показанная на фиг.2, г. Согласно вышеизложенному алгоритму вычисляют значения m(1)i = 2.5, d(1)i = 0.63, p(1)i = 0,5 по формулам (1), (2) и (3). Используя значение p(1)io = 0,5 по формуле (13) вычисляют значения параметров усечения Yi = 1.25 и Кi = 0.75, при этом кратность отказа (при Yi > Yio, Ki < Kio) вычисляют по формуле (15) Li=2.

Таким образом, увеличение значения Yi = 1.25 относительно значения Yio = 0.5 и уменьшение значения Кi = 0.75 относительно значения Кio = 0.9 свидетельствуют о том, что характер неисправности будет проявляться в появлении либо фиксированных единичного и нулевого символов, либо перемежающего отказа в виде скользящих единичного и нулевого символов, либо появлении периодического сбоя. Значение Li=2 говорит о том, что отказ является кратным, то есть, в i-м блоке диагностируемой аппаратуры цифровых систем передачи отказали два элемента.

Анализируя рассмотренные примеры, можно сделать вывод о том, что использование заявленного способа позволяет идентифицировать сбои и перемежающиеся одиночные и кратные отказы диагностируемой аппаратуры цифровых систем передачи, в отличие от способа прототипа. Это достигается вычислением параметров усечения псевдослучайной последовательности, изменение которых связано с изменением технического состояния диагностируемой аппаратуры цифровых систем передачи, характером и кратностью отказов.

Устройство диагностики технического состояния аппаратуры цифровых систем передачи, показанное на фиг. 3, состоит из блока управления 19, генератора псевдослучайной последовательности 11, аттенюатора 13, генератора шума 12, блока анализа 14, блока определения параметров 15, блока памяти 16, блока сравнения 17, блока отображения состояния 18. Выход генератора псевдослучайной последовательности 11 подключен к входу передающего тракта 1 диагностируемой аппаратуры цифровых систем передачи, выход которого подключен к входу аттенюатора 13, выходы аттенюатора 13 и генератора шума 12 подключены к входу приемного тракта 2 диагностируемой аппаратуры цифровых систем передачи, причем передающий 1 и приемный 2 тракты содержат блоки преобразования сигналов, такие как кодер 3, модулятор 4, преобразователь частоты 5 и усилитель высокой частоты 7, преобразователь частоты 8. демодулятор 9, декодер 10 соответственно.

Выходы блоков преобразования сигналов 3, 4, 5, 6, 7, 8, 9, 10 передающего и приемного трактов диагностируемой аппаратуры цифровых систем передачи подключены к информационным входам блока анализа 14. К информационному входу блока памяти 16 подключены выходы блоков анализа 14, определения параметров 15 и сравнения 17. Информационный выход блока памяти 16 подключен к информационным входам блоков определения параметров 15, сравнения 17 и блока отображения состояния 18.

Управляющие входы генератора псевдослучайной последовательности 11, блока анализа 14, блока определения параметров 15, блока памяти 16, блока сравнения 17 и блока отображения состояния 18 подключены к соответствующим выходам блока управления 19.

Генератор псевдослучайной последовательности 11 предназначен для генерирования тестовой псевдослучайной последовательности с известными параметрами Z и N. Генератор псевдослучайной последовательности строится на основе рекурентной линии задержки, известен, описан, например, в книге: Бобнев М.П. "Генерирование случайных сигналов. " Изд. 2-е перераб. и доп. М.: Энергия, 1971, стр. 175 и может быть реализован, например, на регистрах сдвига К155ИР13 (см. В.Л.Шило "Популярные цифровые микросхемы". -М.: Радио и связь. 1987, стр. 110 - 112, рис. 1.78).

Генератор шума 12 предназначен для вырабатывания шумовых радиотехнических сигналов для обеспечения требуемого соотношения сигнал/шум на входе приемного тракта диагностируемой аппаратуры цифровых систем передачи. Данное устройство, основанное на использовании вакуумного диода, описано, например, в книге: "Техническая эксплуатация, надежность средств связи и автоматизированных систем", часть 1 / Л.В.Жих, М.: Военное издательство, 1992. стр. 261. рис. 113а. На основе вакуумного диода, например, типа 2Д2С, создан генератор шума Г2-32 (см. "Измерения в электронике: Справочник". В.А.Кузнецов, В.А.Долгов и другие. -М.: Энергоатомиздат, 1987. стр. 423 - 425).

Аттенюатор 13 предназначен для уменьшения уровня мощности поступающего на вход приемного тракта сигнала псевдослучайной последовательности и представляет собой известное устройство, описанное, например, в книге: "Измерения в электронике: Справочник". В.А.Кузнецов, В.А.Долгов и другие. -М.: Энергоатомиздат, 1987, стр. 353 - 355.

Блок анализа 14, предназначенный для выделения переданной псевдослучайной последовательности на выходах контролируемых блоков преобразования сигналов передающего и приемного трактов диагностируемой аппаратуры цифровых систем передачи: кодера 3, модулятора 4, преобразователя частоты 5, усилителя мощности 6, усилителя высокой частоты 7, преобразователя частоты 8, демодулятора 9, декодера 10. Блок анализа может быть реализован в различных вариантах. В частности, его схема, представленная на фиг. 4, состоит из аналого-цифровых преобразователей 14.1 - 14.5, счетчиков единичных символов (счетчиков "1") 14.6- 14.13 и мультиплексора 14.14.

Информационные входы D аналого-цифровых преобразователей 14.1-14.5 подключены к выходам модулятора 4, преобразователя частоты 5, усилителя мощности 6, усилителя высокой частоты 7, преобразователя частоты 8. Информационные входы D счетчиков "1" 14.6 - 14.13 подключены соответственно к выходам кодера 3, аналого-цифровых преобразователей 14.1-14.5, демодулятора 9, декодера 10, их выходы подключены к информационным входам мультиплексора 14.14. Выход мультиплексора 14.14 подключен к информационному входу блока памяти 16.

Аналого-цифровые преобразователи 14.1-14.5 предназначены для преобразования псевдослучайной последовательности, которая имеет аналоговый вид, в цифровую последовательность. Схемы аналого-цифровых преобразователей 14.1-14.5 идентичны, известны и приведены, например, в книге: В.А.Батушев, В.Н. Вениаминов и др. "Микросхемы и их применение: Справочное пособие". -М.: Радио и связь, 1983, стр. 193 - 198. рис. 6.15.

Счетчики единичных символов 14.6-14.13 предназначены для определения числа единичных символов в каждом j-м Z-разрядном сегменте выделенных псевдослучайных последовательностей N(1)ij и представления этого числа в двоичном коде. Схема счетчиков известна, приведена, например, в книге: А.А. Сикарев, О. Н.Лебедев "Микроэлектронные устройства формирования и обработки сложных сигналов" -М.: Радио и связь, 1983, стр, 128, рис. 518 и может быть реализована, например, на микросхеме К176ИЕ2 (см. В.Л. Шило "Популярные цифровые микросхемы". -М.: Радио и связь, 1987, стр.235 - 236, рис. 2.36.а).

Мультиплексор 14.14 предназначен для поочередной коммутации выходов счетчиков "1" 14.6-14.13 на информационный вход D блока памяти 16. Схема мультиплексора известна, описана, например, в книге: В.С.Гутников, В.В.Лопатин и др. "Электронные устройства информационно-измерительной техники: Учебное пособие". - Л. : ЛПИ им. Калинина, 1980, стр. 70-72, и может быть реализованы, например, на микросхемах К531КП2 (см. В.Л.Шило "Популярные цифровые микросхемы". -М.: Радио и связь, 1987, стр. 143-145, рис. 1.103).

Блок определения параметров 15 предназначен для определения значений статистических параметров выделенных псевдослучайных последовательностей: математического ожидания m(1), дисперсии d(1), вероятности появления единичного символа p(1), а также значений параметров усечения Y и К. Его структурная схема может быть представлена в нескольких вариантах. В частности, схема блока определения параметров 15, представленная на фиг. 5, состоит из сумматоров 15.3, 15.6, 15.8, умножителя 15.2, делителей 15.4, 15.5, 15.7, 15.9, 15.10. 15.12, вычитателей 15.1, 15.11, 15.13.

Входы А вычитателя 15.1 и сумматора 15.8, входы B делителей 15.5 и 15.12 подключены к выходу блока памяти 16. Выход вычитателя 15.1 подключен к входу А перемножителя 15.2, выход которого подключен к входу А сумматора 15.3. Вход А делителя на N 15.4 подключен к выходу сумматора 15.3, а его выход подключен к входам А делителей 15.5 и 15.12. Выход делителя 15.5 подключен к входу А сумматора 15.6 выход которого подключен к входу А делителя на Z 15.7. Выход сумматора 15.8 подключен к входу А делителя на N 15.9, выход которого подключен к входам B вычитателей 15.1, 15.13, сумматора 15.6 и делителя на Z 15.10 выход которого подключен к входу B вычитателя 15.11. Выход делителя 15.12 подключен к входу B вычитателя 15.13. Выходы делителей на Z 15.7, 15.10. вычитателей 15.11 и 15.13 подключены к информационному входу блока памяти 16.

Сумматоры 15.3, 15.6. 15.8 предназначены для суммирования чисел, представленных в двоичном коде.

Вычитатели 15.1, 15.11, 15.13 предназначены для получения значения разности чисел, представленных в двоичном коде.

Умножитель 15.2 предназначен для выполнения операции умножения чисел, представленных в двоичном коде.

Делители 15.4, 15.5, 15.7, 15.9, 15.10 и 15.12 предназначены для выполнения операции деления числа, представленного в двоичном коде на известную константу или переменное число, также представленное в двоичном коде.

Блок памяти 16 предназначен для записи значений p(1), po(1), 1-po(1), Y, Yo, К, Кo и L, хранения их и выдачи требуемых значений в блок определения параметров 15, блок сравнения 17 и блок отображения состояния 18. В качестве блока памяти может быть использовано устройство, схема построения которого известна и приведена, например, в книге: В.А.Батушев, В.Н.Вениаминов и др. "Микросхемы и их применение: Справочное пособие". -М.: Радио и связь, 1983. стр. 175, рис. 5.12, и может быть реализована, например, на микросхеме памяти К537РУ8 (см. В.И.Корнейчук, В.П.Тарасенко "Вычислительные устройства на микросхемах: Справочник". -К.: Техника, 1988, стр. 85 - 87).

Блок сравнения 17 предназначен для сравнения измеренных значений вероятности появления единичных символов p(1), параметров усечения Y и K с известными значениями po(1), Yo и Ko и на основе этого сравнения вычисления значения кратности отказов L и принятия решения о характере неисправности. Вариант схемы блока сравнения 17 может быть представлен на фиг. 6. Блок сравнения 17 состоит из компараторов 17.1-17.3, шифратора 17.4. вычитателей 17.5 и 17.6, сумматоров-вычитателей 17.7 и 17.9, умножителя 17.8. делителя 17.10 и электронного коммутатора 17.11.

Входы А и B компараторов 17.1 - 17.3, вычитателей 17.5 и 17.6 подключены к выходу блока памяти 16. Выходы G1(A<B). G2(A=B), G3(A>B) компараторов 17.1- 17.3 подключены к информационным входам D1 - D9 шифратора 17.1. выход которого подключен к входам выбора режима X сумматоров-вычитателей 17.7 и 17.8 и делителя 17.10, управляющему входу С электронного коммутатора 17.11 и информационному входу D блока памяти 16. Выход вычитателя 17.6 подключен к входу B сумматора-вычитателя 17.7, выход которого подключен к входу А умножителя на Z 17.8. Входы А и В сумматора- вычитателя 17.9 подключены соответственно к выходам умножителя 17.8 и вычитателя 17.5, а его выход подключен к входу А делителя на 2 17.10 и входу А электронного коммутатора 17.11. Выход делителя 17.10 подключен к входу В электронного коммутатора 17.11, выход которого подключен к информационному входу D блока памяти 16.

Компараторы 17.1-17.3 предназначены для сравнения значений чисел, представленных в двоичном коде: p(1) и po(1), Y и Yo, K и Ko. Схема компараторов известна и может быть реализована, например, на микросхеме К555СП1 (см. В. Л. Шило "Популярные цифровые микросхемы". -М.: Радио и связь, 1987, стр. 183- 184, рис. 1.134).

Шифратор 17.4 предназначен для принятия решения о характере отказа. Схема шифратора известна, описана, например, в книге: Токхейм Р." Основы цифровой электроники: Пер. с англ." -М.: Мир,1988, стр. 119 - 120, рис. 5.5, и может быть реализована, например, на микросхеме КМ555ИВЗ (см. В.Л.Шило "Популярные цифровые микросхемы". -М.: Радио и связь, 1987, стр. 140- 142. рис. 1.101).

Вычитатели 17.5 и 17.6 предназначены для получения значения разности чисел, представленных в двоичном коде.

Сумматоры-вычитатели 17.7 и 17.9 предназначены для получения суммы или разности чисел, представленных в двоичном коде.

Схемы сумматоров 15.3. 15.6 и 15.8, вычитателей 15.1, 15.11, 15.13, 17.5 и 17.6, сумматоров-вычитателей 17.7 и 17.9 известны, описаны, например, в книге: Токхейм Р. "Основы цифровой электроники: Пер. с англ." -М.: Мир, 1988, стр. 231 - 232, рис. 9.18, и могут быть реализованы, например, на микросхеме К155ИП4 (см. В.А.Батушев, В.Н.Вениаминов и др. "Микросхемы и их применение: Справочное пособие". -М.: Радио и связь, 1983, стр. 129 -130).

Умножитель 17.8 предназначен для выполнения операции умножения чисел, представленных в двоичном коде. Схема умножителей 15.2 и 17.8 известна, приведена, например, в книге: Токхейм Р. "Основы цифровой электроники: Пер. с англ. " -М.: Мир, 1988, стр. 236 - 240, рис. 9.26, и может быть реализована, например, на микросхеме К155ИП4 (см. В.А.Батушев, В.Н.Вениаминов и др. "Микросхемы и их применение: Справочное пособие". -М.: Радио и связь, 1983, стр. 129 - 130).

Делитель 17.10 предназначен для выполнения операции деления числа, представленного в двоичном коде на известную константу, также представленную в двоичном коде. Схема делителей 15.4, 15.5, 15.7, 15.9, 15.10 и 15.12 и 17.10 известна, описана, например, в книге: В. С. Гутников, В.В.Лопатин и др. "Электронные устройства информационно-измерительной техники: Учебное пособие". - Л. : ЛПИ им. Калинина, 1980, стр. 44 - 46, 48 - 50, рис. 21,a, 24, и может быть реализована, например, на микросхемах К155ИЕ8, К155ИЕ2 (см. В.Л. Шило "Популярные цифровые микросхемы". -М.: Радио и связь, 1987, стр. 94 - 97. рис. 1.69).

Электронный коммутатор 17.11, показанный на фиг. 7, предназначен для обеспечения считывания двоичного сигнала с выхода сумматора-вычитателя 17.9 (вход А) или делителя 17.10 (вход В) на информационный вход D блока памяти 16 в соответствии с управляющим сигналом на входе С. По физической сущности электронный коммутатор 17.1 1 представляет собой элементарный трехпозиционный управляемый переключатель. Схема управляемого переключателя 17.11.1 известна и приведена, например, в книге: В.Л.Шило "Популярные микросхемы КМОП. Справочник." -М.: Ягуар. 1993. стр. 22.

Устройство отображения состояния 18 предназначено для отображения технического состояния диагностируемой аппаратуры цифровых систем передачи. Схема устройства известна, описана, например, в книге: Токхейм Р. "Основы цифровой электроники: Пер. с англ." -М.: Мир, 1988, стр. 124 - 125, рис. 5.9 и может быть реализована, например, на микросхеме К514ИД2 и семисегментном индикаторе AЛ305A (см. В.А.Батушев, В.Н.Вениаминов и др. "Микросхемы и их применение: Справочное пособие". -М. : Радио и связь, 1983, стр.209 -210, рис. 7.4,в).

Блок управления 19 предназначен для выработки управляющих сигналов с целью реализации требуемого алгоритма преобразования сигнала и может быть реализован на микропроцессоре TMS32010 (см., например, "Цифровой процессор обработки сигналов TMS32010 и его применение." /Под ред. А.А.Ланнэ. Л: ВАС, 1990. -296 с. ). Обычно блок управления представляет собой последовательностные логические схемы и могут быть синтезированы по известным правилам (см. В. С. Гутников, В.В.Лопатин и др. "Электронные устройства информационно-измерительной техники: Учебное пособие". - Л.: ЛПИ им. Калинина, 1980, стр. 73 - 76, рис. 42; В.С.Гутников "Интегральная электроника в измерительных устройствах." -Л.: Энергия, 1980. -248 с.).

Заявленное устройство диагностики состояния аппаратуры цифровых систем передачи работает следующим образом.

На первом этапе производится определение значений вероятности появления единичных символов p(1)io и параметров усечения Yio и Kio при исправном состоянии диагностируемой аппаратуры цифровых систем передачи и запоминание этих значений.

С поступлением управляющего сигнала из блока управления 19 "Разрешение передачи" генератор псевдослучайной последовательности 11 вырабатывает псевдослучайную последовательность Fo(t), которая поступает на вход кодера 3 передающего тракта 1, при этом передача Z-разрядных сегментов псевдослучайной последовательности осуществляется N раз. Переданная псевдослучайная последовательность Fo(t) подвергается ряду стандартных преобразований в кодере 3, модуляторе 4, преобразователе частоты 5, усилителе мощности 6 передающего тракта 1, после чего ослабляется в аттенюаторе 13 и смешивается с сигналом шума, поступающем с выхода генератора шума 12. В усилителе высокой частоты 7, преобразователе частоты 8, демодуляторе 9 и декодере 10 приемного тракта 2 производятся обратные преобразования переданной псевдослучайной последовательности.

На выходе каждого i-го, где i = 1, 2, 3,...R, контролируемого блока диагностируемой аппаратуры цифровых систем передачи производится выделение преобразованной псевдослучайной последовательности. Выделенные псевдослучайные последовательности F1(t), F2(t), F3(t), F4(t), F5(t), F6(t), F7(t) и F8(t) поступают на соответствующие информационные входы блока анализа 14, показанного на фиг.4.

Последовательности с выходов модулятора 4, преобразователя частоты 5, усилителя мощности 6, усилителя высокой частоты 7 и преобразователя частоты 8, на выходах которых сигнал имеет аналоговый вид, подаются на информационные входы D соответствующих аналого-цифровых преобразователей 14.1-14.5, где они приводятся к цифровому виду.

Псевдослучайные последовательности, имеющие цифровой вид, с выходов кодера 3, аналого-цифровых преобразователей 14.1-14.5, демодулятора 9 и декодера 10 подаются на соответствующие информационные входы D счетчиков единичных символов (счетчиков "1") 14.6-14.13. По управляющим сигналам "Загрузка", поступающим на установочные входы С счетчиков "1" 14.6-14.13 начинается подсчет числа единичных символов ("1") Nij(1) в каждом j-м Z-разрядном сегменте в каждой i-й выделенной псевдослучайной последовательности.

После поступления каждого Z-го символа сегмента в каждой i-й псевдослучайной последовательности производится считывание значений счетчиков "1" 14.6 - 14.13 путем подачи управляющих сигналов "Код адреса" на вход А мультиплексора 14 и вход X блока памяти 16 при наличии сигнала "Запись" на входе выбора режима Z блока памяти 16. Значения чисел "1" Nij(1), представленных в двоичном коде, с выходов счетчиков "1" 14.6-14.13 поступают на информационные входы X1 - X8 мультиплексора 14.14 соответственно, и в соответствии с значением кодовой комбинации на адресном входе А, вырабатываемой блоком управления 19, поочередно коммутируются на выход Y мультиплексора 14.14.

С выхода мультиплексора 14.14 Nij(1) поступает на информационный вход D блока памяти 16, показанного на фиг. 3, и, в соответствии с кодовой комбинацией на адресном входе X и управляющем входе Z, производится запись значений Nij(1) в соответствующие ячейки памяти блока памяти 16 в следующей последовательности: N11(1), N21(1), . .., Ni1(1),..., NR1(1), N12(1), N22(1),..., Ni2(1), . . . , NR2(1), N1j(1), N2j(1),..., Nij(1),..., NRj,(1), N1N(1),..., N2N(1), . . ., NiN(1),..., NRN(1), после чего происходит обнуление счетчиков "1" по сигналу "Очистка" на входах С счетчиков 14.6 - 14.13.

После занесения в блок памяти 16 значений всех чисел "1" Nij(1) в блоке определения параметров производится вычисление значений математического ожидания mio(1), дисперсии dio(1) числа "1" в Z-разрядном сегменте и вероятности появления "1" pi(1) в j-й позиции Z-разрядного сегмента и по результатам вычисления mio(1), dio(1) и pio(1) определяют значения параметров усечения Yio и Кio.

С выхода блока памяти 16 в соответствии с сигналами "Код адреса" на адресном входе X и "Считывание" на управляющем входе Z вырабатываемыми блоком управления 19, производится последовательное считывание значений Nij(1), принадлежащей i-й последовательности, и подача этих значений на вход А сумматора 15.8 блока определения параметров 15, показанного на фиг. 5, при разрешающем сигнале "Загрузка" на входе С. В сумматоре 15.8 производится суммирование всех j-x значений. Nij(1) i-й последовательности, то есть производится вычисление

Сигнал с выхода сумматора 15.8 подается на вход А делителя 15.9 при разрешающем сигнале "Загрузка", вырабатываемом блоком управления 19, на управляющем входе С. В делителе выполняется операция деления на число N, то есть производится вычисление

Значение m(1)io с выхода делителя 15.9 подается на вход А делителя 15.10, вход B вычитателя 15.1, вход B сумматора 15.7 и вход А вычитателя 15.13. При разрешающем сигнале "Загрузка", вырабатываемом блоком управления 19, на управляющем входе С, в делителе 15.10 выполняется операция деления на число Z, то есть производится вычисление  после чего, при наличии сигнала "Считывание" на входе С, производится подача ее на вход В вычитателя 15.11 и информационный вход D блока памяти 16, в котором, в соответствии с сигналами "Код адреса" адресном входе X и "Запись" на управляющем входе Z, вырабатываемыми блоком управления 19, производится запись значений p(1)io в соответствующие ячейки памяти. В вычитателе 15.11, на входе А которого присутствует двоичное значение "1", производится вычисление 1 - p(1)io при наличии сигнала "загрузка" на входе С.

после чего, при наличии сигнала "Считывание" на входе С, производится подача ее на вход В вычитателя 15.11 и информационный вход D блока памяти 16, в котором, в соответствии с сигналами "Код адреса" адресном входе X и "Запись" на управляющем входе Z, вырабатываемыми блоком управления 19, производится запись значений p(1)io в соответствующие ячейки памяти. В вычитателе 15.11, на входе А которого присутствует двоичное значение "1", производится вычисление 1 - p(1)io при наличии сигнала "загрузка" на входе С.

Значение 1 - p(1)io по сигналу "Считывание" на входе С считывается и подается на информационный вход D блока памяти 16, в котором, в соответствии с сигналами "Код адреса" на адресном входе X и "Запись" на управляющем входе Z, вырабатываемыми блоком управления 19, производится запись значений 1 - p(1)io в соответствующие ячейки памяти.

После вычисления значения m(1)io и подачи его на вход В вычитателя 15.1 производится вычисление значения дисперсии d(1)io С выхода блока памяти 16 в соответствии с сигналами "Код адреса" на адресном входе X и "Считывание" на управляющем входе Z, вырабатываемыми блоком управления 19, производится последовательное считывание значений Nij(1), принадлежащей i-й последовательности, и подача этих значений на вход А вычитателя 15.1 при разрешающем сигнале "Загрузка" на входе С. В вычитателе 15.1 производится вычисление N(1)ij - m(1)io.

Сигнал с выхода вычитателя 15.1 подается на вход умножителя 15.2, в котором производится вычисление [N(1)ij - m(1)io]2, результат которого подается на вход сумматора 15.3, при разрешающем сигнале "Загрузка" на его входе С.

После этого производится обнуление вычитателя 15.1 и умножителя 15.2 по сигналу "Очистка" на управляющих входах С

В сумматоре 15.3 производится вычисление  результат которого подается на вход А делителя 15.4 при разрешающем сигнале "Загрузка" на его входе С.

результат которого подается на вход А делителя 15.4 при разрешающем сигнале "Загрузка" на его входе С.

В делителе 15.4 производится вычисление  После вычисления d(1)io по сигналу "Считывание" на управляющем входе С производится считывание значения d(1)io

После вычисления d(1)io по сигналу "Считывание" на управляющем входе С производится считывание значения d(1)io

Значение d(1)io подается на входы А делителей 15.5 и 15.12. На вход В делителя 15.5, при разрешающем сигнале "Загрузка" на входе С, с выхода блока памяти 16, в соответствии с сигналами "Код адреса" на адресном входе X и "Считывание" на управляющем входе Z, вырабатываемыми блоком управления 19, подается значение p(1)io. В делителе 15.5 производится вычисление d(1)io / p(1)io, результат которого подается на вход В сумматора 15.6,

В сумматоре 15.6. при разрешающем сигнале "Загрузка" на входе С, на вход В которого подано значение m(1)io, производится вычисление m(1)io + d(1)io / p(1)io.

Результат суммирования подается на вход А делителя на Z 15.7, в котором, при разрешающе сигнале "Загрузка" на входе С, производится вычисление Кio = (mio(1) + dio(1)/pMio(1))/Z. После вычисления Кio по сигналу "Считывание" на управляющем входе С производится считывание значения Кio подача значения Kio на информационный вход D блока памяти 16, в котором, в соответствии с сигналами "Код адреса" на адресном входе X и "Запись" на управляющем входе Z, вырабатываемыми блоком управления 19, производится запись значений Кio в соответствующие ячейки памяти.

Параллельно с вычислением значения Kio производится вычисление значения Yio. На вход В делителя 15.12 с выхода блока памяти 16, в соответствии с сигналами "Код адреса" на адресном входе X и "Считывание" на управляющем входе Z, вырабатываемыми блоком управления 19, подается значение 1-p(1)io, на вход А которого подано значение d(1)io. В делителе 15.12, при разрешающем сигнале "Загрузка" на входе С, производится вычисление d(1)io/(1- -p(1)io), результат которого подается на вход В вычитателя 15.13. В вычитателе 15.13, при сигнале "Загрузка" на входе C, на вход А которого подано значение m(1)io производится вычисление Yio = mio(1)-dio(1)/(1-pio(1)). После вычисления Yio по сигналу "Считывание" на управляющем входе С производится считывание значения Yio и подача значения Yio на информационный вход D блока памяти 16, в котором, в соответствии с сигналами "Код адреса" на адресном входе X и "Запись" на управляющем входе Z, вырабатываемыми блоком управления 19, производится запись значений Yio в соответствующие ячейки памяти.

Вычисления, производимые в блоке определения параметров 15, производятся R раз для каждой i-й последовательности и все результаты вычислений заносятся в блок памяти 16.

На втором этапе, характеризующимся наступлением неработоспособного состояния диагностируемой аппаратуры цифровых систем передачи (например, случаи описанные на фиг. 2, б, в, г), производится вычисление значений m(1)i, d(1)i и p(1)i и параметров усечения Yi, Кi и Li

Вычисление значений m(1)i, d(1)i и p(1)i и параметров усечения Yi и Ki производится по вышеизложенному алгоритму, за исключением некоторых операций: после вычисления p(1)i и записи ее значения в блок памяти 16 вычисление 1-p(1)i в вычитателе 15.11 не производится; при вычислении значений Yi и Кi в делителях 15.5, 15.12 используются значения p(1)io и 1-p(1)io, вычисленные на первом этапе.

С выхода блока памяти 16, в соответствии с сигналами "Код адреса" на адресном входе X и "Считывание" на управляющем входе Z, вырабатываемыми блоком управления 19, на входы А и В компараторов 17.2, 17.3 и 17.4 и вычитателей 17.5 и 17.6 блока сравнения 17 подаются значения p(1)io и p(1)i, Yio и Yi, Kio и Кi соответственно. С выходов G1(A<B), G2(A=B), G3(A>B) компараторов 17.2 - 17.4 результаты сравнения А и В, при разрешающих сигналах "Загрузка" на входах С, подаются на информационные входы D1 - D9 шифратора 17.1, при разрешающем сигнале "Загрузка" на его входе С.

Значение кодовой комбинации на выходе шифратора 17.1 считывается по сигналу "Считывание", поступающему на управляющий вход С и подается на информационный вход D блока памяти 16 в соответствии с сигналами "Код адреса" на адресном входе X и "Запись" на управляющем входе Z, вырабатываемыми блоком управления 19. Кодовая комбинация на выходе шифратора 17.4 несет информацию о характере неисправности контролируемого блока преобразования сигналов передающего и приемного трактов диагностируемой аппаратуры цифровых систем передачи и является управляющим сигналом, который поступает на входы выбора режима X сумматоров-вычитателей 17.7 и 17.9, делителя 17.10 и на управляющий вход С электронного коммутатора 17.11.

Вычисление кратности отказов Li, производится по одному из трех вариантов.

Вариант 1. Пусть Y > Yo, K < Ko. Тогда сумматоры-вычитатели 17.7 и 17.9, в соответствии кодовой комбинацией на их входах X, будут работать как вычитатель и сумматор соответственно, а делитель 17.10 будет заперт, в электронном коммутаторе на выход подключен вход А. В вычитателях 17.5 и 17.6, при наличии разрешающих сигналов "Загрузка" на входах С, производится вычисление Yo-Y и Кo-К соответственно. Сигнал с выхода вычитателя 17.6 подается на вход B сумматора-вычитателя 17.7, на входе А которого присутствует "1". В сумматоре-вычитателе 17.7, при наличии разрешающего сигнала "Загрузка" на входе С, производится вычисление: 1-(Кo-К), после чего его результат подается на вход А умножителя на Z 17.8. В умножителе 17.8, при наличии разрешающего сигнала "Загрузка" на входе С, производится вычисление (1-(Ko-K))•Z. С выхода умножителя сигнал подается на вход А сумматора-вычитателя 17.9, на вход В которого поступает сигнал с выхода вычитателя 17.5. В сумматоре-вычитателе 17.9, при наличии разрешающего сигнала "Загрузка" на входе С, производится вычисление Li=(Y0-Y) + (1-(K0-K))•Z, после чего значение Li, подается на вход А электронного коммутатора 17.11, а с его выхода - на вход D блока памяти 16, в соответствии с сигналами "Код адреса" на адресном входе X и "Запись" на управляющем входе Z, вырабатываемыми блоком управления 19.

Вариант 2. Пусть Y < Yo, K < Ko. Тогда сумматоры-вычитатели 17.7 и 17.9, в соответствии кодовой комбинацией на их входах X, будут работать как вычитатель и сумматор соответственно, а делитель 17.10 будет открыт, в электронном коммутаторе на выход подключен вход В. В этом случае выполняются все операции согласно варианту 1, но сигнал L1 поступает на вход делителя 17.10, в котором, при наличии разрешающего сигнала "Загрузка" на входе С, производится вычисление Li=[(Yo-Y) + (1-(Ko-K))•Z]/2.

После чего значение Li подается на вход B электронного коммутатора 17.11, а с его выхода - на вход D блока памяти 16 в соответствии с сигналами "Код адреса" на адресном входе X и "Запись" на управляющем входе Z, вырабатываемыми блоком управления 19.

Вариант 3. Пусть Y > Yo, K > Ko. Тогда сумматоры-вычитатели 17.7 и 17.9 при поступлении единичного импульса на входы выбора режима будут работать как сумматор и вычитатель соответственно, а на делитель 17.10 поступает разрешающий сигнал на управляющий вход. В этом случае, в отличие от варианта 2, в сумматоре-вычитателе 17.7 производится вычисление 1+(Кo-К), а в сумматоре-вычитателе 17.9 производится вычисление (Yo-Y) - (1-(Ko-K))•Z, тогда на выходе делителя 17.10 получим значение

Li=[(1-(Ko-K))•Z - (Yo- Y)+]/2=[(Y-Yo) + (1-(K-Ko))•Z]/2.

После чего значение Li подается на вход В электронного коммутатора 17.11, а с его выхода - на вход D блока памяти 16 в соответствии с сигналами "Код адреса" на адресном входе X и "Запись" на управляющем входе Z, вырабатываемыми блоком управления 19.

После этого из блока памяти 16, в соответствии с сигналами "Код адреса" на адресном входе X и сигналом "Считывание" на управляющем входе Z, считывается совокупность сигналов, представляющих собой кодовые комбинации, характеризующие техническое состояние (неисправный блок, характер неисправности и кратность отказа) диагностируемой аппаратуры цифровых систем передачи и подается на информационный вход блока отображения состояния 18 в котором, при наличии разрешающего сигнала "Загрузка" на входе С, происходит дешифрация входных кодовых комбинаций и отображение технического состояния диагностируемой аппаратуры цифровых систем передачи с помощью семисегментных индикаторов.

Эффективность заявленного технического решения заключается в следующем. Сокращение сроков достоверной оценки состояния аппаратуры цифровых систем передачи позволяет существенным образом влиять на производительность систем передачи. Так, проверка их работоспособности известными методами требует при такой же точности оценки более 5 минут. В процессе обеспечения связи, например, для систем синхронной цифровой иерархии за 1 секунду нижнего их уровня при передаче агрегатов СТМ1 передается 150 Мбит/с информационных и управляющих импульсов (см., например, А.В.Нетес "Основные принципы синхронной цифровой иерархии" // Сети и системы, N6, 1996. -с.59 - 62), следовательно, сокращение времени простоя цифровых систем передачи позволяет существенно повысить их производительность. Идентификация характера и кратности отказа (сбоя) также повышает их ремонтопригодность, что ведет к возрастанию их эксплуатационной надежности.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДИАГНОСТИКИ СОСТОЯНИЯ АППАРАТУРЫ СВЯЗИ | 1997 |

|

RU2124266C1 |

| УСТРОЙСТВО ДИАГНОСТИРОВАНИЯ ЦИФРОВЫХ СИСТЕМ ПЕРЕДАЧИ | 2005 |

|

RU2299513C2 |

| УСТРОЙСТВО ДИАГНОСТИКИ СОСТОЯНИЯ СИСТЕМ СВЯЗИ | 1996 |

|

RU2103819C1 |

| СПОСОБ ШИФРОВАНИЯ/ДЕШИФРОВАНИЯ СООБЩЕНИЙ ХЭШИРУЮЩЕЙ ФУНКЦИЕЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1998 |

|

RU2138126C1 |

| СПОСОБ КРИПТОЗАЩИТЫ СИСТЕМЫ ТЕЛЕКОММУНИКАЦИОННЫХ ТЕХНОЛОГИЙ | 1995 |

|

RU2077113C1 |

| СПОСОБ СКРЕМБЛИРОВАНИЯ АНАЛОГОВОГО СИГНАЛА И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1997 |

|

RU2123764C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1998 |

|

RU2132595C1 |

| МНОГОКАНАЛЬНОЕ АДАПТИВНОЕ РАДИОПРИЕМНОЕ УСТРОЙСТВО | 1994 |

|

RU2107394C1 |

Предлагаемые технические решения объединены единым изобретательским замыслом и относятся к области радиотехники, а именно к области диагностики технического состояния аппаратуры цифровых систем передачи, и, в частности, могут использоваться при определении вида технического состояния аппаратуры цифровых систем передачи с обнаружением и локализацией различных детекторов. Целью изобретения заявленных технических решений является разработка способа и устройства диагностики состояния аппаратуры цифровых систем передачи, позволяющего обнаруживать сбои, одиночные и кратные отказы аппаратуры цифровых систем передачи. Поставленная цель достигается тем, что способ диагностики аппаратуры цифровых систем передачи предусматривает дополнительное выделение переданной псевдослучайной последовательности на выходах контролируемых блоков диагностируемой аппаратуры цифровых систем передачи, вычислении ее статистических характеристик и на основе этих характеристик определение параметров усечения, которые позволяют с требуемой точностью и достоверностью идентифицировать техническое состояние аппаратуры цифровых систем передачи. 2 с. п. ф-лы, 9 ил.

и по полученным результатам определяют параметры возможных технических состояний аппаратуры цифровых систем передачи.

| Устройство диагностики состояния аппаратуры цифровых систем передачи | 1990 |

|

SU1734219A1 |

| RU 2015622 C1, 30.06.94 | |||

| ЭЛЕКТРОВВОД В ГЕРЛШТИЧНЫЕ СОСУДЫ | 0 |

|

SU371445A1 |

| 0 |

|

SU344624A1 | |

| Автоматический огнетушитель | 0 |

|

SU92A1 |

| US 4580016 A, 01.04.84. | |||

Авторы

Даты

1999-06-27—Публикация

1998-01-05—Подача