Предлагаемое изобретение относится к области геофизического приборостроения и может быть использовано в качестве аналого-цифрового преобразователя в исследовательской сейсморегистрирующей аппаратуре.

Известны аналого-цифровые преобразователи (АЦП), применяемые в сейсморегистрирующей аппаратуре. Устройства данного типа работают по методу импульсно-кодовой модуляции (ИКМ). К наиболее распространенным относятся n-разрядные преобразователи последовательного приближения (поразрядного взвешивания). Технология их изготовления в настоящее время достаточно хорошо проработана, и АЦП подобного типа обеспечивают широкий динамический диапазон преобразования входных аналоговых сигналов. Вместе с тем в схеме таких АЦП присутствует большое количество прецизионных компараторов, ключевых элементов и других высокоточных аналоговых компонент, каждый из которых вносит некоторое искажение в преобразованный аналоговый сигнал. В особенности такие искажения - шумы - сказываются при преобразовании сигналов малого уровня. Иными словами, чтобы получить в АЦП, работающем по методу ИКМ, хорошее отношение сигнал/шум, необходимо увеличить число n - разрядов преобразования, но это ведет к увеличению искажающих шумов, для борьбы с которыми требуется введение дополнительных, компенсирующих данные шумы схем, а это в свою очередь значительно усложняет АЦП.

Известны также АЦП для сейсморегистрирующей аппаратуры, в основе работы которых лежит принцип дельта-модуляции. Суть данного метода заключается в том, что аналоговый сигнал подвергается дискретизации с частотой, в несколько десятков или сотен раз превышающей частоту Найквиста, а также квантованию по уровню одним строго фиксированным шагом квантования. В каждый период тактовой частоты происходит сравнение предыдущей выборки с настоящей, а результат сравнения (превышение или непревышение данных выборок относительно друг друга) поступает на выход в виде одного бита информации (логического нуля или единицы). Кроме того, данная однобитовая цифровая последовательность поступает в петлю обратной связи дельта-модулятора (ДМ), где из нее восстанавливается исходный аналоговый сигнал, который в каждый период квантования сравнивается с входным. Как видно, дельта-модулятор содержит небольшое число аналоговых элементов, что позволяет добиться отношения сигнал/шум преобразователя более 100 дБ, а это эквивалентно преобразованию по ИКМ-методу с числом двоичных разрядов n = 16 - 18.

Вместе с тем в ДМ-преобразователе наряду с шумами дробления, связанными с искажающим влиянием элементов схемы, возникают специфические, свойственные только данному методу искажения типа перегрузки по крутизне, которые проявляются в моменты времени, когда восстановленный из цифровой последовательности сигнал не успевает отслеживать входной сигнал. Такие искажения ведут к значительным изменениям амплитуды и фазы восстановленного из цифровой последовательности сигнала. С целью уменьшения искажений типа перегрузки по крутизне на входе дельта-модулятора установлены амплитудный ограничитель и интегрирующая ступень. Однако совокупность этих блоков лишь удовлетворительно ограничивает наклон входного сигнала, тогда как в схеме дельта-модулятора требуется полное устранение перегрузки по крутизне, поскольку после искажения такого рода исходный сигнал не может быть восстановлен. Чтобы устранить перегрузку по крутизне, возможно применение входного аналогового фильтра низкой частоты (ФНЧ) седьмого - восьмого порядка, обеспечивающего крутизну среза входного сигнала более 40 дБ/окт. Однако такой фильтр сложен как в изготовлении, так и в настройке. Кроме того, для его перестройки требуется замена большого числа аналоговых элементов (резисторов, конденсаторов).

Целью изобретения является устранение искажений типа перегрузки по крутизне, возникающих в дельта-модуляторе при резком возрастании амплитуды или частоты входного сигнала. Настоящая цель реализуется путем введения в дельта-модулятор дополнительной петли обратной связи, состоящей из последовательно соединенных гребенчатого фильтра и фильтра низкой частоты.

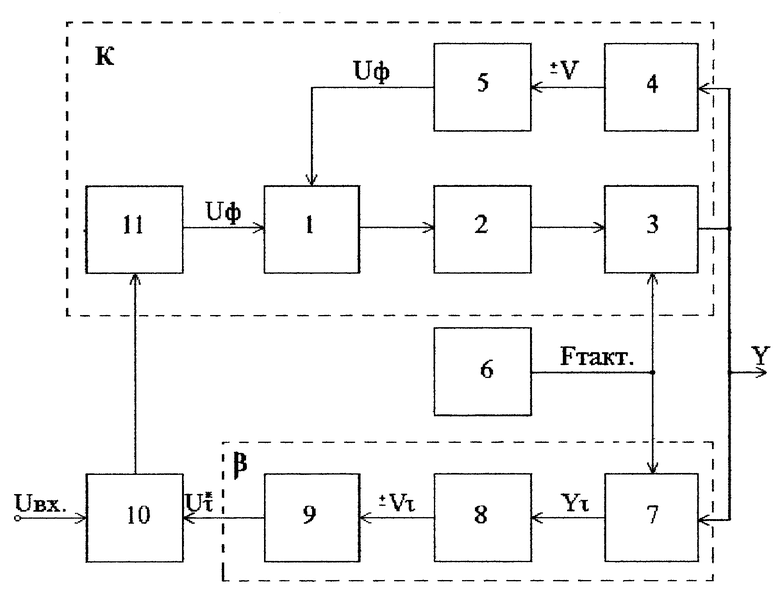

На чертеже показана структурная схема фильтрующего аналого-цифрового преобразователя с использованием дельта-модуляции.

Аналого-цифровой преобразователь содержит последовательно соединенные устройство 1 вычитания, компаратор 2, триггер 3, первый преобразователь 4 полярности и первый интегратор 5, выход которого соединен с первым входом устройства 1 вычитания, последовательно соединенные цифровую линию 7 задержки, второй преобразователь 8 полярности, второй интегратор 9, сумматор 10 и ФНЧ 11, выход которого соединен с вторым входом устройства 1 вычитания, а также генератор 6 тактовой частоты, выход которого соединен с тактовым входом триггера 3 и управляющим входом цифровой линии 7 задержки, входом АЦП является второй вход сумматора 10, а выходом - выход триггера 3, соединенный также с информационным входом цифровой линии 7 задержки.

Устройство работает следующим образом. Собственно дельта-модулятор, состоящий из устройства 1 вычитания, компаратора 2, триггера 3, преобразователя 4 полярности и интегратора 5, под воздействием тактовой частоты Fтакт. генератора 6 преобразует напряжение Uф. в однобитовую цифровую последовательность Y, которая с выхода триггера 3 поступает на выход АЦП, а также на вход цифровой линии 7 задержки. Здесь происходит задержка каждого бита информации на время τ и далее, также как в дельта-модуляторе, из цифровой последовательности Yτ на втором преобразователе 8 полярности и втором интеграторе 9 восстанавливается аналоговый сигнал U*τ, задержанный по отношению к входному Uвх.на время τ. Результат суммирования сигналов U*τ и Uвх. в сумматоре 10 далее дополнительно фильтруется в ФНЧ 11 и в виде сигнала Uф. поступает на вход дельта-модулятора. Таким образом, цифровая линия 7 задержки, второй преобразователь 8 полярности, второй интегратор 9, сумматор 10 и ФНЧ 11 образуют петлю обратной связи, реализующую алгоритм гребенчатого фильтра, т. е. максимальное подавление сигнала на частотах π/τ, 3π/τ, 5π/τ и т.д., причем ФНЧ 11 обеспечивает дополнительную фильтрацию высокочастотных сигналов, начиная с частоты π/τ, и нормальную работу преобразователя (устранение искажения типа перегрузки по крутизне) в диапазоне частот входного сигнала от 0 до π/τ .

При конкретной реализации устройства необходимо учитывать, что системы с описанной петлей обратной связи склонны к самовозбуждению при Kβ≥1[2], где K и β - коэффициенты передачи соответственно прямой и обратной ветвей системы, поэтому для придания устойчивости работе устройства следует выполнять требование Kβ<1.

В лаборатории сейсмометрии Института геофизики УрО РАН было проведено физическое моделирование предлагаемого устройства. Полоса пропускания фильтрующего АЦП была принята 0 - 500 Гц. В качестве ФНЧ 11 использовался фильтр низкой частоты Баттерворта четвертого порядка. Из цифровой последовательности Y в дополнительных преобразователе полярности и интеграторе (не показаны), аналогичных преобразователю полярности и интегратору дельта-модулятора, восстанавливался аналоговый сигнал Uвых. В полосе пропускания 0 - 500 Гц амплитуда Uвых. изменялась не более чем на ±3 дБ. При входном сигнале 1 кГц ( π/τ ) выходной сигнал подавлялся на 64 дБ.

Изобретение относится к области геофизического приборостроения и может быть использовано в качестве аналого-цифрового преобразователя в исследовательской сейсморегистрирующей аппаратуре. Достигаемый технический результат - устранение искажений типа перегрузки по крутизне, вызываемых резким возрастанием крутизны входного сигнала. Устройство содержит устройство вычитания, компаратор, триггер, первый преобразователь полярности, первый интегратор, дополнительную петлю обратной связи, обеспечивающую реализацию алгоритма работы гребенчатого фильтра, которая в совокупности с дополнительным фильтром низкой частоты практически полностью устраняет отмеченные выше искажения. Фильтрующий аналого-цифровой преобразователь с использованием дельта-модуляции содержит устройство вычитания, компаратор, триггер, первый преобразователь полярности, первый интегратор, генератор тактовой частоты и дополнительную петлю обратной связи, которая содержит цифровую линию задержки, второй преобразователь полярности, второй интегратор, сумматор и фильтр низкой частоты. 1 ил.

Фильтрующий аналого-цифровой преобразователь с использованием дельта-модуляции, содержащий последовательно соединенные устройство вычитания, компаратор, триггер, первый преобразователь полярности и первый интегратор, выход которого соединен с первым входом устройства вычитания, а также генератор тактовой частоты, выход которого подключен к тактовому входу триггера, отличающийся тем, что в него введена дополнительная петля обратной связи, реализующая алгоритм работы гребенчатого фильтра и содержащая последовательно соединенные цифровую линию задержки, информационный вход которой соединен с выходом триггера, который также является выходом устройства, а управляющий вход подключен к выходу генератора тактовой частоты, второй преобразователь полярности, второй интегратор, сумматор, второй вход которого является входом устройства, и фильтр низкой частоты, выход которого подключен к второму входу устройства вычитания.

| US 4616349 A, 07.10.86 | |||

| Баскаков С.И | |||

| Радиотехнические цепи и сигналы | |||

| - М.: Высшая школа, 1988, с | |||

| Способ изготовления струн | 1924 |

|

SU345A1 |

| Турлов П.А., Ямпольский А.М., Гольштейн В.Л | |||

| Эксплуатация цифровых сейсморазведочных станций "Прогресс" | |||

| - М.: Недра, 1986, с | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| US 4084151 A, 11.04.78. | |||

Авторы

Даты

1999-01-20—Публикация

1997-08-07—Подача