Изобретение относится к области автоматики и может быть использовано для преобразования аналоговых сигналов в цифровой вид в сейсморегистрирующей или исследовательской сейсмической аппаратуре.

Известны аналого-цифровые преобразователи (АЦП), работающие по методу импульсно-кодовой модуляции (ИКМ) [1], принцип действия которых заключается в следующем. Входной аналоговый сигнал дискретизирует-ся по времени, затем каждый дискрет (выборка) квантуется по уровню, в результате чего на выходе такого устройства формируется n-разрядный двоичный код эквивалентный амплитуде выборки. Прямая пропорциональная зависимость числа разрядов n и амплитуды выборки приводит к тому, что для преобразования аналогового сигнала, изменяющегося в динамическом диапазоне 100 дБ и более, требуется не менее 16 двоичных разрядов АЦП, а учитывая автономность сейсмической аппаратуры и большие массивы регистрируемой информации, это обстоятельство является недостатком.

Известны также аналого-цифровые преобразователи, использующие принцип дифференциальной импульсно-кодовой модуляции (ДИКМ) [2]. В отличие от ИКМ, АЦП данного типа позволяют осуществлять преобразование аналоговых сигналов в достаточно широком динамическом диапазоне с использованием меньшего числа двоичных разрядов. Это достигается за счет того, что преобразованию подвергается не абсолютное значение выборки, как в ИКМ, а разность двух соседних выборок. Очевидно, что такая разность никогда не превысит значение самой выборки. В то же время, если при вычислении разности двух соседних выборок появляется ошибка, то искаженное значение будет зафиксировано, например в накопителе сейсмического регистратора (магнитный диск, твердая память и т. п.). В дальнейшем при считывании информации из накопителя, все данные, следующие за ошибочным значением, будут также искажены, что абсолютно неприемлемо для сейсморегистрирующей аппаратуры.

Ближайшим аналогом (прототипом) предлагаемого устройства преобразования аналоговых сигналов является преобразователь, описанный в [4], где приведена схема, реализующая метод ДИКМ, дополненный блоками, которые, сохраняя положительные свойства метода, одновременно обеспечивают минимизацию ошибок, возникающих при ДИКМ. В частности, в [4] при малом значении или отсутствии разности между двумя соседними выборками преобразованию подвергается сигнал, близкий по значению или равный входному сигналу, благодаря чему ошибки при передаче или записи цифровой информации в память не оказывают большого влияния при восстановлении исходного сигнала так же, как и при обычной ИКМ. В то же время, поскольку фильтр 4 низкой частоты (ФНЧ) в преобразователе [4] имеет фиксированную частоту среза (FСРЕЗА), достаточно трудно избежать ситуации, когда возникает перегрузка на высших частотах при больших уровнях входного сигнала, т.е. переполнение разрядной сетки АЦП 2.

Цель предлагаемого изобретения - устранение перегрузки на высших частотах при больших уровнях входного сигнала - достигается за счет введения блока анализа цифровых кодов на близость к максимуму преобразования, который обеспечивает формирование сигнала, управляющего частотой среза ФНЧ.

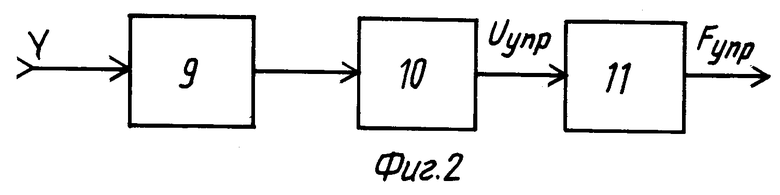

На фиг. 1 показана блок-схема предлагаемого устройства преобразования аналоговых сигналов. Устройство состоит из сумматора 1, n-разрядного АЦП 2, работающего по методу ИКМ, n-разрядного цифро-аналогового преобразователя (ЦАП) 3, ФНЧ 4, устройства 5 вычитания, усилителя 6, генератора 7 тактовой частоты и блока 8 анализа цифровых кодов на близость к максимуму преобразования, причем входом устройства является один из входов сумматора 1, соединенный также с одним из входов устройства 5 вычитания, выход сумматора 1 подключен ко входу АЦП 2, выход которого соединен со входами ЦАП 3 и блока 8 анализа, при этом выход АЦП 2 является выходом устройства, выход ЦАП 3 соединен с входом ФНЧ 4, вход управления частотой среза которого подключен к выходу блока 8 анализа, выход ФНЧ 4 подключен ко второму входу устройства 5 вычитания, выход которого соединен со входом усилителя 6, выход которого подключен ко второму входу сумматора 1, выход генератора 7 тактовой частоты соединен с тактовым входом АЦП 2.

Работает устройство преобразования следующим образом. Входной сигнал UВХ поступает на входы сумматора 1 и устройства 5 вычитания. Выходной сигнал сумматора 1 UΣ преобразуется АЦП 2 в цифровую форму Y с тактовой частотой FТ, причем цифровое значение предыдущей выборки сохраняется на выходе АЦП 2 до следующей выборки и изменяется в момент прихода тактового импульса. Цифровой сигнал Y поступает на выход устройства, а также на дополнительный ЦАП 3 и далее в ФНЧ 4, после чего восстанавливается в исходную аналоговую форму, сравнивается со входным аналоговым сигналом в устройстве 5 вычитания, а полученная разность усиливается в усилителе 6 и поступает на сумматор 1 вместе с входным сигналом. Одновременно цифровой сигнал Y поступает в блок 8 анализа, где производится анализ цифровых кодов на близость значений сигнала к максимуму преобразования, т.е. на близость к переполнению разрядной сетки АЦП 2. В результате этого анализа формируется управляющая частота FУПР, которая с выхода блока 8 анализа подается на управляющий вход ФНЧ 4. В качестве ФНЧ 4 в схеме преобразователя используется фильтр Кауэра 8 порядка на переключаемых конденсаторах фирмы MAXIM - МАХ 297СРА, спецификация на который приведена в [3] . Заметим лишь, что для данного фильтра установлена прямо пропорциональная зависимость между FУПР и FСРЕЗА, которая определяется выражением

FСРЕЗА=FУПР/50 (1).

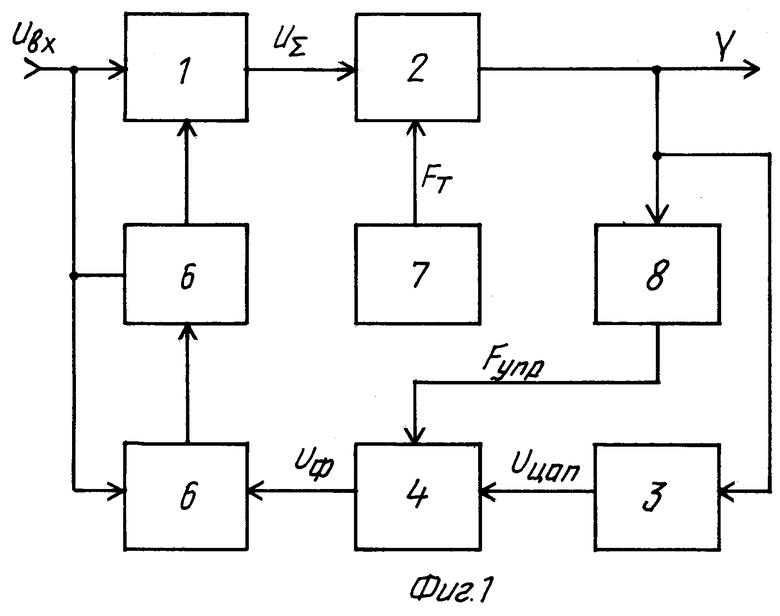

Рассмотрим более подробно работу блока 8 управления. На фиг.2 показана структурная схема блока, который состоит из последовательно соединенных дешифратора 9, интегратора 10 и генератора 11 управляемого напряжением (ГУН). Цифровой сигнал Y поступает на вход дешифратора 9, где анализируется близость значений сигнала к максимуму преобразования. Например код 1100... означает, что используется 2/3 максимума преобразования, 1110... - 3/4 максимума и т.д. В простейшем случае дешифратор может представлять из себя комбинацию логических элементов И, ИЛИ и на его выходе при всех значениях кода меньше 1110... будет присутствовать уровень логического нуля, а при 1110... и больше - уровень логической единицы. Если полученную последовательность уровней лог. 0 и лог. 1 подать на вход интегратора 10, то на его выходе выделится постоянная составляющая этой последовательности UУПР. При этом, чем ближе сигнал к максимуму преобразования, тем больше UУПР. Управляющее напряжение в свою очередь подается на вход ГУН 11, достаточно широко описанного в литературе, который аппаратно может быть реализован, например по схеме традиционного RC генератора, в частотозависимую цепь которого включен полевой транзистор. Последний выполняет роль элемента, регулирующего выходную частоту генератора, т.е. FУПР.

Таким образом, возвращаясь к схеме фиг.1, ФНЧ 4 под воздействием управляющей частоты FУПР изменяет FСРЕЗА в соответствии с соотношением (1), в результате чего устраняется перегрузка на высших частотах при больших уровнях входного сигнала.

В заключение необходимо добавить, что для правильного восстановления аналогового сигнала из цифровой последовательности Y, необходимо использовать ЦАП, ФНЧ и блок анализа с такими же параметрами, как и ЦАП 3, ФНЧ 4 и блок 8 анализа предлагаемого устройства преобразования.

Источники информации

1. Токхейм Р. Основы цифровой электроники. М.: Мир, 1988, с.354 -357, 362-367.

2. Пилипчук Н.И., Яковлев В.П. Адаптивная импульсно-кодовая модуляция. Статистическая теория связи. Вып.25. - М.: Радио и связь, 1986, с.73 -76.

3. Фильтры на переключаемых конденсаторах. Chip News, 4, 1996 г.

4. Способ и устройство преобразования аналоговых сигналов. Патент РФ 2131167. Опубл. 27.05.99. Бюл. 15 - прототип.

Изобретение относится к области автоматики и может быть использовано для преобразования аналоговых сигналов в цифровой вид в сейсморегистрирующей или исследовательской сейсмической аппаратуре. Технический результат заключается в устранении перегрузки на высших частотах при больших уровнях входного сигнала за счет введения блока анализа цифровых кодов на близость к максимуму преобразования. Если сигнал достаточно близок к максимуму преобразования, т.е. на входе устройства присутствует высокочастотный сигнал большой амплитуды, блок анализа вырабатывает на выходе управляющую частоту, с помощью которой происходит изменение частоты среза фильтра низкой частоты и как результат - границы преобразования устройства расширяются. 2 ил.

Устройство преобразования аналоговых сигналов в цифровую форму, содержащее последовательно соединенные сумматор, n-разрядный аналого-цифровой преобразователь, n-разрядный цифроаналоговый преобразователь, фильтр низкой частоты, устройство вычитания и усилитель, выход которого соединен с одним из входов сумматора, а также генератор тактовой частоты, выход которого подключен к тактовому входу n-разрядного аналого-цифрового преобразователя, при этом входом устройства является второй вход сумматора, соединенный со вторым входом устройства вычитания, а выходом устройства является выход n-разрядного аналого-цифрового преобразователя, отличающееся тем, что в него дополнительно введен блок анализа цифровых кодов на близость к максимуму преобразования, вход которого подключен к выходу n-разрядного аналого-цифрового преобразователя, а выход соединен с входом управления частотой среза фильтра низкой частоты.

| СПОСОБ И УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ АНАЛОГОВЫХ СИГНАЛОВ | 1997 |

|

RU2131167C1 |

| US 4771266 А, 13.09.1988 | |||

| СПОСОБ ПОСТРОЕНИЯ НАПРАВЛЯЮЩЕЙ КРИВОЙ ЯРИМОВА ЦИЛИНДРИЧЕСКОЙ ПОВЕРХНОСТИ РОТОРА ИЛИ КОРПУСА (ВАРИАНТЫ) | 2001 |

|

RU2202702C2 |

| ТОКХЕЙМ Р | |||

| Основы цифровой электроники | |||

| - М.: Мир, 1988, с.354-357, 362-367 | |||

| ПИЛИПЧУК Н.И | |||

| и др | |||

| Адаптивная импульсно-кодовая модуляция | |||

| Статистическая теория связи | |||

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

| - М.: Радио и связь, 1986, с.73-76. | |||

Авторы

Даты

2003-03-20—Публикация

2000-08-04—Подача