Изобретение относится к геофизическому приборостроению и может быть использовано в качестве автономного регистратора низкочастотного сейсмического сигнала.

Цель изобретения - увеличение объема записи и повышение качества воспроизведения.

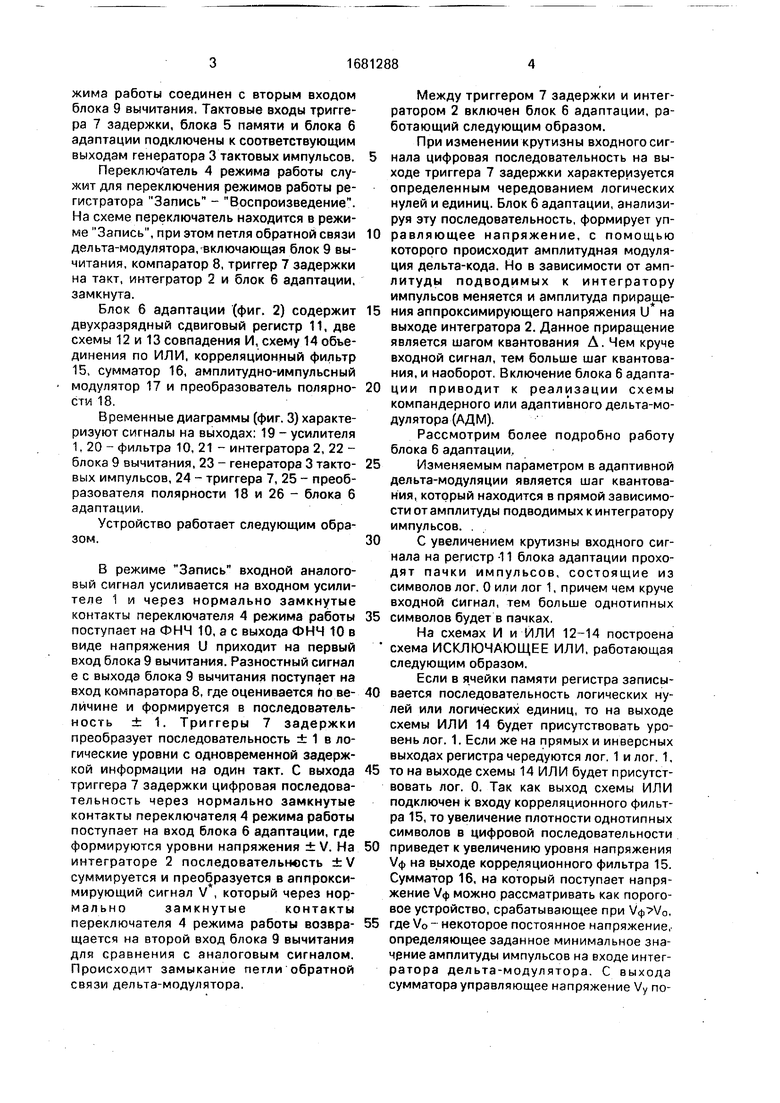

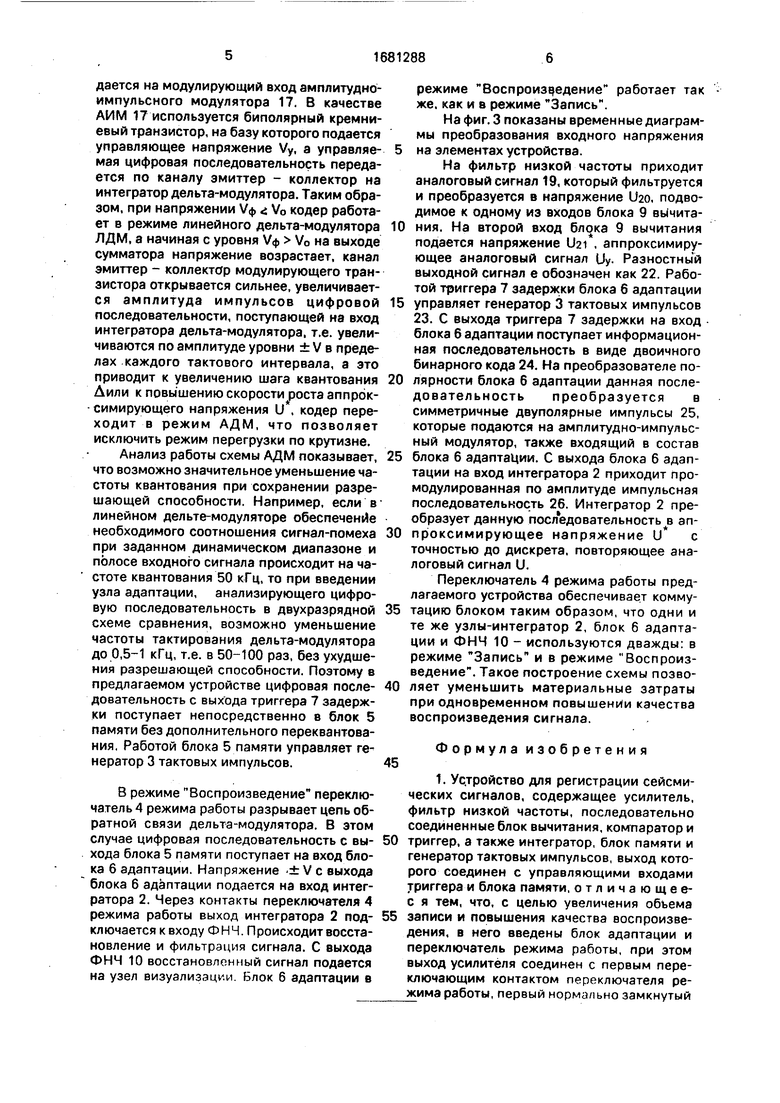

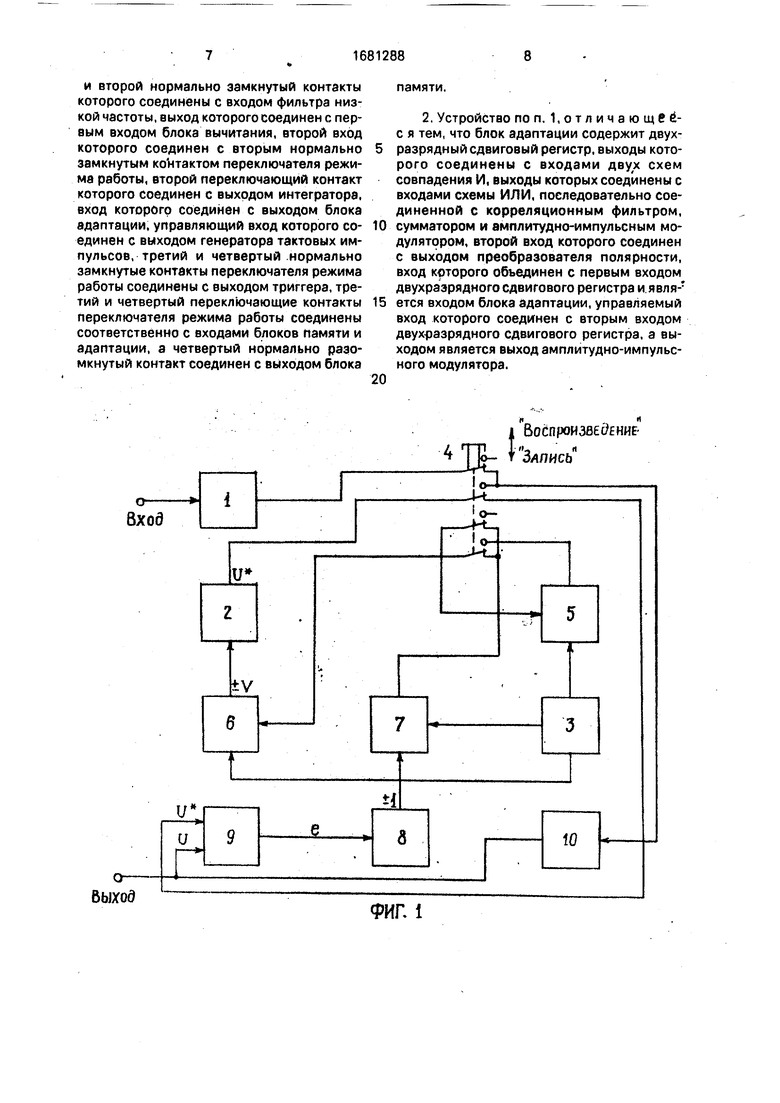

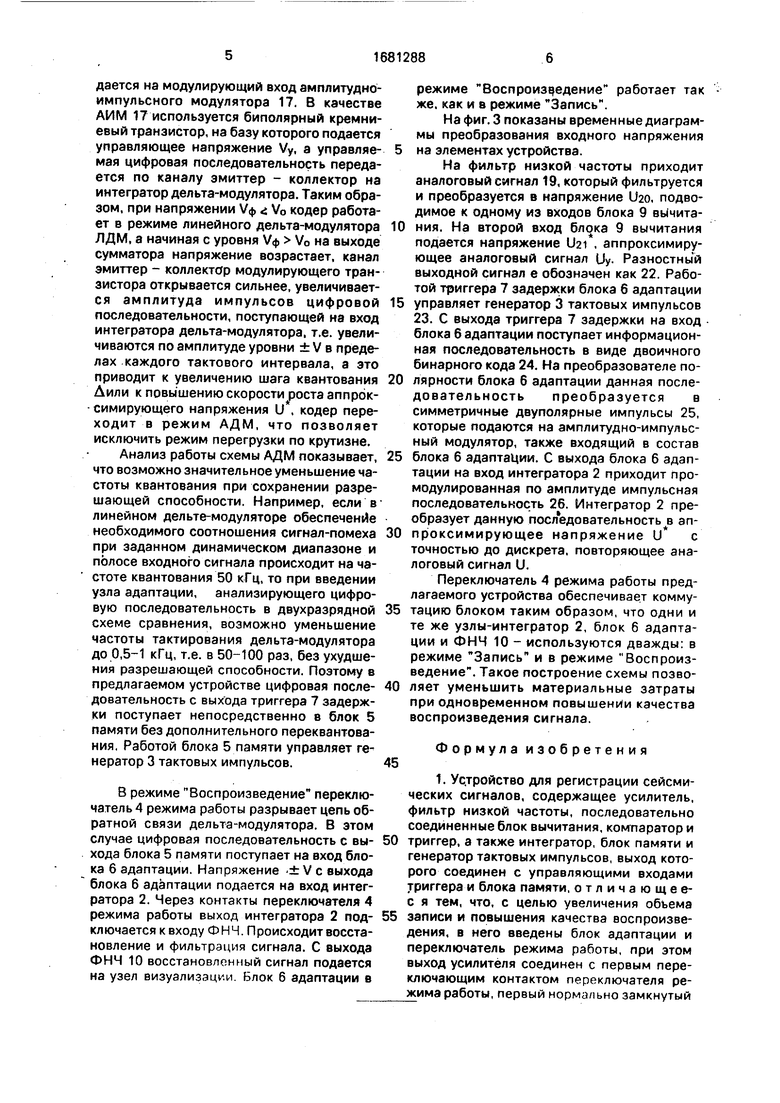

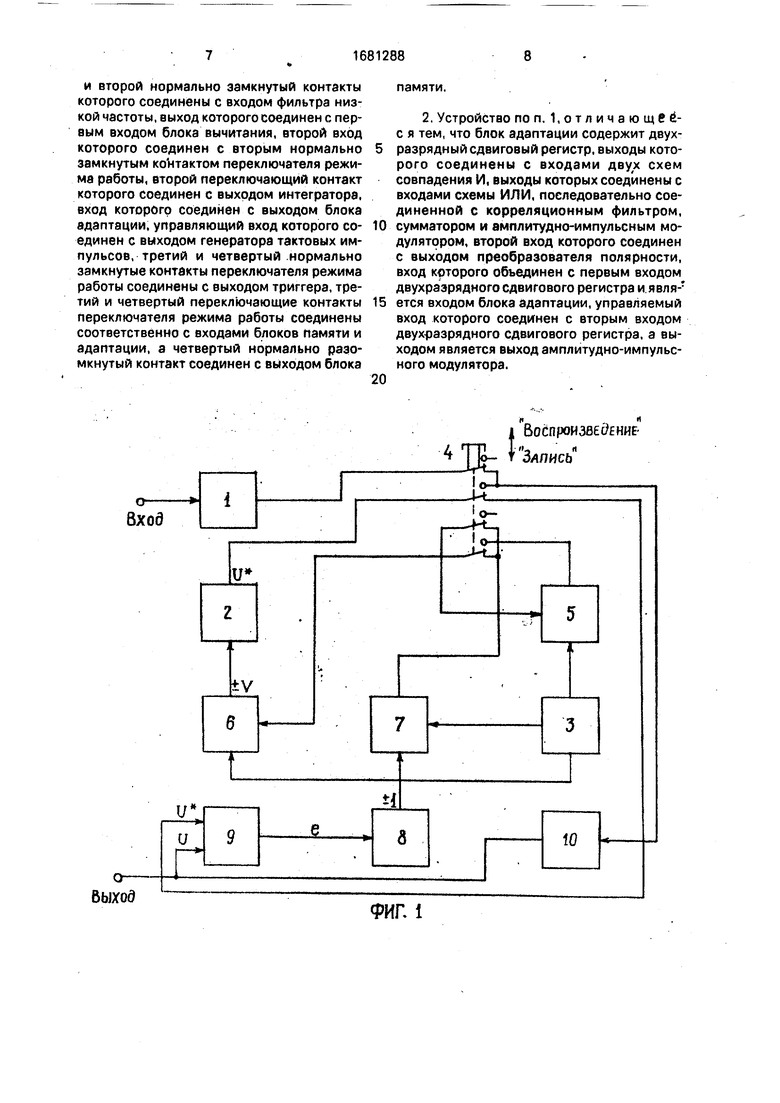

На фиг. 1 приведена блок-схема устройства для регистрации сейсмических сигналов; на фиг. 2 - схема блока адаптации; на фиг. 3 - временные диаграммы преобразования входного напряжения на боках устройства.

Устройство (фиг. 1) содержит усилитель 1, интегратор 2, генератор 3 тактовых импульсов, переключатель 4 режима работы, блок 5 памяти, блок 6 адаптации, триггер 7

задержки на такт, компаратор 8, блок 9 вычитания и фильтр 10 низкой частоты.

Выход входного усилителя 1 через контакты переключателя 4 режима работы соединен с входом ФНЧ 10, выход ФНЧ 10 подключен к первому входу блока 9 вычитания, выход которого соединен с входом компаратора 8, выход компаратора 8 соединен с информационным входом триггера 7 задержки на такт, а выход последнего через контакты переключателя 4 режима работы подключен к входам блока 5 памяти, блока 6 адаптации, причем выход блока 5 памяти соединен с нормально разомкнутым контактом переключателя 4 режима работы, вход интегратора 2 подключен к выходу блока 6 адаптации и выход интегратора 2 через нормально замкнутые контакты переключателя 4 реО СО

ГО 00 00

жима работы соединен с вторым входом блока 9 вычитания. Тактовые входы триггера 7 задержки, блока 5 памяти и блока 6 адаптации подключены к соответствующим выходам генератора 3 тактовых импульсов.

Переключатель 4 режима работы служит для переключения режимов работы регистратора Запись - Воспроизведение. На схеме переключатель находится в режиме Запись, при этом петля обратной связи дельта-модулятора, включающая блок 9 вычитания, компаратор 8, триггер 7 задержки на такт, интегратор 2 и блок 6 адаптации, замкнута.

Блок б адаптации (фиг. 2) содержит двухразрядный сдвиговый регистр 11, две схемы 12 и 13 совпадения И, схему 14 объединения по ИЛИ, корреляционный фильтр 15, сумматор 16, амплитудно-импульсный модулятор 17 и преобразователь полярности 18.

Временные диаграммы (фиг. 3) характеризуют сигналы на выходах: 19 - усилителя 1, 20 - фильтра 10, 21 - интегратора 2, 22 - блока 9 вычитания, 23 - генератора 3 тактовых импульсов, 24 - триггера 7, 25 - преобразователя полярности 18 и 26 - блока 6 адаптации.

Устройство работает следующим образом.

В режиме Запись входной аналоговый сигнал усиливается на входном усилителе 1 и через нормально замкнутые контакты переключателя 4 режима работы поступает на ФНЧ 10, а с выхода ФНЧ 10 в виде напряжения U приходит на первый вход блока 9 вычитания. Разностный сигнал е с выхода блока 9 вычитания поступает на вход компаратора 8, где оценивается по величине и формируется в последовательность ± 1. Триггеры 7 задержки преобразует последовательность ± 1 в логические уровни с одновременной задержкой информации на один такт. С выхода триггера 7 задержки цифровая последовательность через нормально замкнутые контакты переключателя 4 режима работы поступает на вход блока 6 адаптации, где формируются уровни напряжения ± V. На интеграторе 2 последовательнее™ ±V суммируется и преобразуется в аппроксимирующий сигнал V, который через нормальнозамкнутыеконтактыпереключателя 4 режима работы возвращается на второй вход блока 9 вычитания для сравнения с аналоговым сигналом. Происходит замыкание петли обратной связи дельта-модулятора.

Между триггером 7 задержки и интегратором 2 включен блок б адаптации, работающий следующим образом.

При изменении крутизны входного сигнала цифровая последовательность на выходе триггера 7 задержки характеризуется определенным чередованием логических нулей и единиц. Блок 6 адаптации, анализируя эту последовательность, формирует управляющее напряжение, с помощью которого происходит амплитудная модуляция дельта-кода. Но в зависимости от амплитуды подводимых к интегратору импульсов меняется и амплитуда прираицения аппроксимирующего напряжения U на выходе интегратора 2. Данное приращение является шагом квантования А. Чем круче входной сигнал, тем больше шаг квантования, и наоборот. Включение блока 6 адаптации приводит к реализации схемы компандерного или адаптивного дельта-модулятора (АДМ).

Рассмотрим более подробно работу блока 6 адаптации.

Изменяемым параметром в адаптивной дельта-модуляции является шаг квантования, который находится в прямой зависимости от амплитуды подводимых к интегратору импульсов.

С увеличением крутизны входного сигнала на регистр -11 блока адаптации проходят пачки импульсов, состоящие из символов лог. О или лог 1, причем чем круче входной сигнал, тем больше однотипных

символов будет в пачках.

На схемах И и ИЛИ 12-14 построена схема ИСКЛЮЧАЮЩЕЕ ИЛИ, работающая следующим образом.

Если в ячейки памяти регистра записывается последовательность логических нулей или логических единиц, то на выходе схемы ИЛИ 14 будет присутствовать уровень лог. 1. Если жена прямых и инверсных выходах регистра чередуются лог. 1 и лог. 1,

то на выходе схемы 14 ИЛИ будет присутствовать лог. 0. Так как выход схемы ИЛИ подключен к входу корреляционного фильтра 15, то увеличение плотности однотипных символов в цифровой последовательности

приведет к увеличению уровня напряжения Уф на выходе корреляционного фильтра 15. Сумматор 16, на который поступает напряжение Уф можно рассматривать как пороговое устройство, срабатывающее при Уфтл/0,

где Уо - некоторое постоянное напряжение, определяющее заданное минимальное зна- чэние амплитуды импульсов на входе интегратора дельта-модулятора. С выхода сумматора управляющее напряжение Vy подается на модулирующий вход амплитудно- импульсного модулятора 17. В качестве АИМ 17 используется биполярный кремниевый транзистор, на базу которого подается управляющее напряжение Vy, а управляемая цифровая последовательность передается по каналу эмиттер - коллектор на интегратор дельта-модулятора. Таким образом, при напряжении /ф ; V0 кодер работает в режиме линейного дельта-модулятора ЛДМ, а начиная с уровня Уф V0 на выходе сумматора напряжение возрастает, канал эмиттер - коллектор модулирующего транзистора открывается сильнее, увеличивается амплитуда импульсов цифровой последовательности, поступающей на вход интегратора дельта-модулятора, т.е. увеличиваются по амплитуде уровни ± V в пределах каждого тактового интервала, а это приводит к увеличению шага квантования Лили к повышению скорости роста аппрок- симирующего напряжения U , кодер переходит в режим АДМ, что позволяет исключить режим перегрузки по крутизне. Анализ работы схемы АДМ показывает, что возможно значительное уменьшение частоты квантования при сохранении разрешающей способности. Например, если в линейном дельте-модуляторе обеспечение необходимого соотношения сигнал-помеха при заданном динамическом диапазоне и полосе входного сигнала происходит на частоте квантования 50 кГц, то при введении узла адаптации, анализирующего цифровую последовательность в двухразрядной схеме сравнения, возможно уменьшение частоты тактирования дельта-модулятора до 0,5-1 кГц, т.е. в 50-100 раз, без ухудшения разрешающей способности. Поэтому в предлагаемом устройстве цифровая последовательность с выхода триггера 7 задержки поступает непосредственно в блок 5 памяти без дополнительного переквантования. Работой блока 5 памяти управляет генератор 3 тактовых импульсов.

В режиме Воспроизведение переключатель 4 режима работы разрывает цепь обратной связи дельта-модулятора. В этом случае цифровая последовательность с выхода блока 5 памяти поступает на вход блока 6 адаптации. Напряжение -± V с выхода блока 6 адаптации подается на вход интегратора 2. Через контакты переключателя 4 режима работы выход интегратора 2 подключается к входу ФНЧ. Происходит восстановление и фильтрация сигнала. С выхода ФНЧ 10 восстановленный сигнал подается на узел визуализации. Блок 6 адаптации в

режиме Воспроизведение работает так же. как и в режиме Запись.

На фиг. 3 показаны временные диаграммы преобразования входного напряжения

на элементах устройства.

На фильтр низкой частоты приходит аналоговый сигнал 19, который фильтруется и преобразуется в напряжение U20, подводимое к одному из входов блока 9 вычитания. На второй вход блока 9 вычитания подается напряжение U21 , аппроксимирующее аналоговый сигнал Uy. Разностный выходной сигнал е обозначен как 22. Работой триггера 7 задержки блока 6 адаптации

управляет генератор 3 тактовых импульсов 23. С выхода триггера 7 задержки на вход блока 6 адаптации поступает информационная последовательность в виде двоичного бинарного кода 24. На преобразователе полярности блока б адаптации данная последовательность преобразуется в симметричные двуполярные импульсы 25, которые подаются на амплитудно-импульсный модулятор, также входящий в состав

блока 6 адаптации. С выхода блока 6 адаптации на вход интегратора 2 приходит про- модулированная по амплитуде импульсная последовательность 26. Интегратор 2 преобразует данную посл едовательность в аппроксимирующее напряжение U с точностью до дискрета, повторяющее аналоговый сигнал U.

Переключатель 4 режима работы предлагаемого устройства обеспечивает коммутацию блоком таким образом, что одни и те же узлы-интегратор 2, блок 6 адаптации и ФНЧ 10 - используются дважды: в режиме Запись и в режиме Воспроизведение. Такое построение схемы позволяет уменьшить материальные затраты при одновременном повышении качества воспроизведения сигнала.

45

Формула изобретения

1. Устройство для регистрации сейсмических сигналов, содержащее усилитель, фильтр низкой частоты, последовательно соединенные блок вычитания, компаратор и

0 триггер, а также интегратор, блок памяти и генератор тактовых импульсов, выход которого соединен с управляющими входами триггера и блока памяти, отличающее- с я тем, что, с целью увеличения объема

5 записи и повышения качества воспроизведения, в него введены блок адаптации и переключатель режима работы, при этом выход усилителя соединен с первым переключающим контактом переключателя режима работы, первый нормально замкнутый

и второй нормально замкнутый контакты которого соединены с входом фильтра низкой частоты, выход которого соединен с первым входом блока вычитания, второй вход которого соединен с вторым нормально замкнутым контактом переключателя режима работы, второй переключающий контакт которого соединен с выходом интегратора, вход которого соединен с выходом блока адаптации, управляющий вход которого соединен с выходом генератора тактовых импульсов, третий и четвертый нормально замкнутые контакты переключателя режима работы соединены с выходом триггера, третий и четвертый переключающие контакты переключателя режима работы соединены соответственно с входами блоков памяти и адаптации, а четвертый нормально разомкнутый контакт соединен с выходом блока

памяти.

2. Устройство поп, 1,отличающвё- с я тем, что блок адаптации содержит двухразрядный сдвиговый регистр, выходы которого соединены с входами двух схем совпадения И, выходы которых соединены с входами схемы ИЛИ, последовательно соединенной с корреляционным фильтром,

сумматором и амплитудно-импульсным модулятором, второй вход которого соединен с выходом преобразователя полярности, вход которого объединен с первым входом двухразрядного сдвигового регистра и явля-

ется входом блока адаптации, управляемый вход которого соединен с вторым входом двухразрядного сдвигового регистра, а выходом является выход амплитудно-импульсного модулятора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| ФИЛЬТРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ИСПОЛЬЗОВАНИЕМ ДЕЛЬТА- МОДУЛЯЦИИ | 1997 |

|

RU2125343C1 |

| СПОСОБ ВОССТАНОВЛЕНИЯ ИСХОДНОГО СИГНАЛА ПРИ ДЕЛЬТА-МОДУЛЯЦИИ И УСТРОЙСТВО ДЛЯ ДЕЛЬТА-ДЕМОДУЛЯЦИИ | 1994 |

|

RU2129333C1 |

| ВЫСОКОИНФОРМАТИВНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ИСПОЛЬЗОВАНИЕМ ДЕЛЬТА-МОДУЛЯЦИИ ДЛЯ СЕЙСМИЧЕСКИХ ИССЛЕДОВАНИЙ | 1997 |

|

RU2128880C1 |

| Система связи с асинхронной дельта-модуляцией | 1989 |

|

SU1624695A1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1988 |

|

SU1573470A1 |

| Адаптивный дельта-кодер | 1987 |

|

SU1425839A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Устройство речевого сопровождения в сейсмической станции, использующее принцип адаптивной дельта-модуляции | 2018 |

|

RU2683894C1 |

| Дискретный адаптивный дельта-модулятор | 1976 |

|

SU641647A1 |

Изобретение относится к области геофизического приборостроения и может быть использовано в качестве автономного регистратора низкочастотного сейсмического сигнала. Цель изобретения - увеличение объема записи и повышение качества воспроизведения. За счет введения дельта- модулятора снижается частота квантования при оцифровке аналогового сигнала, что ведет к снижению необходимого объема памяти цифровой информации. Кроме того, использование при записи и воспроизведении одних и тех же блоков регистратора, коммутируемых переключателем режима работы, .приводит к снижению материальных затрат и повышению точностью восстановления аналогового сигнала из цифровой последовательности. 1 з.п.ф-лы, 3 ил.

Выход

ВОСПРОИЗВЕДЕНИЕIUИ

ЗАПИСЬ

ФИП 1

задержки

Кинтегра-t тору

Фиг. 2

&

±V

п

Vy

Т.

| Полевая телеметрическая сейсмическая станция | 1984 |

|

SU1255978A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США N 4616349, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1991-09-30—Публикация

1989-06-27—Подача