Изобретение относится к измерительной и вычислительной технике и может использоваться для измерения с высокой точностью и высоким быстродействием временных интервалов между импульсами.

Известно устройство для измерения временных интервалов, которое содержит основной и нониусный генераторы, дискриминатор, первый и второй триггеры, элемент задержки, основной и нониусные счетчики, блок сравнения и обладает повышенным быстродействием [1] . В этом устройстве в момент поступления границы временного интервала осуществляется запуск нониусного генератора, а окончание преобразования производится при совпадении нониусного сигнала с передним фронтом или спадом основного сигнала, что позволяет примерно в два раза повысить его быстродействие. Однако во многих случаях двукратное повышение быстродействия оказывается недостаточным. Кроме того, в известном устройстве снижается точность из-за невозможности обеспечить параметры основного и нониусного сигналов, в том числе скважность импульсов основного сигнала с точностью, присущей нониусному методу, отсутствуют средства стабилизации частоты нониусного сигнала, не обеспечивается точная стыковка основной и нониусной шкал.

Наиболее близким по технической сущности к заявляемому измерителю является нониусный измеритель временных интервалов [2], который содержит опорный генератор, два нониусных генератора с фазовой автоподстройкой частоты (ФАПЧ), входное устройство, основной и нониусные счетчики, триггер, микропроцессорный блок. В данном устройстве импульс, отмечающий начальную границу измеряемого временного интервала, запускает первый нониусный генератор, на выходе которого вырабатывается N1 импульсов до совпадения с опорным сигналом; импульс, отмечающий конечную границу интервала, запускает второй нониусный генератор, на выходе которого вырабатывается N2 импульсов; между моментами совпадения в основном счетчике подсчитывается N0 импульсов опорного сигнала. Код L временного интервала подсчитывается в микропроцессорном блоке по формуле

L=K•N0+(K+1)•(N1-N2),

где К - коэффициент интерполяции (целое число), задающий соотношение между периодами нониусного Тн и опорного То сигналов по формуле

Тн=(К+1)•То/К.

Известное устройство обладает высокой точностью, так как в нем осуществляется регулировка частоты нониусного сигнала с помощью системы ФАПЧ, а также обеспечивается точная стыковка шкал путем подсчета импульсов основного опорного сигнала между моментами окончания преобразования в нониусных генераторах. Однако это устройство имеет ограниченное быстродействие, вызванное тем, что для измерения требуется достаточно длительный отрезок времени, который может многократно превосходить по длительности измеряемый интервал.

Изобретение направлено на повышение быстродействия нониусного измерителя без снижения его точности.

Это достигается тем, что в нониусный измеритель, содержащий опорный генератор, входное устройство, вход которого является входом измерителя, первый и второй нониусные блоки, первые входы которых подключены к выходам входного устройства, а вторые входы которых подключены к выходу опорного генератора, ключ, информационный вход которого подсоединен к выходу опорного генератора, управляющие входы ключа соединены с первыми выходами первого и второго нониусных блоков, первый и второй нониусные счетчики, входы которых подключены к вторым выходам первого и второго нониусных блоков, триггер, входы которого соединены с первыми выходами первого и второго нониусных блоков, основной счетчик, вход которого подключен к выходу ключа, блок фиксации и управления, входы которого подключены к первым выходам первого и второго нониусных блоков, к выходу триггера, а также к выходам основного счетчика и первого и второго нониусных счетчиков, а выход которого соединен с третьими входами первого и второго нониусных блоков, введена секционированная линия задержки с n-1 выходами, вход которой подключен к выходу опорного генератора, а выходы которой соединены с входами с четвертого по n+2-й первого и второго нониусных блоков, а выходы с третьего по n+2-й первого и второго нониусных блоков соединены с входами блока фиксации и управления.

Кроме того, в каждый нониусный блок введены формирователь запуска, подстраиваемый генератор, делитель, фазовый детектор, схемы детектирования с первой по n-ю, управляемые формирователи с первого по n-й, первый второй и третий переключатели, первый и второй триггеры, элементы задержки с первого по n+1-й, первую и вторую схемы И, первую и вторую схемы ИЛИ, регистр, коммутатор, схему запуска, причем вход формирователя запуска является первым входом нониусного блока, а его выход соединен с входом запуска подстраиваемого генератора, выход которого соединен с входом делителя, выход которого подключен к первому входу фазового детектора, второй вход которого подключен к выходу первой схемы детектирования, а выход которого соединен с управляющим входом подстраиваемого генератора, вход первой схемы детектирования является вторым входом нониусного блока, входы схем детектирования со второй по n-ю являются соответственно входами нониусного блока с четвертого по n+2-й, входы установки всех схем детектирования объединены и подключены к выходу формирователя запуска, входы синхронизации всех схем детектирования объединены и подсоединены к выходу подстраиваемого генератора, а выходы всех схем детектирования соединены с первыми входами управляемых формирователей, выходы которых подключены к входам второй схемы ИЛИ и информационным входам регистра, выход первого управляемого формирователя подключен к первому входу первой схемы ИЛИ, выходы управляемых формирователей со второго по n-й соединены с входами элементов задержки с третьего по n+1-й, выходы которых соединены с входами с второго по n-й первой схемы ИЛИ, вход установки первого триггера подключен к выходу первого переключателя, а выход первого триггера соединен с входом первого элемента задержки, выход которого соединен с входом записи регистра, а также с входом второго элемента задержки, выход которого соединен с вторым входом второго переключателя, а также с первым входом второй схемы И, второй вход которой подключен к выходу первой схемы ИЛИ, а выход второй схемы И соединен с входом установки второго триггера, выход которого является первым выходом нониусного блока, синхронизирующий вход второго триггера подключен к первому выходу схемы запуска, а его информационный вход соединен с уровнем логического нуля, выход первой схемы И является вторым выходом нониусного блока, прямой вход первой схемы И подключен к выходу первого элемента задержки, а ее инверсный вход подсоединен к выходу подстраиваемого генератора, первый вход схемы запуска является третьим входом нониусного блока, а ее второй выход соединен с первым входом первого переключателя, второй вход которого подключен к выходу формирователя запуска, выход второй схемы ИЛИ соединен с вторым входом третьего переключателя, первый вход которого подключен к выходу первого управляемого формирователя, а выход третьего переключателя соединен с входом сброса первого триггера, к первому входу второго переключателя подключен уровень логической единицы, а выход второго переключателя соединен с вторыми входами всех управляемых формирователей, входы коммутатора подключены к выходам управляемых формирователей с второго по n-й, а его выход соединен с вторым входом схемы запуска.

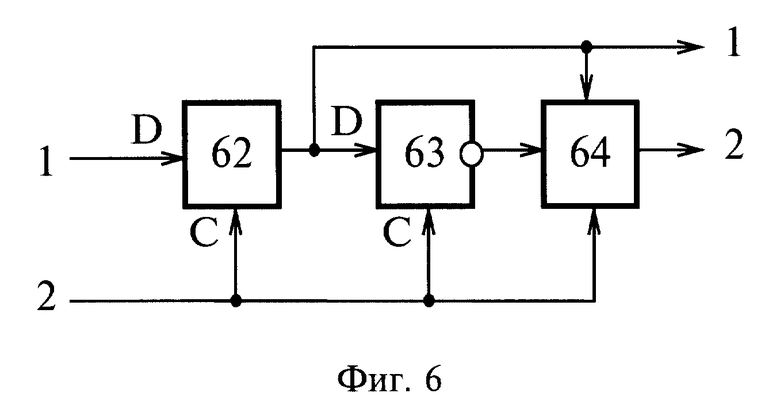

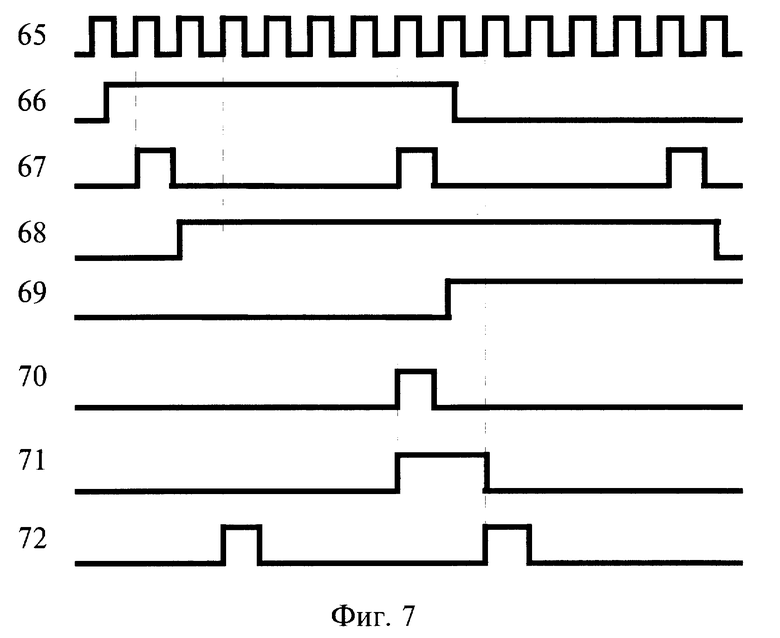

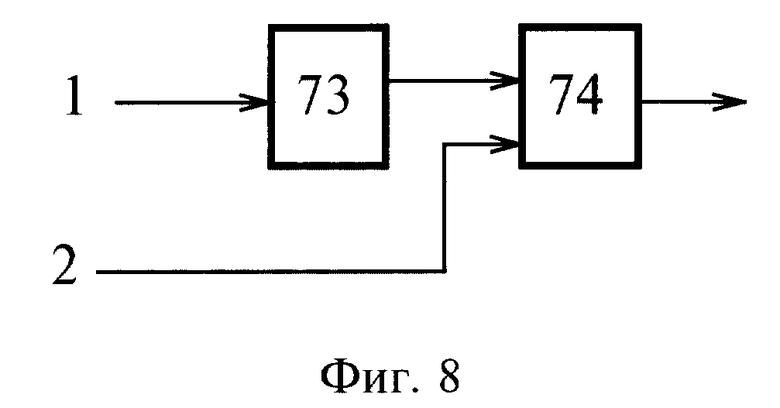

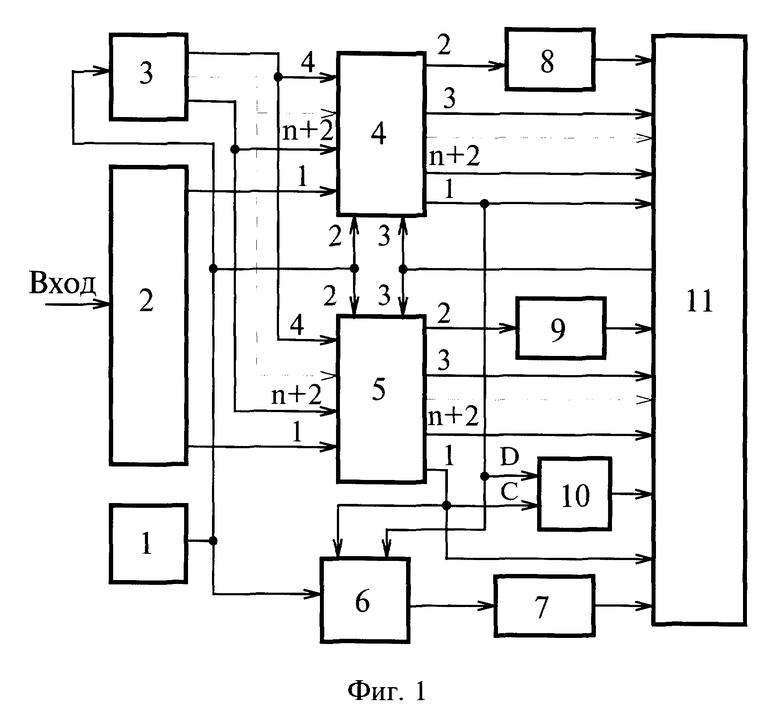

На фиг. 1 изображена структура заявляемого устройства. На фиг. 2 изображена схема нониусного блока для устройства, показанного на фиг. 1. На фиг. 3 приведена временная диаграмма работы устройства, приведенного на фиг. 1. На фиг. 4 и 5 приведены временные диаграммы работы нониусного блока, приведенного на фиг. 2. На фиг. 6 изображена схема запуска для нониусного блока, изображенного на фиг. 2. На фиг. 7 приведена временная диаграмма работы схемы запуска. На фиг. 8 приведена схема управляемого формирователя для нониусного блока, изображенного на фиг. 2.

На фиг. 1 изображено: 1 - опорный генератор; 2 - входное устройство; 3 - секционированная линия задержки; 4 и 5- первый и второй нониусные блоки; 6 - ключ; 7 - основной счетчик; 8 и 9- первый и второй нониусные счетчики; 10 -триггер; 11 - блок фиксации и управления.

Первые входы первого и второго нониусных блоков 4 и 5 подключены к выходам входного устройства 2, вход которого является входом измерителя, вторые входы первого и второго нониусных блоков 4 и 5 подключены к выходу опорного генератора 1, информационный вход ключа 6 подсоединен к выходу опорного генератора 1, управляющие входы ключа 6 соединены с первыми выходами первого и второго нониусных блоков 4 и 5, входы первого и второго нониусных счетчиков 8 и 9 подключены к вторым выходам первого и второго нониусных блоков 4 и 5, входы триггера 10 соединены с первыми выходами первого и второго нониусных блоков 4 и 5, вход основного счетчика 7 подключен к выходу ключа 6, входы блока фиксации и управления 11 подключены к первым выходам первого и второго нониусных блоков 4 и 5, к выходу триггера 10, а также к выходам основного счетчика 7 и первого 8 и второго 9 нониусных счетчиков, а выход блока фиксации и управления 11 соединен с третьими входами первого и второго нониусных блоков 4 и 5, вход секционированной линии задержки 3 подключен к выходу опорного генератора 1, а ее выходы соединены с входами с четвертого по n+2-й первого и второго нониусных блоков 4 и 5, выходы с третьего по n+2-й первого и второго нониусных блоков 4 и 5 соединены с входами блока фиксации и управления 11.

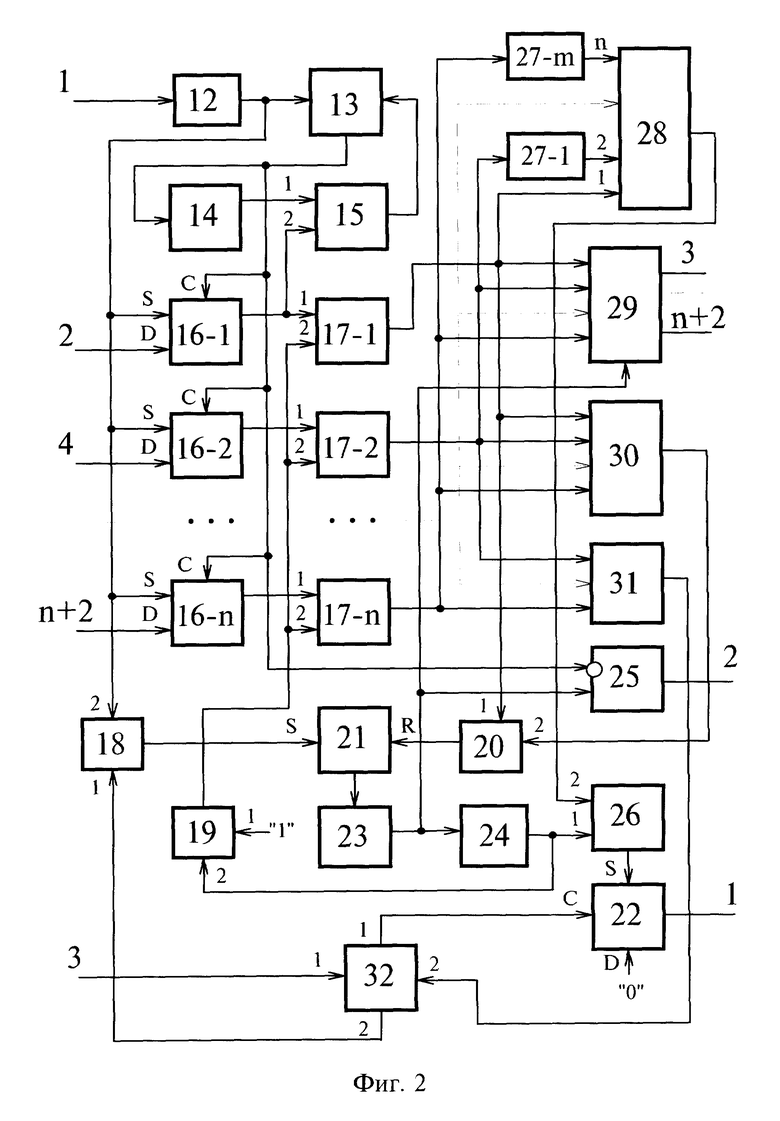

На фиг. 2 приведена схема нониусного блока для устройства, изображенного на фиг. 1. На фиг. 2 изображено: 12 - формирователь запуска; 13 - подстраиваемый генератор; 14 - делитель; 15 - фазовый детектор; 16-1 ... 16-n - схемы детектирования; 17-1 ... 17-n - управляемые формирователи; 18, 19 и 20 - первый второй и третий переключатели; 21 и 22 - первый и второй триггеры; 23 и 24 - первый и второй элементы задержки; 25 и 26 - первая и вторая схемы И; 27-1 . . . 27-m -элементы задержки с третьего по (n+1)-й (m=n-1); 28 - первая схема ИЛИ; 29 - регистр; 30 - вторая схема ИЛИ; 31 - коммутатор; 32 - схема запуска.

Формирователь запуска 12 является первым входом нониусного блока, а его выход соединен с входом запуска подстраиваемого генератора 13, выход которого соединен с входом делителя 14, выход которого подключен к первому входу фазового детектора 15, второй вход которого подключен к выходу первой схемы детектирования 16-1, а выход которого соединен с управляющим входом подстраиваемого генератора 13. Вход первой схемы детектирования 16-1 является вторым входом нониусного блока, входы схем детектирования 16-2 ... 16-n являются соответственно входами нониусного блока с четвертого по n+2-й, входы установки всех схем детектирования 16-1 ... 16-n объединены и подключены к выходу формирователя запуска 12, входы синхронизации всех схем детектирования 16-1 ... 16-n объединены и подсоединены к выходу подстраиваемого генератора 13, а выходы всех схем детектирования 16-1 ... 16-n соединены с первыми входами управляемых формирователей 17-1 ... 17-n, выходы которых подключены к входам второй схемы ИЛИ 30 и информационным входам регистра 29. Выход первого управляемого формирователя 17-1 подключен к первому входу первой схемы ИЛИ 28, выходы управляемых формирователей со второго по n-й 17-2 ... 17-n соединены с входами элементов задержки с третьего по n+1-й 27-1 ... 27-m, выходы которых соединены с входами с второго по n-й первой схемы ИЛИ 28. Вход установки первого триггера 21 подключен к выходу первого переключателя 18, а выход первого триггера 21 соединен с входом первого элемента задержки 23, выход которого соединен с входом записи регистра 29, а также с входом второго элемента задержки 24, выход которого соединен с вторым входом второго переключателя 19, а также с первым входом второй схемы И 26, второй вход которой подключен к выходу первой схемы ИЛИ 28. Выход второй схемы И 26 соединен с входом установки второго триггера 22, выход которого является первым выходом нониусного блока. На информационный вход второго триггера 22 подается уровень логического нуля, а его синхронизирующий вход подключен к первому выходу схемы запуска 32. Выход первой схемы И 25 является вторым выходом нониусного блока, прямой вход первой схемы И подключен к выходу первого элемента задержки 23, а ее инверсный выход подсоединен к выходу подстраиваемого генератора 13. Первый вход схемы запуска 32 является третьим входом нониусного блока, а ее второй выход соединен с первым входом первого переключателя 18, второй вход которого подключен к выходу формирователя запуска 12. Выход второй схемы ИЛИ 30 соединен с вторым входом третьего переключателя 20, первый вход которого подключен к выходу первого управляемого формирователя 17-1, а выход третьего переключателя 20 соединен с входом сброса первого триггера 21. К первому входу второго переключателя 19 подключен уровень логической единицы, а выход второго переключателя 19 соединен с вторыми входами всех управляемых формирователей 17-1 ... 17-n, входы коммутатора 31 подключены к выходам управляемых формирователей с второго по n-й 17-2 . . . 17-n, а выход коммутатора 31 соединен с вторым входом схемы запуска.

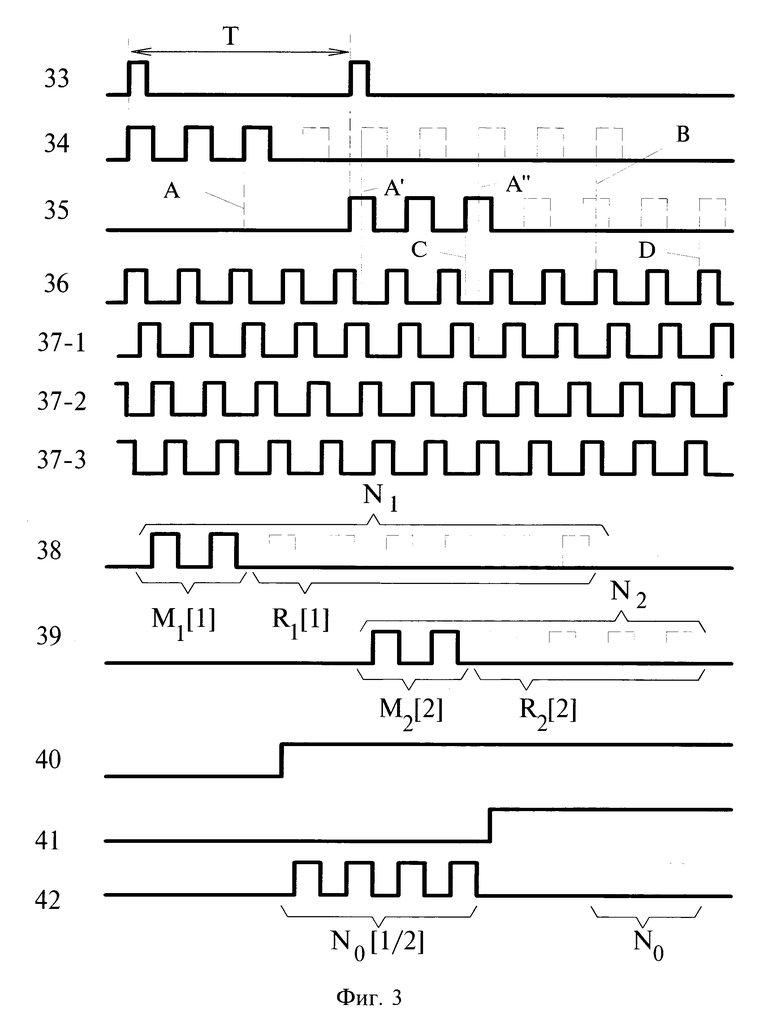

На фиг. 3 - 5 приведены временные диаграммы, поясняющие работу схем, показанных на фиг. 1 и 2, для случая, когда используются три вспомогательных сигнала (n=4).

На фиг. 3 приведена временная диаграмма измерения временного интервала Т измерителем, изображенным на фиг. 1. На фиг. 3 изображено: 33 - входной сигнал; 34 и 35 - первый и второй нониусные сигналы, вырабатываемые в первом и втором нониусных блоках 4 и 5; 36 - основной опорный сигнал; 37-1, 37-2 и 37-3 - первый, второй и третий вспомогательные сигналы на выходах секционированной линии задержки 3; 38 и 39 - импульсы на вторых выходах нониусных блоков 4 и 5; 40 и 41 - сигналы окончания преобразования на первых выходах нониусных блоков 4 и 5; 42 - сигнал на выходе ключа 6 (счетном входе основного счетчика 7). Пунктиром на фиг. 3 показаны сигналы, которые были бы дополнительно сформированы в известном устройстве. На фиг. 3 и в дальнейшем предполагается, что количество нониусных импульсов равно количеству периодов соответствующего сигнала, а также считается, что совпадение нониусного сигнала с опорным (основным или вспомогательным) происходит в момент совпадения передних фронтов этих сигналов.

Период Тн нониусных сигналов в нониусных блоках 4 и 5 одинаков и связан с периодом То основного опорного сигнала соотношением (2). Вспомогательные опорные сигналы формируются на выходах секционированной линии задержки 3 из основного опорного сигнала путем сдвига друг относительно друга на величину То/n, где n-1=3 - количество вспомогательных сигналов.

До начала измерения проводится калибровка, в которой определяются поправки Ri[j] . Каждая поправка Ri[j] определяется как количество импульсов нониусного сигнала в i-м нониусном блоке между совпадением нониусного сигнала с j-м вспомогательным сигналом и совпадением нониусного сигнала с основным опорным сигналом. Поправки определяются для всех i и j. Во время калибровки входные сигналы не поступают.

Так, например, на фиг. 3 поправка R1[1] для первого вспомогательного сигнала 37-1 в первом нониусном блоке 4 определяется как количество импульсов между совпадением нониусного сигнала 34 с первым вспомогательным сигналом 37-1 в точке A и совпадением нониусного сигнала с основным опорным сигналом 36 в точке В. Поправка R1[2] для второго вспомогательного сигнала 37-2 определяется как количество импульсов между совпадением нониусного сигнала 34 с вторым вспомогательным сигналом 37-2 в точке A' и совпадением нониусного сигнала с основным опорным сигналом 36 в точке В. Поправка R1[3] для третьего вспомогательного 37-3 сигнала определяется как количество импульсов между совпадением нониусного сигнала 34 с третьим вспомогательным сигналом 37-3 в точке A'' и совпадением нониусного сигнала с основным опорным сигналом 36 в точке В. Аналогично определяются поправки R2[j] во втором нониусном блоке 5. Для упрощения в примере, показанном на фиг. 3, поправки равны следующим значениям: R1[1]=R2[1]=6, R1[2]=R2[2]=4, R1[3]=R2[3]=2, хотя в общем случае поправки R1[j] и R2[j] при одном значении j могут и не совпадать.

Во время калибровки в нониусных блоках 4 и 5 последовательно задаются номера j=1, 2, ... вспомогательных сигналов, для которых осуществляется калибровка. Здесь возможны различные варианты: 1) проводится по одному циклу работы (испытания) для каждого вспомогательного сигнала; 2) сначала задается j=l и проводится серия испытаний для первого вспомогательного сигнала, затем задается j=2 и проводится серия испытаний для второго сигнала и т. д. 3) после одного испытания номер j увеличивается и так многократно; после последнего сигнала происходит возврат к первому сигналу, при этом для каждого сигнала производится серия измерений. В последних двух случаях поправки определяются как средние значения по многократным испытаниям.

Во время калибровки на вторых выходах нониусных блоков 4 и 5 вырабатываются импульсы между совпадениями нониусного сигнала с j-м вспомогательным сигналом и основным опорным сигналом. Так, например, при определении поправки R1[1] для первого вспомогательного сигнала в примере, показанном на фиг. 3, на втором выходе первого нониусного блока будет выработано 6 импульсов. На выходах первого 8 и второго 9 нониусных счетчиков фиксируются коды соответственно R1[j] и R2[j], которые поступают в блок фиксации и управления 11, где они запоминаются или вычисляются их средние значения, которые будут использоваться при измерении. Блок фиксации и управления 11 может быть реализован с применением микропроцессорных средств и может включать в себя буферное запоминающее устройство для хранения кодов. Результаты калибровки R1[j] и R2[j] могут формироваться по одиночным испытаниям, что сокращает время калибровки, однако, определение средних значений R1[j] и R2[j] на основе многократных испытаний позволяет снизить влияние случайных составляющих погрешности.

Как отмечалось выше, величина сдвига сигналов на выходах секционированной линии задержки 3 должна устанавливаться близкой к величине Тз=То/n, однако, точного значения Тз устанавливать не требуется, так как отклонение сдвига не влияет на точность. Это отклонение выявляется в режиме калибровки и учитывается в кодах R1[j] и R2[j] и соответственно при вычислении величины временного интервала.

При измерении импульс, отмечающий начало измеряемого интервала Т, проходя через входное устройство 2, запускает первый нониусный блок 4, а импульс, отмечающий конец Т, запускает второй нониусный блок 5. Нониусный сигнал 34 (см. фиг. 3), вырабатываемый в первом нониусном блоке 4, совпадает с первым вспомогательным сигналом 37-1 в точке A. При этом на втором выходе первого нониусного блока 4 вырабатывается M1[1]=2 импульсов, которые подсчитываются на первом нониусном счетчике 8 (см. сигнал 38). Если бы использовалось известное устройство, то совпадение с основным сигналом 36 произошло бы в точке В, и на втором выходе первого нониусного блока 4 было бы выработано N1=8 импульсов. В момент окончания преобразования сигнал 40 на первом выходе первого нониусного блока 4 переключается из нулевого состояния в единичное, а на выходах с третьего по (n+2)-й (на фиг. 3 - 5 n=4) первого нониусного блока 4 вырабатывается код j1, который показывает, с каким из сигналов произошло совпадение. Необходимо отметить, что изменение сигналов на первых выходах первого и второго нониусных блоков 4 и 5 происходит синхронно к основному сигналу 36.

Нониусный сигнал 35 во втором нониусном блоке 5 совпадает по фазе с вторым вспомогательным сигналом 37-2 в точке C. При этом на втором выходе второго нониусного блока 5 будет выработано М2[2]=2 импульсов (см. сигнал 39), которые подсчитываются на втором нониусном счетчике 9. Если бы использовалось известное устройство, то совпадение с основным опорным сигналом 36 произошло бы в точке D, и на втором выходе второго нониусного блока 5 было бы выработано N2=6 импульсов. В момент окончания преобразования сигнал 41 на первом выходе второго нониусного блока 5 переключается из нулевого состояния в единичное, а на выходах с третьего по (n+2)-й второго нониусного блока 5 вырабатывается код j2 который показывает, с каким из сигналов произошло совпадение во втором нониусном блоке.

Между моментами окончания преобразования в первом 4 и втором 5 нониусных блоках, отмечаемых передними фронтами сигналов 40 и 41, на выходе ключа 6 вырабатывается N0[j1/j2] импульсов опорного генератора 1, которые подсчитываются на основном счетчике 7. При этом индекс j1 показывает, с каким из сигналов произошло совпадение в первом нониусном блоке 4, j2 - с каким из сигналов произошло совпадение во втором нониусном блоке 5. На фиг. 3 j1=1, j2= 2, N0[l/2]=4, хотя в общем случае j1 и j2 могут принимать любое из значений: 0, 1, 2 или 3, где 0 показывает, что совпадение произошло с основным опорным сигналом. Следует отметить, что в рассматриваемом примере j1 и j2 представляются унитарным кодом, хотя в общем случае кодирование может быть любым, в том числе двоичным позиционным кодом.

По окончании преобразования в обоих нониусных блоках 4 и 5 данные M1[j1] и M2[j2] с выходов первого 8 и второго 9 нониусных счетчиков, N0[j1/j2] с выхода основного счетчика 7, а также с выхода триггера 10, на котором фиксируется знак кода N0[j1/j2] поступают в блок фиксации и управления 11, где происходит вычисление результата измерения. Кроме того, с выходов с третьего по n+2-й первого и второго нониусных блоков в блок фиксации и управления 11 поступают коды j1 и j2, которые показывают, с каким из сигналов произошло совпадение.

Вычисление кода L временного интервала осуществляется по формуле (1). Для получения значений N1 (i=1, 2) к кодам Mi[ji] добавляются определенные ранее в режиме калибровки коды поправок Ri[ji] при соответствующих значениях j, при этом, если совпадение произошло с основным опорным сигналом, то добавление не производится. Вычисление кода N0 производится на основе кода N0[j1/j2] путем вычитания R1[j1] и прибавления R2[j2], где j1 и j2 - коды на выходах с третьего по (n+2)-й первого и второго нониусных блоков 4 и 5. После этих действий код L временного интервала Т вычисляется по известной формуле (1).

В примере, показанном на фиг. 3, к кодам M1[1]=2 и М2(2]=2 добавляются соответственно коды R1[1]=6 и R2[2]=4, а код N0 получается из кода N0[l/2] путем вычитания R1[1]=6 и прибавления R2[2]=4. В результате имеем

L= K•{ N0[1/2] -R1[1] +R2[2] } + +(К+1)•{ M1[1] +R1[1]-(М2[2]+R2[2])} = 2•К+(К+1)•(8-6)=2•К+2•(K+1)

Если бы использовалось известное устройство, то в соответствии с формулой (1) для примера на фиг. 3 было бы получено:

L=K•N0+(K+1)•(N1-N2)= 2•K+(К+1)•(8-6)=2•К+2•(К+1)

В результате коды N0, N1 и N2 и соответственно результат измерения L в заявляемом измерителе получаются такие же, как и в известном устройстве, однако, преобразование заканчивается раньше.

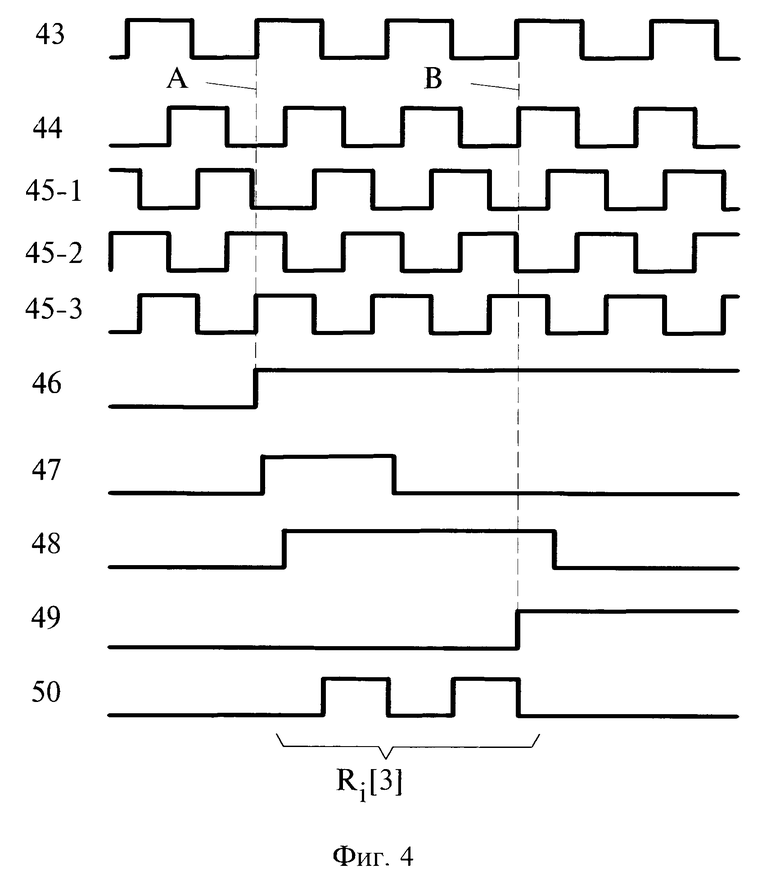

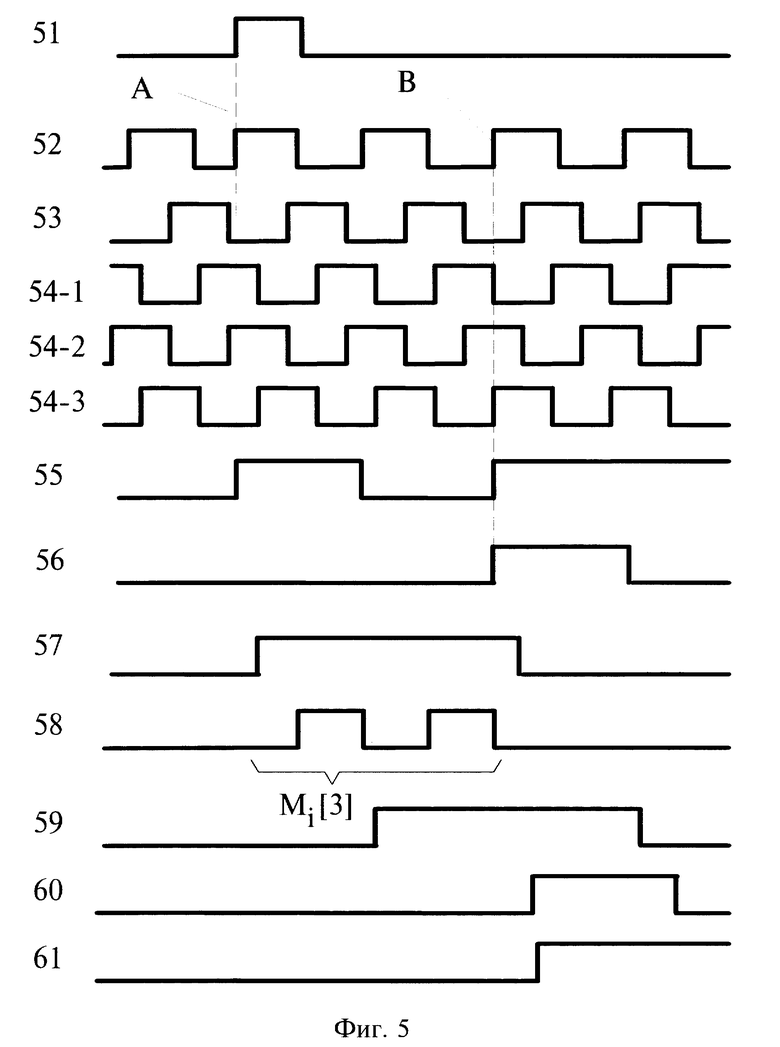

На фиг. 4 и 5 приведены временные диаграммы работы нониусного блока, изображенного на фиг. 2, при n=4 в режимах калибровки и измерения соответственно. Следует отметить, что при n=4 нониусный блок имеет четыре схемы детектирования 16-1, . .. 16-n, четыре управляемых формирователя 17-1, ... 17-n, на входы с четвертого по шестой нониусного блока поступают три вспомогательных сигнала, с выхода регистра 29 выдается четырехразрядный код j.

На фиг. 4 изображено: 43 - сигнал на выходе подстраиваемого генератора 13 (см. фиг. 2); 44 - основной опорный сигнал, поступающий на второй вход нониусного блока с выхода опорного генератора 1 (см. фиг. 1); 45-1, 45-2 и 45-3 - первый, второй и третий вспомогательные сигналы, поступающие на входы нониусного блока с четвертого по n+2-й; 46 - сигнал на выходе четвертой схемы детектирования 16-n (n=4); 47 - сигнал на выходе четвертого управляемого формирователя 17-n (n= 4); 48 - сигнал на выходе первого элемента задержки 23; 49 - сигнал на первом выходе нониусного блока (выход второго триггера 22), 50 - сигнал на втором выходе нониусного блока (выход первой схемы И 25).

На фиг. 5 изображено: 51 - сигнал на выходе формирователя запуска 12; 52 - сигнал на выходе подстраиваемого генератора 13; 53 - основной опорный сигнал, поступающий на второй вход нониусного блока; 54-1, 54-2 и 54-3 - первый, второй и третий вспомогательные сигналы, поступающие на входы нониусного блока с четвертого по n+2-й; 55 - сигнал на выходе четвертой схемы детектирования 16-n (n=4); 56 - сигнал на выходе четвертого управляемого формирователя 17-n (n=4); 57 - сигнал на выходе первого элемента задержки 23; 58 - сигнал на втором выходе нониусного блока; 59 - сигнал на выходе второго элемента задержки 24; 60 - сигнал на выходе n+1-го (n=4) элемента задержки 27-m (m=n-1=3); 61 - сигнал на первом выходе нониусного блока (выход второго триггера 22).

В режиме калибровки сигналы запуска на первый вход нониусного блока не поступают, поэтому фаза сигнала 43 на выходе подстраиваемого генератора 13 не изменяется. На выходе делителя 14 вырабатывается сигнал с периодом Тд = К•Тн, который поступает на первый вход фазового детектора 15. Схемы детектирования 16-1 ... 16-n реализованы на D-триггерах с динамическим запуском, при этом на входы "D" этих триггеров поступают сигналы с входов 2, 4 ... n+2 нониусного блока, на входы синхронизации "C" поступает сигнал с выхода подстраиваемого генератора 13, а на входы "S" установки D-триггеров поступает сигнал с выхода формирователя запуска 12. Когда сигналы на входы установки "S" не поступают, на выходах схем детектирования 16-1 ... 16-n вырабатываются сигналы с одинаковой частотой fсд = fо - fн = 1/Тсд(fо=1/То, fн = 1/Тн), причем в момент совпадения фаз (передних фронтов) сигналов на входах схем 16-1 ... 16-n на их выходах происходит переключение из нуля в единицу. Сигнал с выхода первой схемы детектирования 16-1 поступает на второй вход фазового детектора 15, который управляет частотой подстраиваемого генератора 13 так, чтобы поддерживать равенство периодов Тд и Тсд, что в свою очередь обеспечивает выполнение соотношения (2).

В режиме калибровки переключатели 18, 19 и 20 находятся в первом положении, они пропускают сигналы, поступающие на их первые входы. Таким образом на вход установки первого триггера 21 поступает сигнал с второго выхода схемы запуска 32, на вход сброса первого триггера 21 поступает сигнал с выхода первого управляемого формирователя 17-1, на вторые (управляющие) входы формирователей 17-1, ... 17-n поступает уровень логической единицы. Коммутатор 31 пропускает на свой выход сигнал, для которого в данный момент производится калибровка. На фиг. 4 приведена временная диаграмма для случая, когда производится калибровка для третьего вспомогательного сигнала 45-3, который поступает на n+2-й вход нониусного блока (n=4), то есть на вход четвертой схемы детектирования 16-n.

Поскольку схемы детектирования реализованы на D -триггерах, то, как отмечено выше, при совпадении фаз (передних фронтов) нониусного сигнала на выходе подстраиваемого генератора 13 и выбранного вспомогательного сигнала (на фиг. 4 третьего сигнала 45-3) в точке A (см. фиг. 4), сигнал 46 на выходе четвертой схемы детектирования 16-n (n=4) переходит из нулевого состояния в единичное. Это вызывает появление импульса на выходе четвертого управляемого формирователя 17-n (см. сигнал 47 на фиг. 4), который, проходя через коммутатор 31, через схему запуска 32, через первый переключатель 18, устанавливает первый триггер 21 в единичное состояние, что вызывает появление единичного уровня на выходе первого элемента задержки 23 (см. сигнал 48). Это разрешает прохождение сигналов с выхода подстраиваемого генератора 13 через инверсный вход первой схемы И 25 на второй выход нониусного блока. Величина задержки первого элемента задержки 23 должна составлять около четверти периода подстраиваемого генератора 13, чтобы обеспечить надежное управление прохождением импульсов через первую схему И 25.

При совпадении фаз сигнала 43 подстраиваемого генератора 13 и основного опорного сигнала 44 в точке В сигнал на выходе первой схемы детектирования 16-1 переходит из нулевого состояния в единичное. Это вызывает появление импульса на выходе первого управляемого формирователя 17-1, который через первый вход третьего переключателя 20 сбрасывает первый триггер 21, что прекращает прохождение импульсов с выхода подстраиваемого генератора 13 через первую схему И 25 на второй выход нониусного блока. Одновременно через первую схему ИЛИ 28 и вторую схему И 26 устанавливается в единичное состояние второй триггер 22, единичный сигнал на выходе которого свидетельствует об окончании работы (см. сигнал 49).

В режиме измерения переключатели 18, 19 и 20 находятся во втором положении (пропускают сигналы со своих вторых входов). На вход установки первого триггера 21 поступает сигнал с выхода формирователя запуска 12, на вторые (управляющие) входы формирователей 17-1 ... 17-n поступают сигналы с выхода второго элемента задержки 24, на вход сброса первого триггера 21 поступает сигнал с выхода второй схемы ИЛИ 30.

При поступлении сигнала запуска на первый вход нониусного блока на выходе формирователя запуска 12 вырабатывается импульс (см. сигнал 51 на фиг. 5), который устанавливает новую фазу колебаний сигнала 52 на выходе подстраиваемого генератора 13. Одновременно этим же импульсом, проходящим через первый переключатель 18, устанавливается в единичное состояние первый триггер 21, после чего на выходе первого элемента задержки 23 устанавливается высокий уровень (см. сигнал 57), который разрешает прохождение импульсов с выхода подстраиваемого генератора 13 через инверсный вход первой схемы И 25 на второй выход нониусного блока (см. сигнал 58 на фиг. 5).

При совпадении фаз (передних фронтов) сигнала 52 на выходе подстраиваемого генератора 13 с любым из сигналов, поступающих на входы 2, 4, ... n+2 на выходе соответствующего управляемого формирователя 17-1 ... 17-n вырабатывается импульс. На фиг. 5 показано совпадение в точке В с третьим вспомогательным сигналом 54-3, при этом вырабатывается импульс на выходе четвертого управляемого формирователя 17-n (см. сигнал 56). Этот импульс поступает на вход второй схемы ИЛИ 30 и проходит на ее выход. Этим сигналом с выхода второй схемы ИЛИ 30 первый триггер 21 сбрасывается в нулевое состояние, и прохождение сигналов через первую схему И 25 прекращается.

Одновременно на выходе первой схемы ИЛИ 28 вырабатывается сигнал об окончании, синхронный к основному опорному сигналу 53. Последнее достигается тем, что для каждого из вспомогательных сигналов вводятся задержки, величина ti которых для i-ro вспомогательного сигнала выбирается из соотношения ti + tio = Тo, где tio - задержка i-ro

вспомогательного сигнала на секционированной линии задержки 2 по отношению к основному опорному сигналу на выходе опорного генератора 1 (см. фиг. 1). Например, при n= 4 для третьего вспомогательного сигнала значение ti примерно равно Тo/4. Эта задержка осуществляется на (n+1)-м элементе задержки 27-m (см. сигнал 60). Таким образом, сигнал на выходе первой схемы ИЛИ 28 вырабатывается примерно в одно время со следующим передним фронтом сигнала опорного генератора. Импульс с выхода первой схемы ИЛИ 28, проходя через вторую схему И 26, устанавливает второй триггер 22 в единичное состояние (см. сигнал 61), что приводит к выработке на первом выходе нониусного блока сигнала окончания преобразования. Так как сигнал на выходе первой схемы ИЛИ 28 задержан до ближайшего фронта сигнала опорного генератора, то сигнал на первом выходе нониусного блока будет синхронным с основным опорным сигналом.

Кроме того, по спаду сигнала 57 на выходе первого элемента задержки 23 в регистр 29 записывается информация о том, с каким из сигналов произошло совпадение. В случае, показанном на фиг. 5, в регистр будет записан код, содержащий единицу в разряде, соответствующем третьему вспомогательному сигналу, а в остальных разрядах будут нули. При указанной реализации код на выходе регистра 29 будет унитарным и потому избыточным. Для сокращения разрядности на выходе регистра можно включить кодопреобразователь, однако это увеличит аппаратные затраты. Введение кодопреобразователя эффективно при большом количестве вспомогательных сигналов.

Величина задержки во втором элементе задержки 24 выбирается такой, чтобы предотвратить прохождение единичного уровня с выхода схем детектирования 16-1 ... 16-n при установке их в единичное состояние в момент запуска. Так, например, на фиг. 5 первый импульс с выхода четвертой схемы детектирования 16-n (см. сигнал 55) не проходит через четвертый управляемый формирователь 17-n, так как в этот момент времени сигнал 59 на выходе второго элемента задержки 24 равен нулю.

Таким образом, схема нониусного блока в режиме измерения обеспечивает выработку на втором выходе импульсов нониусного сигнала от момента запуска до момента совпадения с любым из вспомогательных сигналов или основным опорным сигналом, выработку на выходах с третьего по n+2-й кода, указывающего, с каким из сигналов произошло совпадение, а также выработку на первом выходе сигнала об окончании преобразования, синхронного к основному опорному сигналу.

На фиг. 6 показан возможный вариант реализации схемы запуска 32, входящей в состав нониусного блока, изображенного на фиг. 2. Эта схема обеспечивает в режиме калибровки однократный запуск по сигналу, поступающему на третий вход нониусного блока. В состав схемы запуска входят третий 62 и четвертый 63 триггеры, а также третья схема И 64.

На фиг. 7 показана временная диаграмма работы схемы запуска. На фиг. 7 изображено: 65 - вспомогательный сигнал, для которого проводится калибровка, 66 - сигнал, поступающий на третий вход нониусного блока (первый вход схемы запуска), 67 - сигнал на выходе коммутатора 31 (второй вход схемы запуска), 68 - сигнал на выходе третьего триггера 62, 69 - сигнал на выходе четвертого триггера 63, 70 - сигнал на выходе третьей схемы И 64, 71 - сигнал на выходе первого триггера 21, 72 - сигнал на выходе формирователя 17-1.

При поступлении сигнала на третий вход нониусного блока третий триггер 62 по заднему фронту (спаду) сигнала 67 с выхода коммутатора 31 устанавливается в единичное состояние. Следующий импульс с выхода коммутатора 31 пройдет через третью схему И 64 на второй выход схемы запуска, а затем через первый вход первого переключателя 18 поступит на вход установки первого триггера 21, который переключается в единичное состояние (см. сигнал 71 на фиг. 7). Этот же импульс с выхода коммутатора 31 своим спадом установит четвертый триггер 63 в единичное состояние (см. сигнал 69) и запретит дальнейшее прохождение импульсов с выхода коммутатора 31 через третью схему И 64. Таким образом, данная схема пропускает на свой второй выход только один импульс с выхода коммутатора 31 и обеспечивает однократный запуск нониусного блока при поступлении сигнала на третий вход нониусного блока.

На фиг. 8 раскрывается схема управляемых формирователей 17-1, ... 17-n, в состав которой входят формирователь импульсов 73 и четвертая схема И 74. Формирователь 73 формирует импульс длительностью примерно Тo. Если на второй (управляющий) вход поступает разрешающий сигнал, то импульс с выхода формирователя 73 проходит на выход, в противном случае на выходе схемы И вырабатывается уровень логического нуля.

Заявляемое устройство обладает повышенным быстродействием по сравнению с известными, что достигается применением вспомогательных опорных сигналов, сдвинутых друг относительно друга, при этом за счет введения режима калибровки, в котором определяются поправки, точность заявляемого измерителя по сравнению с известным не ухудшается.

Источники информации

1. Авторское свидетельство СССР N 930213, кл. G 04 F 10/00, 1982.

2. Электроника, 1977, N 23, с. 25-34.

Измеритель предназначен для измерения временных интервалов с высокой точностью и высоким быстродействием и может использоваться для контроля устройств вычислительной техники и систем передачи данных. Измеритель содержит опорный генератор, входное устройство, первый и второй нониусные блоки, ключ, основной, первый и второй нониусные счетчики, триггер, секционированную линию задержки с n - 1 выходами, блок фиксации и управления. Заявляемый измеритель имеет более высокое быстродействие по сравнению с известными устройствами. Повышение быстродействия достигается применением вспомогательных опорных сигналов, сдвинутых друг относительно друга, при этом за счет введения режима калибровки определяются поправки для вспомогательных сигналов. 1 з.п.ф-лы, 8 ил.

| Чу Д, Фергюссон К | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| - Электроника, 1977, N 23, с | |||

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

| Измеритель серии временных интервалов | 1980 |

|

SU930213A1 |

| SU 913328 A, 15.03.82 | |||

| Устройство и способ устранения колебаний оптического разряда | 2020 |

|

RU2738461C1 |

| US 3611134 A, 05.10.71. | |||

Авторы

Даты

1999-03-10—Публикация

1997-09-05—Подача