Изобретение относится к аналого-цифровому преобразованию напряжения для обеспечения цифрового представления входного сигнала напряжения. В частности, это изобретение относится к верньерной настройке, которая изменяет разрешающую способность аналого-цифровых преобразователей напряжения.

Измерительная схема, осуществляющая аналого-цифровое преобразование напряжения, в общем используется, чтобы преобразовать воспринятый параметр в цифровое представление воспринятого параметра для непосредственного анализа или для передачи в удаленное место. В управляющих системах воспринятый параметр измеряется и оценивается, чтобы определить соответствующие управляющие петлей настройки.

Типично скорость и точность критичны в эффективной работе управляющей петли. Всякий раз, когда скорость и точность могут быть увеличены, выгоды значительны. Например, в патенте США 4791352, озаглавленном "Передатчик с верньерным измерением", обеспечивает значительные улучшения в скорости и разрешающей способности цифровых преобразователей параметров при выполнении преобразований с множеством зарядовых пакетов, которые аккумулируются в интеграторе. Количество заряда в каждом пакете представляет воспринятый параметр. Аккумулированный заряд сравнивается с опорным уровнем и результирующий выход используется в качестве сигнала обратной связи, чтобы управлять аккумуляцией зарядовых пакетов в интеграторе. Число зарядовых пакетов, генерированное во время измерительного цикла, представляет воспринятый параметр. Цифровое представление воспринятого параметра определяется из сосчитанных чисел.

Улучшенная точность достигается в указанном патенте добавлением верньерной настройки к каждому измерительному циклу. Верньерная настройка - это настройка, которая изменяет разрешающую способность аналого-цифрового преобразователя напряжения. Во время первой части измерительного цикла множество первых зарядовых пакетов генерируется первым потенциалом возбуждения и обеспечивается "грубая" настройка заряда, аккумулированного в интеграторе. Во время второй части измерительного цикла множество зарядовых пакетов генерируется вторым потенциалом возбуждения, меньшим чем первый. Количество заряда в каждом зарядовом пакете изменяется с потенциалом возбуждения, и, следовательно, множество вторых зарядовых пакетов обеспечивает "точную" настройку заряда в интеграторе. Точная настройка обеспечивает значительно большую точность цифрового результата, чем "грубая" настройка.

Верньерное устройство по патенту обеспечивает улучшенное сочетание скорости и разрешающей способности, однако, генерирование грубого и точного потенциалов возбуждения (используя как резистивные, так и емкостные делители напряжения, операционные усилители с программируемой регулировкой усиления или другие делители напряжения) добавляют значительную сложность и необходимость в настройках схемы. С целью обеспечить удобный счет зарядовых пакетов, отношения резистивных делителей напряжения должны быть настроены на целое число и дополнительно согласованы друг с другом тем числом в обоих делителях.

Согласно изобретению передатчик воспринимает параметр, такой как давление, и обеспечивает выходное представление воспринятого параметра. Передатчик включает в себя аналого-цифровой преобразователь напряжения, имеющий верньерную настройку, чтобы получить ожидаемый технический результат - повысить быстродействие и разрешающую способность преобразования. Преобразование включает в себя один или более измерительных циклов, которые генерируют цифровые выходы, представляющие входные сигналы напряжения. Входные сигналы напряжения представляют воспринятый параметр.

Измерительная схема, реализованная в аналого-цифровом преобразователе напряжения, содержит запоминающую схему, соединенную с входными сигналами напряжения для обеспечения запоминающей емкости с множеством способных выбирать значений. Входные сигналы напряжения выборочно подаются на запоминающую емкость для периодического заряжения и разряжения запоминающей емкости и для обеспечения зарядового выхода, представляющего поданные входные сигналы напряжения и выбранные емкостные значения.

Аккумулирующая заряд схема присоединяется к зарядовому выходу для аккумулирования заряда из запоминающей схемы. Аккумулированный общий заряд пропорционален интегралу количества заряда, разряжаемого из запоминающей схемы. Аккумулирующая заряд схема обеспечивает балансовый выход, представляющий сравнение аккумулированного заряда и опорного заряда.

Тактовая схема соединяется с балансовым выходом для обеспечения сигналов обратной связи как функций балансового выхода, которые управляют заряжением и разряжением запоминающей емкости, чтобы генерировать последовательность зарядовых пакетов на зарядовом выходе. Первая последовательность зарядовых пакетов доводит аккумуляцию заряда до опорного заряда в первом ряду интервалов, когда первое емкостное значение выбирается в запоминающей схеме. Вторая последовательность зарядовых пакетов доводит аккумуляцию заряда до опорного заряда во втором ряду интервалов, когда выбирается второе емкостное значение.

Вычислительная схема соединяется с тактовой схемой для счета чисел зарядовых пакетов, генерированных в измерительном цикле. Вычислительная схема обеспечивает цифровые выходы, соединенные с выходной схемой, которая генерирует выходные сигналы, указывающие выходные сигналы напряжения как функции сосчитанных чисел. Построенная на основе измерительной схемы тензочувствительная измерительно-преобразовательная схема включает в себя первый и второй аналого-цифровые преобразователи напряжения в соответствии с настоящим изобретением, описанным выше. Измерительно-преобразовательная схема также включает в себя резистивный мост и по крайней мере один прецизионный резистор, соединенный последовательно с резистивным мостом. Резистивный мост реагирует на давление и температуру. Прецизионный резистор, однако, имеет сопротивление, которое меньше реагирует на температуру, чем резистивный мост. Первый аналого-цифровой преобразователь напряжения обеспечивает выход, представляющий падение напряжения на прецизионном резисторе и указывающий температуру резистивного моста. Второй аналого-цифровой преобразователь напряжения обеспечивает выход, представляющий приложенное давление и температуру резистивного моста. Вычислительная схема объединяет выход первого аналого-цифрового преобразователя напряжения с выходом второго аналого-цифрового преобразователя напряжения, чтобы генерировать цифровое представление приложенного давления, которое скорректировано по температуре.

Сущность изобретения заключается в том, что измерительная схема содержит блок переключения, блок накопления заряда, вычислительное устройство, генератор импульсов и устройство управления переключателями, причем первые выходы устройства управления переключателями соединены с управляющими входами блока переключения, первая группа входов блока переключения является информационным входом схемы, имеющей выход, который является выходом вычислительного устройства, первый выход блока переключения подключен через блок накопления заряда ко входу генератора импульсов, первый выход генератора импульсов соединен с первыми входами вычислительного устройства и устройства управления переключателями. Кроме того, в ней содержатся устройство запоминающих емкостей и устройство выбора запоминающей емкости, вход которого соединен со вторым выходом генератора импульсов, а выход устройства выбора запоминающей емкости подключен ко второму входу устройства управления переключателями, вход и выход устройства запоминающих емкостей соединены с соответствующими вторым выходом и второй группой входов блока переключения, вторые выходы устройства управления переключателями подключены ко вторым входам вычислительного устройства, устройство запоминающих емкостей содержит множество избирательно соединяемых конденсаторов, множество конденсаторов содержит первый конденсатор и второй конденсатор и соотношение емкостных значений первого и второго конденсаторов составляет (2n - 1):1, где n является целым числом. Кроме того схема аккумулирования заряда включает в себя компаратор, интегратор, причем вход компаратора подключен к выходу интегратора, вход интегратора подключен к первому выходу блока переключения, а выход компаратора подключен ко входу генератора импульсов, интегратор включает в себя операционный усилитель, связанный с конденсатором в петле отрицательной обратной связи.

При этом схема также содержит дополнительный блок переключения, дополнительное устройство выбора запоминающей емкости, дополнительный блок накопления заряда, дополнительное устройство запоминающих емкостей, резистор и резистивный мост Уитстона для измерения активного сопротивления, выполненный с возможностью изменения выходного сигнала в ответ на входное воздействие давления и температуры, причем первые выходы моста Уитстона для измерения активного сопротивления подключены к первой группе входов блока переключения, один из двух выходов моста Уитстона для измерения активного сопротивления через резистор, а другие непосредственно соединены с первой группой входов дополнительного блока переключения, первый выход дополнительного блока переключения соединен через дополнительный блок накопления заряда с дополнительным входом генератора импульсов, дополнительный выход генератора импульсов через дополнительное устройство выбора запоминающей емкости соединен с третьим входом устройства управления переключателями, дополнительные выходы устройства управления переключателями подключены к управляющим входам дополнительного блока переключения, второй выход и вторая группа входов дополнительного блока переключения соединены, соответственно, со входом и выходами дополнительного устройства запоминающих емкостей.

Согласно способу формирования информационного сигнала, входное воздействие преобразуют в электрический сигнал, на основании которого с помощью запоминающих емкостей формируют первый и второй сигналы, значения которых соответствуют набору величин противоположной полярности за счет зарядов и разрядов запоминающих емкостей, при этом суммарный заряд в части наборов зависит от величины входного воздействия, затем производят накопление полученных значений сигналов, сравнивают полученное значение накопленных сигналов с опорным значением, по результату сравнения управляют формированием сигналов каждой полярности путем регулирования накопления зарядов до порогового значения, результат измерения определяется через временной параметр, полученный из соотношения числа сформированных наборов величин зарядов и разрядов, число сформированных наборов величин зарядов и разрядов регулируют путем изменения емкостного значения запоминающих емкостей за счет использования двух отличных друг от друга по величине запоминающих емкостей, приводящего к изменению количества зарядов в наборах, первый и второй сигналы формируют при соответствии значения запоминающей емкости первой величине, при которой накопленные значения наборов соответствуют первому пороговому значению, дополнительно формируют третий и четвертый сигналы с помощью запоминающей емкости при соответствии ее значения второй величине, причем значения третьего и четвертого сигналов соответствуют наборам значений зарядов противоположной полярности, при этом суммарный заряд в части наборов зависит от величины входного воздействия, затем производят накопление полученных значений третьего и четвертого сигналов с последующим сравнением полученного значения со вторым пороговым значением, устанавливаемым по величине меньшей первого порогового значения и на основании результата сравнения формируют последовательность управляющих сигналов, временные параметры которых соответствует количеству наборов величин зарядов при двух условиях, когда значение запоминающей емкости равно первой величине и когда оно равно второй величине, кроме того результат измерения получают подсчетом количества наборов величин зарядов, по меньшей мере одной полярности, при этом результат измерения получают подсчетом количества наборов величин зарядов, в, по меньшей мере, первом и третьем сигналах, а емкостное значение запоминающих емкостей изменяют после того, как число сформированных наборов величин зарядов в первом сигнале, плюс число сформированных наборов величин зарядов во втором сигнале сравняется с первым заранее выбранным числом.

В соответствии со способом этап начала нового измерительного цикла начинается после того, как число сформированных наборов величин зарядов в третьем сигнале, плюс число сформированных наборов величин зарядов в четвертом сигнале сравняется со вторым заранее выбранным числом, емкостное значение запоминающих емкостей изменяют путем избирательного параллельного соединения двух отличных друг от друга по значению запоминающих емкостей, а соотношение емкостного значения двух отличных друг от друга по емкостному значению запоминающих емкостей составляет (2n-1):1, где n является целым числом.

Краткое описание чертежей

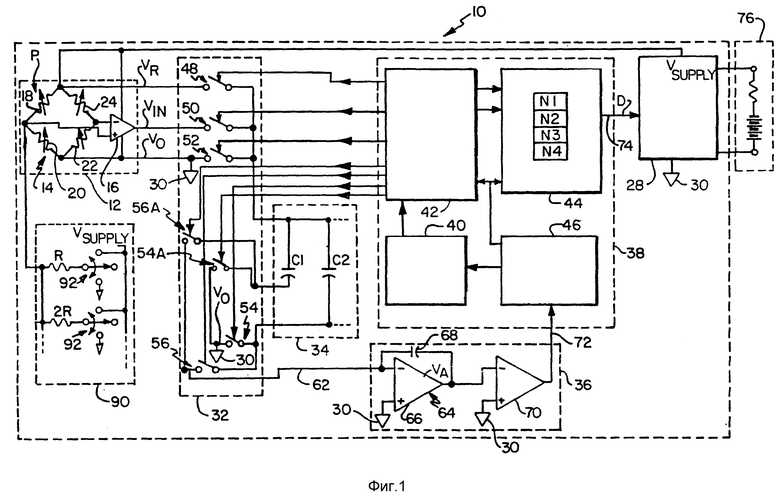

Фиг. 1 - диаграмма передатчика, содержащего аналого-цифровой преобразователь напряжения, соответствующий настоящему изобретению.

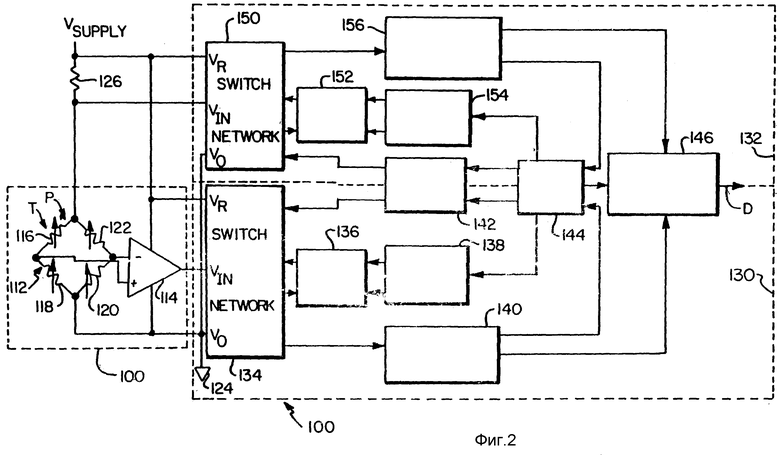

Фиг. 2 - диаграмма тензочувствительного датчика давления и процессора датчика, содержащего первый и второй аналого-цифровые преобразователи напряжения в соответствии с настоящим изобретением.

Подробное описание предпочтительных вариантов осуществления

Фиг. 1 иллюстрирует передатчик 10, который включает в себя аналого-цифровой преобразователь напряжения в соответствии с настоящим изобретением. Аналого-цифровой преобразователь напряжения выполняет серию последовательных измерительных циклов, чтобы преобразовать выход датчика параметра и выход передатчика, который представляет воспринятый параметр.\

В варианте осуществления, показанном на фиг. 1, передатчик 10 включает в себя тензочувствительную измерительную схему 12, которая реагирует на приложенное давление P. Тензочувствительная измерительная схема 12 включает в себя резисторный мост 14 и предусилитель 15. Резисторный мост 14 включает в себя резисторы 18, 20, 22 и 24, имеющие сопротивления, которые чувствительны к прилагаемому давлению P. Точка соединения между резисторами 18 и 24 присоединяется к питающему напряжению Vsupply в выходной схеме 28. Резисторный мост 14 электрически возбуждается Vsupply и присоединяется к системной "земле" 30 в точке соединения между резисторами 20 и 22. Потенциал выходного напряжения датчика, представляющий приложенное давление P, подается на предусилитель 16 в его инвертирующий (-) и неинвертирующий (+) входы. Инвертирующий (-) вход соединяется с точкой соединения между резисторами 22 и 24. Неинвертирующий (+) вход соединяется с точкой соединения между резисторами 18 и 20. Предусилитель 16 обеспечивает тензочувствительный измерительный выходной сигнал V1N, представляющий давление P в качестве входа передатчика. Входной сигнал передатчика VR присоединяется к Vsupply, которое обеспечивает сигнал опорного напряжения для передатчика 10. Входной сигнал передатчика V0 подается в точку соединения между резисторами 20 и 22 и к системной земле 30. Входные сигналы напряжения VR, V1N и V0 присоединяются, как описано выше, чтобы генерировать потенциалы напряжения V1 и VR, которые представляют давление P, приложенное к резисторному мосту 14. Потенциал напряжения V1 - это разность между VR и V1N. Потенциал напряжения V2 - это разность между V1N и V0.

Передатчик включает выключатель сети 32, являющийся блоком переключения, устройство запоминающей емкости 34, блок накопления или аккумулирования заряда 36, управляющую схему 38, которая содержит устройства управления переключателем памяти 40 для выбора запоминающей емкости, управления переключателем сети 42, вычислительное устройство 44, генератор тактовых импульсов 46, первый выход которого соединен с первыми входами устройств 44 и 42, второй выход соединен со входом устройства 40, выход которого подключен ко второму входу устройства 42, первые выходы которого соединены с управляющими входами блока переключения, вторые выходы соединены со вторыми входами устройства 44.

Вход и выход устройства 34 соединены со вторым выходом и второй группой входов блока 32, первая группа входов которого является информационным входом схемы, выходом которой является выход устройства 44.

Первый выход блока 32 через блок 35 подключен ко входу тактовой схемы, которая замыкает петлю обратной связи между схемой 36 и устройствами 40 и 42.

Вычислительная схема 44 определяет цифровое значение D, представляющие давление P, приложенное к резисторному мосту 14.

Входные напряжения передатчика VR, V1N и V0 подаются на переключатели 48, 50 и 52, соответственно, в выключателе сети 32. Управление выключателем сети 42 воздействует на переключатели 48, 50 и 52, чтобы выборочно подавать напряжение VR, VIN и V0 в запоминающую схему 44. Управление выключателя сети 42 также воздействует на переключатели 54, 54A и 56, 56A, подавая выбранные входы напряжения и запоминающую схему 34 и присоединения запоминающую схему 34 к земле 30.

Запоминающая схема 34 содержит запоминающую емкость, созданную конденсаторами C1 и C2. Переключатели 54, 54A и 56, 56A дают возможность запоминающей емкости иметь выбираемые значения. Конденсатор C1, имеющий меньшее значение емкости, выбирается переключателями 54A и 56A. Альтернативно, большее значение емкости выбирается также замыканием переключателей 54 и 56, чтобы создать параллельную комбинацию конденсаторов C1 и C2. В одном варианте осуществления конденсатор C1 имеет значение емкости C, и конденсатор C2 имеет значение емкости 2N -1/С, где C - это мера емкости, и N - это заранее выбранное число, которое определяет отношение C1 к C2. Следовательно, параллельное сочетание C1 и C2 имеет значение емкости 2NC.

Во время измерительного цикла управление выключателем сети 42 управляет переключателями 48, 50, 52, 54, 54A и 56, 56A в выключателе сети 32 для попеременного заряжения и разряжения запоминающей емкости в запоминающей схему 34. Управление выключателем сети 42 сперва замыкает выбранные переключатели в выключателе сети 32, чтобы присоединить запоминающую емкость между системной землей 30 и выбранным одним из входных напряжений передатчика V0, V1N или VR. Выбранный заряд сохраняется на запоминающей емкости, когда выбранные переключатели размыкаются. Далее, управление переключателем сети 42 замыкает другие выбранные переключатели в выключателе сети, чтобы разряжать запоминающую емкость и генерировать зарядовый пакет на зарядовом выходе 62 через переключатель 56. Термин "пакет" относится к дискретному количеству электрического заряда, который течет в или из емкости, когда она заряжается из первого потенциала напряжения во второй потенциал напряжения, отличный от первого потенциала. Количество заряда в зарядовом пакете - это функция запоминающей емкости, потенциал напряжения, поданный, когда запоминающая емкость была заряжена, и потенциал напряжения, поданный, когда запоминающая емкость заряжается.

В одном варианте осуществления потенциалы напряжений V1 и V2 выборочно подаются в запоминающую схему 34, чтобы заряжать запоминающую емкость или до первого запасенного заряда, имеющего первую полярность, или до второго запасенного заряда, имеющего вторую полярность, противоположную первой полярности. Суммирующие или вычитающие зарядовые пакеты генерируются первым и вторым запасенными зарядами, соответственно.

Во время первой части измерительного цикла управляющая схема 38 воздействует на управление переключателем памяти 40, чтобы управлять управлением выключателя сети 42, чтобы выбирать большее значение емкости 2NC замыканием переключателей 54, 54A и 56, 56A в запоминающей схеме 34. Управление выключателем сети 42 воздействует на выбранные переключатели в выключателе сети 32, чтобы попеременно заряжать и разряжать запоминающую емкость для генерирования первой последовательности суммирующих и вычитающих зарядовых пакетов на зарядовом выходе 62. Число отдельных суммирующих и вычитающих зарядовых пакетов может изменяться, но общее число зарядовых пакетов (N1 + N2) в первой последовательности останавливается на предварительно выбранном числе, где N1 = подсчет зарядовых пакетов, обеспечивающий заряд со значением (2NCV1) для интегратора 64; N2 = подсчет зарядовых пакетов, обеспечивающих заряд со значением (2NCV2) для интегратора 64.

Отдельные числа N1 и N2 зарядовых пакетов в первой последовательности могут соответствовать или суммирующим или вычитающим зарядовым пакетам в зависимости от полярностей V1 и V2, как они подаются в запоминающую схему.

Аккумулирующая заряд схема 36 присоединяется к зарядовому выходу 62 и содержит интегратор 64, который аккумулирует суммирующие и вычитающие зарядовые пакеты из зарядового выхода 62. Интегратор 64 содержит усилитель 66 и конденсатор 68. Неинвертирующий вход (+) усилителя 66 присоединяется к системной земле 30. Инвертирующий (-) вход усилителя 66 присоединяется к зарядовому выходу 62. Конденсатор 68 присоединяется между инвертирующим входом и выходом усилителя 66. Интегратор 64 аккумулирует зарядовые пакеты, генерированные на зарядовом выходе 62, используя время интеграции тока, генерированного зарядовыми пакетами. Суммирующие и вычитающие зарядовые пакеты добавляются или вычитаются из аккумулированного заряда. Выходной потенциал VA генерируется усилителем 66 и представляет количество заряда, аккумулированного интегратором 64. Выход присоединяется к инвертирующему (-) входу компаратора 70. Неинвертирующий (+) вход компаратора 70 присоединяется к системной земле 30 и представляет опорный уровень. Компаратор 70 обеспечивает балансовый выход 72, указывающий сравнение между аккумулированным зарядом и опорным зарядом.

Тактовая схема 46 осуществляет текущий контроль балансового выхода 72, определяет, находится ли аккумулированный заряд выше или ниже опорного заряда, и затем воздействует на управление выключателем сети 42, чтобы выборочно генерировать суммирующий или вычитающий зарядовые пакеты, чтобы направлять аккумулированный заряд к опорному заряду внутри первого ряда интервалов. Первый ряд интервалов определяется во время первой части измерительного цикла выбранной большей запоминающей емкостью 2NC и величиной приложенных напряжений V1 и V2.

Первый ряд интервалов определяет грубую настройку аккумулированного заряда в интеграторе 64 по отношению к опорному заряду. Баланс заряда в интеграторе 64 после первой части измерительного цикла приближается к балансу, показанному уравнением 1 ниже:

N12NCV1=N22NCV2 (1)

Во время второй части измерительного цикла управление переключателем памяти 40 управляет управлением выключателя сети 42, чтобы выбирать меньшую величину емкости C в запоминающей схеме 34 с помощью размыкания переключателей 54 и 56. Управление выключателем сети 42 затем воздействует на выбранные переключатели и выключателе сети 32, чтобы генерировать вторую последовательность суммирующих и вычитающих зарядовых пакетов. Общее число зарядовых пакетов (N3 + N4) во второй последовательности также останавливается на предварительно выбранном числе. Где N3 - подсчет зарядовых пакетов, обеспечивающий заряд с значением (CV1) для интегратора 64; V4 - подсчет зарядовых пакетов, обеспечивающих заряд с значением (CV2) для интегратора 64.

Вычислительная схема 44 поддерживает подсчет отдельных зарядовых пакетов N1, N2, N3 и N4 во время первой и второй частей измерительного цикла.

Количество заряда в каждом зарядовом пакете меньше во второй части измерительного цикла, чем в первой, так как каждый пакет во второй последовательности генерируется разряжением меньшей величины емкости C, а не 2NC. Каждый зарядовый пакет во второй последовательности аккумулируется интегратором 64. Управление выключателем сети 42 выборочно генерирует симмурирующие и вычитающие зарядовые пакеты для направления аккумулированного заряда в интегратор 64 к опорному заряду внутри второго ряда интервалов. Второй ряд интервалов меньше, чем первый ряд интервалов (что в результате ведет к большей разрешающей способности), так как количество заряда в каждом зарядовом пакете меньше во второй части измерительного цикла, чем в первой. Меньшие зарядовые пакеты обеспечивают точную настройку заряда, аккумулированного в интеграторе 64, Аккумулированный заряд балансируется по первой и второй части измерительного цикла, приближающимся к уравнению 2

(N12NCV1) + (N3CV1) = (N22NCV2) = (N4CV2) (2)

Члены в уравнении 2 могут быть перестроены, чтобы обеспечить выражение для соотношения V1/V2:

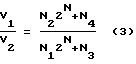

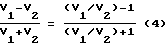

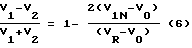

Входное напряжение передатчика V1N по существу пропорционально воспринятому параметру и опорному напряжению VR. Величина (V1 - V2)/(V1 + V2), таким образом, представляет воспринятый параметр, но независящий от опорного напряжения VR. Уравнение (3) заменяется на уравнение (4) ниже, чтобы обеспечить уравнению (5), которое выражает (V1-V2)/(V1+V2) в виде отношения 2N и подсчетов N1, N2, N3 и N4.

Под управлением сил связи, фиксирующих (N2+N1) и (N4+N3), которые служат предварительно выбранными числами, знаменатель правой части уравнения (5) - это величина, фиксированная управляющей схемой и отношением 2N большей и меньшей запоминающей емкостей. Это ограничивает требование для деления каждый раз, когда измерение возобновляется. Левая сторона уравнения (5) может быть переписана в виде входного напряжения передатчика V1N и опорного напряжения VR, как показано в уравнении (6)

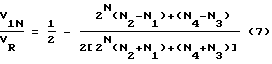

Когда V0 = 0, уравнения (5) и (6) могут быть суммированы, чтобы дать уравнение (7)

Левая часть уравнения (7) пропорциональна входному напряжению V1N, а первая часть уравнения (7) является функцией числа зарядовых пакетов, сосчитанных во время измерительного цикла. Устройство, таким образом, выполняет преобразование из входного напряжения в цифровое число, представляющее входное напряжение. Входное напряжение V1N пропорционально VR, так как VR - это потенциал, который питает резисторный мост 14. Отношение V1N/VR, таким образом, не зависит от VR.

В уравнении (7) выше все величины в правой части уравнения являются полными числами, или целыми числами, таким образом упрощая цифровое вычисление. Вычисление правой части уравнения (7) может быть дополнительно упрощено в дополнительном предпочтительном варианте осуществления, чтобы устранить необходимость вычитания каждый раз, когда выход обновляется. Числа N и (N1+N2) = K1 и (N3+N4)=K2 в знаменателе уравнения (7) могут быть все заранее определены или фиксированы преднамеренно, и, следовательно, знаменатель сам становится постоянным, фиксированным преднамеренно. Заменяющие константы K1 и K2 в уравнении (7) и упрощение обеспечивают уравнение (8)

В уравнении (8) знаменатель фиксируется, и единственные изменения в уравнении - это N1 и N3. Знаменатель, таким образом, становится масштабным фактором, и вычисление выхода может быть выполнено, используя только две переменные N1 и N3. Альтернативно, равенство (7) может быть обработано так, чтобы дать в результате уравнение, которое зависит только от переменных N2 и N4. Расчет в вычислительной схеме 44, таким образом упрощается.

По уравнениям (7) и (8) вычислительная схема 44 может определять цифровые значения D из сосчитанных чисел зарядовых пакетов. Цифровые значения D представляют давление P, приложенное к резисторному мосту 14. Каждый последующий измерительный цикл обновляет цифровые значения D, и вычислительная схема 44 подает их на выход 74. Выходная схема 28 присоединяется к выходу 74 и преобразует каждое значение D в аналоговую величину, такую как ток для передачи в удаленное место через передающую петлю 76. Передающая петля 76 может быть двухпроводной 4-20 миллиамперной передающей петлей. Управляющая схема 38 генерирует каждое обновленное значение D с постоянной скоростью, вследствие сил связей в общем числе зарядовых пакетов, которые генерируются во время каждой части измерительного цикла. Зарядовые пакеты обеспечиваются на фиксированной скорости повторения. Это упрощает цифроаналоговое преобразование, выполняемое выходной схемой 28, так как обновление поступает в предопределенное время.

Вычислительная схема 44 управляет накоплением окончательных подсчетов N1, N2, N3 и N4 отдельных суммирующих и вычитающих зарядовых пакетов во время каждой части измерительного цикла и управляет вычислением цифровых значений D в конце каждого измерительного цикла.

Любой зарядовый дисбаланс, еще остающийся в интеграторе 64 после грубой и точной настройки, переносится в следующий измерительный цикл. Ошибки в последовательности цифровых значений D стремится усредняться до нуля или аннулироваться по времени. Выход передатчика на петле 76, интегрированный по времени, таким образом, по существу свободен от ошибок, вследствие заряда, остающегося в интеграторе 64 в конце каждого измерительного цикла. Использование меньшего и большего значений емкости обеспечивает верньерную настройку с заданным сочетанием возросшей скорости и разрезающей способности.

В альтернативном варианте осуществления (не показан) запоминающая схема 34 содержит больше, чем два конденсатора, чтобы обеспечить запоминающую емкость, имеющую большее число избираемых значений. Измерительный цикл делится соответственно, чтобы обеспечить дополнительные уровни разрешающей способности вне "грубой" и "точной" настроек, описанных выше. На каждом уровне разрешающей способности дополнительные зарядовые пакеты генерируются, чтобы балансировать аккумулированный заряд по отношению к опорному заряду. Числа генерированных дополнительных зарядовых пакетов пересчитываются и добавляются как новые члены в уравнение 2. Вычислительная схема 44 настраивается, чтобы приспосабливать дополнительно подсчитанные числа и чтобы при этом увеличить точность цифровых значений D.

Схема смещения 90 может быть предусмотрена, чтобы обнулить выход моста 14 во время изготовления. Схема смещения 90 может содержать R-2R схему лестничного типа, присоединенную к трехпозиционным переключателям 92, как показано, или другая смещающая схемотехника, такая как различные цифроаналоговые преобразователи, может быть использована. Во время изготовления переключателя 92 настраиваются, наблюдая электрический выход моста 14, до тех пор, пока выход 14 не настроится на заданный уровень.

Фиг. 2 иллюстрирует процессор датчика, имеющий два аналого-цифровых преобразователя напряжения в соответствии с настоящим изобретением, как описано выше. Два преобразователя одновременно преобразуют напряжения в цифровые значения, представляющие давление и температуру, прилагаемые к тензометру. Преобразователи объединяются, чтобы генерировать цифровое представление давления, скорректированное по температуре, и температуру, скорректированную по давлению.

Тензочувствительная измерительная схема 110 включает в себя резисторный мост 112 и предусилитель 114. Резисторный мост 112 включает в себя резисторы 116, 118, 120 и 122. Предусилитель 114 включает в себя инвертирующий (-) и неинвертирующий (+) входы, которые присоединяются к резисторному мосту 112 в точках соединения между резисторами 116 и 118 и между резисторами 120 и 122, соответственно. Предусилитель 114 также присоединяется между питающим напряжением Vsupply и системной землей 124. Резисторный мост 112 присоединяется к системной земле 124 в точке соединения между резисторами 118 и 120. Прецизионный резистор 126 присоединяется между питающим напряжением Vsupply и резисторным мостом 112 в точке соединения между резисторами 116 и 122.

Процессор датчика 100 содержит первый и второй аналого-цифровые преобразователи напряжения 130 и 132: которые объединяются, чтобы пользоваться общей схемотехникой. Первый и второй аналого-цифровые преобразователи напряжения 130 и 132 каждый соответствует настоящему изобретению, как описано выше. Первый аналого-цифровой преобразователь напряжения 130 содержит выключатель сети 134, запоминающую схему 136, управление переключателем памяти 138, аккумулирующую заряд схему 140, управление выключателем сети 142, тактовую схему 144 и вычислительную схему 146. Выключатель сети 134 содержит входы напряжений VR, V1N и V0. Вход напряжения VR, присоединяется к питающему напряжению Vsupply для обеспечения опорного напряжения, указывающего потенциал напряжения, приложенного к мосту 112. Вход напряжения V0 присоединяется к системной земле 124. Выход предусилителя 114 присоединяется к входу напряжения V1N, чтобы обеспечить входные сигналы напряжения, представляющие напряжение P и температуру T, прилагаемые к резисторному мосту 112. Управление выключателя сети 142 воздействует на выключатель сети 134, чтобы выборочно подавать входные напряжения VR, V1N и V0 на запоминающую схему 136, пока первый аналого-цифровой преобразователь напряжения осуществляет измерительные циклы, чтобы получить цифровые значения, представляющие давление P и температуру T, приложенные к резисторному мосту 112.

Сопротивления резисторного моста 112 чувствительны к температуре, которая заставляет их выходы напряжения нежелательно изменяться с температурой. Чтобы преодолеть эту проблему, мост 112 электрически возбуждается питающим напряжением Vsupply через прецизионный резистор 126, который относительно нечувствителен к температуре по отношению к мосту 112. Потенциал напряжения V4 на резисторе 126 является при этом функцией температуры T резисторного моста 112. Потенциал напряжения V4 подается на выключатель сети 150 второго аналого-цифрового преобразователя напряжения 132 через входы напряжений VR и V1N. Вход напряжения V0 выключателя сети 150 присоединяется к системной земле 124. Второй аналого-цифровой преобразователь напряжения 132 содержит выключатель сети 150, запоминающую схему 152, управление переключателем памяти 154, аккумулирующую заряд схему 156, управление выключателем сети 142, тактовую схему 144 и вычислительную схему 146. Потенциал напряжения V4 преобразуется вторым аналого-цифровым преобразователем напряжения 132 в цифровое представление, указывающее температуру T, приложенную к резисторному мосту 112 тензочувствительной измерительной схемы 110.

Первый и второй аналого-цифровые преобразователи напряжения 130 и 132 используются управлением выключателя сети 142, тактовый схемой 144 и вычислительной схемой 146. Это уменьшает количество схемотехники, содержащей процессор датчика 100. Так как тактовая схема 144 является общей для первого и второго аналого-цифровых преобразователей напряжения 130 и 132, то работа обоих преобразователей предпочтительно синхронизируется так, чтобы оба преобразователя начинали и завершали измерительные циклы в одно и то же время. Цифровые представления давления P и температуры T являются при этом коррелированными по времени друг с другом, допуская простое вычисление вычислительной схемы 146 цифрового представления давления P, приложенного к тензочувствительной измерительной схеме 112, корректированной по температуре T, используя только самые последние значения, полученные для давления P и температуры T.

Процессор датчика 100, тензочувствительная измерительная схема 112 и прецизионный резистор 126 могут быть включены в передатчик, где по существу вся емкость для цифровой преобразовательной схемотехники включается в единый комплементарный металл-оксидный полупроводник (КМОП), наложенную особую интегральную схему (ASIC). Это обеспечивает предпочтительно компактный маломощный передатчик.

Несмотря на то, что настоящее изобретение описано со ссылкой на предпочтительные варианты осуществления, специалисты в данной области признают, что изменения могут быть сделаны в форме и деталях, не отступая от духа и объема изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИЗМЕРИТЕЛЬНАЯ СХЕМА | 1987 |

|

RU2133969C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДАВЛЕНИЯ | 1993 |

|

RU2139509C1 |

| МУЛЬТИФАЗНАЯ ИЗМЕРИТЕЛЬНАЯ СИСТЕМА С СИНХРОНИЗИРОВАННЫМИ СИГМА-ДЕЛЬТА КОНВЕРТОРАМИ | 2004 |

|

RU2379831C2 |

| ИЗМЕРИТЕЛЬНАЯ ЦЕПЬ С ДАТЧИКАМИ ИЗ ШУНТИРОВАННЫХ КОНДЕНСАТОРОВ | 2003 |

|

RU2301405C2 |

| ЭКРАНИРОВАННЫЙ ЕМКОСТНОЙ ДАТЧИК | 1994 |

|

RU2144680C1 |

| ПОЛЕВОЙ ПЕРЕДАТЧИК С ДИАГНОСТИЧЕСКИМ РЕЖИМОМ САМОТЕСТИРОВАНИЯ | 2003 |

|

RU2359281C2 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ДАВЛЕНИЯ С ЕМКОСТНЫМ ДАТЧИКОМ В ЦЕПИ ОБРАТНОЙ СВЯЗИ УСИЛИТЕЛЯ | 2003 |

|

RU2319124C2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ОБНАРУЖЕНИЕМ ОШИБОК, СВЯЗАННЫХ С ВЫХОДОМ ЗА ПРЕДЕЛЫ ДИАПАЗОНА | 2005 |

|

RU2341893C2 |

| ВНЕПУЛЬТОВЫЙ ДАТЧИК ДЛЯ ЗАПОМИНАНИЯ ИНФОРМАЦИИ | 1995 |

|

RU2143129C1 |

| ЦЕПЬ ЕМКОСТНОГО ДАТЧИКА | 2007 |

|

RU2401987C2 |

Изобретение относится к измерительной технике и может быть использовано для аналого-цифрового преобразования. Техническим результатом является повышение быстродействия и разрешающей способности. Схема содержит блок переключения, блок накопления заряда, вычислительное устройство, генератор импульсов, устройство управления переключателями, устройство запоминающих емкостей и устройство выбора запоминающей емкости. В способе число сформированных наборов величин зарядов и разрядов регулируют путем изменения емкостного значения запоминающих емкостей. 2 с. и 12 з.п.ф-лы, 2 ил.

| US 4791352 A, 13.12.88 | |||

| Устройство для регистрации кратковременных замыканий и размыканий электрических контактов | 1987 |

|

SU1499267A2 |

| Цифровой измеритель сопротивления | 1987 |

|

SU1522119A1 |

Авторы

Даты

1999-09-10—Публикация

1990-08-30—Подача