Изобретение относиться к радиотехнике и может использоваться в передающей аппаратуре телеграфной связи.

Известно устройство для формирования многочастотного сигнала, содержащее опорный генератор, блок установки фаз, фазовращатель, выходной сумматор и два канала формирования сигналов, каждый из которых выполнен в виде последовательно соединенных блока делителей частоты с управляемыми фазами, канального сумматора и перемножителя.

Однако известное устройство не может формировать многочастотные сигналы двухчастотной и четырехчастотной телеграфии.

Наиболее близким по технической сущности к изобретению является устройство для формирования сигналов двухчастотной и четырехчастотной телеграфии, содержащее последовательно соединенные опорный генератор и многоотводный делитель частоты, последовательно соединенные шифратор, формирователь кодовой последовательности, второй блок памяти, накапливающий сумматор, первый блок памяти, цифроаналоговый преобразователь и фильтр нижних частот, причем тактовые входы накапливающего сумматора и формирователя кодовой последовательности подключены к выходам многоотводного делителя частоты.

Однако известное устройство не предназначено для формирования многочастотного сигнала.

Задачей изобретения является обеспечение формирования многочастотного сигнала двухчастотной и четырехчастотной телеграфии.

Для этого в устройство для формирования сигналов двухчастотной и четырехчастотной телеграфии, содержащее последовательно соединенные опорный генератор и многоотводный делитель частоты, последовательно соединенные шифратор, формирователь кодовой последовательности, второй блок памяти, накапливающий сумматор и первый блок памяти, последовательно соединенные цифроаналоговый преобразователь и фильтр нижних частот, при этом тактовые входы накапливающего сумматора и формирователя кодовой последовательности подключены к выходам многоотводного делителя частоты, введены мультиплексор, на управляющий вход которого поступает внешняя команда, последовательно соединенные третий блок памяти и первый умножитель, последовательно соединенные четвертый блок памяти и второй умножитель, сумматор, входы которого подключены к выходам умножителей, счетчик адреса, пятый и шестой блоки памяти, входы которых подключены к выходу счетчика адреса, а выходы подключены ко вторым входам умножителей, при этом входы третьего и четвертого блоков памяти подключены к выходу накапливающего сумматора, выходы сумматора и первого блока памяти подключены на первый и второй входы мультиплексора соответственно, выход мультиплексора подключен ко входу цифроаналогового преобразователя, причем тактовый вход счетчика адреса подключен к выходу многоотводного делителя частоты.

Предлагаемое техническое решение соответствует критерию изобретения "новизна", т.к. отличается от прототипа наличием новых функциональных элементов и новых связей между элементами.

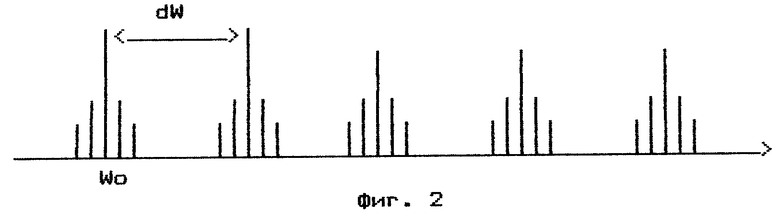

На фиг. 1 изображена структурная электрическая схема предлагаемого устройства, на фиг. 2 - спектр выходного сигнала.

Устройство содержит опорный генератор 1 (ОГ), многоотводный делитель 2 частоты (МДЧ), шифратор 3 (Ш), формирователь 4 кодовой последовательности (ФКП), второй блок 5 памяти (БП2), накапливающий сумматор 6 (НС), первый блок 7 памяти (БП1), цифроаналоговый преобразователь 8 (ЦАП), фильтр 9 нижних частот (ФНЧ), мультиплексор 10 (MX), третий блок 11 памяти (БП3), четвертый блок 12 памяти (БП4), пятый блок 13 памяти (БП5), шестой блок 14 памяти (БП6), первый умножитель 15 (УМ1), второй умножитель 16 (УМ2), сумматор 17 (СМ), счетчик адреса 18 (СА).

Все перечисленные блоки соединены следующим образом: 3-4-5-6-7-10-8-9, 6-11-15-17-10, 6-12-16-17, 1-2-6, 2-18-13-15, 18-14-16, 2-4.

Устройство работает следующим образом.

Устройство может работать как в одночастотном, так и в многочастотном режимах, для переключения служит внешняя команда, поступающая на управляющий вход мультиплексора 10.

В одночастотном режиме работы на выход мультиплексора 10 подключается сигнал с выхода первого блока 7 памяти, который выполняет функции кодового функционального преобразователя, где каждой кодовой комбинации текущей фазы ставится в соответствие код, несущий информацию о мгновенном значении сигнала в данный момент времени.

Адресные входы первого блока 7 памяти подключены к кодовым выходам накапливающего сумматора 6.

Код на выходе накапливающего сумматора 6 при каждом тактовом импульсе на его входе, поступающем с многоотводного делителя 2 частоты, изменяется на величину А (код установки накапливающего сумматора) и в каждый тактовый момент времени соответствует текущей фазе выходного сигнала и одновременно определяет адрес выборки кода амплитуды синусоиды из первого блока 7 памяти, где производится преобразование кода фазы в код амплитуды.

Код амплитуды с выхода первого блока 7 памяти через мультиплексор 10 поступает на входы цифроаналогового преобразователя 8, на выходе которого получается многоуровневое ступенчатое напряжение, из которого с помощью фильтра 9 нижних частот выделяется сигнал формируемой частоты.

При изменении А (при фиксированных значениях тактовой частоты и емкости накапливающего сумматора) изменяется количество выборок на одном периоде синусоиды и соответственно частота выходного сигнала.

Таким образом, первый блок 7 памяти выполняет функции кодового функционального преобразователя, в нем записаны коды значений амплитуд одного периода синусоиды.

Коды установок накапливающего сумматора 6 записаны во втором блоке 5 памяти, адресные входы которого подключены к выходам формирователя 4 кодовой последовательности, т. е. коды на выходе формирователя 4 кодовой последовательности являются адресами кодов установки накапливающего сумматора 6, записанных во втором блоке 5 памяти.

Первый и второй блоки памяти являются типовыми элементами, выполненными на стандартных аппаратно-программируемых микросхемах памяти 556РТ7.

Сигналы манипуляции по первому и второму входам поступают на шифратор 3, который формирует коды управления для формирователя 4 кодовой последовательности.

Сигналы частотной телеграфии формируются на выходе устройства при последовательном поступлении на вход накапливающего сумматора 6 двух значений кодов, соответствующих двум значениям характеристических частот.

Сигналы двойной частотной телеграфии формируются при поступлении на вход накапливающего сумматора 6 четырех значений кодов, соответствующих четырем значениям характеристических частот.

Коды установок накапливающего сумматора 6, образующие на выходе устройства сигналы характеристических и промежуточных частот, зашиваются во второй блок 5 памяти, выборка кода производиться по тем адресам, которые задаются формирователем 4 кодовой последовательности.

Для уменьшения уровня внеполосных составляющих спектра выходного сигнала организован плавный переход от одной характеристической частоты к другой.

В установившемся состоянии устройства, когда состояние входов манипуляции не изменяется и по входам манипуляции поступает любой из наборов сигналов "пауза" или "посылка", код на выходе формирователя 4 кодовой последовательности задает адрес ячейки второго блока 5 памяти, в которой записан код установки накапливающего сумматора 6, образующий на выходе устройства сигнал, частота которого равна характеристической частоте, для установленного набора сигналов манипуляции.

В момент смены знака сигнала манипуляции на одном или на двух входах устройства на выходах формирователя 4 кодовой последовательности начинает формироваться последовательность кодов, которые задают адреса второго блока 5 памяти, по которым записаны коды установки накапливающего сумматора 6, образующие на выходе устройства сигнал с промежуточными значениями частот, численные значения которых находятся в интервале между предыдущей характеристической частотой и той, которая установится при новом наборе сигналов манипуляции.

По окончании переходного процесса, длительность которого обычно составляет до 30% от длительности единичной посылки, формирование последовательности кодов на выходе формирователя 4 кодовой последовательности заканчивается и на этом выходе устанавливается код, который задает адрес ячейки второго блока 5 памяти, в которой записан код установки накапливающего сумматора 6, образующий на выходе устройства сигнал, частота которого равна характеристической частоте, для вновь установленного набора сигналов манипуляции.

Закон изменения частоты выходного сигнала при манипуляции влияет на уровень внеполосных спектральных составляющих и может быть любым, например синусным, линейным, параболическим.

Количество промежуточных значений частот за время переходного процесса определяет точность воспроизведения заданного закона.

Изменяя прошивку второго блока 5 памяти можно реализовать с достаточной точностью практически любой закон изменения частоты выходного сигнала при плавном переходе от одной характеристической частоты к другой.

Назначение формирователя 4 кодовой последовательности - за время плавного перехода от одной характеристической частоты к другой сформировать кодовую последовательность адресов обращения ко второму блоку 5 памяти.

Формирователь 4 кодовой последовательности предполагает любую аппаратную реализацию, выполняющую описанные выше функции, например может быть использована схема на база реверсивного счетчика, режимом работы которого управляют сигналы, поступающие с шифратора 3.

Шифратор 3 - логическая схема, формирующая коды управления, определяющие режимы работы формирователя 4 кодовой последовательности, например направление счета, начало и остановку счета. При изменении состояния одного из входов манипуляции код управления на выходе шифратора изменяется и в схеме устройства начинается процесс плавного перехода от одной характеристической частоты к другой.

В многочастотном режиме работы на выход мультиплексора 10 подключается сигнал с выхода сумматора 17.

Необходимый многочастотный сигнал представляет собой сумму узкополосных многократно разнесенных по частоте сигналов, несущих одну и ту же информацию.

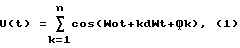

Рассмотрим аналитическое обоснование предлагаемого устройства для многочастотного сигнала без манипуляции:

где Wo - начальная несущая частота (частота любой из частотных составляющих многочастотного сигнала),

dW - интервал частотного разнесения многочастотного сигнала,

фk - начальная фаза каждой частотной составляющей многочастотного сигнала,

n - количество частотных составляющих многочастотного сигнала,

k - порядковый номер частотной составляющей.

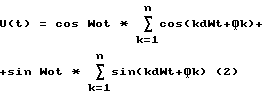

После преобразований формулы (1) выходной сигнал будет представлен в следующем виде:

Рассмотрим полученную формулу. Многочастотный сигнал образуется путем перемножения одночастотного представленного в цифровом виде сигнала на низкочастотную огибающую многочастотного сигнала.

Каждый конкретный многочастотный сигнал имеет заранее известные параметры:

- количество частотных составляющих - n;

- интервал частотного разнесения - dW;

- начальные фазы каждой из частотных составляющих - фk.

Начальные фазы частотных составляющих выбирают исходя из минимизации пикфактора выходного сигнала.

Учитывая известные заранее параметры (n, dW, фk) можно рассчитать синусную и косинусную составляющие огибающей многочастотного сигнала и записать их в блоки памяти.

Синусная и косинусная составляющие огибающей многочастотного сигнала считываются из БП5 13 и БП6 14 с тактовой частотой, поступающей на вход счетчика адреса 18.

Синусная и косинусная составляющие одночастотного сигнала считываются из БП3 11 и БП4 12 по адресу, определяемому выходом накапливающего сумматора 6.

Тактовая частота, управляющая работой накапливающего сумматора 6, совпадает с тактовой частотой работы счетчика адреса 18, выборки из блоков памяти БП5 13, БП6 14, БП3 11, БП4 12 производятся одновременно.

В результате перемножения на цифровых умножителях 15, 16 одночастотного сигнала и огибающей многочастотного сигнала и их суммирования на сумматоре 17 формируется цифровой многочастотный сигнал.

При поступлении сигналов манипуляции аналогично тому, как это происходит в одночастотном режиме, шифратор 3 формирует сигналы управления для формирователя 4 кодовой последовательности, которая, в свою очередь, формирует адреса обращения ко второму блоку 5 памяти, из которого выбираются коды установок накапливающего сумматора 6, код на выходе которого определяет адрес выборки из БП3 11 и БП4 12.

Преобразование цифрового сигнала в аналоговый производится так же, как и при формировании одночастотного сигнала.

На фиг.2 приведен спектр пятичастотного манипулированного сигнала.

При необходимости иметь в устройстве несколько различных многочастотных сигналов, отличающихся количеством частотных составляющих, интервалом частотного разнесения и начальными фазами, можно провести предложенные расчеты для каждого из многочастотных сигналов, записать их результаты в различные области памяти БП5 13 и БП6 14 и, подавая извне команды на включение (на схеме не показаны), подключать к умножителям соответствующие области памяти БП5 13 и БП6 14.

Таким образом, предлагаемое устройство позволяет формировать многочастотный сигнал, представляющий собой сумму узкополосных многократно разнесенных по частоте сигналов, несущих одну и ту же информацию.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИГНАЛОВ ДВУХЧАСТОТНОЙ И ЧЕТЫРЕХЧАСТОТНОЙ ТЕЛЕГРАФИИ | 1992 |

|

RU2065255C1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2212110C1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2233552C2 |

| СИНТЕЗАТОР ЧАСТОТ | 1997 |

|

RU2137287C1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| СИСТЕМА СВЯЗИ | 2003 |

|

RU2249914C2 |

| ДАТЧИК КОНТРОЛЬНЫХ СИГНАЛОВ | 1997 |

|

RU2131643C1 |

| СИНТЕЗАТОР ЧАСТОТ | 1995 |

|

RU2119238C1 |

| ВОЗБУДИТЕЛЬ РАДИОПРИЕМНИКА | 1990 |

|

RU2119250C1 |

| УСТРОЙСТВО СЛОЖЕНИЯ РАЗНЕСЕННЫХ СИГНАЛОВ | 1990 |

|

RU2031543C1 |

Изобретение относится к радиотехнике и может использоваться а передающей аппаратуре телеграфной связи. Техническим результатом является обеспечение формирования многочастотного сигнала двухчастотной и четырехчастотной телеграфии. Для достижения технического результата в устройство для формирования сигналов двухчастотной и четырехчастотной телеграфии введены мультиплексор, на управляющий вход которого поступает внешняя команда, последовательно соединенные третий блок памяти и первый умножитель, последовательно соединенные четвертый блок памяти и второй умножитель, сумматор, входы которого подключены к выходам умножителей, счетчик адреса, пятый и шестой блоки памяти, входы которых подключены к выходу счетчика адреса, а выходы подключены ко вторым входам умножителей, при этом входы третьего и четвертого блоков памяти подключены к выходу накапливающего сумматора, выходы сумматора и первого блока памяти подключены на первый и второй входы мультиплексора соответственно, выход мультиплексора подключен ко входу цифроаналогового преобразователя, причем тактовый вход счетчика адреса подключен к выходу многоотводного делителя частоты. 2 ил.

Устройство для формирования сигналов двухчастотной и четырехчастотной телеграфии, содержащее последовательно соединенные опорный генератор и многоотводный делитель частоты, последовательно соединенные шифратор, формирователь кодовой последовательности, второй блок памяти, накапливающий сумматор и первый блок памяти, последовательно соединенные цифроаналоговый преобразователь и фильтр нижних частот, при этом тактовые входы накапливающего сумматора и формирователя кодовой последовательности подключены к выходам многоотводного делителя частоты, отличающееся тем, что в него введены мультиплексор, на управляющий вход которого поступает внешняя команда, последовательно соединенные третий блок памяти и первый умножитель, последовательно соединенные четвертый блок памяти и второй умножитель, сумматор, входы которого подключены к выходам умножителей, счетчик адреса, пятый и шестой блоки памяти, входы которых подключены к выходу счетчика адреса, а выходы подключены ко вторым входам умножителей, при этом входы третьего и четвертого блоков памяти подключены к выходу накапливающего сумматора, выходы сумматора и первого блока памяти подключены на первый и второй входы мультиплексора соответственно, выход мультиплексора подключен ко входу цифроаналогового преобразователя, причем тактовый вход счетчика адреса подключен к выходу многоотводного делителя частоты.

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИГНАЛОВ ДВУХЧАСТОТНОЙ И ЧЕТЫРЕХЧАСТОТНОЙ ТЕЛЕГРАФИИ | 1992 |

|

RU2065255C1 |

| Устройство формирования многочастотного сигнала | 1980 |

|

SU1084939A1 |

| US 3890581 A, 17.06.75 | |||

| Способ электродуговой сварки | 1976 |

|

SU584996A1 |

Авторы

Даты

1999-09-10—Публикация

1997-12-16—Подача