Изобретение относится к радиотехнике и может использоваться в радиопередающих и радиоприемных устройствах. Известен синтезатор частот, содержащий опорный генератор, накопительный сумматор, элемент задержки, мультиплексор, два сумматора кодов, три регистра частоты, перемножитель кодов, преобразователь кодов, цифроаналоговый преобразователь, фильтр нижних частот [1].

Данный синтезатор слишком сложен и не обеспечивает достаточную точность частоты выходного сигнала.

Известны синтезаторы частот, в которых для повышения точности используются различные схемные решения [2].

Используемые для повышения точности схемные решения либо сложны, например, схема десятичного сумматора, где за счет последовательного соединения двоичных сумматоров снижается быстродействие схемы, либо вообще не могут обеспечить точность не хуже точности опорного генератора.

Известен цифровой синтезатор частот, содержащий генератор тактовых импульсов, делитель частоты, блок формирования кода частоты, формирователь управляющего кода, два накопителя фазы, умножитель кодов, блок суммирования, распределитель импульсов, три регистра памяти, блок постоянной памяти, коммутатор, ЦАП и фильтр нижних частот [3].

Данный синтезатор не позволяет получать точное значение частоты выходного сигнала.

Известен синтезатор сигналов с заданным законом изменения фазы, содержащий два делителя частоты, блок формирования кодов фазы и частоты, N-1 комбинационных сумматора, N преобразователей кода, N дополнительных регистров памяти, элемент задержки, коммутатор, регистр памяти, ЦАП, фильтр нижних частот, блок формирования кодов фазы, синхронизатор, опорный генератор [4].

Данный синтезатор не обеспечивает достаточную точность частоты выходного сигнала.

Задача изобретения - упрощение устройства и повышение точности частоты выходного сигнала.

Для этого в синтезатор частот, содержащий последовательно соединенные первый регистр и умножитель, последовательно соединенные опорный генератор и блок синхронизации, первый мультиплексор, блок памяти, последовательно соединенные второй регистр, цифроаналоговый преобразователь и фильтр нижних частот, введены N вторых мультиплексоров, N первых сумматоров, N вторых сумматоров и N третьих регистров, причем первые входы N первых сумматоров соединены с соответствующими выходами умножителя, вторые входы N первых сумматоров соединены между собой и с выходом N-го третьего регистра, выход каждого из N первых сумматоров подключен к первому входу соответствующего второго сумматора, выход переноса каждого из N первых сумматоров соединен с управляющим входом соответствующего второго мультиплексора, выходы N вторых мультиплексоров соединены с вторыми входами соответствующих вторых сумматоров, выход каждого из которых подключен к входу соответствующего третьего регистра, выход каждого из N третьих регистров соединен с соответствующим входом первого мультиплексора, выход первого мультиплексора соединен с входом блока памяти, выход блока памяти соединен с входом второго регистра, выходы блока синхронизации соединены с тактовыми входами N третьих регистров, управляющими входами первого мультиплексора и с тактовым входом второго регистра, при этом первые входы N вторых мультиплексоров соединены между собой и являются входом сигнала "логический 0", вторые входы N вторых мультиплексоров соединены между собой и являются входом, на который подается добавочный код.

Предлагаемое техническое решение соответствует критерию изобретения "новизна", т. к. отличается от прототипа наличием новых функциональных элементов и новых связей между элементами.

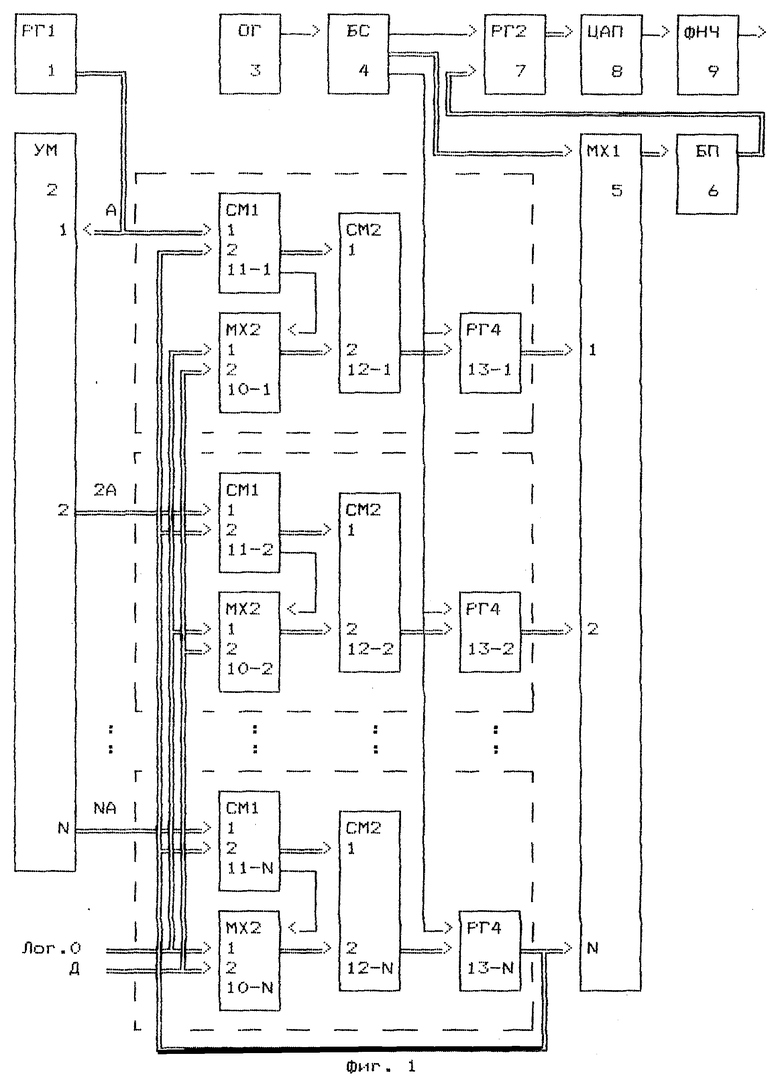

На фиг. 1 изображена структурная электрическая схема предлагаемого устройства, на фиг. 2 - временные диаграммы работы устройства.

Синтезатор содержит последовательно соединенные первый регистр 3(РГ1) и умножитель 2 (УМ), последовательно соединенные опорный генератор 1 (ОГ), блок 4 синхронизации (БС), первый мультиплексор 5 (МХ1), блок 6 памяти (БП), второй регистр 7 (РГ2), цифроаналоговый преобразователь 8 (ЦАП) и фильтр 9 нижних частот (ФНЧ), N вторых мультиплексоров 10-1, 10-2,...10-N (МХ2), N первых сумматоров 11-1, 11-2,...11-N (СМ1), N вторых сумматоров 12-1, 12-2,. . . 12-N (СМ2) и N третьих регистров 13-1, 13-2,...13-N (РГ3), причем первые входы N первых сумматоров соединены с соответствующими выходами умножителя, вторые входы N первых сумматоров соединены между собой и с выходом N-го третьего регистра, выход каждого из N первых сумматоров подключен к первому входу соответствующего второго сумматора, выход переноса каждого из N первых сумматоров соединен с управляющим входом соответствующего второго мультиплексора, выходы N вторых мультиплексоров соединены со вторыми входами соответствующих вторых сумматоров, выход каждого из которых подключен к входу соответствующего третьего регистра, выход каждого из N третьих регистров соединен с соответствующим входом первого мультиплексора, выход первого мультиплексора соединен с входом блока памяти, выход блока памяти соединен с входом второго регистра, выходы блока синхронизации соединены с тактовыми входами N третьих регистров, управляющими входами первого мультиплексора и с тактовым входом второго регистра, при этом первые входы N вторых мультиплексоров соединены между собой и являются входом сигнала "логический 0", вторые входы N вторых мультиплексоров соединены между собой и являются входом, на который подается добавочный код.

Устройство работает следующим образом.

Как известно, в прямых цифровых синтезаторах частоты формирование сигнала заданной частоты осуществляется путем вычисления в тактовые моменты времени кода линейно нарастающей фазы, преобразования кода фазы в код амплитуды синусоидального колебания, цифроаналогового преобразования и низкочастотной фильтрации.

Выходная частота прямого цифрового синтезатора равна

где Fо - частота опорного сигнала,

A - код частоты,

P - коэффициент деления (определяется емкостью сумматора).

Для пояснения работы устройства представим схему устройства, состоящую из параллельных трактов суммирования - N блоков формирования суммы (БФС), каждый из которых состоит из второго мультиплексора 10-1, 10-2,...10-N и последовательно соединенных первого сумматора 11-1, 11-2,...11-N, второго сумматора 12-1, 12-2, ...12-N и третьего регистра 13-1, 13-2,...13-N.

На вторые входы первых сумматоров 11-1, 11-2,...11-N всех N БФС поступает код с выхода третьего регистра 13-N N-го БФС, а на первые входы первых сумматоров 11-1, 11-2,...11-N всех N БФС с умножителя 2 поступают коды, кратные коду A (A, 2A, 3A,...). В каждом из БФС емкость первого сумматора 11-1, 11-2,...11-N равна P - коэффициенту деления. N-ый БФС, код с выхода третьего регистра 13-N которого поступает непосредственно на вторые входы первых сумматоров 11-1, 11-2,...11-N всех N БФС, выполняет функцию накапливающего сумматора, работающего с шагом NA.

Суммирование происходит одновременно на всех БФС, отличаются они лишь кодом, поступающим с умножителя 2 на первые входы первых сумматоров 11-1, 11-2,...11- N. По окончании процесса суммирования производится одновременная запись в третьи регистры 13-1, 13-2,... 13-N всех N БФС кодов, которые являются промежуточными между NA отсчетами кода фазы и составляют в сумме последовательный набор текущих фаз выходного сигнала устройства, а код, записанный в третий регистр 13-N N-го БФС, кроме того и исходным кодом для следующего цикла суммирования.

Вернемся к формуле (1).

Выходная частота стандартных высокостабильных генераторов, как правило, кратна 1 МГц, емкость сумматора равна степени числа 2.

При некратности чисел в числителе и знаменателе дроби реальное значение частоты на выходе устройства, получаемое делением этих чисел, не точно соответствует требуемому значению частоты, т.к. результат деления - число не целое.

Представим емкость накапливающего сумматора как сумму двух чисел - одно из них кратно коду требуемой частоты А, а другое дополняет это число до значения, являющегося степенью числа 2:

N = К • А + Д, (2)

где К - целое число,

Д - добавочный код.

Для получения значения выходной частоты с точностью опорного генератора предлагается корректировать емкости сумматоров.

В каждом из N БФС при отсутствии сигнала переноса на выходе первого сумматора 11-1, 11-2,...11-N на второй вход соответствующего второго сумматора 12-1, 12-2,..,12-N через соответствующий второй мультиплексор 10-1, 10-2,... 10-N поступает сигнал "логический 0" и код с выхода соответствующего второго сумматора 12-1, 12-2, . . .12-N проходит на соответствующий третий регистр 13-1, 13-2,...13-N.

При переполнении любого из первых сумматоров 11-1, 11-2,...11-N, которое может произойти после проведения очередной записи кода в третьи регистры 13-1, 13-2,...13-N и, как следствие, смене кода на вторых входах первых сумматоров 11-1, 11-2,...11-N, на выходе переноса соответствующего первого сумматора 11-1, 11-2,...11-N появляется сигнал, которым управляя соответствующим вторым мультиплексором 10-1, 10-2,...10-N подключает на второй вход соответствующего второго сумматора 12-1, 12-2,...12-N добавочный код Д, и на вход соответствующего третьего регистра 13-1, 13-2,...13-N для новой записи поступает код равный сумме остатка на выходе каждого из переполненных первых сумматоров 11-1, 11-2,...11-N из очередного цикла и добавочного кода Д. По окончании процесса суммирования полученное значение суммы записывается в соответствующий третий регистр 13-1, 13-2,...13-N, сигнал переноса на выходе переноса каждого из переполненных первых сумматоров 11-1, 11-2,...11-N пропадает и соответствующий второй мультиплексор 10-1, 10-2,...10-N вновь подключает на второй вход соответствующего второго сумматора 12-1, 12-2,...12-N сигнал "логический 0". Сигналы переполнения первых сумматоров 11-1, 11-2,... 11-N в каждом из ФКС формируются независимо друг от друга.

Общее необходимое количество параллельно включенных ФКС определяется собственным быстродействием каждого из них.

В умножителе 2 формируются коды чисел кратных А. Коды этих чисел формируются на основе типовых схем умножения или же с использованием дополнительных сумматоров. Так коды 2А, 4А, 8А,... получаются простым сдвигом исходного кода А на 1, 2, 3,... разряда, а коды ЗА, 5А, 6А,... получают суммированием (2А + А), (4А + А), (4А + 2А),... на нескольких дополнительных сумматорах (могут входить в состав схемы умножителя, на чертеже не показаны).

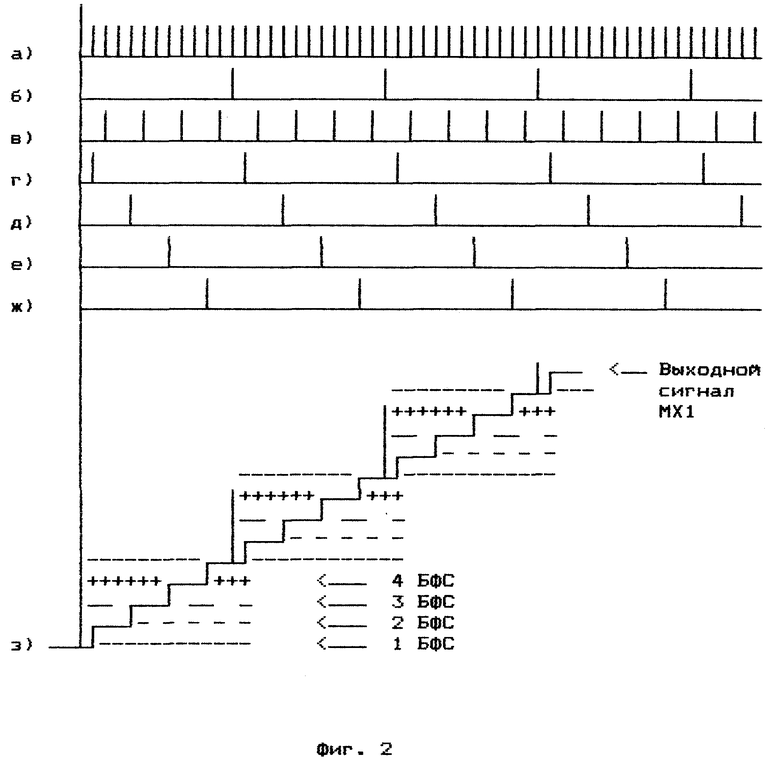

Блок 4 синхронизации, на вход которого подается сигнал опорного генератора 3, вырабатывает тактовые сигналы для записи во второй регистр 7 и N третьих регистров 13-1, 13-2,...13-N, а также управляющие сигналы для первого мультиплексора 5, обеспечивая при этом высокую точность вырабатываемых сигналов (не хуже точности опорного генератора). Выходные сигналы блока 4 синхронизации приведены на фиг. 2б - фиг. 2ж, на фиг. 2а - входные сигналы, поступающие с опорного генератора 3. Сигналы, приведенные на фиг. 2б, используются для записи кодов в N третьих регистров 13-1, 13-2,...13-N всех N ФКС, сдвинутые по времени относительно них и распределенные по количеству ФКС сигналы поступают на управляющим вход первого мультиплексора 5 (фиг. 2г - фиг. 2ж), сдвинутые относительно управляющих сигналов первого мультиплексора 5 сигналы поступают на тактовый вход второго регистра 7 (фиг. 2в). На фиг. 2з показаны значения кодов отсчетов синусоидальной функции для случая N = 4, приведенные к аналоговому виду.

Сформированные значения кодов с выхода первого мультиплексора 5 подаются непосредственно на блок 6 памяти, выполненный на программируемом постоянном запоминающем устройстве (ПЗУ), и определяют адрес выборки кода амплитуды синусоиды из блока 6 памяти. В ПЗУ записан период синусоиды, с количеством выборок равным емкости сумматора (Р-Д). Оставшаяся часть ПЗУ не программируется и не используется. При этом каждому коду на выходе первого мультиплексора 5 соответствует точное значение огибающей синусоиды.

Код амплитуды поступает на входы цифроаналогового преобразователя 8, на выходе которого получается многоуровневое ступенчатое напряжение, из которого с помощью фильтра 9 нижних частот выделяется сигнал формируемой частоты.

Сравним предложенное устройство с известными.

В известном устройстве [1] используется корректировка емкости накапливающего сумматора путем введения добавочного кода, но в результате дальнейших преобразований появляется погрешность, приводящая к неточности выходного сигнала.

Обоснуем сказанное.

Рассмотрим часть схемы известного устройства [1] (сумматор 8, регистр 9, умножитель 10, преобразователь 11 кодов, ЦАП 12 и ФНЧ 13). Преобразование кодов, сформированных на выходе накапливающего сумматора 2, в коды многоуровневого ступенчатого напряжения осуществляется после дополнительного вычитания (сумматор 8) и умножения (умножитель 10) на дополнительное число L, что объясняется тем, что в преобразователе 11 кодов записаны значения кодов для каждого из Р = 2n значений синусоиды, а на выходе накапливающего сумматора 2 появляются коды, представляющие собой долю периода синусоиды, описанную значением (P-B).

Величина L = Р/(Р-В) (в описании известного устройства [1] в этой формуле допущена опечатка) - это масштабный коэффициент и в общем случае не целое число. Но код на выходе накапливающего сумматора 2 это целое число, адрес выборки преобразователя 11 кодов тоже целое число, поэтому в каждом случае результат умножения необходимо округлить до целого числа, отбросив дробную часть, что неизбежно приведет к погрешности в выборе мгновенных значений амплитуды выходного сигнала, а следовательно к ухудшению спектральных характеристик выходного сигнала, к снижению его точности.

Поясним вышесказанное конкретным примером.

Допустим, необходимо разработать синтезатор частот с шагом сетки частот 5 Гц, частота опорного генератора 1,25 МГц, точность частоты выходного сигнала должна быть не хуже точности опорного генератора. Максимально необходимая емкость накапливающего сумматора определяется при A = 1, fвых. = 5 Гц и будет равна 1250000/5=250000. Ближайшее большее число, являющееся степенью числа 2, это 262144 = 218, т.е. для реализации поставленных условий необходим восемнадцатиразрядный накапливающий сумматор. Добавочный код B равен 262144-250000=12144. Теперь для известного устройства [1] определим значение числа L = 262144/(262144-250000)=1,048576. Предложенный расчет подтвердил неточность процедуры умножения в известном устройстве [1].

Рассмотрим известные устройства [3] и [4]. Схемы названных устройств достаточно похожи - в них используется две группы сумматоров - накапливающий сумматор для формирования кода частоты, комбинационный сумматор для формирования промежуточных отсчетов кода фазы.

Некратное в общем виде соотношение частоты опорного генератора и емкостей сумматоров не позволяет получать точное значение частоты. Если для повышения точности выходного сигнала ввести ограничение емкости, то делать это нужно для обоих групп сумматоров, что в известных устройствах не предусмотрено.

Кроме того, предложенное в известном устройстве [3] умножение исходного кода частоты на n возможно лишь в случае, если соотношение Fвых и Fо достаточно велико и результат умножения остается заведомо меньше емкости накапливающего сумматора.

Преимущество предлагаемого устройства по сравнению с известным состоит в том, что за счет коррекции емкости сумматоров в каждом цикле его работы точность выходной частоты синтезатора частот даже при некратных значениях емкости сумматора и частоты опорного сигнала определяется точностью частоты опорного генератора, а предложенная схема сумматоров позволяет получать предельное быстродействие схемы более простым способом.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНТЕЗАТОР ЧАСТОТ | 1995 |

|

RU2119238C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИГНАЛОВ ДВУХЧАСТОТНОЙ И ЧЕТЫРЕХЧАСТОТНОЙ ТЕЛЕГРАФИИ | 1997 |

|

RU2137313C1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2212110C1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2233552C2 |

| ВОЗБУДИТЕЛЬ РАДИОПРИЕМНИКА | 1990 |

|

RU2119250C1 |

| ДАТЧИК КОНТРОЛЬНЫХ СИГНАЛОВ | 1997 |

|

RU2131643C1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1992 |

|

RU2041563C1 |

| УСТРОЙСТВО СЛОЖЕНИЯ РАЗНЕСЕННЫХ СИГНАЛОВ | 1990 |

|

RU2031543C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИГНАЛОВ ДВУХЧАСТОТНОЙ И ЧЕТЫРЕХЧАСТОТНОЙ ТЕЛЕГРАФИИ | 1992 |

|

RU2065255C1 |

Изобретение относится к радиотехнике и может использоваться в радиопередающих и радиоприемных устройствах. Задача изобретения - упрощение устройства и повышение точности частоты выходного сигнала. Синтезатор частот содержит последовательно соединенные первый регистр и умножитель, последовательно соединенные опорный генератор и блок синхронизации, первый мультиплексор, блок памяти, последовательно соединенные второй регистр, цифроаналоговый преобразователь и фильтр нижних частот, N вторых мультиплексоров, N первых сумматоров, N вторых сумматоров и N третьих регистров. За счет коррекции емкости сумматоров в каждом цикле его работы точность выходной частоты синтезатора частот даже при некратных значениях емкости сумматора и частоты опорного сигнала определяется точностью частоты опорного генератора. 2 ил.

Синтезатор частот, содержащий последовательно соединенные первый регистр и умножитель, последовательно соединенные опорный генератор и блок синхронизации, первый мультиплексор, блок памяти, последовательно соединенные второй регистр, цифроаналоговый преобразователь и фильтр нижних частот, отличающийся тем, что в него введены N вторых мультиплексоров, N первых сумматоров, N вторых сумматоров и N третьих регистров, причем первые входы N первых сумматоров соединены с соответствующими выходами умножителя, вторые входы N первых сумматоров соединены между собой и с выходом N-го третьего регистра, выход каждого из N первых сумматоров подключен к первому входу соответствующего второго сумматора, выход переноса каждого из N первых сумматоров соединен с управляющим входом соответствующего второго мультиплексора, выходы N вторых мультиплексоров соединены с вторыми входами соответствующих вторых сумматоров, выход каждого из которых подключен к входу соответствующего третьего регистра, выход каждого из N третьих регистров соединен с соответствующим входом первого мультиплексора, выход первого мультиплексора соединен с входом блока памяти, выход блока памяти соединен с входом второго регистра, соответствующие выходы блока синхронизации соединены с тактовыми входами N третьих регистров, управляющими входами первого мультиплексора и с тактовым входом второго регистра, при этом первые входы N вторых мультиплексоров соединены между собой и являются входом сигнала "логический 0", вторые входы вторых мультиплексоров соединены между собой и являются входом, на который подается добавочный код.

| Цифровой синтезатор частот | 1988 |

|

SU1589366A1 |

| Синтезатор сигналов с заданным законом изменения фазы | 1989 |

|

SU1686693A1 |

| Цифровой синтезатор частот | 1989 |

|

SU1635244A2 |

Авторы

Даты

1999-09-10—Публикация

1997-12-16—Подача