1. Область техники

Изобретение относится к электронным системам коммутации, использующим многопроцессорные устройства, и, в частности, к способу проверки состояния процессора.

2. Уровень техники

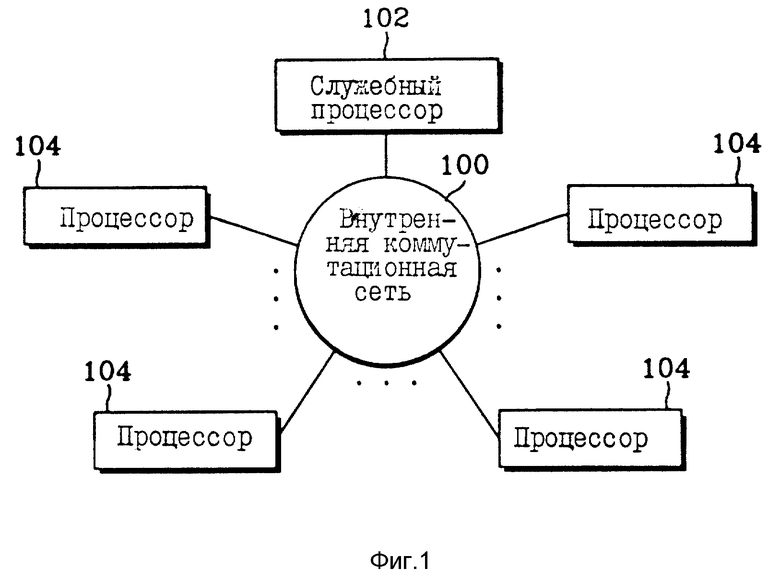

На фиг. 1 показана общая структура системы коммутации, которая является разновидностью многопроцессорной системы, где служебный процессор 102 периодически опрашивает состояние каждого из единичных процессоров 104 посредством внутренней сети коммутации 100, либо принимает информацию об аппаратно изменяемом состоянии для управления состоянием процессоров. Управление состоянием процессоров подразумевает выполнение полного набора функций, связанных с обслуживанием сбоев процессоров, включая нарушение функции программного обеспечения и сбои таких аппаратных элементов, как системная плата или соединительные провода и т.д. Информация о состоянии процессора хранится в виде базы данных ДВ, а таблица состояний, содержащая путевую информацию для эффективной передачи управляющих сигналов между процессорами, корректируется с использованием информации реального масштаба времени. Информация реального масштаба времени, передаваемая между процессорами, содержит текущее состояние процессоров, и, таким образом, идентичность информации должна обеспечиваться во всех процессорах системы.

В обычном способе управления состоянием процессора, как описано выше, для обнаружения сбоев процессора, исключая такие аппаратно обнаруживаемые сбои, как обрывы на плате, короткие замыкания проводов и т.д., служебный процессор должен периодически выполнять операции приема/передачи сообщений для проверки состояния всех процессоров в системе, которые относятся к высоким классам в двухуровневой системе. Сбой процессора, как было отмечено выше, воспринимается служебным процессором в виде постоянной нагрузки, что может приводить к ошибкам в периоды максимальной нагрузки. Далее, связываясь со всеми процессорами, служебный процессор вынужден физически занимать дальний путь во внутренней коммутационной сети, что приводит к ухудшению эффективности внутренней сети при передаче сообщений. Кроме того, в том случае, если сбои одновременно возникают во множестве процессоров, несколько запросов на изменение содержимого таблицы состояния процессоров одновременно принимаются служебным процессором, причем задания на изменение содержимого таблицы выполняются сразу же при получении запросов, вследствие чего возникают "зависания" служебного модуля, обусловленные чрезмерной перегрузкой. "Зависания" служебного процессора являются опасными сбоями, приводящими к прекращению доступа исполнителя к системе, либо нарушению таких функций, как восстановление потерянной информации, загрузка системы и т.п.

Краткое изложение существа изобретения

Целью настоящего изобретения является разработка способа распределенной обработки для проверки состояния процессора, который обеспечивает снижение нагрузки служебного процессора посредством единичных процессоров, состояние которых проверяется.

Другой целью изобретения является разработка способа распределенной обработки, обеспечивающего проверку состояния процессора без использования отдельных аппаратных средств.

Еще одной целью настоящего изобретения является разработка способа распределенной обработки для проверки состояния процессора, предотвращающего сбой служебного процессора при его перегрузке, вызванной одновременным поступлением в служебный процессор нескольких запросов на изменение состояния множества процессоров, одновременно вышедших из строя.

Для достижения этих и других целей в настоящем изобретении сканирующие задания для проверки состояния процессоров, выполняемые служебным процессором, распределяются и разграничиваются по областям действия так, чтобы выполнять взаимные проверки состояния единичных процессоров путем соединения всех процессоров системы в последовательную структуру в виде связанного списка. Состояние контролируемого процессора доводится до служебного процессора только в том случае, когда процессор имеет состояние сбоя, благодаря чему нагрузка служебного процессора сокращается. Кроме того, в случае одновременного выхода из строя множества процессоров и, как следствие, одновременного поступления в служебный процессор нескольких запросов на изменение их состояния, служебный процессор обрабатывает запросы в отведенные интервалы времени, а не все одновременно.

Краткое описание чертежей

В дальнейшем изобретение поясняется описанием конкретного варианта его воплощения со ссылками на сопровождающие чертежи, на которых:

фиг. 1 - изображает систему коммутации согласно изобретению,

фиг. 2 - изображает диаграмму распределенной обработки для проверки состояния процессора согласно изобретению,

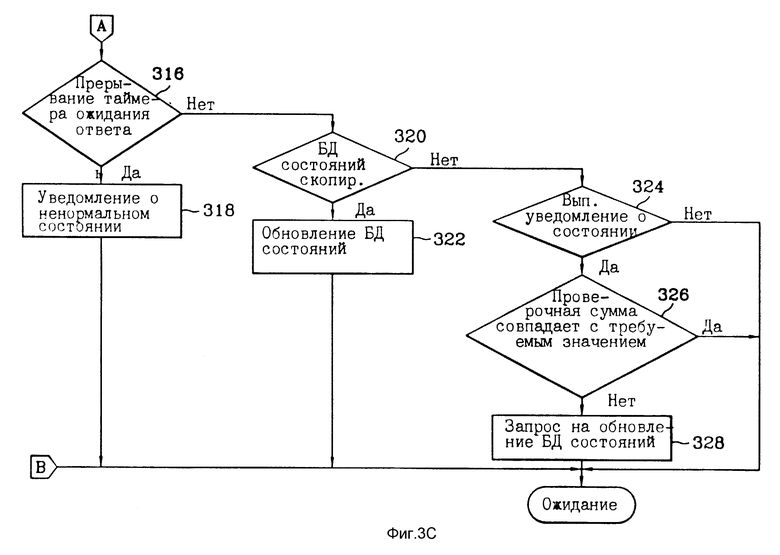

фиг. 3а, 3в, 3с - изображает блок-схему проверки состояния единичного процессора согласно изобретению,

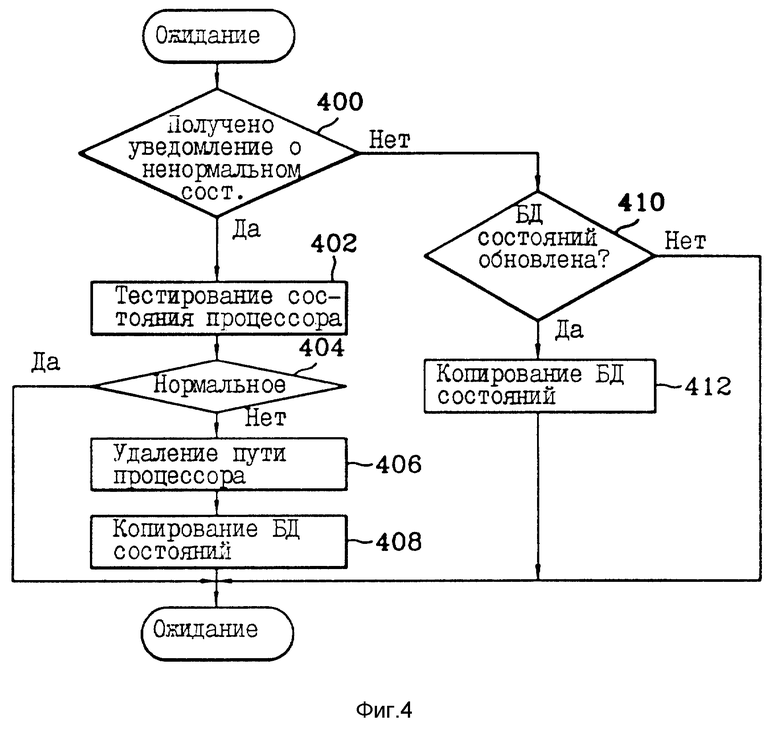

фиг. 4 - изображает блок-схему операции контроля состояния процессоров, выполняемых служебным процессором согласно изобретению.

Описание предпочтительного варианта воплощения

Специалистам в данной области техники понятна возможность применения на практике других вариантов воплощения настоящего изобретения без специфических деталей, или с другими специфическими деталями. В дальнейшем детальные описания функций и структуры, затрудняющие понимание сути изобретения, не пригодятся.

Первоначально для проверки состояния процессора с использованием способа распределенной обработки в виде соответствующей базы данных (БД) создается идентификационная таблица (1Д - таблица), в которой всем перечисленным процессорам, входящим в одно устройство, присваиваются идентификационные номера 1Д. Эта 1Д-таблица обязательно создается в системе и может быть реализована различными способами.

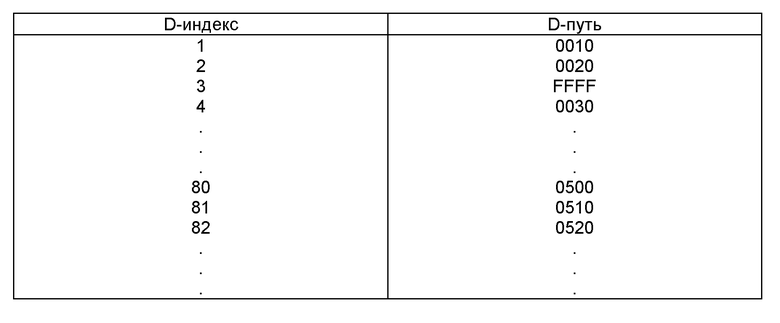

Далее создается Таблица путей процессоров, которая управляется с использованием информации реального масштаба времени, в виде таблицы, структура которой такова, что логические идентификаторы процессоров проиндексированы, а затем пути процессоров поставлены в соответствие индексированным идентификаторам.

В приведенной выше таблице, построенной в предположении, что все процессоры системы находятся в нормальном состоянии, "Д-индекс", как индекс, который непосредственно определяется идентификатором процессора, не имеет физического положения, а "Д-пути", как величины собственных путей, представляющих текущее состояние путей процессоров, используется в качестве указателей для индикации физического адреса реального процессора. Соответственно, состоянием процессора можно управлять регулированием величины Д-пути. В случае, когда подключенный процессор функционирует нормально, Д-путь имеет специфическую величину, а если процессор демонтирован или функционирует ненормально, Д-путь имеет "холостое" значение "FFFFH", означающее неисправность этого процессора. Представленная Таблица пути аналогично управляется для всех процессоров, опрашиваемых служебным процессором, являющимся главным процессором, и соответственно используется при проверке состояния, которая проводится единичным процессором для примыкающего к нему процессора. При проверке состояния процессора не требуется использования всей Таблицы пути и поэтому для проверки идентичности информации используется способ взаимного сравнения вычисленных значений проверочных сумм для Д-путей. В настоящем изобретении Таблица пути процессоров используется в качестве исходной таблицы для проверки состояния процессоров с использованием прилегающих к ним процессоров, передающих сообщения друг другу, причем идентичность информации между процессорами обеспечивается за счет проверки Таблицы пути процессоров каждый раз при периодическом проведении операций по проверке состояния процессоров.

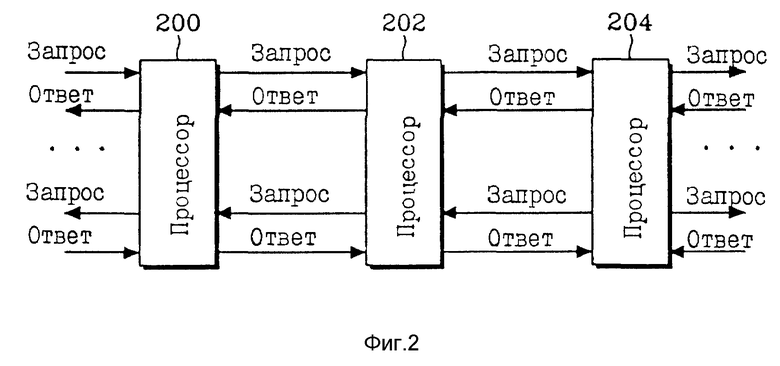

На фиг. 2 показана принципиальная схема, иллюстрирующая способ распределенной обработки для проверки состояния всех процессоров, функционирующих в системе в виде единичных объектов. Все процессоры в системе коммутации логически соединены так, чтобы образовать последовательную структуру. В процессорах 200, 202 и 204, которые являются соседними процессорами в Таблице пути процессоров (табл. 1), состояние процессора 202 проверяется процессорами 200 и 204, а состояния процессоров 200 и 204 проверяются предшествующим и последующим процессорами, соединенными в структуру с двумя линиями, включающую процессор 202. В данном способе распределенной обработки процессоры 200 и 202 взаимно проверяют состояние друг друга путем выполнения основной операции, в которой периодически повторяются задания на запрос значения контрольной суммы пути соседнего процессора и которая выполняется одинаковым образом для взаимно соединенных процессоров.

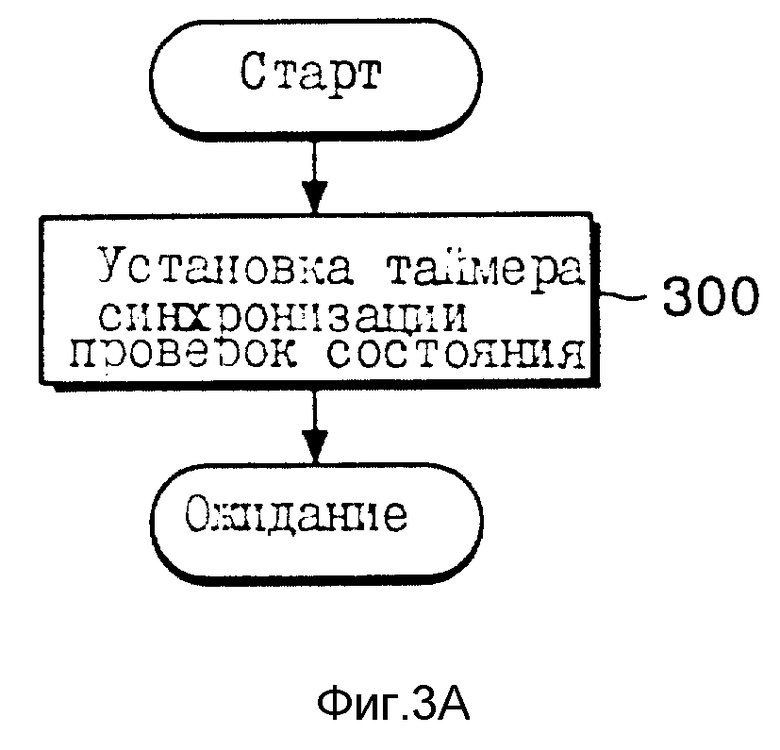

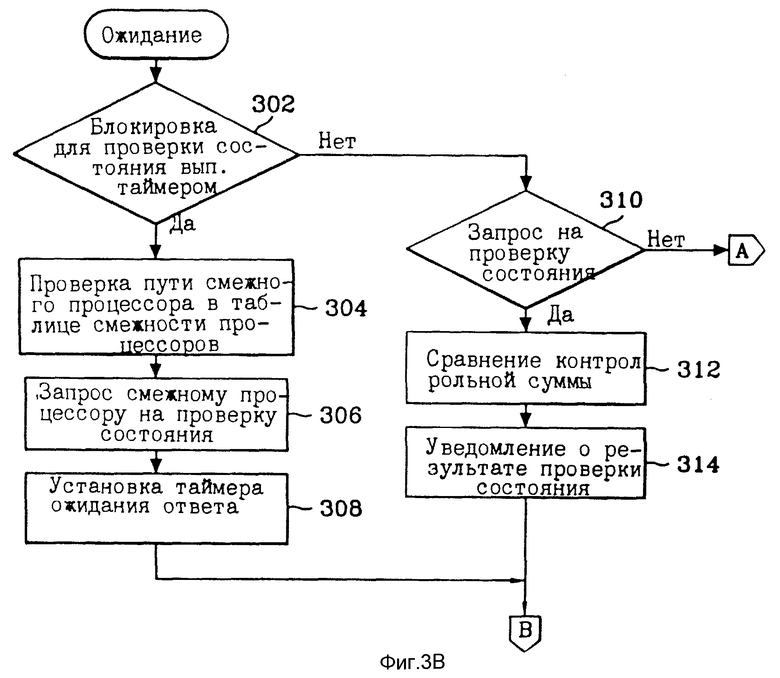

Блок-схемы на фиг. 3а и 3в, с иллюстрируют операции по проверке состояния единичного процессора в соответствии с изобретением. Такие проверочные операции выполняются одинаковым образом во всех единичных процессорах 104, показанных на фиг. 1. На шаге 300 каждый из процессоров 104 после установки синхронизирующего таймера ожидает операции проверки состояния. После того, как синхронизирующий таймер выполняет блокировку для проверки состояния процессора, соответствующий процессор отыскивает смежный с ним процессор в Таблице пути (табл. 1) и затем посылает запрос на проверку контрольной суммы этого смежного процессора в соответствии с Таблицей пути, после чего устанавливает таймер ожидания ответа (шаги 302-308). В это время, если ответ получен от смежного процессора на протяжении отведенного промежутка времени, соответствующий процессор сравнивает значение полученной контрольной суммы с ее собственным значением, и если значение полученной контрольной суммы не совпадает со своим собственным значением, то запрашивается копия эталонной Таблицы пути процессоров в служебный процессор 102 (шаги 324-328). В противном случае, если вышеупомянутый смежный процессор находится в нормальном состоянии, взаимная проверка на основе обмена сообщениями продолжается. Если ответ не получен в отведенный промежуток времени, соответствующий процессор принимает решение о том, что смежный ему процессор находится в ненормальном состоянии и уведомляет об этом ненормальном состоянии служебный процессор 102, выполняя, таким образом, проверку состояния смежного процессора (шаги 316-318). Так как процессоры объединены в структуру с использованием двойных соединительных линий, то при выявлении двух сбойных процессоров с идентичными неисправностями, служебный процессор принимает запрос от процессора с низшим логическим идентификатором, вследствие чего удается избежать избыточной работы. Кроме того, в случае поступления в служебный процессор сообщения о ненормальном состоянии, выполняется тест на проверку состояния процессора, и если сбойное состояние процессора подтверждено, эталонная Таблица пути процессоров изменяется и затем копируется для всех процессоров.

На фиг. 4 показана блок-схема операции по контролю состояния процессора, выполняемых служебным процессором в соответствии с изобретением, которые используются при описании процесса выполнения теста на проверку состояния процессора и при описании процедуры копирования эталонной Таблицы пути процессоров. При обнаружении сбоя служебный процессор 102 выполняет тест на проверку состояния соответствующего процессора, в результате чего подтверждается или опровергается нормальное состояние этого процессора (шаги 400-404). В результате выполненного теста, если проверенный процессор находится в состоянии сбоя, соответствующий процессор помечается как нерабочий (FFFFH) в Таблице пути (табл. 1), а затем база данных состояний процессоров копируется во все процессоры 104. С этого момента неисправный процессор удаляется из списка контролируемых процессоров и для этого процессора операции проверки больше не выполняются. Однако, так как служебный процессор управляет загрузкой, если сбой устранен и соответствующий процессор возвращен в рабочее состояние, то при этом, если прошло уведомление об обновлении базы данных состояний, служебный процессор 102 заново помещает соответствующий процессор в Таблицу пути процессоров (табл. 1) и копирует базу данных состояний для доведения ее до всех процессоров 104 (шаги 410-412).

Однако в случае использования способа, описанного в настоящем изобретении, так же, как и обычных способах, если возникают сбои во множестве процессоров, то несколько запросов одновременно поступают в служебный процессор. Следовательно, каждый раз при возникновении описанного случая, если Таблица пути процессоров изменяется, то перегрузка, вызванная обновлением базы данных, не может быть обработана. Соответственно, для разрешения этой проблемы задание может быть выполнено после периода блокировки, установленного таймером в соответствии со временем копирования данных, так, что следующее задание может быть принято в заданный временной интервал каждый раз при обработке одного запроса. Упомянутый временной интервал устанавливается с учетом реальных размеров обновляемой базы данных путем посылки и загрузки транслируемого сообщения. Несмотря на то, что задание выполняется в заданные интервалы времени, если Таблица пути процессоров не изменена, то запрос на изменение таблицы продолжается и, соответственно, пропусков в выполнении задания не возникает.

Выше показано, что в настоящем изобретении обеспечиваются взаимные проверки процессорами состояний друг друга, соответствующие функции могут быть распределены и разнесены по областям действия. Соответственно понижается загрузка служебного процессора, имеющего центральную управляющую структуру. Кроме того, состояние процессора может быть проверено только с использованием программных средств, не прибегая к различному аппаратному оборудованию. В дополнение, одновременно поступающие запросы на изменение состояние обрабатываются в заданные интервалы времени и, таким образом, предотвращается перегрузка служебного процессора.

Несмотря на то, что выше была описана и проиллюстрирована предпочтительная реализация представленного изобретения, компетентным лицам будет понятна возможность проведения различных изменений и модификаций изобретения, эквивалентные замены могут быть выполнены и для отдельных его элементов без отклонения от истинного объема представленного изобретения.

Изобретения относятся к области электронных систем коммутации, использующих многопроцессорные устройства. Техническим результатом является снижение нагрузки служебного процессора за счет взаимных проверок состояния между единичными процессорами системы. Способы включают следующие действия: проверяют состояния процессоров посредством взаимных проверок состояния между единичными процессорами на основе объединения единичных процессоров в цепочечную структуру, имеющую вид связанного списка, и уведомляют служебный процессор о ненормальном состоянии единичного процессора, когда процессор находится в неисправном состоянии. 2 с. и 4 з.п.ф-лы, 4 ил., 1 табл.

| Ди- ( -карбалкоксиметокси)-диэтилсиланы, проявляющие нейротропную активность | 1974 |

|

SU565915A1 |

| US 5210861 A, 11.05.93 | |||

| US 5261096 A, 09.11.93 | |||

| SU 1546990 A1, 28.02.90 | |||

| Устройство для контроля цифровой вычислительной системы | 1987 |

|

SU1529242A1 |

Авторы

Даты

1999-11-27—Публикация

1996-06-28—Подача