(Л

d

| название | год | авторы | номер документа |

|---|---|---|---|

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| Оперативное запоминающее устройство с исправлением ошибок | 1988 |

|

SU1674269A1 |

| ПАРАЛЛЕЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С ПРОГРАММИРУЕМОЙ АРХИТЕКТУРОЙ | 2012 |

|

RU2486581C1 |

| Ультразвуковой терапевтический аппарат | 1989 |

|

SU1717106A1 |

| Устройство для контроля параллельной вычислительной системы | 1987 |

|

SU1451697A1 |

| Устройство для контроля и перезапуска ЭВМ | 1987 |

|

SU1464162A1 |

| ОТКАЗОУСТОЙЧИВАЯ БОРТОВАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА, УСТРОЙСТВО "СЛУЖБА СТОРОЖЕВОГО ТАЙМЕРА, СПОСОБ РАБОТЫ ОТКАЗОУСТОЙЧИВОЙ БОРТОВОЙ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ" | 1998 |

|

RU2131619C1 |

| СПОСОБ ФОРМИРОВАНИЯ ОТКАЗОУСТОЙЧИВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2010 |

|

RU2439674C1 |

| Устройство для управления переключением резервных блоков | 1981 |

|

SU1108623A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных комплексах с повышенными требованиями к надежности. Целью изобретения является повышение надежности системы. В качестве примера рассмотрена цифровая вычислительная система (ЦВС), в состав которой включено устройство для ее контроля. Система содержит блоки процессоров 1,2, блоки ОЗУ 3 и 4, блоки ПЗУ 5 и 6, соединенные между собой магистралью 7, устройство ввода-вывода 8, устройство для контроля 9, которое содержит блок пуска 10, блок управления реконфигурациями 11, регистры режима 12 и состояния 13, счетчик количества реконфигураций 14, "сторожевой" таймер 15. 5 ил., 2 табл.

Фи.1

68

Изобретение относится к цифровой вычислительной технике и может быть использовано в вычислительных комплексах с повышенными требованиями по надежности.

Цель изобретения - повышение надежности системы.

На фиг. 1 приведена структурная схема вычислительной системы с устройством для контроля; на Лиг. 2 - функциональная схема блока управления реконфигурациями пример исполнения ;/ на фиг.З - функциональная схема блока пуска, пример исполнения ; на фиг. 4 - схема поиска работоспособной конфигурации на фиг, 5 - один из вариантов распределения поля памяти.

Вычислительная сис тема с устройством для контроля (фиг. 1) содержит блоки процессоров 1 и 2, блоки ОЗУ 3 и 4, блоки ПЗУ 5 и 6j соединенные между собой магистралью 7, устройство 8 ввода-вывода для сопряжения с внешними устройствами и устройство 9 для контроля цифровой вычислительной системы (ЦВС).

Устройство для контроля образуют блок 10 пуска, блок 11 управления реконфигурациями, регистры 12 и 13 режима и состояния соответственно 5 счет ЧР5К 14 количества реконфигураций и сторожевой таймер 5.

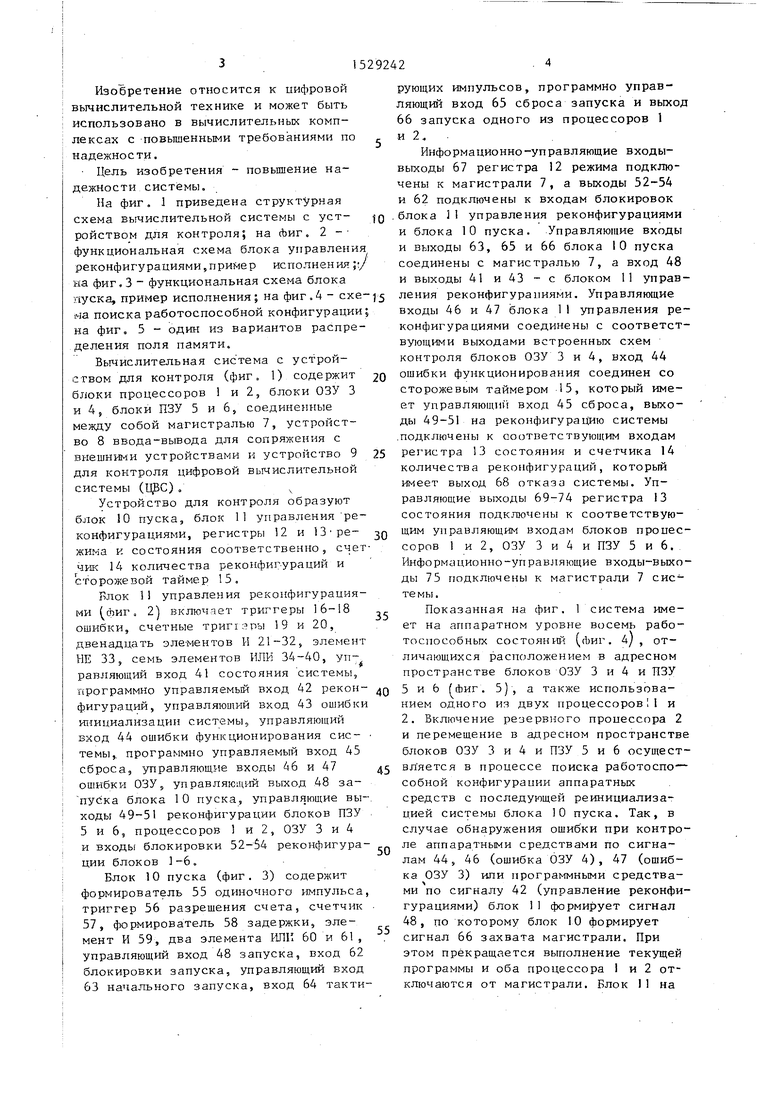

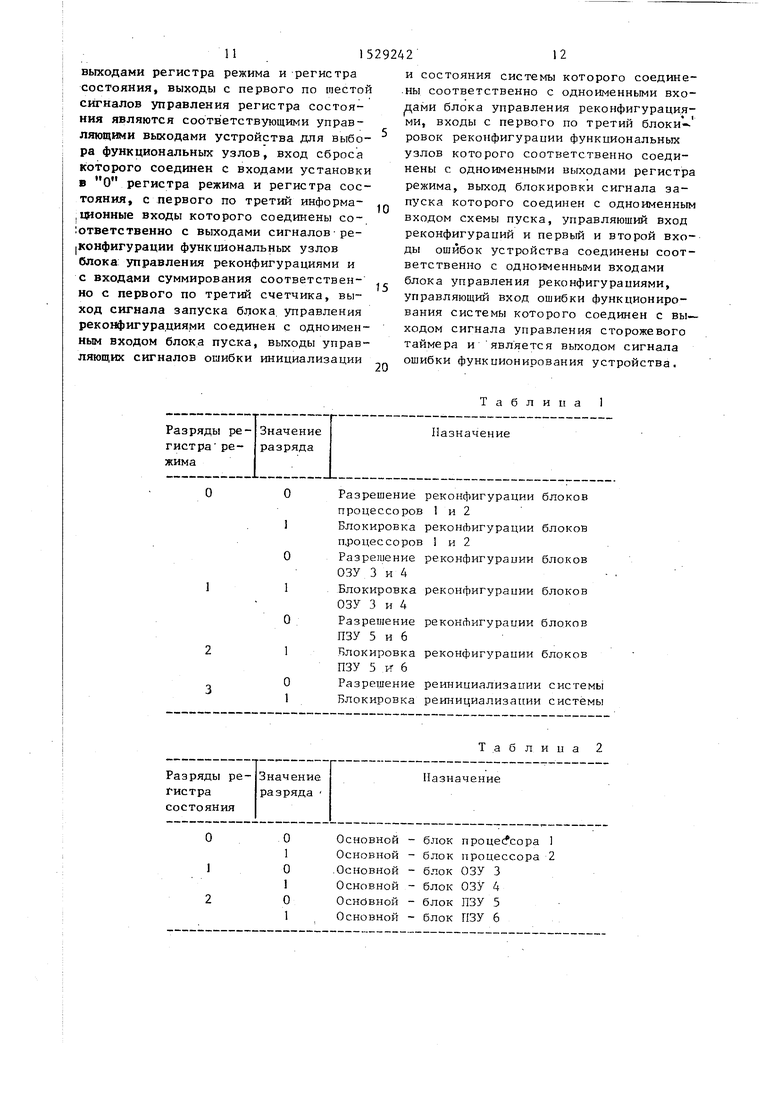

Блок 1 управления реконфигурациями фиг. 2 включает триггеры 16-18 ошибки, счетные триггзпы 19 и 20, двенадцать эле-ментов И 21-32, элемент НЕ 33, семь элементов ИЛИ 34-40, управляющий вход 41 состояния системы, программно управляемый вход 42 реконфигураций, управляющий вход 43 ошибки инициализации системы, управляющир вход 44 ошибки функционирования сие- темы,. nporpaNiMHo управляемый вход 45 сброса, управляющие входы 46 и 47 ошибки ОЗУ, управляющим выход 48 за- пуйка блока 10 пуска, управляющие выходы 49-51 реконфигурации блоков ПЗУ 5 и 6, процессоров и 2, ОЗУ 3 и 4 и входы блокировки 52-54 реконфигурации блоков 1-6.

Блок 10 пуска (фиг. 3) содержит формирователь 55 одиночного импульса триггер 56 разрешения счета, счетчик 57, формирователь 58 задержки, элемент И 59, два элемента ИЛИ 60 и 61, управляющий вход 48 запуска, вход 62 блокировки запуска, управляющий вход 63 начального запуска, вход 64 такти0

5

0

5

0

5

0

5

0

5

рующих импульсов, программно управляющий вход 65 сброса запуска и выход 66 запуска одного из процессоров 1

и 2

Информационно-управляющие входы- выходы 67 регистра 12 режима подключены к магистрали 7, а выходы 52-54 и 62 подключены к входам блокировок .блока I1 управления реконфигурациями и блока 10 пуска. Управляющие входы и выходы 63, 65 и 66 блока 10 пуска соединены с магистралью 7, а вход 48 и выходы 41 и 43 - с блоком 11 управления реконфигураПИЯМИ. Управляющие входы 46 и 47 блока 11 управления реконфигурациями соединены с соответствующими выходами встроенных схем контроля блоков ОЗУ 3 и 4, вход 44 ощибки функционирования соединен со сторожевым таймером 15, который имеет управляющий вход 45 сброса, выходы 49-51 на реконфигура 11ию системы .подключены к соответствующим входам регистра 13 состояния и счетчика 14 количества реконфигураций, который имеет выход 68 отказа системы. Управляющие выходы 69-74 регистра 13 состояния подключены к соответствующим управляющим входам блоков процессоров 1 и 2, ОЗУ 3 и 4 и ПЗУ 5 и 6.. Информационно-управляющие входы-выходы 75 подключены к магистрали 7 системы.

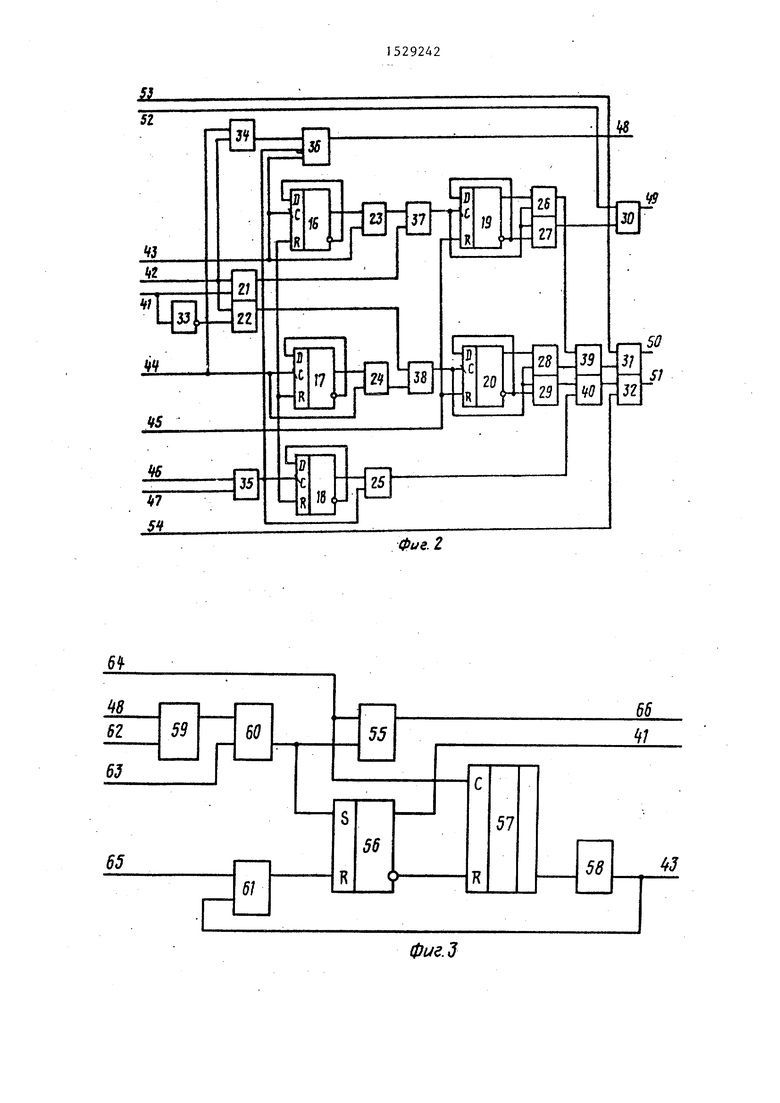

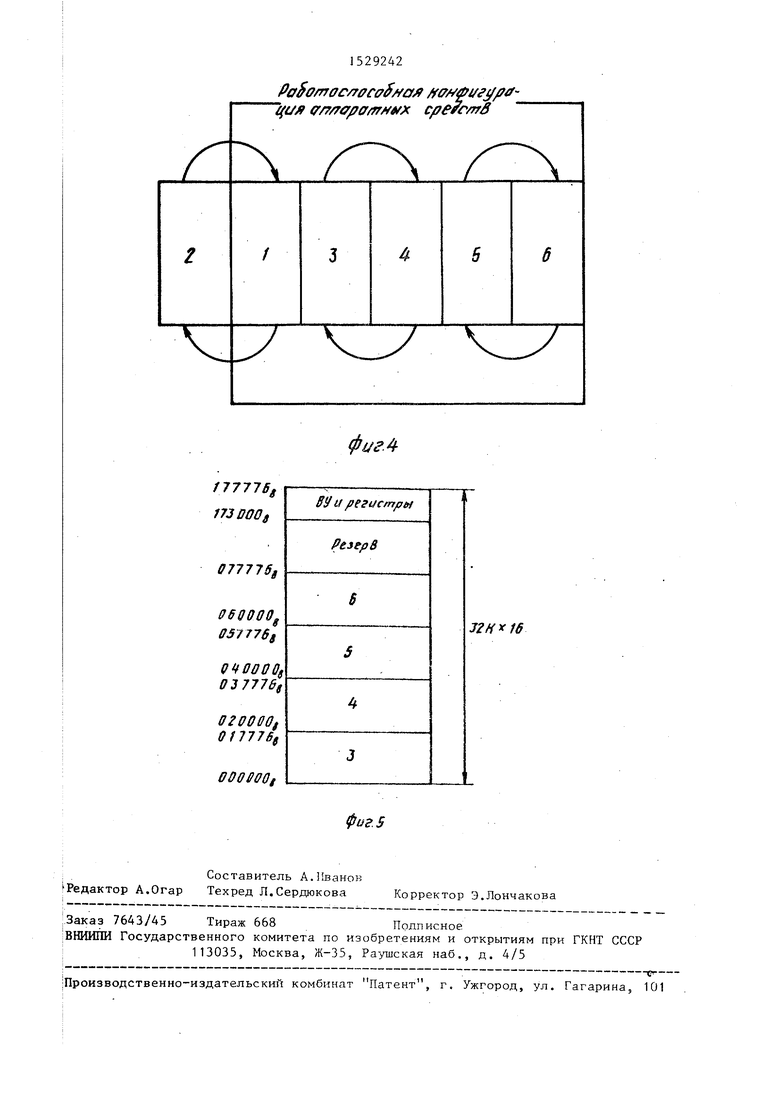

Показанная на фиг. 1 система имеет на аппаратном уровне восемь работоспособных состояний ((Ьиг. 4) , отличающихся расположением в адресном пространстве блоков ОЗУ 3 и 4 и ПЗУ 5 и 6 fd)Hr. 5), а также использованием одного из двух процессоров I1 и 2. Включение резервного пропессора 2 и перемещение в адресном пространстве блоков ОЗУ 3 и 4 и ПЗУ 5 и 6 осуществляется в процессе поиска работоспо- собной конфигурации аппаратных средств с последующей реинициализа- цией системы блока 10 пуска. Так, в случае обнаружения ошибки при контроле аппаратными средствами по сигналам 44, 46 (ошибка ОЗУ 4), 47 (ошибка ОЗУ 3) или программными средствами по сигналу 42 (управление реконфигурациями) блок 11 формирует сигнал 48, по которому блок 10 формирует сигнал 66 захвата магистрали. При этом прекращается выполнение текущей программы и оба процессора 1 и 2 отключаются от магистрали. Блок 11 на

основании полученных сигналов об ошибках с учетом текущего состояния системы и количества предьщущих состояний формирует сигналы 49 (реконфигурация ПЗУ), 50 (реконфигурация процессоров) , 51 (реконфигурация ОЗУ), фиксирующиеся в регистре 13 состояни где они преобразуются в сигналы 69 (выбор процессора 1), 70 (выбор про- цессора 2), 71 (выбор ОЗУ 3), 72 (выбор ОЗУ ii) , 73 (выбор ПЗУ 5) , 74 (выбор ПЗУ 6), которые управляют реконфигурациями орс.

При ошибке функционирования основного процессора происходит захват магистрали блоком 10, реконфигурация процессоров по сигналам 69 и 70, а затем снятие захвата магистрали, что приводит соответственно к запуску процессора, выбранного основным.

Блок- 1 1 управления реконфигурациями обнаруживает ошибки в функционировании программ ПЗУ совместно с аппаратными средствами контроля (счетчик 57, формирователь 58 схемы 10) и программными средствами контроля.

Процедура обнаружения .ошибки в функционировании программы в ПЗУ осуществляется следующим образом.

При правильном функционировании ЦВС после, выполнения программы за- из ПЗУ в ОЗУ осуществляется в результате

чего формируется программируемый сигнал 65 (.Сброс) , которьй сбрасывает счетчик 57. В дальнейшем управление функционированием ЦрС передается программе, расположенной в ОЗУ.

При неправильном функционировании ЦВС сигнал 65 ( Сброс) не вырабатывается и счетчик 57 через формирователь 58 задержки формирует сигнал 43 по которому блок 11 формирует сигнал 49, а регистр 13 - сигналы 73 и 74, что обеспечивает переключение ПЗУ.

При ошибках в ячейках ПЗУ, не влияющих на выполнение программы функционирования, подпрограмма контроля сама принимает решение о реконфигурации и формирует программируемый сигнал 42, который через блок 11 вызывает реконфигурацию ПЗУ.

Перемещение блоков ПЗУ 5 и 6 и блоков ОЗУ 3 и 4 соответственно сигналам 73 и 74, 71 и 72 осуществляется путем изменения адресных коэффициентов на Входе селектора адреса в каждом блоке ОЗУ.

грузки

о

программный контроль.

15

20

25

я, Q .

5292426Реинициализация повторная инициализация) ЦВС осуществляется всякий раз после реконфигурации в результате зафиксированной ошибки функционирования. Под инициализацией системы подразумевается установка в исходное состояние функциональных узлов процессоров 1 и 2 и запуск выполнения программы с начальной точки.

Блок 10 пуска на время реконфигурации системы сигналом 66 захватывает магистраль и устанавливает . в исходное состояние функциональные узлы процессоров 1 и 2. После завершения реконфигурации системы снимается сиг- над 66 захвата и осуществляется запуск выполнения программы из ПЗУ для очередной,работоспособной конфигурации imc.

Алгоритм работы системы сводится к нескольким процедурам: обнаружения отказа, оценки повреждения, вызванного отказом, устранения влияния отказавшего устройства и восстановления утраченной информации.

Эти процедуры реализованы на базе программных и аппаратных средств контроля. Рассмотрим реализацию каждой из четырех указанных процедур на определенной группе диагностируемых функциональных узлов.

Пара функциональных узлов основной процессор - ОЗУ соответствует режиму работы ЦВС по программе функционирования из ОЗУ.

Процедура Обнаружение отказа осуществляется путем прерывания программы по временным отсчетам по сигналу 44 и выполнения подпрограммы контроля.

При отсутствии ошибок формируется программируемый сигнал 45 сброса сторожевого таймера 15 и блока II управления реконфигурациями. При наличии ошибок, не влияющих на выполнение подпрограммы контроля, формируется программируемый сигнал 42.

При наличии ошибок, исключающих выполнение программ, не формируется сигнал 45 и сторожевой таймер 15 формирует следующий временной отсчет, по которому блок 11 фиксирует ошибку.

Процедура Диагностирование отказавшего устройства реализована в предположении, что в паре взаимодействующих узлов процессор - ОЗУ более вероятной является ошибка процессора. Поэтому вначале происходит реконфигу30

40

45

50

55

Ьация процессора, а затем при повторении - реконфигурапия ОЗУ. I Процедура Опенка повреждения, , вызванного отказом, реализована в лредположении, что обнаруженный отказ исключает продолжение работы L BC я требуется реинициализация для новой работоспособной конфигураиии.

Процедура Устранение влияния от азавше го устройства и восстановление утраченной информации происходит следующим образом.

По сигналу 42 блок 11 формирует сигнал 485 по которому блок 10 выдает сигнал 66 захвата магистрали и установки функциональных узлов процессоров 1 и 2-в ис хо дно е- состояние . Одновременно по сигналу 42 блок 11 формирует сигналы 50 и 51 на реконфигурацию соответственно процессоров и ОЗУ. Сигнал 41 указывает на работу пары функциональных узлов процессор ОЗУ, поэтому необходимые реконфигура ции происходят только с процессорами или ОЗУ. Сигналы 50 и 51 фиксируются н регистре 13 состояния и преобразуются в сигналы 69 - 72/, После выполнения реконфигураций по временному отсчету от сторожевого таймера 15 по сигналу 64 снимается сигнал 66 захяа та и осуществляется запуск процессора.

По сигналу 4-. при отсутствии сигнала 45 сброса cTopox- Boi o таймера 1 и блока 11 формирование сигналов на захват магистрали, реконЛигурапим, реинициализацию и запуск выполняется аналогично

Пара функциональных узлов процес- I сор - ПЗУ соответствует режиму рабо- ;ты иве по программе загрузки из ПЗУ : в ОЗУ.

: Процедура Обнаружение отказа осуществляется путем формировапия (при отсутствии ошибок в конце выполнения программы загрузки програм- : мируемого сигнала 65 сброса счетчика ; 57 инициализации. При наличии ошибок : не влияющих на выполнение программы I загрузки, формируется программируемы : сигнал 42. При наличии ощибок, ис- ; ключающих выполнение программы загру : кк, не формируется сигнал 65 сброса : и счетчик 57 инициализации через фор i мирователь 58 задержки вырабатывает I сигнал 43 ошибки инициализации, по 1 которому блок 11 фиксирует ошибку.

15

20

10

25

-

30

35

40

45

50

55

Процедура Диагностирование отказавшего устройства реализована в предположении, что в паре функциональных узлов процессор - ПЗУ при наличии сигнала 43. более вероятной является ошибка ПЗУ, а при формировании сигнала 42 более вероятной - ошибка процессора. Поэтому в одном случае вначале происходит реконфигурация ПЗУ, а затем при повторении - реконфигурация процессоров, для другого случая - вначале реконфигурация процессоров, затем - реконфигурация ПЗУ.

Процедура Оценка повреждения, вызванного отказом реализована в предположении, что обнаруженный отказ исключает продолжение работь ПВС и требуется реинициализация для новой работоспособной конфигурации.

Процедура Устранение влияния отказавшего устройства и восстановление утраченной информапии происходит следующим образом.

.По сигналу 42 блок 11 формирует сигнал 48, по которому блок 10 Нормирует сигнал 66 захвата магистрали и установки в исходное состояние функциональных узлов процессоров 1 и 2.

Одновременно по сигналу 42 блок формирует сигналы 49 и 50 на рекон- фиг урапию соответственно процессоров. Сигнал 41 указывае.т на ра боту функциональных узлов процессор - ПЗУ, поэтому необходимые реконфигурации проходят только с процессорами или ПЗУ.

Сигналы 49 и 50 фиксируются, в регистре 13 состояния и преобразуются в сигналы 69, 70, 73 и 74. После выполнения реконфигураций по временному отсчету от сторожевого таймера 15 по сигналу 64 снимается сигнал 66 захвата и осуществляется запуск процессора .

При формировании сигнала 43 захват магистрали, реконфигурация, ре- ш ициализация и запуск вьтолняются аналогично, за исключением того, что первыми реконфигурируются блоки ПЗУ, а затем пропессоры.

Функциональный узел ОЗУ.

Процедура Обнаружение отказа осуществляется встроенной схемой контроля в каждом блоке ОЗУ.

При считьшании информации из ОЗУ 3 или 4 при наличии ошибок формируется соответственно сигнал 47 или 46.

15

20

25

Процедура /1иагностирование отказавшего устройства реализована на аппаратном уровне и вьтолняется одновременно с функционированием программ .

Процедура Оценка повреждения, вызванного отказом реализована в предположении, что обнаруженный отказ исключает продолжение работы UBC и требуется реинициализация для новой работоспособной конфигурации.

Процедура Устранение влияния отказавшего устройства и восстановление утраченной информации происходит следующим образом.

По сигналу. 46 или 47 блок 11 формирует сигнал 48, по которому блок 10 формирует сигнал 66 захвата магистрали и установки в исходное состояние функциональных узлов процессоров I и 2.

Одновременно по сигналу 46 или 47 блок 11 формирует сигнал 51 на реконфигурацию ОЗУ, который фиксируется в регистре 13 состояния и преобразуется в сигналы 71 и 72. После выполнения реконфигураций по временному отсчету от сторожевого таймера 15 по сигналу 64 снимается сигнал 66 захвата и осуществляется запуск процессора. .

Тестовое диагностирование представляет собой автоматизированный контроль функциональных узлов и локализацию дефектов с помощью тест-программ, которые могут располагаться как в самой UpC, так и в специальной технологической контрольно-проверочной аппаратуре.

Для тестового диагностирования ЦВС, обладающей свойством отказа устойчивости, т.е. маскирующей свои ошибки, необходимо иметь возможность управлять состояниями системы и контролировать их. С этой целью в устройство 9 управления введены программно- доступные регистры 12 и 13 режима и состояния. При проверке отдельных функциональных узлов в регистре 12 режима должен устанавливаться код в соответствии с табл. 1, блокирующий или разрешающий возможные рекоцфи- гураиии или реинициализацию системы. Это дает возможность проверить в составе иве от дельные . узлы и локализо- 55 вать дефекты с высокой точностью на этапах настройки и изготовления, а на этапе эксплуатации более точно

30

35

40

45

50

0

5

0

5

5

0

5

0

5

0

устранить отказ, что в результате по- вычает надежность и ресурс IJBC. При этом состояние ЦрС фиксируется в регистре 13 состояния, формат которого приведен в табл. 2. Содержимое регистра 13 состояния анализируется основным пропессором или внешним активным устройством через магистраль.

Пример. При считьгоании информации из ОЗУ 3, в котором существует отказавшая ячейка памяти, формируется сигнал 47, что вызывает взаимное 1те- ремещение блоков ОЗУ 3 и 4. Это маскирует ошибку, которую невозможно обнаружить и локализовать. В такой ситуации, если в регистр 12 режима в разряд 1 (табл. 1) записать код 1, который формирует сигнал 54 бло1;иров-- ки -реконфигурапии блоков ОЗУ, то блок 11 не установит сигнал 51 на реконфигурацию и тестирование блоков ОЗУ 3 и 4 выполнится в одном объеме и с большей глубиной поиска дефектов.

При выполнении тестового диагностирования по другим устройствам LVBC В регистр 12 режима записьгоаются коды в соответствии с табл. 1, которые .формируют сигналы 52-54 и 62 блок-иро- вок. В зависимости от вьтолняемой тестовой проверки могут формироваться как отдельные сигналы блокировок, так и группа таких сигналов.

Формула изобретения

Устройство для контроля оифровэй вычислительной системы, содержащее блок пуска, сторожевой таймер и счетчик, причем выход сигнала запуска блока пуска является одноименным выходом устройства, входы начального пуска и блокировки начального пуска которого соединены с одноименными входами блока пуска, тактовый вход которого соединен с одноименным выходом сторожевого таймера, вход сброса которого соединен с входом сброса в О счетчика и является входом сброса устройства, выход переполнения счетчика является выходом сигнала Отказ системы устройства, отличающееся тем, что, с целью повышения надежности системы, в устройство введены регистр режима, регистр состояния и блок управления реконфигурациями, причем инсЬормацион - |но-уТ1равляющие входы-выходы устройст- 1ва Соединены с одноименными входамивыходами регистра режима и регистра состояния, выходы с первого по шестой сигналов управления регистра состояния являются соответствующими управляющими выходами устройства для выбора функциональных узлов, вход сброса которого соединен с входами установки в О регистра режима и регистра состояния, с первого по третий информа- ,иионные входы которого соединены со- Ютветственно с выходами сигналов ре- |Конфигурации функциональных узлов блока: управления реконфигурациями и с входами суммирования соответственно с первого по третий счетчика, выход сигнала запуска блока, управления реконфигурадиями соединен с одноименным входом блока пуска, выходы управляющих сигналов ошибки инициализации

и состояния системы которого соедине- ны соответственно с одноименными входами блока управления реконфигурациями, входы с первого по третий блоки- ровок реконфигурации функциональных узлов которого соответственно соединены с одноименными выходами регистра режима, выход блокировки сигнала запуска которого соединен с одноименным входом схемы пуска, управляющий вход реконфигураций и первый и второй входы ошибок устройства соединены соответственно с одноименными входами блока управления реконфигурациями, управляющий вход ошибки функционирования системы которого соединен с выходом сигнала управления сторожевого таймера и является выходом сигнала ошибки функционирования устройства.

Таблица 1

Таблица 2

фиг. Z

фие.З

Po omoc/7ffCff$/fa/f /fff/i ue /fff fff/Jf C/jei C/TfS

n7776g 173DOOa

077775,

ffffOffOOg 057776

Q OOOOg 037776,

огоооо

On776f

oooeoOf

фиг Л

| Патент США № 4072852, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля двухпроцессорной системы | 1982 |

|

SU1013962A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-12-15—Публикация

1987-12-07—Подача