Настоящее изобретение относится к системам связи с частотной модуляцией (ЧМ). Более конкретно, настоящее изобретение относится к новой двухрежимной системе связи, селективно работающей как в режиме с ЧМ, так и в режиме многостанционного доступа с кодовым разделением каналов (МДКР).

Предшествующий уровень техники

Демодуляция принимаемых ЧМ сигналов связи традиционно выполняется с использованием аналоговых методов обработки сигналов. Однако в последнее время разработаны методы, которые позволяют обрабатывать аналоговые сигналы связи с использованием цифровых методов обработки сигналов. К числу таких методов относятся методы дискретизации фазы и дискриминации приходящего сигнала для восстановления информации передаваемых сообщений. Информация, содержащаяся в сообщениях, часто восстанавливается с использованием, например, квадратурных методов детектирования.

Одним из методов демодуляции ЧМ сигнала, пригодным для цифровой реализации, является так называемое "прямое преобразование". При использовании метода прямого преобразования или "нулевой промежуточной частоты" в приемнике осуществляется смешивание приходящего радиочастотного сигнала с преобразованием его непосредственно в полосу частот модуляции (базовую полосу). Преимущество прямого преобразования состоит в том, что фильтрация для обеспечения селективности каналов может производиться непосредственно в базовой полосе и, следовательно, может быть с выгодой реализована с применением технологии интегральных схем.

Недостаток демодуляции прямого преобразования связан с возникновением паразитных напряжений смещения постоянной составляющей, которые могут возникать на выходе смесителя вместе с полезным сигналом базовой полосы, который также может содержать спектральные компоненты постоянного тока. Паразитное напряжение смещения постоянной составляющей может также быть обусловлено смещениями по постоянному току, возникающими в каскаде смесителя, а также сигналом утечки радиочастотного гетеродина, подвергающимся понижающему преобразованию на частоту постоянного тока. Влияние таких паразитных смещений постоянного тока на процесс демодуляции ЧМ сигнала можно моделировать, например, в виде нелинейности, содержащейся в идеальном демодулированном сигнале. Величина результирующего искажения, т.е. "ошибка смещения", является функцией величины смещения постоянного тока относительно огибающей ЧМ сигнала. Для типовых применений с использованием аудиосигнала допустимая достоверность воспроизведения требует, чтобы ошибки смещения были менее нескольких процентов. Следовательно, существует потребность в цифровом приемнике ЧМ сигнала, обеспечивающем отделение полезного сигнала базовой полосы от паразитных смещений постоянного тока.

Кроме того, цифровые приемники, работающие на принципе прямого преобразования, обладают относительно узким динамическим диапазоном. Для обеспечения обработки в динамическом диапазоне принимаемого ЧМ сигнала необходимо предусмотреть дополнительные схемы автоматической регулировки усиления (АРУ). В типовом случае в цифровых приемниках процедура АРУ включает в себя детектирование, аналого-цифровое преобразование и измерение в базовой полосе мощности приходящего сигнала. Измеренное значение сравнивается с полезным опорным значением и формируется сигнал ошибки. Сигнал ошибки фильтруется с помощью фильтра цепи АРУ, и отфильтрованный цифровой выходной сигнал используется для регулировки усиления усилителя таким образом, чтобы уровень сигнала совпадал с желательной мощностью сигнала. Для осуществления цифровой демодуляции с оптимальным отношением сигнала к шуму АРУ используется для поддержания величин сигналов базовой полосы близкими к полному динамическому диапазону аналого-цифровых преобразователей (АЦП) базовой полосы. Однако в общем случае это требует обеспечения того, чтобы усилители с АРУ перекрывали полный динамический диапазон мощности принимаемых сигналов.

При некоторых условиях функционирования цифровой приемник может принимать сигнал, который проявляет быстрые и значительные вариации мощности. Например, в цифровых приемниках, таких как используемые в мобильных сотовых телефонных системах с МДКР, необходимо ограничить мощность принимаемого сигнала для обеспечения надлежащей обработки принимаемого сигнала. Аналогичным образом, в цифровых приемниках, которые являются совместимыми с МДКР режимом и с обычным ЧМ режимом, т.е. в двухрежимных приемниках с МДКР/ЧМ, необходимо предусмотреть ограничение мощности как широкополосных МДКР сигналов, так и узкополосных ЧМ сигналов. Процесс ограничения усложняется вследствие различия в динамических диапазонах, связанных с мощностью принимаемых ЧМ и МДКР сигналов. То есть величина принимаемых ЧМ сигналов может изменяться в динамическом диапазоне порядка 110 дБ, что соответствует сотовым системам, в то время как существующие методы регулировки мощности в МДКА системах в типовом случае приводят к намного более ограниченному динамическому диапазону порядка 80 дБ.

Обеспечение отдельных схем АРУ для каждого из режимов двухрежимных приемников с ЧМ/МДКР приводит к усложнению аппаратных средств и повышает стоимость таких приемников. Соответственно, было бы желательным создать схемы АРУ, обеспечивающие работу с использованием как узкополосных ЧМ сигналов с широким динамическим диапазоном, так и широкополосных МДКР сигналов с более ограниченным динамическим диапазоном.

В цифровых приемниках используется ряд методов осуществления цифровой демодуляции ЧМ сигналов. К обычно используемым методам относятся демодуляция сигнала промежуточной частоты (ПЧ) с использованием счета пересечений нуля или демодуляция в базовой полосе с использованием квадратурного детектирования.

Цифровой способ квадратурной демодуляции ЧМ сигнала описан в патенте США N 4675882 на "Демодулятор ЧМ сигнала", переуступленном компании Моторола, Инк. В этом патенте описано устройство, предназначенное для обработки дискретизированного входного векторного сигнала, представляющего собой квадратурный ЧМ сигнал, центрированный по существу на нулевой частоте. Вектора квадратурного входного сигнала масштабируются для обеспечения попадания их в предварительно определенный диапазон величин. Кроме того, вектор входного сигнала поворачивается до достижения предварительно определенного квадранта с использованием грубого значения фазы, выработанного накопителем фазы. В пределах предварительно определенного квадранта точное значение фазы определяется по положению повернутого вектора, причем точное и грубое значения фазы суммируются, и выходной сигнал формируется в виде составного значения фазы. Последовательные выборки составной фазы затем вычитаются для формирования последовательности выборки демодулированного сообщения.

Различные характеристики устройства демодулирования по патенту США N 4675882 требуют реализации этого устройства на основе процессоров цифровых сигналов, а не с использованием специализированных цифровых аппаратных средств. Например, это устройство использует цифровой определитель обратного значения, предназначенный для формирования обратной величины синфазной компоненты сигнала базовой полосы до перемножения с противофазной компонентой. В предпочтительном варианте осуществления определитель обратной величины аппроксимирует функцию f(x) = 1/x полиномом Чебышева, что наиболее удобно реализовать с использованием цифрового процессора сигналов. К сожалению, относительно высокое потребление мощности таких цифровых процессоров сигналов является существенным недостатком по сравнению со специализированными цифровыми аппаратными средствами различного типа портативных приемопередатчиков связи, таких как устройства персональной связи.

Кроме того, можно сделать вывод, что устройство демодуляции по патенту N 4675882 является восприимчивым к ошибкам смещения по постоянному току, возникающим вследствие сигнала утечки гетеродина, а также иных источников проникающего сигнала, обуславливающего формирование постоянной составляющей. То есть указанное известное устройство отображает энергию сигнала постоянной составляющей непосредственно в базовую полосу на нулевой частоте, на которой также присутствуют полезные квадратурные компоненты сигнала базовой полосы. Соответственно, результирующая оценка фазового угла может оказаться искаженной в присутствии существенной энергии добавочного сигнала постоянной составляющей.

Фильтрация сигнала часто выполняется с использованием фильтров ПЧ для достижения адекватной режекции внеполосного сигнала. Хотя требуемая степень режекции сигнала может быть обеспечена с использованием фильтров ПЧ на керамике, однако подобные фильтры имеют относительно большие габариты и высокую стоимость. Фильтры ПЧ с меньшими габаритами или более дешевые в общем случае не обеспечивают требуемые характеристики режекции сигналов и, следовательно, в общем случае не могут быть использованы в приемниках ЧМ сигнала сотовых телефонов.

Хорошо известно, что последние достижения в технологии интегральных схем (ИС) обеспечили возможность реализации активных фильтров базовой полосы с достаточно малыми габаритами и стоимостью. Отсюда следует, что было бы весьма желательным использовать активные фильтры базовой полосы на ИС для реализации существенной режекции внеполосных сигналов, что позволяет использовать малогабаритные недорогие фильтры ПЧ для обеспечения дополнительной требуемой режекции сигналов. Также известно, что способность режекции активного фильтра является функцией усиления фильтра, однако активные фильтры базовой полосы на ИС с более высоким усилением проявляют повышенную восприимчивость к нежелательным смещениям, обусловленным постоянной составляющей. Эта повышенная восприимчивость может быть объяснена увеличением усиления эффекта, обусловленного источниками упомянутого смещения. Это значит, что паразитные компоненты постоянной составляющей усиливаются активным фильтром базовой полосы на ИС и будут действовать как источник шума в демодуляторе ЧМ сигнала.

Таким образом, использование активных фильтров базовой полосы на ИС приводит к необходимости обеспечения некоторого механизма подавления паразитных смещений, обусловленных постоянной составляющей. К сожалению, тракт обработки на ПЧ обычных цифровых приемников в типовом случае включает в себя гетеродин, частота которого выбрана так, чтобы радиочастотная несущая частота преобразовывалась с понижением частоты в постоянную составляющую, при этом приводя к разрушению амплитудной и фазовой информации на несущей частоте в процессе обработки, связанной с подавлением смещения по постоянному току. Это не представляет проблемы для цифровой демодуляции сигналов с подавленной несущей, таких как передаваемые сигналы с квадратурной фазовой манипуляцией. Однако в сотовых телефонных системах с использованием ЧМ сигналов существенная амплитудная и фазовая информация часто присутствует на несущей частоте, и эффективность системы может быть значительно снижена, если такая информация будет разрушена.

В стандартных сотовых телефонных системах с ЧМ сигналом речевая информация в типовом случае проходит через высокочастотный фильтр для обеспечения подавления энергии сигналов на частотах ниже 300 Гц до подачи на частотный модулятор. Хотя частично речевая информация может присутствовать в ЧМ сигнале на частотах, смещенных менее чем на 300 Гц, такие интермодуляционные продукты являются нестационарными. Соответственно, подавление низкочастотных интермодуляционных продуктов обычно не приводит к потере заметной части речевой информации.

Поэтому дополнительной задачей изобретения является создание устройства АРУ для использования в двухрежимном приемнике, которое обеспечивает фильтрацию в базовой полосе без потери информации на несущей частоте.

Сущность изобретения

Настоящее изобретение относится к новой двухрежимной цифровой системе связи для передачи информационного сигнала при работе в режиме с использованием ЧМ сигнала и в режиме с МДКР. Цифровая система связи содержит двухрежимный передатчик для передачи информационного сигнала с использованием ЧМ сигнала связи при работе в режиме ЧМ и для передачи информационного сигнала с использованием сигнала с квадратурной фазовой манипуляцией (КФМн) с расширенным спектром при работе в режиме МДКР.

Система связи также содержит двухрежимный приемник для приема ЧМ сигнала связи при работе в режиме ЧМ и для приема сигнала с КФМн с расширенным спектром при работе в режиме МДКР. Двухрежимный приемник также содержит цифровой демодулятор для восстановления информационного сигнала из принятого ЧМ сигнала при работе в режиме ЧМ и для восстановления информационного сигнала из принятого сигнала с КФМн при работе в режиме МДКР.

Что касается двухрежимного приемника, то демодулятор ЧМ сигнала может быть включен в состав цифрового демодулятора для преобразования оцифрованного принятого ЧМ сигнала связи базовой полосы, предпочтительно с центральной частотой на предварительно определенной частоте базовой полосы, смещенной относительно нулевой частоты, в восстановленный информационный сигнал. Преобразование выполняется таким образом, чтобы каждая цифровая выборка принятого сигнала базовой полосы включала первую и вторую компоненты выборки в фазовой квадратуре. В предпочтительном варианте осуществления демодулятор ЧМ сигнала первоначально обеспечивает вычисление отношения первой и второй компонент каждой цифровой выборки входного сигнала. Фазодемодулированный сигнал определяется путем вычисления арктангенса для каждого отношения цифровой выборки. Частотно-демодулированный сигнал, эквивалентный демодулированному информационному сигналу, определяется путем фильтрации демодулированной по фазе последовательности с использованием цифрового блока дифференцирования.

Краткое описание чертежей

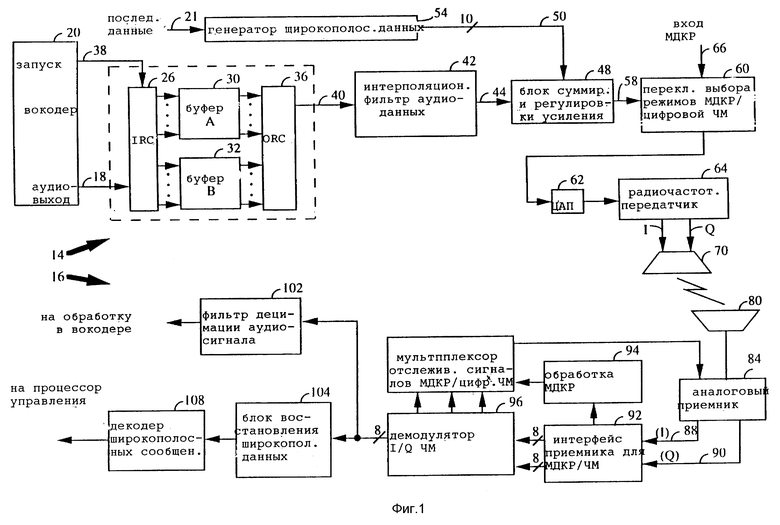

Фиг. 1 - блок-схема двухрежимной цифровой системы связи, соответствующей изобретению.

Фиг. 2 - блок-схема интерполяционного фильтра аудиосигнала, предназначенного для использования в двухрежимном передатчике системы связи, соответствующей изобретению.

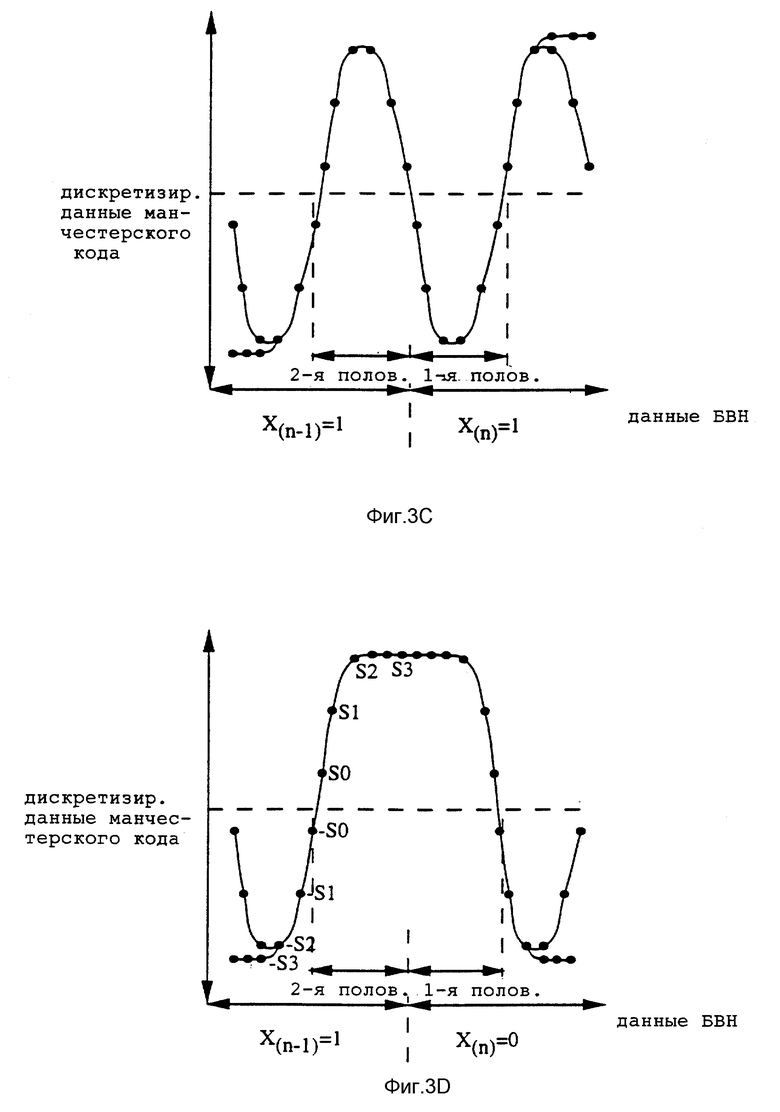

Фиг. 3A - 3D - набор дискретизированных широкополосных синусоидальных сигналов, формируемых генератором широкополосного сигнала, включенным в двухрежимный передатчик в режиме ЧМ.

Фиг. 3E - представление в табличной форме информации, проиллюстрированной на фиг. ЗА - 3D.

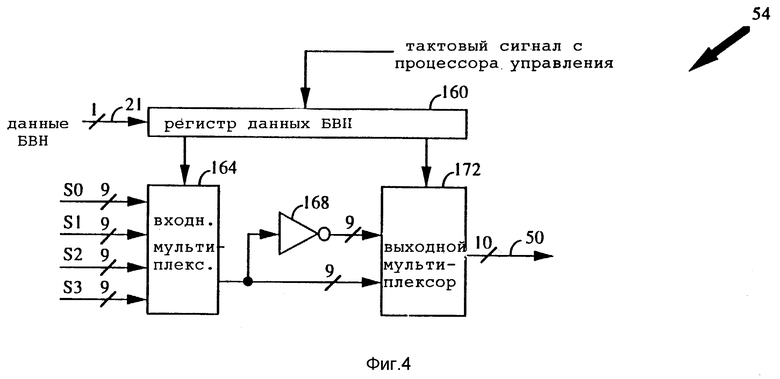

Фиг. 4 - блок-схема предпочтительного варианта осуществления генератора сигнала широкополосных данных.

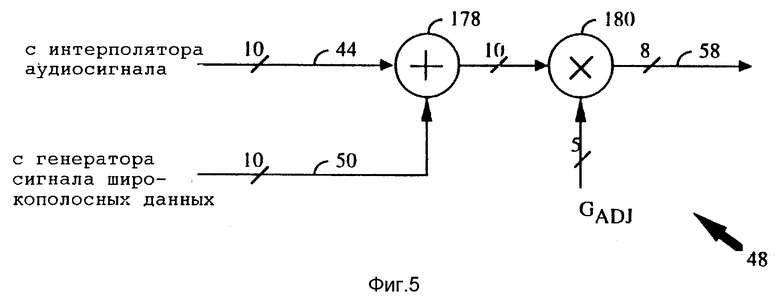

Фиг. 5 - блок-схема блока суммирования и регулировки усиления, входящего в состав двухрежимного передатчика.

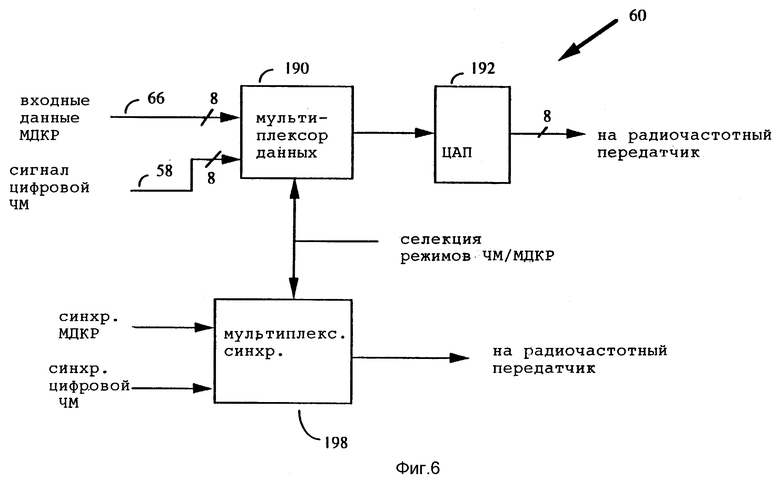

Фиг. 6 - блок-схема мультиплексора МДКР/ЧМ, обеспечивающего селективную подачу сигнала режима МДКР и цифрового ЧМ сигнала на радиочастотный передатчик.

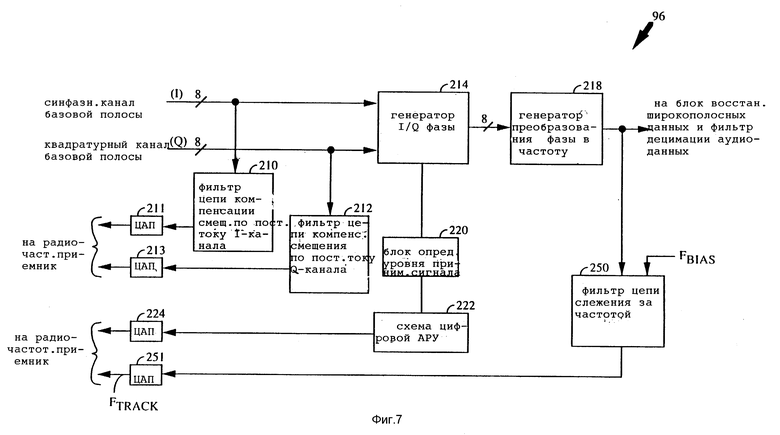

Фиг. 7 - блок-схема предпочтительного варианта осуществления квадратурного демодулятора ЧМ сигнала, входящего в состав двухрежимного приемника, соответствующего изобретению

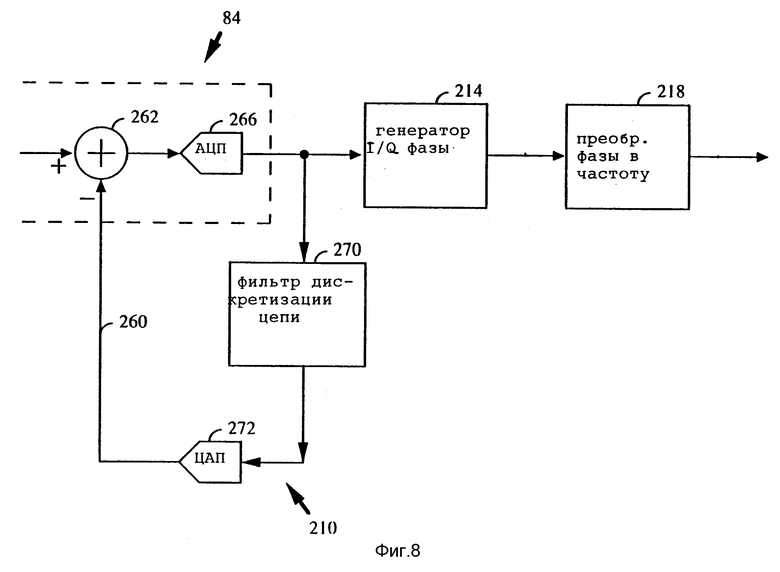

Фиг. 8 - блок-схема канала синфазной составляющей системы компенсации смещения по постоянному току.

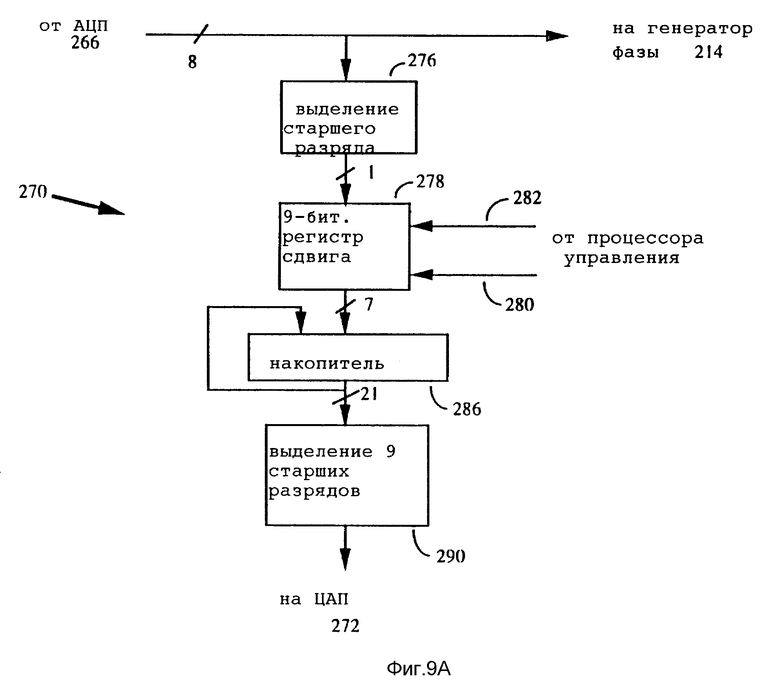

Фиг. 9A - блок-схема предпочтительного варианта осуществления фильтра цепи дискретизации, содержащегося в схеме фильтра цепи компенсации смещения по постоянному току канала синфазной составляющей.

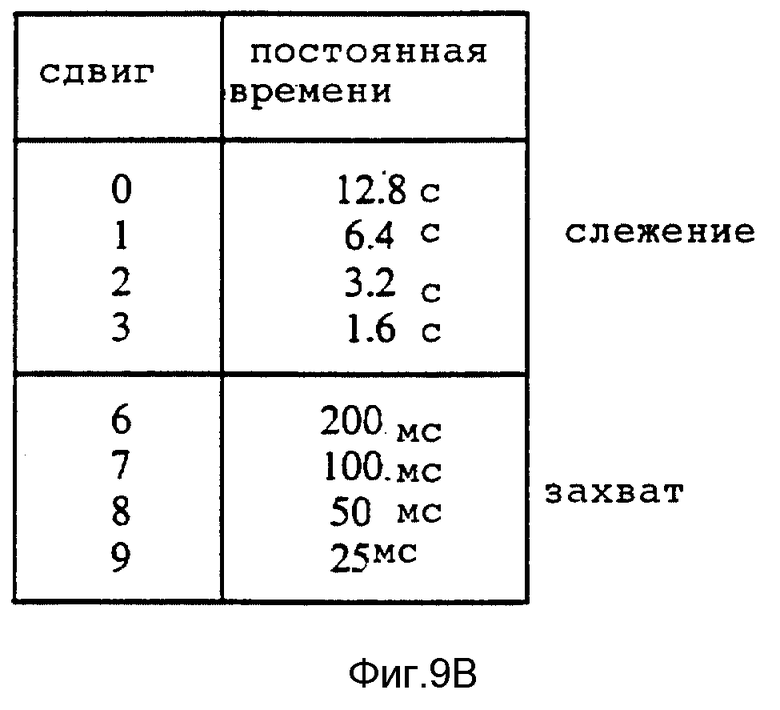

Фиг. 9B - таблица постоянных времени, соответствующих настройке цепи коррекции смещения по постоянному току при работе в режимах слежения и захвата.

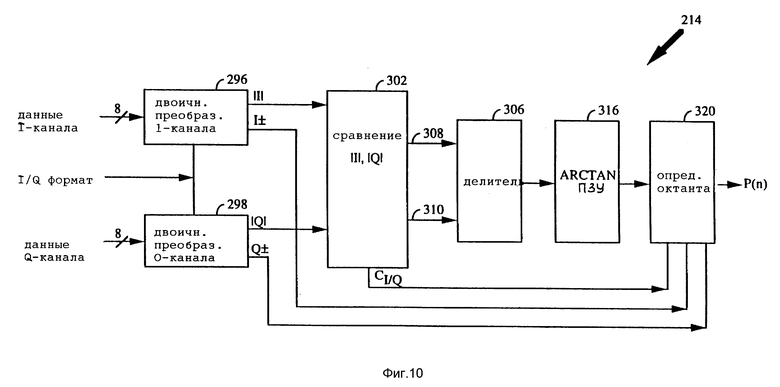

Фиг. 10 - блок-схема, иллюстрирующая генератор квадратурных значений фазы, входящий в состав квадратурного демодулятора ЧМ сигнала.

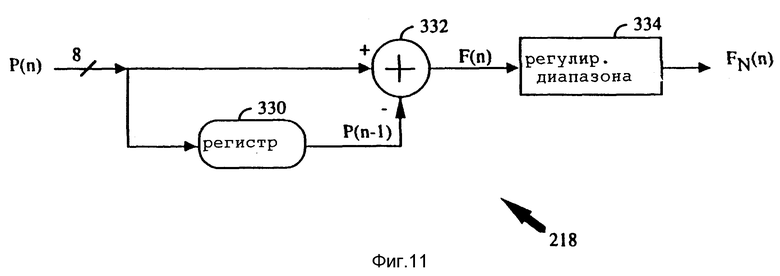

Фиг. 11 - блок-схема предпочтительного варианта осуществления генератора для преобразования фазы в частоту, входящего в состав квадратурного демодулятора ЧМ сигнала.

Фиг. 12A - иллюстрация выполнения цифровой цепи АРУ, обеспечивающей регулировку усиления сигнала ПЧ.

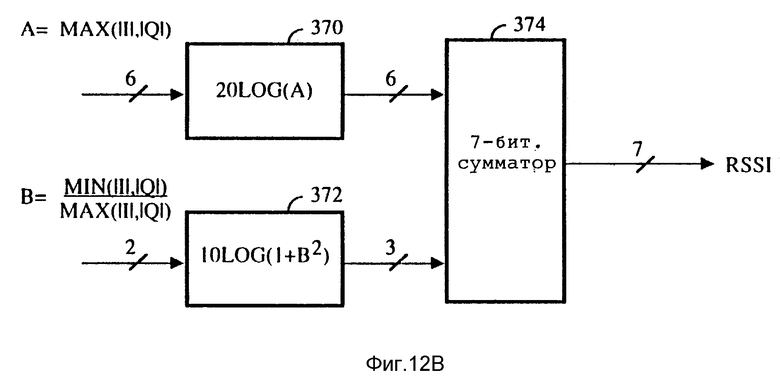

Фиг. 12B - блок-схема, иллюстрирующая предпочтительный вариант осуществления блока индикации уровня принимаемого сигнала для цепи цифровой АРУ.

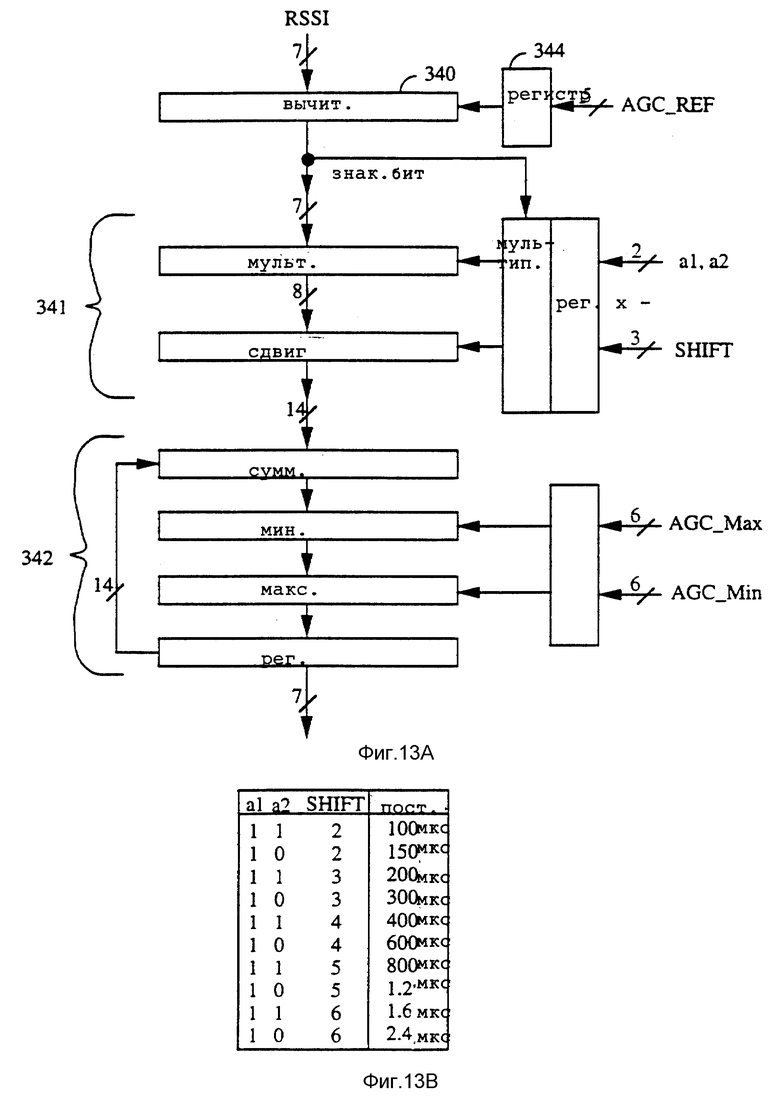

Фиг. 13A - предпочтительный вариант осуществления схемы цифровой АРУ, содержащей интегратор и блок вычитания.

Фиг. 13B - таблица постоянных времени цепи АРУ, соответствующих различным комбинациям выбранных параметров усиления цепи АРУ.

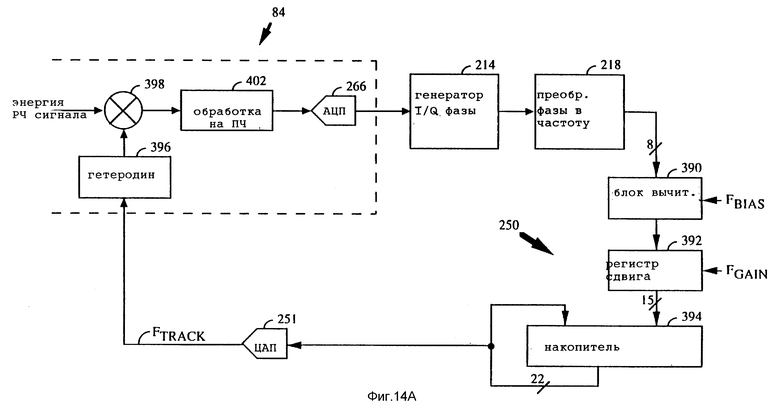

Фиг. 14A - иллюстрация предпочтительного варианта осуществления цепи слежения за частотой, входящей в состав двухрежимного приемника, соответствующего изобретению.

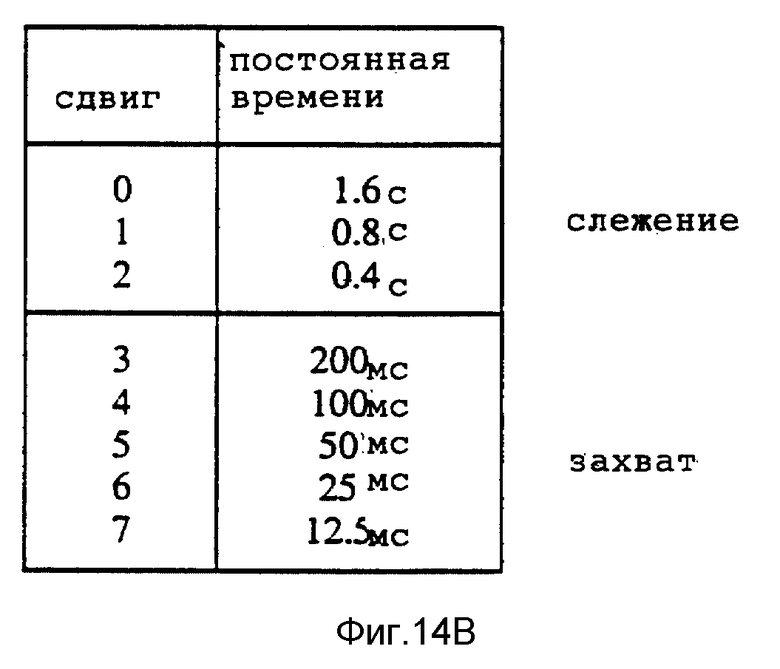

Фиг. 14B - таблица постоянных времени цепи слежения за частотой, соответствующих выбранным постоянным времени цепи регулировки усиления.

Фиг. 15 - блок-схема предпочтительного варианта осуществления фильтра децимации аудиосигнала, входящего в состав двухрежимного приемника, соответствующего изобретению.

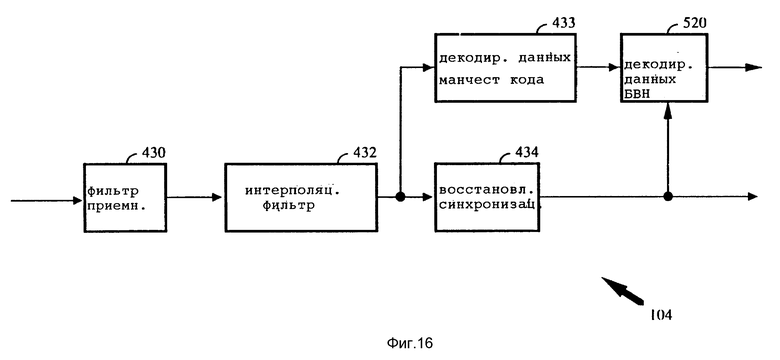

Фиг. 16 - иллюстрация выполнения схем восстановления широкополосных данных.

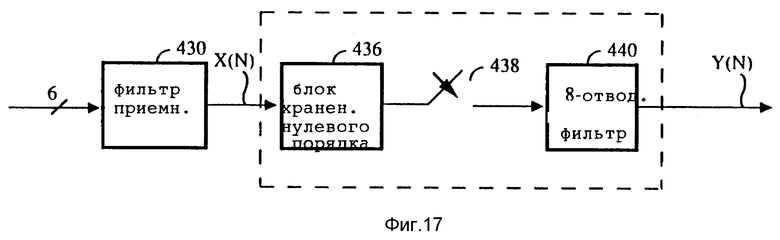

Фиг. 17 - блок-схема интерполяционного фильтра, входящего в состав схемы восстановления широкополосных данных.

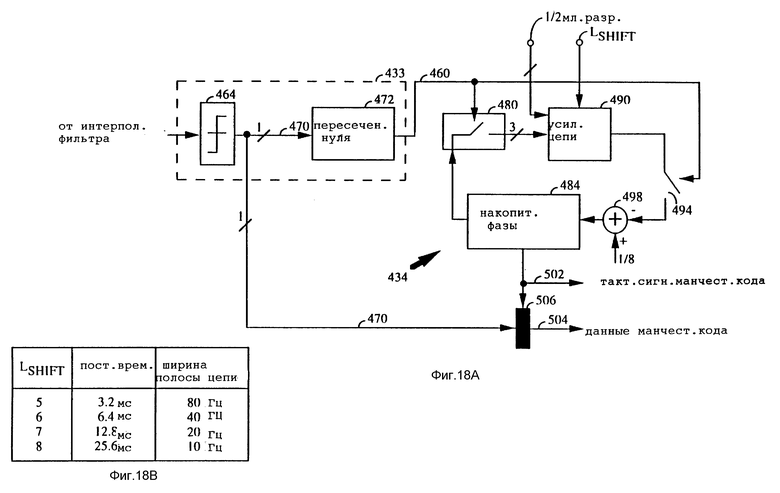

Фиг. 18A - блок-схема схем восстановления синхронизации и декодирования с использованием манчестерского кода.

Фиг. 18B - таблица постоянных времени и значений ширины полосы цепи для фазоследящей цепи в схеме декодирования с использованием манчестерского кода.

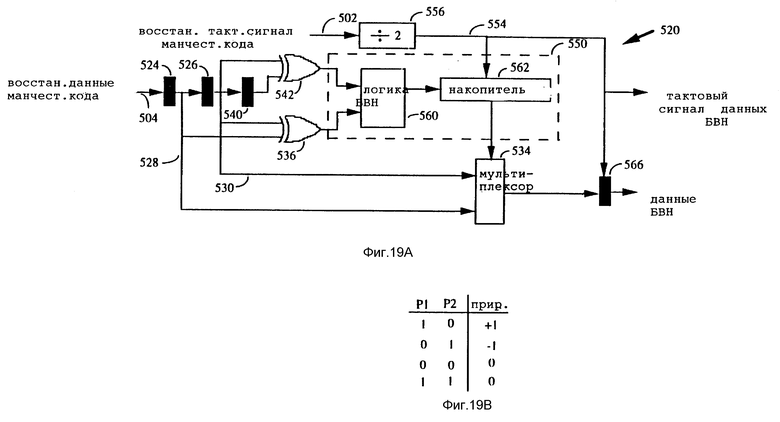

Фиг. 19A - схематичное представление декодера типа "без возвращения к нулю", входящего в состав схемы восстановления широкополосных данных.

Фиг. 19B - таблица, иллюстрирующая работу логической схемы "без возвращения к нулю", входящей в состав декодера типа "без возвращения к нулю".

Детальное описание предпочтительного варианта осуществления изобретения

На фиг.1 представлен пример осуществления двухрежимной цифровой системы связи, соответствующей изобретению. Двухрежимная система связи содержит двухрежимный передатчик 14, предназначенный для передачи цифровых информационных сигналов к двухрежимному цифровому приемнику 16. В режиме цифровой ЧМ передаваемые цифровые информационные сигналы генерируются в двухрежимном передатчике посредством ЧМ радиочастотной несущей на базе оцифрованных аудиосигналов и широкополосных сигналов данных. В режиме работы с множественным доступом передаваемые информационные сигналы содержат, например, информационные сигналы МДКР типа. Сигнал селекции режимов ЧМ и МДКР, подаваемый на передатчик 14 посредством процессора управления (не показан), обеспечивает селекцию либо режима цифровой ЧМ, либо режима МДКР.

1. Общие характеристики двухрежимного передатчика

Как показано на фиг. 1, канал обработки цифровой ЧМ передатчика 14 обеспечивает прием дискретизированных информационных аудиосигналов 18 с цифрового процессора сигналов 20, а также прием последовательного потока двоичных данных сообщений 21 от процессора управления (не показан). В рассматриваемом варианте осуществления дискретизированные (например, 12-битовые) информационные аудиосигналы 18 подаются на интерполяционный фильтр 42 аудиосигнала передатчика 14 со скоростью 20 киловыборок в секунду (квыб./с). Как описано ниже, интерполяционный фильтр 42 преобразует дискретизированные данные аудиосигнала со скоростью 20 квыб./с в поток со скоростью 120 квыб./с дискретизированных данных аудиосигнала 44, причем каждая аудиовыборка 44 состоит из 10 битов. Дискретизированные аудиоданные 44 затем объединяются в блоке суммирования и регулировки усиления 48 с дискретизированным сигналом широкополосных данных 50, формируемым генератором 54 широкополосных данных.

Составной цифровой сигнал частотной модуляции 58, формируемый блоком суммирования и регулировки усиления 48, подается на переключатель выбора режима 60 в составе интерфейса передачи МДКР/ЧМ сигналов. В режиме работы с использованием ЧМ сигнала переключатель выбора режимов 60 подает цифровой сигнал частотной модуляции на цифроаналоговый преобразователь (ЦАП) 62. В передатчике 64 радиочастотного сигнала полученный аналоговый сигнал частотной модуляции непосредственно модулирует несущую ПЧ. Более подробно способ генерирования цифрового сигнала частотной модуляции в соответствии с изобретением описан ниже со ссылками на фиг.2-4.

После переключения из режима цифровой ЧМ в режим МДКР сигнал данных режима МДКР, подаваемый по линии 66 ввода данных МДКР, подается на радиочастотный передатчик 64 вместо сигнала цифровой частотной модуляции. В режиме МДКР передатчик 64 генерирует синфазную (I) и квадратурную (Q) псевдошумовые последовательности PNI и PNQ, которые в типовом случае соответствуют конкретной области (ячейке сотовой связи), в которую передается информация в режиме работы МДКР. В передатчике 64 сигнал данных МДКР обрабатывается по схеме "Исключающее ИЛИ" с последовательностями PNI и QNI для обеспечения расширения спектра сигнала данных в режиме МДКР до его передачи. Полученные в результате последовательности с расширенным спектром синфазного канала (I-канала) и квадратурного канала (Q-канала) используются для двухуровневой фазовой модуляции пары синусоидальных сигналов в квадратуре. Модулированные синусоидальные сигналы суммируются, фильтруются в полосе, преобразуются на радиочастоту и вновь фильтруются и усиливаются перед их излучением антенной 70 по каналу связи к двухрежимному приемнику 16. Возможный вариант осуществления передатчика и генератора сигнала для режима МДКР описан, например, в патенте США N 5103459, выданном в 1992 г. на "Систему и способ формирования сигналов в сотовой системе телефонной связи с МДКР", переуступленном правопреемнику настоящего изобретения и упоминаемом здесь для ссылки.

2. Общие характеристики двухрежимного приемника

Как показано на фиг. 1, двухрежимный приемник 16 содержит приемную антенну 80 для приема информационных сигналов I - канала и Q - канала, переданных двухрежимным передатчиком 14. Как в режиме МДКР, так и в режиме цифровой ЧМ, информационные сигналы I - канала и Q - канала, принятые антенной 80, подвергаются обработке посредством аналогового приемника 84 прямого преобразования. В аналоговом приемнике 84 информационные сигналы I - канала и Q - канала смешиваются с сигналом гетеродина для формирования синфазного (I) и квадратурного (Q) сигналов базовой полосы. В режиме цифровой ЧМ частота гетеродина выбирается смещенной на предварительно определенную величину относительно радиочастотной несущей. Таким способом принятые I и Q информационные сигналы преобразуются в I и Q сигналы цифровой ЧМ базовой полосы, смещенные относительно нулевой частоты, т.е. от нулевой ПЧ на предварительно определенную величину.

Как упоминалось выше, в обычных приемниках прямого преобразования ЧМ сигнала любая паразитная энергия сигнала постоянной составляющей, содержащаяся во входном сигнале, непосредственно отображается в полосу на нулевой частоте, относительно которой центрированы квадратурные составляющие полезного сигнала базовой полосы. В результате последующие оценки фазового угла могут оказаться искаженными в присутствии значительной энергии постороннего сигнала постоянной составляющей. В соответствии с изобретением смещение по частоте, преднамеренно введенное в аналоговый приемник 84, позволяет устранить такую энергию паразитного сигнала постоянной составляющей при обработке I и Q сигналов базовой полосы.

В режиме МДКР составляющие синфазного и квадратурного каналов сигнала МДКР в базовой полосе подаются посредством выходных линий 88 и 90 на АЦП 92 интерфейса приемника для режимов МДКР и ЧМ. Затем составляющие сигнала МДКР базовой полосы передаются с АЦП 92 на схему обработки 94 МДКР сигналов. В схеме обработки 94 МДКР сигналов составляющие сигнала МДКР базовой полосы демодулируются, разделяются и декодируются, например, rак описано в патенте США N 5103459.

В режиме цифровой ЧМ синфазный и квадратурный сигналы базовой полосы подаются на АЦП 92 по выходным линиям 88 и 90 приемника. В АЦП 92 синфазный и квадратурный сигналы базовой полосы оцифровываются со скоростью следования выборок, например, 40 квыб./с для формирования 8-битовых синфазной и квадратурной выборок. Полученные 8-битовые синфазные и квадратурные выборки подаются со скоростью, например? 40 квыб./с на демодулятор 96 I/Q выборок ЧМ сигнала. В демодуляторе цифрового ЧМ сигнала синфазный и квадратурный сигналы базовой полосы демодулируются с получением сигнала фазы и затем преобразуются в демодулированный по частоте сигнал. Как описано более подробно ниже, демодулятор цифрового ЧМ сигнала 96 также содержит цепь слежения за смещением постоянной составляющей, предназначенную для исключения смещения постоянной составляющей, введенной при радиочастотной обработке в приемнике 84, цепь АРУ и цепь слежения за частотой.

Как показано на фиг. 1, в режиме цифровой ЧМ демодулированный по частоте сигнал подается со скоростью, например, 40 квыб./с как на фильтр децимации 102 аудиосигнала, так и на схему восстановления широкополосных данных 104. После обработки фильтром децимации 102 аудиосигнал, дискретизированный с понижением частоты выборок, подается на вокодер (не показан) для восстановления принятой аудиоинформации. Одновременно с этим схема восстановления широкополосных данных 104 обеспечивает выделение принятых широкополосных данных и информации синхронизации из демодулированного по частоте сигнала. Эта выделенная информация широкополосного сигнала затем используется декодером сообщений широкополосных данных 108 для идентификации кадров кодовых слов широкополосных данных, коррекции ошибок по битам и для направления идентифицированных кодовых слов и сообщений в процессор управления для дальнейшей оценки.

3. Детальное описание двухрежимного передатчика

A. Интерполяционный фильтр аудиосигнала

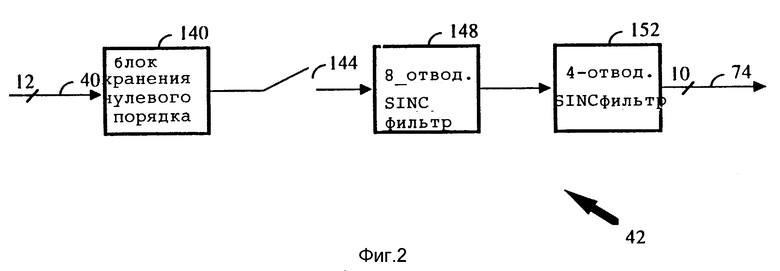

На фиг. 2 представлена блок-схема интерполяционного фильтра 42 аудиосигнала. Как показано на фиг. 2, каждая 12-битовая выборка аудиоданных с процессора 20 цифрового сигнала передается со скоростью 20 квыб./с по линии 18 на регистр хранения 140 нулевого порядка в составе интерполяционного фильтра 42 аудиосигнала. Выходной сигнал регистра хранения 140 нулевого порядка дискретизируется с помощью интерполяционного переключателя 44 с частотой, эквивалентной предварительно определенному целому кратному скорости входных данных. В предпочтительном варианте переключатель 144 имеет частоту переключения 120 кГц, т.е. соответствует шестикратной скорости входных данных. Полученные в результате аудиоданные, дискретизированные со скоростью 120 кб/с, затем последовательно обрабатываются SINC фильтром 148 с 8 отводами и SINC фильтром 152 с 4 отводами. Фильтры 148 и 152 могут характеризоваться следующими функциями преобразования T8 и T4 в z-области:

T8=(1+ z-1 + ... + z-7)/8;

T4=(1+ z-l = ... = z-3)/4,

Фильтр 152 с 4 отводами обеспечивает поток со скоростью 120 кб/с дискретизированных аудиоданных 44, причем каждая выборка аудиоданных 44 состоит из 10 бит.

В. Генератор сигнала широкополосных данных

В предпочтительном варианте генератор 54 сигнала широкополосных данных обеспечивает прямое синтезирование модулирующего сигнала с частотной манипуляцией (ЧМн) из двоичных данных 21 сообщений. Если данные сообщения 21 состоят из последовательности двоичных данных без возврата к нулю (БВД), то генератор 54 осуществляет как кодирование манчестерским кодом последовательность БВД данных, так и синтезирует модулирующий сигнал с ЧМн. Каждая логическая единица БВД данных кодируется манчестерским кодом в последовательность нуль-один, а каждый логический нуль БВД данных кодируется манчестерским кодом в последовательность один-нуль. Для ограничения спектральной ширины полосы полученного в результате сигнала, модулированного с использованием ЧМн, идеализированные переходы манчестерской последовательности синтезируются как синусоподобные переходы. Генератор широкополосных данных предпочтительно проектируется для исключения необходимости в низкочастотной фильтрации сигнала модуляции широкополосных данных перед частотной модуляцией несущей.

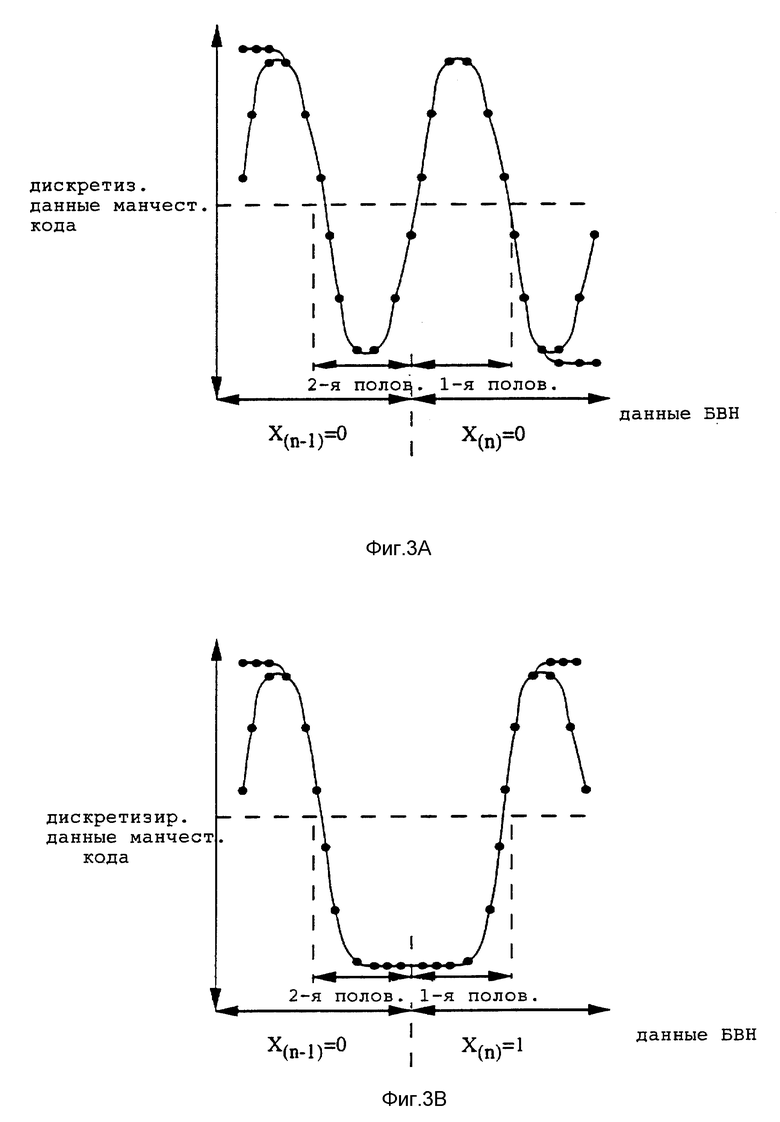

На фиг. ЗА - 3D представлен набор дискретизированных широкополосных сигналов, формируемых генератором 54 в ответ на различные пары битов БВН данных. Первый бит в каждой паре битов ВБД данных идентифицируется на горизонтальной оси на фиг. ЗА - 3D записью X(n-1), а второй бит идентифицируется записью X(n). Как показано на фиг. 3A - 3D, двенадцать выборок формируются в ответ на каждый бит БВН данных для формирования синусоидального представления, соответственно каждому биту манчестерских данных. На каждом из чертежей 3A - 3D изображены 12 точек, соответствующих последним шести выборкам манчестерских данных для БВН бита X(n-1) и первым шести выборкам манчестерских данных для БВН бита X(n). Синтезированные значения сигнала определены посредством предварительно определенных констант +/- s0, s1, s2 и s3. Информация, проиллюстрированная на графиках на фиг. 3A - 3D, представлена в табличной форме на фиг. 3E.

На фиг. 4 представлена блок-схема предпочтительного варианта выполнения генератора 54 широкополосных данных. В примере по фиг.4 входные двоичные БВН данные подаются со скоростью, например, 10 кб/с, а дискретизированное манчестерское представление формируется со скоростью 120 квыб./с с разрешением выборок, равным 10 бит. Генератор 54 содержит регистр 160 БВН данных для запоминания последовательных пар двоичных БВН данных X(n-1), X(n). Входной мультиплексор 164 генерирует последовательность, состоящую из значений s0, s1, s2 и/или s3, основываясь на значениях X(n-1) и X(n), хранящихся в регистре 160. Например, на фиг. 3E показано, что для X(n-1) = 0 и X(n) = 1 мультиплексор 164 будет генерировать последовательность s0, s1, s2, s3, s3, s3, за которой будет следовать последовательность s3, s3, s3, s2, s1, s0. Эти последовательности и обратные значения этих последовательностей, формируемые инвертором 168, подаются затем на выходной мультиплексор 172. Для взятого для примера случая X(n-1) = 0 и X(n) = 1 выходной мультиплексор 172 формирует последовательность -s0, -s1, -s2, -s3, -s3, -s3 соответственно второй половине X(n-1) = 0 и последовательность -s3, -s3, -s3, -s2, -s1, -s0 соответственно первой половине X(n) = 1. В общем случае выходной мультиплексор 172 осуществляет выбор между последовательностью, формируемой входным мультиплексором 164, и дополняющей последовательностью, формируемой инвертором 168, для генерирования дискретизированного сигнала, связанного с парой ВБН значений X(n) и X(n-1), запомненной в данный момент в регистре 160.

C. Блок суммирования и регулировки усиления

На фиг. 5 представлена блок-схема блока суммирования и регулировки усиления 48. Блок 48 включает в себя цифровой сумматор 178 для объединения дискретизированных аудиоданных 44 с дискретизированным сигналом широкополосных данных 50 (фиг. 4). Результирующий 10-битовый дискретизированный сигнал частотной модуляции затем масштабируется с помощью умножителя 180 с использованием 6-битовой константы GADJ регулировки усиления. Константа GADJ выбрана так, чтобы обеспечивать компенсацию любых отклонений от желательного отклика, характеризующего собой зависимость напряжения от частоты, управляемого напряжением генератора (не показан) в радиочастотном передатчике 64. Сигнал 58 цифровой частотной модуляции с отрегулированным коэффициентом усиления с выхода умножителя 180 подается затем на мультиплексор 60 режимов МДКР и ЧМ.

D. Цифроаналоговые преобразователи интерфейса для режимов МДКР и ЧМ

На фиг. 6 представлена блок-схема мультиплексора 60 режимов МДКР и ЧМ. Как показано на фиг. 6, мультиплексор данных 190 получает как данные режима МДКР, так и сигнал 58 цифровой частотной модуляции. Соответствующий поток данных мультиплексируется и передается на ЦАП 192 для преобразования в аналоговый сигнал перед подачей на радиочастотный передатчик 64 (фиг. 1). Выбор из цифрового входного потока для передачи на выход осуществляется при управлении с помощью сигнала выбора режима ЧМ/МДКР, поступающего на мультиплексор 190. Аналогичным образом либо тактовый сигнал для режима МДКР, либо тактовый сигнал для цифрового сигнала ЧМ подается на ЦАП 192 для осуществления синхронизации процедуры преобразования данных с хронированием входной последовательности данных (ЧМ или МДКР).

4. Детальное описание двухрежимного приемника

A. Демодулятор цифрового ЧМ сигнала базовой полосы

1. Общие характеристики

В соответствии с фиг. 1, при работе в режиме ЧМ 8-битовые синфазные и квадратурные выборки выдаются с АЦП 92 интерфейса приема для режимов МДКР/ЧМ со скоростью 40 квыб./с на демодулятор 96 синфазной и квадратурной составляющих ЧМ сигнала. Блок-схема предпочтительного варианта осуществления демодулятора 96 синфазной и квадратурной составляющих ЧМ сигнала показана на фиг. 7. Синфазные и квадратурные выборки соответственно представляют действительную и мнимую части комплексного векторного представления широкополосного эквивалента принятого ЧМ сигнала. В рассматриваемом примере осуществления широкополосный эквивалентный сигнал переносится на частоту в базовой полосе, смещенную относительно нулевой частоты (т.е. 0 Гц) на предварительно определенную величину. Как отмечено выше, аналоговый приемник 84 обеспечивает отображение этих принимаемых сигналов, которые смещены относительно центральной частоты радиочастотного сигнала на предварительно определенную величину, например 150 Гц, на нулевую частоту. Такая величина смещения по постоянному току позволяет осуществить различение между немодулированным ЧМ сигналом, т. е. непрерывным сигналом, и ошибками смещения по постоянному току, введенными при аналоговой обработке. В соответствии с одним из аспектов изобретения ошибки смещения по постоянному току сохраняются на нулевой частоте, в то время как перенесенный по частоте сигнал постоянной составляющей отображается на ненулевую частоту базовой полосы, эквивалентную предварительно определенной величине смещения по частоте (например, 150 Гц). Как описано ниже со ссылками на фиг. 8, блоки 210 и 212 цепей коррекции смещения по постоянному току синфазного (I) и квадратурного (Q) каналов предназначены для устранения этого смещения по постоянному току в канале приема сигнала до последующей его обработки демодулятором 96 синфазной и квадратурной составляющих. Цепи коррекции смещения по постоянному току 210 и 212 обеспечивают эффективное устранение ошибок смещения по постоянному току без внесения искажений в информацию, содержащуюся в сигнале постоянной составляющей.

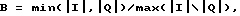

Демодулятор 96 ЧМ сигнала, кроме того, содержит генератор 214 синфазного и квадратурного значения фазы, предназначенный для формирования оценки фазового угла вектора принимаемого ЧМ сигнала. Функция, реализуемая генератором 214 синфазного и квадратурного значения фазы, может быть представлена следующим образом:

P(n)=arctan{I(n)/Q(n)},

где P(n) обозначает фазовый угол, относящийся к выборке вектора ЧМ сигнала, определяемый составляющими I(n) и Q(n). Пример определения функции арктангенса в четырех квадрантах, позволяющего оценить фазовый угол P(n), может быть представлен следующим образом:

(i) вычислить

(ii) определить оценку фазы Pe в пределах от 0 до π/4, где Pe(n) = TAN-1(B),

(iii) отобразить оценку фазы Pe в диапазон от -π до π, основываясь на относительных величинах модулей  и знаках I и Q.

и знаках I и Q.

Вышеуказанное определяет возможный способ выполнения вычисления арктангенса в четырех квадрантах. Ясно, что специалистами в данной области техники могут быть использованы и другие варианты указанного алгоритма.

Последовательность оценок фазы с генератора 214 синфазных и квадратурных значений фазы преобразуются в сигнал частоты с помощью генератора 218 преобразования фазы в частоту. В рассматриваемом варианте осуществления на вход генератора 218 преобразования фазы в частоту подается 8-битовый нормированный сигнал фазы P(n), где 0 < P(n) < 2. Функция дифференцирования, выполняемая генератором 218 преобразования фазы в частоту, может быть математически представлена следующим образом:

F(n)=P(n) - P(n-1),

где F(n) - выборка частоты, полученная из нормированных выборок фазы P(n) и P(n-1). В предпочтительном примере осуществления выборки частоты F(n) нормируются относительно последовательности выборок FN(n) так, что -1 < FN(n) < 1. Генератор 214 синфазного и квадратурного значений фазы и генератор 218 преобразования фазы в частоту описаны ниже более детально со ссылками на фиг. 10 и 11.

Как показано на фиг. 7, блок определения уровня принятого сигнала 220 вычисляет оценку уровня принятого сигнала, основываясь на параметрах  которые обеспечиваются генератором 214 синфазного и квадратурного значений фазы. Полученный в результате сигнал индикации уровня принятого сигнала используется в цифровой схеме АРУ 222 для формирования цифрового сигнала АРУ, который затем преобразуется в аналоговый сигнал АРУ с помощью ЦАП 224.

которые обеспечиваются генератором 214 синфазного и квадратурного значений фазы. Полученный в результате сигнал индикации уровня принятого сигнала используется в цифровой схеме АРУ 222 для формирования цифрового сигнала АРУ, который затем преобразуется в аналоговый сигнал АРУ с помощью ЦАП 224.

Как показано на фиг. 7, фильтр 250 цепи слежения за частотой принимает выборки частоты FN(n), формируемые генератором 218 преобразования фазы в частоту. Фильтр 250 цепи слежения за частотой генерирует цифровой сигнал, который преобразуется в аналоговый сигнал слежения за частотой (FTRAK) с помощью ЦАП 251. Сигнал FTRACK используется аналоговым приемником для подстройки частоты сигнала гетеродина, используемого при понижающем преобразовании принятого радиочастотного сигнала. Как отмечено выше, энергия ЧМ сигнала синфазного и квадратурного каналов часто переносится в аналоговом приемнике 84 на частоту базовой полосы, отличную от 0 Гц, для того чтобы облегчить исключение ошибок смещения по постоянному току. Соответственно, в фильтре 250 цепи слежения за частотой предусмотрено предварительно определенное постоянное смещение частоты (FBIAS), вычитаемое из обрабатываемых выборок частоты FN(n) для обеспечения компенсации смещения в базовой полосе, вводимого в аналоговом приемнике 84.

2. Описание работы демодулятора ЧМ сигнала

На фиг. 8 представлена блок-схема фильтра цепи коррекции смещения по постоянному току 210 синфазного (I) канала. Ясно, что фильтр цепи коррекции смещения по постоянному току 212 квадратурного (Q) канала идентичен фильтру 210. Как показано на фиг. 8, сигнал коррекции смещения 260 синфазного канала, формируемый фильтром цепи коррекции 210, подается на блок вычитания 262 в тракте синфазного канала базовой полосы. Фильтр цепи коррекции 210 выполнен таким образом, что сигнал коррекции смещения 260 синфазного канала аппроксимирует любое паразитное смещение по постоянному току, присутствующее в тракте синфазного канала. Таким путем скомпенсированный сигнал, формируемый блоком вычитания 262, по существу становится свободным от ошибок смещения по постоянному току.

В процессе функционирования оцифрованный сигнал синфазного канала с выхода АП 266 в составе приемника 84 дискретизируется и фильтруется в фильтре цепи дискретизации 270. Полученный в результате цифровой сигнал коррекции синфазного канала затем преобразуется в аналоговый сигнал коррекции 260 синфазного канала с помощью ЦАП 272 и подается на блок вычитания 262.

На фиг. 9A представлен предпочтительный вариант осуществления фильтра цепи дискретизации 270. Фильтр 270 содержит регистр 276 выделения старшего разряда для подачи старшего разряда, т.е. знакового бита 8-разрядного выходного сигнала АЦП на регистр сдвига 278. Постоянная времени фильтра цепи коррекции смещения по постоянному току 210 синфазного канала может управляться посредством подстройки числа битов сдвига 280, которые вместе с сигналом смещения 282, дополняющим до двух, подаются на регистр сдвига 278 с помощью процессора управления приемника, 11-битовый выходной сигнал регистра сдвига 278 подается на накопитель 286, который формирует 21-битовый накопленный выходной сигнал, расширенный за счет знака, на 9-битовую схему выделения старшего разряда 290. Схема выделения 290 передает девять старших разрядов 21-битового накопленного цифрового сигнала коррекции смещения на ЦАП 272 (фиг. 8), который формирует аналоговый сигнал коррекции 260 синфазного канала.

Более конкретно, в таблице, представленной на фиг. 9B, иллюстрируется способ, которым сдвиги разрядов, выполненные в регистре сдвига 278, устанавливают постоянную времени цепи коррекции смещения по постоянному току. Как показано на фиг. 9B, цепь коррекции смещения по постоянному току обеспечивает работу как в режиме слежения, так и режиме захвата. Работа в режиме захвата характеризуется более короткими постоянными времени цепи, что обеспечивает быструю первоначальную сходимость коррекции смещения. Относительно короткие постоянные времени цепи, используемые в режиме захвата, увеличивают ширину полосы цепи относительно ширины полосы в режиме слежения, что приводит к возникновению больших ошибок смещения в режиме захвата, чем в режиме слежения. И наоборот, более длительные постоянные времени цепи и, следовательно, более узкие значения ширины полосы используются в режиме слежения, чтобы минимизировать ошибки смещения в установившемся состоянии. Такое двухрежимное функционирование обеспечивает возможность достижения начальной сходимости с минимальной задержкой и одновременно позволяет оптимизировать характеристики в установившемся состоянии.

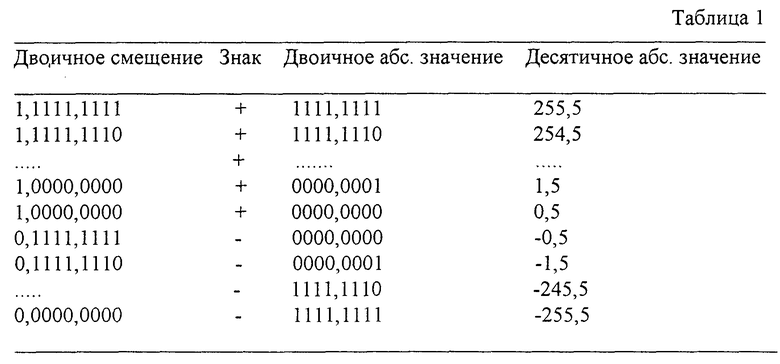

На фиг. 10 представлена блок-схема генератора 214 синфазного и квадратурного значений фазы. Генератор 214 содержит схемы двоичного преобразования 296 и 298 синфазного и квадратурного каналов для определения знака и величины данных базовой полосы для синфазного и квадратурного каналов. В предпочтительном варианте осуществления эти данные представляются схемам двоичного преобразования 296 и 298 синфазного и квадратурного каналов в двоичной форме со смещением.

Для данных базовой полосы в двоичном формате со смещением схемы преобразования 296 и 298 выполняют функцию, представленную в Таблице 1. А именно, если старший разряд входной выборки данных базовой полосы представляет собой логическую единицу, то абсолютное значение (т.е.  или

или  ) выборки эквивалентно восьми младшим разрядам выборки, в противном случае абсолютное значение получается путем инвертирования восьми младших разрядов. Схемы преобразования также формируют знаковые значения I± и Q± соответственно, указывая знаки текущих выборок данных базовой полосы синфазного и квадратурного каналов.

) выборки эквивалентно восьми младшим разрядам выборки, в противном случае абсолютное значение получается путем инвертирования восьми младших разрядов. Схемы преобразования также формируют знаковые значения I± и Q± соответственно, указывая знаки текущих выборок данных базовой полосы синфазного и квадратурного каналов.

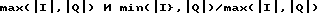

Как показано на фиг. 10, цифровой компаратор 302 сравнивает значения  и подает min

и подает min соответственно на цифровой делитель 306 по сигнальным линиям 308 и 310. Компаратор 302 также формирует сигнал управления CI/Q. Если

соответственно на цифровой делитель 306 по сигнальным линиям 308 и 310. Компаратор 302 также формирует сигнал управления CI/Q. Если  то сигнал управления CI/Q устанавливается на 1. В противном случае сигнал управления CI/Q устанавливается на 0.

то сигнал управления CI/Q устанавливается на 1. В противном случае сигнал управления CI/Q устанавливается на 0.

Делитель 306 формирует 6-битовый сигнал RATIO (отношение), определяемый как  Сигнал RATIO подается в таблицу ARCTAN ROM (ПЗУ функции арктангенс) и служит в качестве указателя для таблицы 316. Более конкретно, функция THETA = arctan (RATIO) запоминается в таблице 316. Указатель RATIO находится в пределах от 0 до 63 в соответствии с десятичным диапазоном от 0 до 1, а вычисленные значения THETA находятся в диапазоне от 0 до 31 соответственно десятичному диапазону от 0 до π/4 В рассматриваемом примере таблица 316 ARCTAN ROM содержит набор из 64 5-битовых оценок фазы, как представлено в таблице 2.

Сигнал RATIO подается в таблицу ARCTAN ROM (ПЗУ функции арктангенс) и служит в качестве указателя для таблицы 316. Более конкретно, функция THETA = arctan (RATIO) запоминается в таблице 316. Указатель RATIO находится в пределах от 0 до 63 в соответствии с десятичным диапазоном от 0 до 1, а вычисленные значения THETA находятся в диапазоне от 0 до 31 соответственно десятичному диапазону от 0 до π/4 В рассматриваемом примере таблица 316 ARCTAN ROM содержит набор из 64 5-битовых оценок фазы, как представлено в таблице 2.

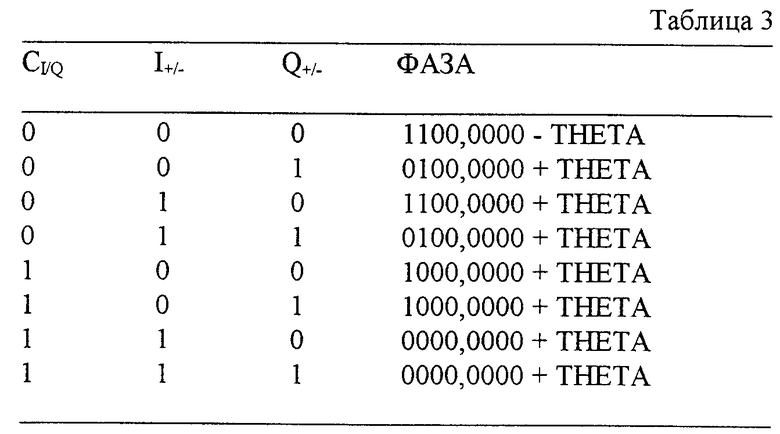

Как показано в таблице 2, в таблице 316 ARCTAN ROM хранятся только "основные значения" фазовой информации. Т.е. в целях экономии области памяти таблица ARCTAN ROM включает только значения 1/8 плоскости полярных координат, т. е. от нуля до π/4. Соответственно, модуль определения октанта 320 обеспечивает формирование выходной последовательности P(n) значений фазы путем поворота значения THETA, полученного из таблицы 316 ARCTAN ROM, до нужного октанта. Процедура определения октанта выполняется с использованием соотношений 1 > 0, Q > 0,  т.е. с использованием значений I+/-, Q+/-, CI/Q. В таблице 3 представлены четыре результата определения значения фазы, выполненные блоком определения октанта 320, по отношению к значениям THETA, связанным с соответствующими комбинациями I+/-, Q+/-, CI/Q.

т.е. с использованием значений I+/-, Q+/-, CI/Q. В таблице 3 представлены четыре результата определения значения фазы, выполненные блоком определения октанта 320, по отношению к значениям THETA, связанным с соответствующими комбинациями I+/-, Q+/-, CI/Q.

Логические операции, выполненные для вычисления значений фазы, приведенных в таблице 3, могут быть эквивалентным образом выражены в следующем виде:

ФАЗА [7] = Q+/-;

ФАЗА [6] = I+/- ИСКЛЮЧАЮЩЕЕ ИЛИ Q+/-;

ФАЗА [5] = CI/Q ИСКЛЮЧАЮЩЕЕ ИЛИ I+/- ИСКЛЮЧАЮЩЕЕ ИЛИ Q+/-;

ФАЗА [4...] = CI/Q ИСКЛЮЧАЮЩЕЕ ИЛИ I+/- ИСКЛЮЧАЮЩЕЕ ИЛИ Q+/- ИСКЛЮЧАЮЩЕЕ ИЛИ THETA [4...],

где ФАЗА [i] указывает i-ый бит 8-битового значения без знака, причем бит 0 соответствует младшему разряду.

На фиг. 11 представлена блок-схема предпочтительного варианта осуществления генератора 218 преобразования фазы в частоту. Генератор 218 предназначен для преобразования последовательности значений фазы P(n), сформированной генератором фазы I/Q 214 в нормированную последовательность значений частоты FN(n). И вновь, функция дифференцирования, выполняемая регистром сдвига 330 и цифровым сумматором 332 в генераторе 218 преобразования фазы в частоту может быть математически представлена в виде F(n) = P(n) - P(n-1). Модуль определения диапазона 334 предназначен для нормирования последовательности выборок F(n) к последовательности FN(n) так, что -1 < PN(n) < 1. В рассматриваемом примере это уточнение диапазона вычисляется по модулю 2. Например, уточнение диапазона P(n) = 1,1 по модулю 2 приводит к отображению этой величины в нормированное значение частоты FN(n) = - 0,9. Такая арифметика суммирования по модулю 2 устраняет любую неоднозначность в расчете разности фаз, вытекающую из циклов фазы, "накручиваемых" вокруг единичного круга. Частотные выборки затем обрабатываются с помощью фильтра децимации аудиосигнала 102 и схемы восстановления 104 широкополосных данных, как будет описано ниже.

На фиг. 12A представлена блок-схема цифровой цепи АРУ, обеспечивающей регулировку усиления сигнала ПЧ, генерируемого приемником 84. Цифровая цепь АРУ включает блок индикации уровня принятого сигнала 220, схему цифровой АРУ 222 и ЦАП 224. При функционировании цепи АРУ сигналы, индицирующие уровень принятого сигнала, формируются блоком индикации уровня принятых сигналов 220 на основе значений  формируемых демодулятором I/Q 96. Как показано на фиг. 12A, в цепи АРУ предусмотрен цифровой блок вычитания 340 для вычитания опорного уровня AGE_REF из выходного сигнала индикации уровня принятого сигнала. Полученный сигнал ошибки интегрируется интегратором 342 в фильтре цепи и затем подается на ЦАП 224.

формируемых демодулятором I/Q 96. Как показано на фиг. 12A, в цепи АРУ предусмотрен цифровой блок вычитания 340 для вычитания опорного уровня AGE_REF из выходного сигнала индикации уровня принятого сигнала. Полученный сигнал ошибки интегрируется интегратором 342 в фильтре цепи и затем подается на ЦАП 224.

Аналоговый сигнал АРУ с ЦАП 224 фильтруется ФНЧ 346 в приемнике 84 и затем используется для регулировки усиления усилителя 350 в тракте сигнала ПЧ приемника. Усилитель 350 обеспечивает линейную (в дБ) регулировку усиления в широком динамическом диапазоне. Усилитель 350 может быть таким, как описано в патенте США N 5099204 на "Усилитель с линейной регулировкой усиления", переуступленном правопреемнику настоящего изобретения.

Ниже представлено обобщенное описание обработки в базовой полосе, выполняемой в приемнике 84. Более конкретно, регулируемый по уровню сигнал ПЧ с усилителя с АРУ 350 переносится на частоту базовой полосы с помощью смесителя 354. Как указано выше, частота сигнала гетеродина, подаваемого на смеситель 354, выбирается так, чтобы центральная ПЧ отображалась на частоту базовой полосы, смещенную от нуля Гц. Сигналы I и Q базовой полосы, формируемые смесителем 354, затем фильтруются и преобразуются в цифровую форму в блоке 358 ФНЧ и АЦП перед тем, как передавать их на интерфейс 92 режимов МДКР и ЧМ приемника.

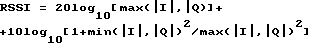

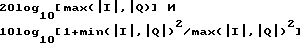

На фиг. 12B представлен предпочтительный вариант осуществления блока индикации уровня принимаемого сигнала 220. Блок индикации уровня 220 обеспечивает выполнение функции 10 log10(I2 + Q2). Эта функция может быть в альтернативном виде представлена следующим образом:

Значения  могут быть получены с генератора I/Q фазы 214, поскольку эти промежуточные результаты также требовалось определить в процессе демодулирования фазы. Вычисления

могут быть получены с генератора I/Q фазы 214, поскольку эти промежуточные результаты также требовалось определить в процессе демодулирования фазы. Вычисления  выполняются первым и вторым блоками 370 и 372 логарифмической функции, которые могут быть выполнены с использованием, например, просмотровых таблиц на ПЗУ программируемых логических матриц или обычных логических схем. Сигнал индикации уровня принимаемого сигнала затем получается путем объединения выходных сигналов блоков 370 и 372 логарифмической функции в цифровом сумматоре 374.

выполняются первым и вторым блоками 370 и 372 логарифмической функции, которые могут быть выполнены с использованием, например, просмотровых таблиц на ПЗУ программируемых логических матриц или обычных логических схем. Сигнал индикации уровня принимаемого сигнала затем получается путем объединения выходных сигналов блоков 370 и 372 логарифмической функции в цифровом сумматоре 374.

На фиг. 13A представлен предпочтительный вариант осуществления цифрового блока вычитания 340 и интегратора 342 цифровой схемы АРУ 222. Как показано на фиг. 13A, сигнал AGC_REF с регистра 344 подается на блок вычитания 340 вместе с сигналом индикации уровня (RSSI) со схемы индикации уровня принимаемого сигнала 220. В рассматриваемом примере осуществления параметр AGC_REF представляет собой 5-битовую константу, которая загружается в регистр 344 посредством процессора управления приемника. Как показано на фиг. 13A, 5-битовый сигнал AGC_ REF предварительно определенной константы с процессора управления подается вместе с 7-битовым сигналом RSSI с блока индикации уровня принимаемого сигнала 220 на блок вычитания 340. Получаемая разность (т. е. ошибка уровня сигнала) между оценкой сигнала RSSI и уровнем полезного сигнала (AGC_ REF) масштабируется схемой коэффициента усиления фильтра цепи 341. Усиление фильтра цепи определяется значением G = O a1a2 • 1SHIFT. В рассматриваемом варианте осуществления дробные компоненты (a1а2) содержат 2-битовые значения, а арифметический левый сдвиг, определенный параметром SHIFT, представляет собой 3-битовое значение. В качестве примера, для a1= 1, a2 = 1 и SHIFT= 3 эквивалентное усиление цепи равно 0,11 • 2-3 (в двоичном значении) или 3/32 (в десятичном значении).

Как показано на фиг. 13A, процедура дробного масштабирования реализуется как полное умножение, а процедура сдвига выполняется как арифметический левый сдвиг. Два предварительно определенных сигнала постоянного усиления цепи, соответственно определенные как AGC_Attack и AGC_Decay подаются на схему АРУ. Каждый из этих сигналов состоит из 2-битового сегмента, представляющего компоненты усиления a1 и a2, и 3-битового сегмента, представляющего параметр SHIFT. Знаковый бит сигнала ошибки уровня сигнала определяет масштабирование посредством сигналов AGC_ Attack и AGC_Decay. Если этот знаковый бит положителен (т. е. логический "0"), то ошибка масштабируется усилением, определяемым сигналом AGC_Decay. Для положительных ошибок уровня сигнала цепь АРУ будет снижать уровень сигнала путем снижения усиления усилителя с АРУ. В этом случае усиление цепи и, следовательно, соответствующая постоянная времени цепи определяются значением AGC_Decay. Аналогичным образом, в присутствии отрицательных ошибок уровня сигнала цепь АРУ обеспечивает увеличение уровня сигнала путем увеличения усиления усилителя с АРУ. При этих условиях усиление цепи и постоянные времени определяются значением AGC_Attack.

Выбор постоянных времени цепи осуществляется в соответствии с желательным балансом, который должен быть достигнут между способностью отслеживания уровня сигнала цепи АРУ и степенью, до которой уровень сигнала базовой полосы должен поддерживаться ограниченным в динамическом диапазоне ЦАП приемника с АРУ. На фиг. 13B представлены значения параметров, соответствующие взятому для примера множеству постоянных времени цепи.

В соответствии с фиг. 13A, масштабированная 8-битовая ошибка уровня сигнала подается на 14-битовый интегратор с насыщением 342. Кроме того, 6-битовые предварительно определенные верхний и нижний уровни насыщения (AGC_ Max, AGC_ Min) интегратора 342 подаются на схему АРУ посредством процессора управления приемника. Интегратор 342 обеспечивает сведение средней ошибки сигнала к нулю, что эквивалентно минимизации разности между средней оценкой уровня сигнала (RSSI) и желательным уровнем сигнала (AGC_REF). Предельные значения насыщения (AGC_Max, AGC_Min) в типовом случае выбираются как соответствующие верхнему и нижнему предельным значениям диапазона управляющего напряжения усилителя с АРУ. Семь старших битов выделяются из выходного сигнала интегратора 342 и подаются на ЦАП 224 (фиг. 12A), что вновь обеспечивает регулировку усиления усилителя с АРУ.

На фиг. 14A представлен предпочтительный вариант осуществления цепи слежения за частотой, входящей в состав двухрежимного приемника. Как показано на фиг. 14A, фильтр цепи слежения за частотой 250 включает в себя цифровой блок вычитания 390, на который подается 8-битовый сигнал демодулированной частоты с генератора 218 преобразования фазы в частоту. Блок вычитания 390 предназначен для вычитания сигнала смещения частоты (FBIAS), который в рассматриваемом варианте осуществления примерно эквивалентен одному младшему биту частоты (т.е. 156 Гц) из 8-битового сигнала демодулированной частоты. Результирующий разностный сигнал подается на регистр сдвига 392 и поразрядно сдвигается в соответствии с постоянной усиления цепи слежения за частотой FGAIN. В таблице 14B приведены постоянные времени цепи слежения за частотой, связанные с различными постоянными усиления FGAIN.

Выходной сигнал регистра сдвига 392, расширенный за счет знака, затем передается на цифровой накопитель 394. В рассматриваемом варианте осуществления выходной сигнал с регистра сдвига 392 имеет точность 15 бит, причем накопитель 394 имеет ширину 22 бита. Как показано на фиг. 14A, выходной сигнал накопителя 394 в виде 8 старших битов подается на ЦАП 251. Следует также иметь в виду, что при работе в режиме МДКР сигнал слежения за частотой МДКР может быть мультиплексирован на ЦАП 251 вместо выходного сигнала накопителя 394.

Сигнал слежения за частотой FTRACK, формируемый ЦАП 251, используется для подстройки частоты гетеродина 396, входящего в состав радиочастотного каскада приемника 84. Приемник 84 также содержит смеситель 398 для переноса частоты принятого радиочастотного сигнала в соответствии с приложенной частотой гетеродина 396. Полученный в результате сигнал ПЧ затем подается на каскад обработки на ПЧ 402, выходной сигнал которого дискретизируется АЦП 266 и подается на генератор I/Q фазы 214. Таким путем цепь слежения за частотой по фиг. 14A облегчает цифровое слежение в замкнутом контуре за несущей частотой принимаемого радиочастотного сигнала. Кроме того, цифровая реализация устройства, представленного на фиг. 14A, обеспечивает возможность программирования параметра FGAIN для обеспечения требуемого отклика цепи.

B. Фильтр децимации аудиосигнала

На фиг. 15 представлена блок-схема предпочтительного варианта осуществления фильтра децимации аудиосигнала 102. Фильтр децимации при своем функционировании преобразует сигнал демодулированной частоты с демодулятора I/Q фазы в сигнал с более низкой скоростью передачи данных. В рассматриваемом примере осуществления, 8-битовые данные со скоростью 40 квыб./с, формируемые демодулятором ЧМ сигнала, преобразуются фильтром 102 в 12-битовые данные со скоростью 12 квыб./с.

Выполнение фильтра, как показано на фиг. 15, основывается на использовании набора SINC фильтров (т.е. фильтров с характеристикой вида sinc (х) = sin(x)/х) для обеспечения эффективной реализации аппаратными средствами. В частности, фильтр 102 содержит входной SINC фильтр 412 с тремя отводами, каскадно соединенный с SINC3 фильтром 416 с двумя отводами. Выходной сигнал фильтра 416 суб-дискретизируется с помощью переключателя 418, например, с частотой 20 квыб./с. Фильтр 102 в типовом случае выполнен с возможностью обеспечения ослабления по меньшей мере 40 дБ в частотном диапазоне от 16 до 20 кГц. Такая степень ослабления может быть обеспечена за счет реализации SINC фильтров в соответствии со следующими функциями преобразования в z-области:

SINC фильтр - Передаточная функция

3-отводный SINC фильтр (412) - (1+z-1+z-2)/4

2-отводный SINC3 фильтр (416) - (1+z-1)(1+z-1)(1+z-1)/8

C. Синхронизация широкополосного сигнала и восстановление данных

На фиг. 16 представлен возможный вариант осуществления блока восстановления широкополосных данных 104. Блок восстановления широкополосных данных 104 предназначен для выполнения восстановления синхронизации и осуществления операций декодирования потока данных, кодированных с использованием манчестерского кода, принятого двухрежимным приемником 16. Блок 104 включает фильтр 430 приемника, который аппроксимирует согласованный фильтр для потока символов манчестерского кода. Кроме того, фильтр 430 приемника ограничивает по полосе демодулированный ЧМ сигнал и режектирует высокочастотный шум, сформированный в генераторе 218 преобразования фазы в частоту. В возможном варианте осуществления фильтр 430 приемника предназначен для эмулирования характеристик аналогового фильтра нижних частот Баттерворта четвертого порядка, имеющего частоту отсечки, примерно равную 13 кГц. Если демодулированный ЧМ сигнал формируется демодулятором I/Q фазы со скоростью 40 квыб./с, то фильтр 430 приемника может быть реализован как 2-отводный SINC фильтр (с нулем для скорости передачи 20 квыб./с), имеющий передаточную функцию z-преобразования вида (1+z-1)/2.

Как показано на фиг. 16, интерполяционный фильтр 432 предусмотрен для увеличения частоты дискретизации отфильтрованного сигнала, формируемого фильтром 430 приемника, для достижения разрешения выборок, соответствующего обработке, осуществляемой блоками восстановления синхронизации и декодирования данных, кодированных манчестерским кодом, 433 и 434 соответственно. Интерполяционный фильтр 432 более детально представлен на фиг. 17. Он содержит схему хранения нулевого порядка 436, предназначенную для приема потока выборок со скоростью 40 квыб./с с фильтра 430 приемника. Переключатель 438 обеспечивает дополнительную дискретизацию выходного сигнала схемы хранения нулевого порядка 436, например, с частотой 320 квыб./с для обеспечения требуемого разрешения по времени для восстановления синхронизации и детектирования потока символов, кодированных манчестерским кодом, со скоростью 20 кб/с. Полученный в результате дискретизированный поток со скоростью 320 квыб. /с фильтруется 8-отводным SINC фильтром 440 с передаточной функцией (1 + z-1 +...+ z-7)/8. Полученная в результате линейно интерполированная последовательность y(n), сформированная 8-отводным SINC фильтром 440 в ответ на последовательность x(n), формируемую фильтром 430, может быть представлена в следующем виде:

y(8n + k) = x(n), для k=0 и

y(8n + k) = y(8n + k - 1) + (x(n) - x(n-1))/8 для k = 1, ...7.

На фиг. 18A представлен вариант осуществления блока восстановления синхронизации и блока декодирования манчестерского кода 433 и 434. В рассматриваемом варианте осуществления блок декодирования манчестерского кода 434 реализован с использованием цифровой фазоследящей цепи 1-го порядка, синхронизация в которой управляется пересечениями нуля 460, формируемыми блоком восстановления синхронизации 433. Как показано на фиг. 18A, блок восстановления синхронизации 433 включает в себя схему пороговой обработки данных 464 для подачи битов данных 470, прошедших пороговую обработку при скорости интерполяции 320 квыб. /с, на схему пересечений нуля 472. Биты данных 470, прошедших пороговую обработку, формируются на основе знака входной последовательности выборок. Более конкретно, каждое пересечение нуля 460 формируется в схеме пересечений нуля 472 путем обработки по схеме ИСКЛЮЧАЮЩЕЕ ИЛИ последовательных битов данных 470, прошедших пороговую обработку.

Цифровая фазоследящая цепь блока декодирования манчестерского кода 434 предназначена для обеспечения синхронизации с взятой для примера скоростью передачи символов манчестерского кода 20 квыб./с. Блок декодирования 434 содержит фазовый детектор 480 для определения пересечения нуля дискретизированными значениями фазы, обеспечивающий дискретизацию выходного сигнала накопителя фазы 484 после генерирования каждого пересечения нуля 460. В предпочтительном варианте осуществления фазовый детектор 480 формирует 3-битовый сигнал ошибки, выделенный из 3 старших битов накопителя фазы, к которому добавляется смещение 1/2 младшего бита для формирования несмещенной 4-битовой оценки ошибки фазы. Каждая продетектированная выборка фазы, формируемая с помощью фазового детектора 480, поразрядно сдвигается в регистре масштабирования усиления цепи 490 в соответствии с командой сдвига усиления цепи (LSHIFT) с процессора управления приемника. Величина такого поразрядного сдвига, выполняемого в регистре масштабирования 490, определяет постоянную времени и, следовательно, ширину полосы цифровой фазоследящей цепи в блоке 434. Постоянные времени и значения ширины полосы, связанные с взятым для примера набором значений LSHIFT, представлены на фиг. 18B.

Как показано на фиг. 18B, в предпочтительном варианте значения LSHIFT находятся в диапазоне от 5 до 8, что соответствует диапазону значений ширины полосы от 80 Гц до 10 Гц.

Как показано на фиг. 18A, накопитель фазы 484 обновляется идентичными приращениями фазы, например, с частотой 320 Гц. В рассматриваемом примере осуществления каждое фиксированное приращение фазы выбирается равным 1/8, что приводит в результате к изменению значения накопителя 484 от -1 до +1 на каждый символ манчестерского кода 16 тактовых циклов с частотой 320 кГц. Накопитель фазы 484 в общем случае реализуется с циклическим возвратом при переполнении от +/-1.

В процессе функционирования цифровая фазоследящая цепь по фиг. 18A синхронизируется по фазе так, что пересечения нуля 460 входного сигнала совпадают с пересечениями нуля выходного сигнала +/-1 накопителя фазы 484. Хотя это в принципе приводит к средней ошибке дискретизированной фазы, равной нулю на выходе фазового детектора 480, однако различные факторы (например, разрешение времени квантования, шумы сигнала) обеспечивают непрерывную работу фазоследящей цепи, обуславливая ненулевую ошибку дискретизированной фазы. В качестве конкретного примера рассмотрим случай, когда переходы сигнала +/-1 с накопителя фазы 484 являются "опережающими" пересечениями нуля 460 входного сигнала. В этом случае результирующий положительный сигнал ошибки вычитается из следующего значения 1/8 приращения фазы, подаваемого на блок вычитания 498, тем самым снижая опережение фазы с выхода накопителя фазы 484 относительно входных пересечений нуля 460.

В соответствии с фиг. 18A, восстановленный тактовый сигнал 502 манчестерского кода может быть получен из знака ошибки фазы, накопленной накопителем 484. В процессе фазовой синхронизации положительные переходы восстановленного тактового сигнала 502 манчестерского кода соответствуют межсимвольным переходам восстановленным данным манчестерского кода 504, формируемым регистром-защелкой 506. Более конкретно, данные манчестерского кода 504 формируются путем фиксации (506) сигнала 470, прошедшего пороговую обработку, по заднему фронту восстановленного тактового сигнала 502 манчестерского кода.

На фиг. 19A представлен декодер БВН 520, входящий в состав блока 104 восстановления широкополосных данных. Как показано на фиг. 19A, данные манчестерского кода 504 с блока 104 переносятся через входные регистры сдвига 524 и 526, из которых выводятся последовательные пары символов манчестерского кода по сигнальным линиям 528 и 530. Каждая пара манчестерских символов подается на мультиплексор 534 и на первую логическую схему ИСКЛЮЧАЮЩЕЕ ИЛИ 536. Символы манчестерского кода также подаются на вторую логическую схему ИСКЛЮЧАЮЩЕЕ ИЛИ 542 и, кроме того, проходят через входной регистр сдвига 540. Как показано на фиг. 19A, выходной сигнал регистра 540 также подается на вторую логическую схему ИСКЛЮЧАЮЩЕЕ ИЛИ 542.

В предпочтительном варианте осуществления декодер БВН 520 содержит фильтр "случайного блуждания" (ФСБ) 550, предназначенный для восстановления данных БВН и фазы тактового сигнала в соответствии с выходными сигналами логических схем ИСКЛЮЧАЮЩЕЕ ИЛИ 536 и 542. Декодер БВН 520 также получает тактовый сигнал 554 битов БВН, который формируется путем пропускания восстановленного тактового сигнала 502 манчестерского кода через схему деления на два 556. Однако непосредственное преобразование манчестерского кода в данные БВН не может быть выполнено только на базе информации синхронизации, присущей тактовому сигналу 554 битов БВН, поскольку имеет место фазовая неоднозначность в 180o между тактовым сигналом манчестерского кода 502 и тактовым сигналом 554 битов БВН. В соответствии с изобретением эта фазовая неоднозначность разрешается с помощью ФСБ 550, использующего конкретное свойство обнаружения ошибок, присущее восстановленным данным 504 манчестерского кода. А именно, характерным свойством потока данных манчестерского кода является то, что логическая операция ИСКЛЮЧАЮЩЕЕ ИЛИ, осуществляемая над последовательными символами манчестерского кода, всегда дает единицу.

В соответствии с фиг. 19A каждая последовательная пара символов 528 и 530 манчестерского кода соответствует паре возможных декодированных значений данных БВН. ФСБ 550 обеспечивает выбор одного из этих значений БВН посредством мультиплексора 534 посредством обработки восстановленных данных манчестерского кода для определения наиболее вероятной фазы выборки БВН. Более конкретно, логическая схема БВН 560 в ФСБ 550 получает выходные сигналы с логических схем ИСКЛЮЧАЮЩЕЕ ИЛИ 542 и 536, которые далее упоминаются как индикаторы действительности фазы Фаза 1 (P1) и Фаза 2 (P2). Эти индикаторы действенности фазы P и P2 идентифицированы двумя возможными битами 530 и 528 данных БВН соответственно, поданными на мультиплексор 534. В момент нарастающего фронта восстановленного тактового сигнала БВН 554 накопитель 562 в ФСБ 440 получает значение с приращением, полученным от логической схемы БВН 560.

В предпочтительном варианте значение приращения равно либо 0, либо +/-1 и формируется логической схемой БВН 560 путем анализа индикаторов P1 и P2 действительности фазы в соответствии со свойством обнаружения ошибок, присущим манчестерскому коду, как упомянуто выше. Следует отметить, что для любых данных трех последовательных символов манчестерского кода P1 формируется путем обработки в соответствии с логической операцией ИСКЛЮЧАЮЩЕЕ ИЛИ первого и второго символов, а P2 формируется путем обработки в соответствии с логической операцией ИСКЛЮЧАЮЩЕЕ ИЛИ второго и третьего символов. Индикаторы P1 и P2 действительности фазы "корректны", если установлены равными 1, поскольку это удовлетворяет ограничению обнаружения ошибок для манчестерского кода, в соответствии с которым операция ИСКЛЮЧАЮЩЕЮ ИЛИ, производимая над последовательными символами, дает единицу. Если значение P1 корректно, а значение P2 некорректно, то накопитель 562 получает приращение. В противном случае (т. е. если P1 = 0 и P2 = 1) накопитель 562 получает отрицательное приращение. Если P1 и P2 имеют одно и то же значение, то накопитель не получает ни положительного, ни отрицательного приращения. На фиг. 19B представлена таблица, в которой приведена логика работы логической схемы БВН 560.

В рассматриваемом примере осуществления накопитель 562 имеет длину 6 битов и, следовательно, переходит в насыщение при -31 или +32. Корректный символ БВН выбирается мультиплексором 534 на основании знака значения, хранящегося в накопителе 562. В частности, положительное накопленное значение приводит к появлению символа манчестерского кода в сигнальной линии 530, подаваемого на выходной регистр 566, в то же время мультиплексор 534 пропускает символ манчестерского кода из линии 528 в регистр 566 в ответ на отрицательное накопленное значение.

Декодер БВН 520 выполнен с возможностью его самосинхронизации. Т.е. декодер 520 не требует инициализации после начала работы системы. Кроме того, наихудший случай "блуждания" до достижения корректной фазы БВН соответствует 32 для реализаций ФСБ 550, использующих 6-битовый накопитель.

В предпочтительном варианте осуществления последовательный поток данных БВН с выходного регистра 566 может включать в себя сообщения различного формата, кодированные двухрежимным передатчиком 14. Очевидно, что специалистами в данной области техники могут быть разработаны различные способы идентификации и выделения такой информации сообщений из последовательных данных БВН.

Описание предпочтительных вариантов осуществления изобретения приведено для того, чтобы дать возможность специалистам в данной области техники реализовать и использовать настоящее изобретение. Различные модификации указанных вариантов очевидны для специалистов в данной области техники, и общие принципы, определенные в настоящем описании, могут быть применены для других вариантов, без использования дополнительного изобретательства. Таким образом, настоящее изобретение не ограничено вариантами, раскрытыми в настоящем описании, а должно соответствовать наиболее широкому его объему, согласованному с принципами и новыми признаками изобретения, раскрытыми в описании.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКИ УСИЛЕНИЯ В ЦИФРОВОМ РАДИОПРИЕМНИКЕ | 1995 |

|

RU2163416C2 |

| ПРИЕМНАЯ СИСТЕМА AMPS, ИСПОЛЬЗУЮЩАЯ АРХИТЕКТУРУ НУЛЕВОЙ ПРОМЕЖУТОЧНОЙ ЧАСТОТЫ | 2003 |

|

RU2308804C2 |

| СПОСОБ И УСТРОЙСТВО АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКИ УСИЛЕНИЯ И ИСКЛЮЧЕНИЯ СМЕЩЕНИЯ ПОСТОЯННОЙ СОСТАВЛЯЮЩЕЙ В ПРИЕМНИКЕ С КВАДРАТУРНОЙ ДЕМОДУЛЯЦИЕЙ | 1995 |

|

RU2156538C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ЦИФРОВЫХ ДАННЫХ С ПЕРЕМЕННОЙ СКОРОСТЬЮ ПЕРЕДАЧИ | 1994 |

|

RU2266623C2 |

| ЛИНЕАРИЗОВАННАЯ ЦИФРОВАЯ АВТОМАТИЧЕСКАЯ РЕГУЛИРОВКА УСИЛЕНИЯ | 1996 |

|

RU2158474C2 |

| АРХИТЕКТУРА ПРИЕМНИКА С ПРЯМЫМ ПРЕОБРАЗОВАНИЕМ | 2008 |

|

RU2496229C2 |

| АРХИТЕКТУРА ПРИЕМНИКА С ПРЯМЫМ ПРЕОБРАЗОВАНИЕМ | 2013 |

|

RU2540263C2 |

| АРХИТЕКТУРА ПРИЕМНИКА С ПРЯМЫМ ПРЕОБРАЗОВАНИЕМ | 2002 |

|

RU2379825C2 |

| ГЕНЕРАТОРЫ ПСЕВДОСЛУЧАЙНОГО ШУМА ДЛЯ СИСТЕМ СВЯЗИ С РАСШИРЕННЫМ СПЕКТРОМ | 2001 |

|

RU2269202C2 |

| УСИЛИТЕЛЬ С ПЕРЕМЕННЫМ УСИЛЕНИЕМ И ВЫСОКИМ ДИНАМИЧЕСКИМ ДИАПАЗОНОМ | 1997 |

|

RU2209504C2 |

Предложена двухрежимная цифровая система связи для передачи информационного сигнала при работе в режиме с использованием частотной модуляции (ЧМ) и в режиме множественного доступа. Цифровая система связи содержит двухрежимный передатчик для передачи информационного сигнала с использованием ЧМ сигнала связи при работе в режиме ЧМ и для передачи информационного сигнала с использованием сигнала связи режима множественного доступа при работе в режиме множественного доступа. Система связи, кроме того, содержит двухрежимный приемник для приема ЧМ сигнала связи при работе в режиме с использованием ЧМ и для приема сигнала связи режима множественного доступа при работе в режиме множественного доступа. Двухрежимный приемник содержит цифровой демодулятор (96) для восстановления информационного сигнала из принятого ЧМ сигнала в режиме с использованием ЧМ и для восстановления информационного сигнала из принятого сигнала режима множественного доступа при работе в режиме множественного доступа. Техническим результатом является обеспечение фильтрации в базовой полосе без потери информации на несущей частоте. 2 с. и 4 з.п.ф-лы, 29 ил., 3 табл.

| Автоматический огнетушитель | 0 |

|

SU92A1 |

| Автоматический огнетушитель | 0 |

|

SU92A1 |

| Устройство для двустороннего шлифования торцов цилиндрических деталей | 1989 |

|

SU1756118A1 |

| US 5237586 A, 17.08.93. | |||

Авторы

Даты

1999-11-27—Публикация

1995-12-19—Подача