Область техники

Изобретение относится к системе для мультиплексирования/демультиплексирования данных межпроцессорного обмена (IPC) в режиме асинхронной передачи при обмене в режиме асинхронной передачи.

Уровень техники

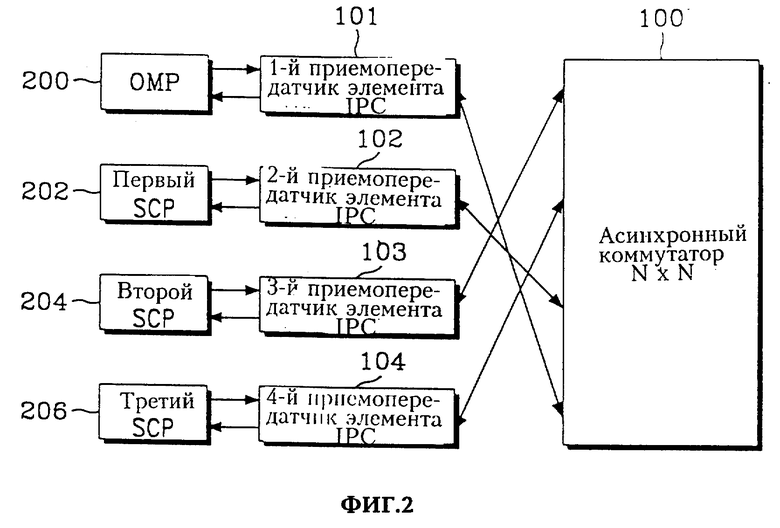

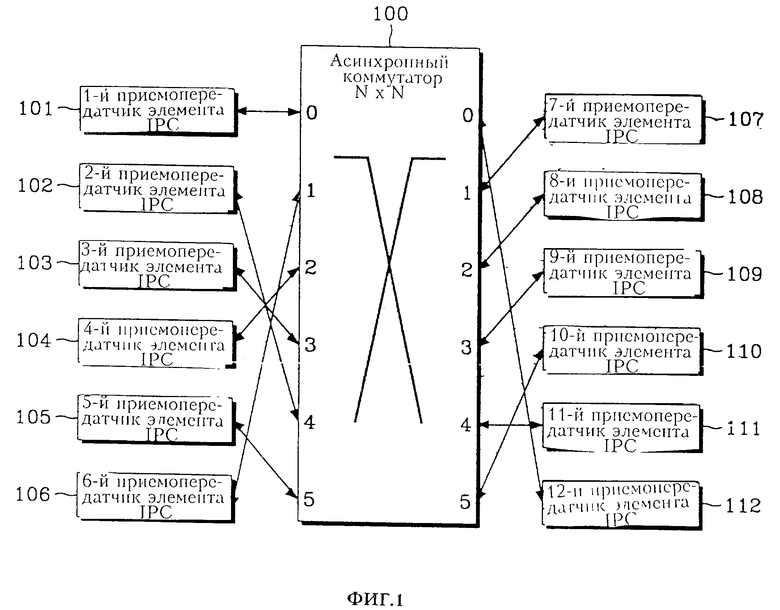

Для межпроцессорного обмена (IPC) в режиме асинхронной передачи (ATM) требуется один приемопередатчик данных IPC на один процессор, как показано на фиг. 1. Когда емкость (количество каналов) ATM коммутатора 100 увеличивается, то увеличивается количество процессоров и одновременно должно увеличиваться количество приемопередатчиков данных IPC. Более того, так как требуется один порт ATM-коммутатора на каждый приемопередатчик данных IPC, то увеличивается количество портов ATM-коммутатора. Количество приемопередатчиков данных IPC увеличивается в соответствии с увеличением скорости передачи в абонентских портах до 155 Мбит/сек. Такое увеличение количества портов ATM-коммутатора приводит к серьезному препятствию при наращивании системы.

Во время работы, когда OMP (процессор обслуживания и работы) 200 передает данные IPC, OMP 200 формирует данные IPC и передает данные IPC на первый приемопередатчик 101 данных IPC, как изображено на фиг. 2. Первый приемопередатчик 101 данных IPC передает данные IPC, принятые от OMP 200, в ATM-коммутатор 100. В противоположность этому, данные IPC опять передаются в OMP 200 через первый приемопередатчик 101 данных IPC. Таким образом, работают с первого по третий процессоры управления абонентом (SCP) 202, 204 и 206. Так как для одного процессора требуется один переключающий порт, то количество портов должно соответственно увеличиваться с увеличением количества процессоров. Поэтому требуются большие аппаратные затраты и становится трудно эффективно управлять ресурсами. Подобные системы описаны в патенте США N 5182801.

Сущность изобретения

Задачей настоящего изобретения является создание системы, которая может преодолеть описанные выше проблемы посредством мультиплексирования/демультиплексирования данных IPC.

Другой задачей настоящего изобретения является создание системы, которая может эффективно управлять новыми ресурсами с помощью мультиплексирования/демультиплексирования данных IPC.

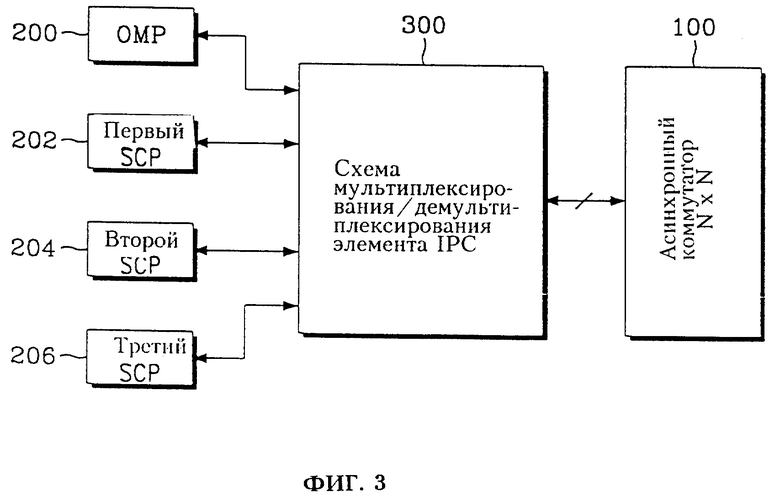

Согласно одному аспекту изобретения, система для мультиплексирования/демультиплексирования данных межпроцессорного обмена (IPC) в режиме асинхронной передачи включает в себя систему мультиплексирования/демультиплексирования данных IPC, включенную через процессор обслуживания и работы к первому - третьему процессорам управления абонента и ATM-коммутатору. Схема мультиплексирования/демультиплексирования данных IPC считывает значение идентификатора виртуального пути (VPI) данных IPC, принятых от ATM-коммутатора, для выбора процессора, к которому требуется передать данные IPC, передает принятые данные IPC в соответствующий процессор со скоростью 100 Мбит/сек и коммутирует данные IPC, принятые от конкретного процессора, с помощью процессора обслуживания и работы и с первого по третий процессоры управления абонента.

Настоящее изобретение будет более подробно описано со ссылками на сопроводительные чертежи.

Краткое описание чертежей

Фиг. 1 - диаграмма, иллюстрирующая путь данных IPC,

фиг. 2 - диаграмма, иллюстрирующая путь данных IPC через приемопередатчики данных IPC, подключенные к процессорам,

фиг. 3 - диаграмма, иллюстрирующая конфигурацию ATM-обмена с использованием схемы мультиплексирования/демультиплексирования данных IPC в соответствии с настоящим изобретением,

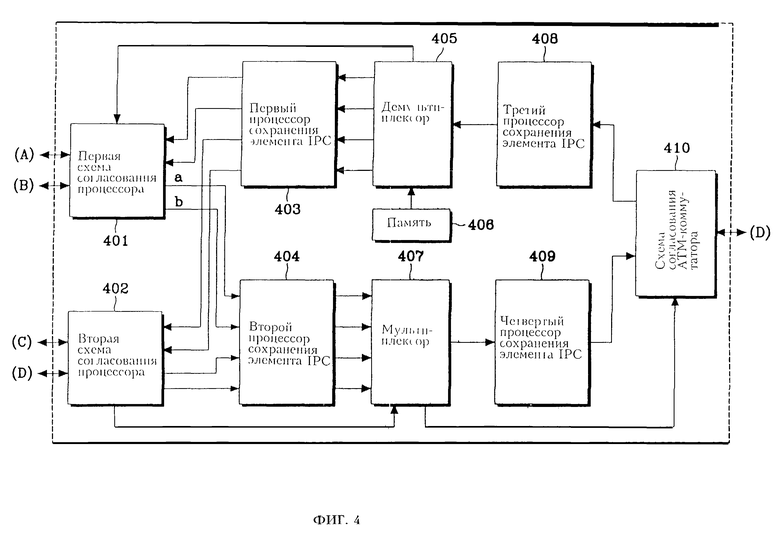

фиг. 4 подробно изображает схему мультиплексирования/демультиплексирования данных IPC, изображенную на фиг. 3,

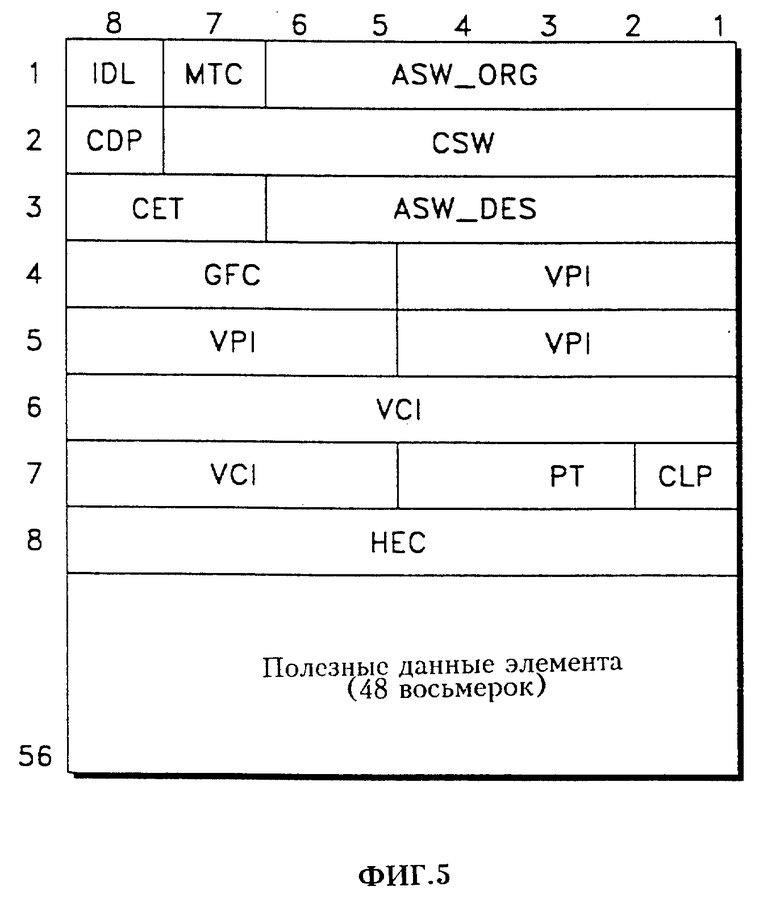

фиг. 5 изображает формат данных IPC из 56 байт согласно настоящему изобретению,

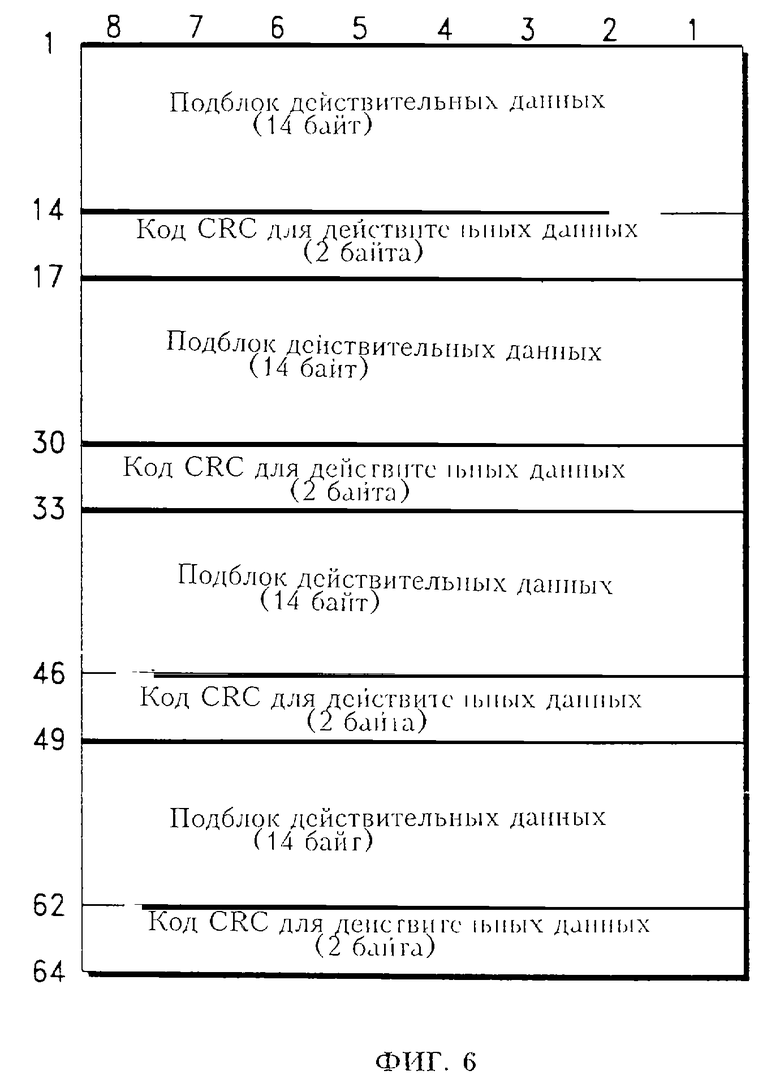

фиг. 6 изображает формат данных IPC из 64 байт согласно настоящему изобретению,

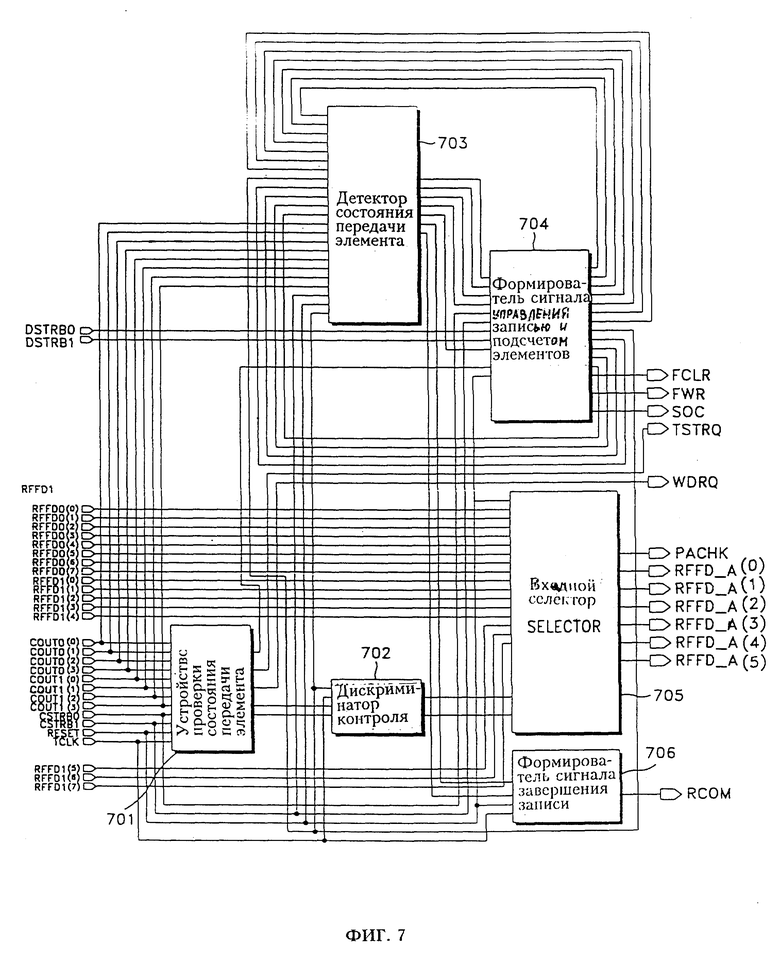

фиг. 7 - подробная блок-схема схемы согласования первого или второго процессора, изображенных на фиг. 4,

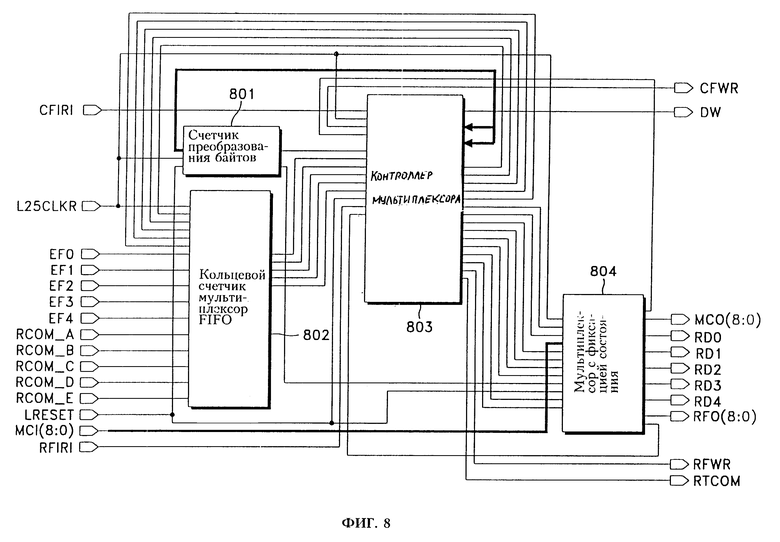

фиг. 8 - подробная блок-схема мультиплексора, изображенного на фиг. 4,

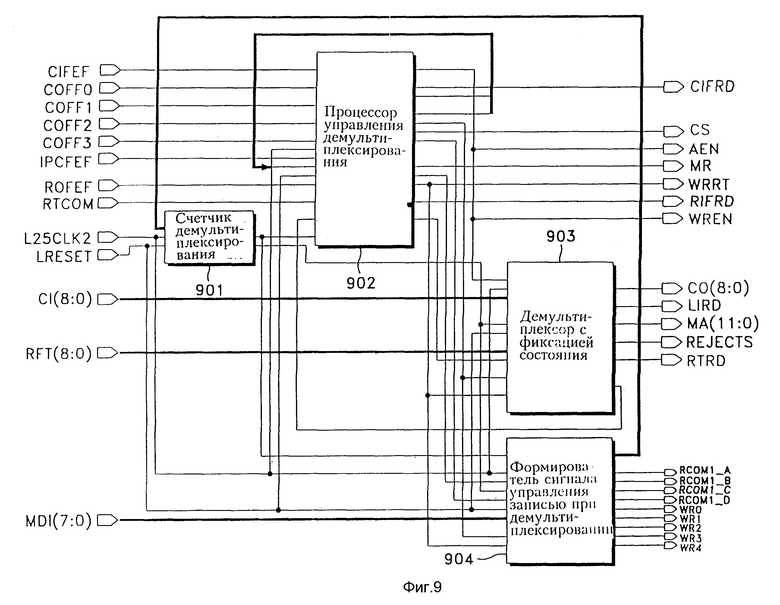

фиг. 9 - подробная блок-схема демультиплексора, изображенного на фиг. 4,

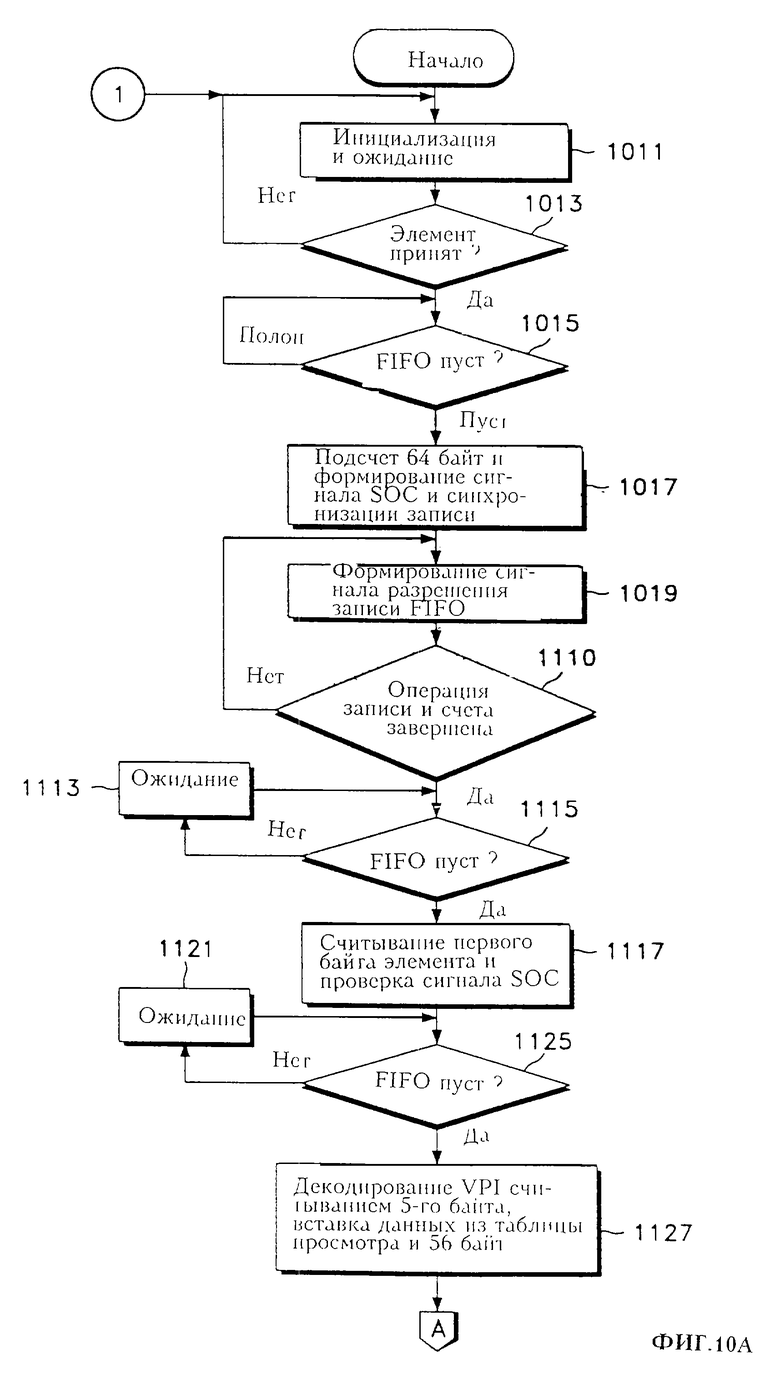

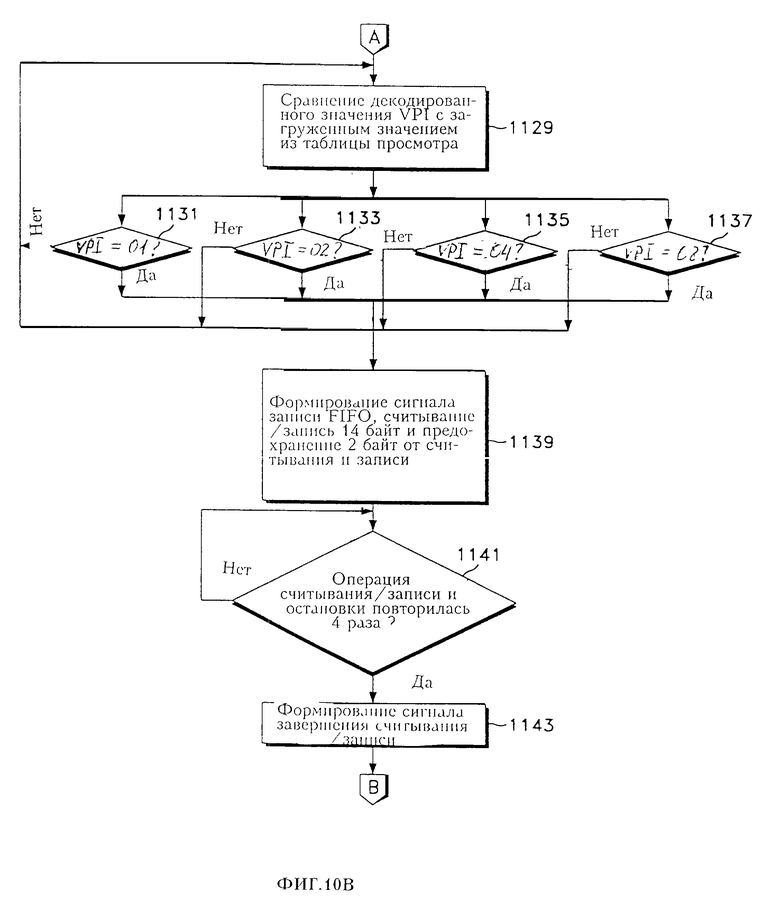

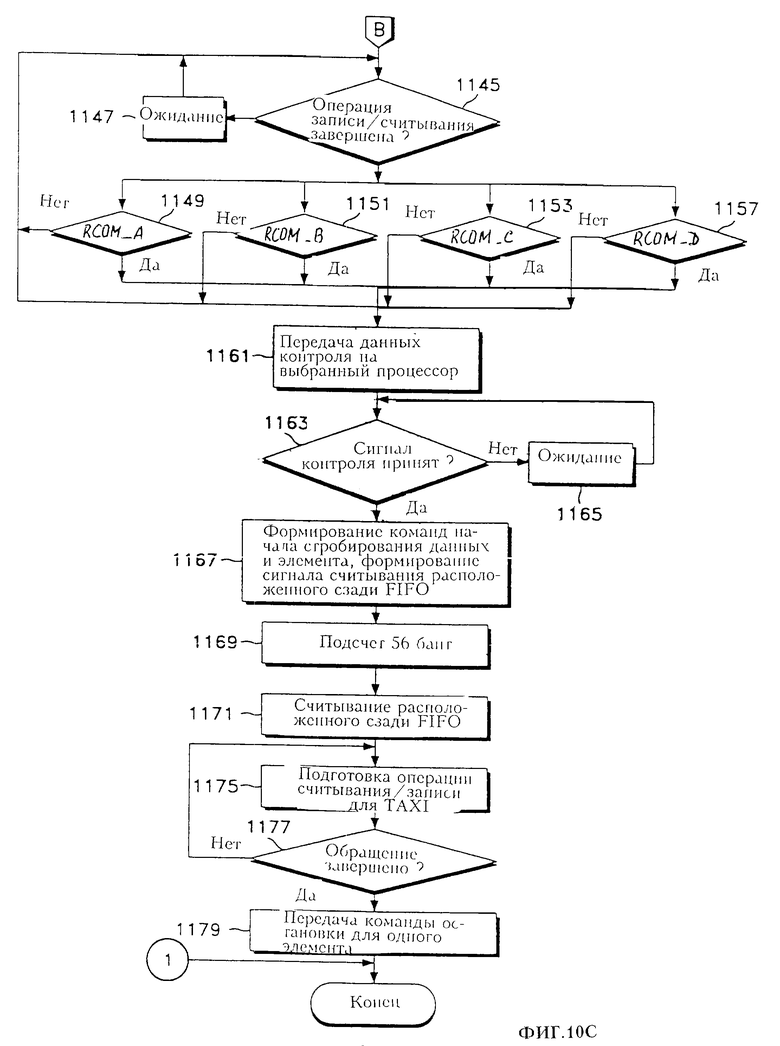

фиг. 10A-10C изображает последовательность операций при процедуре демультиплексирования согласно настоящему изобретению,

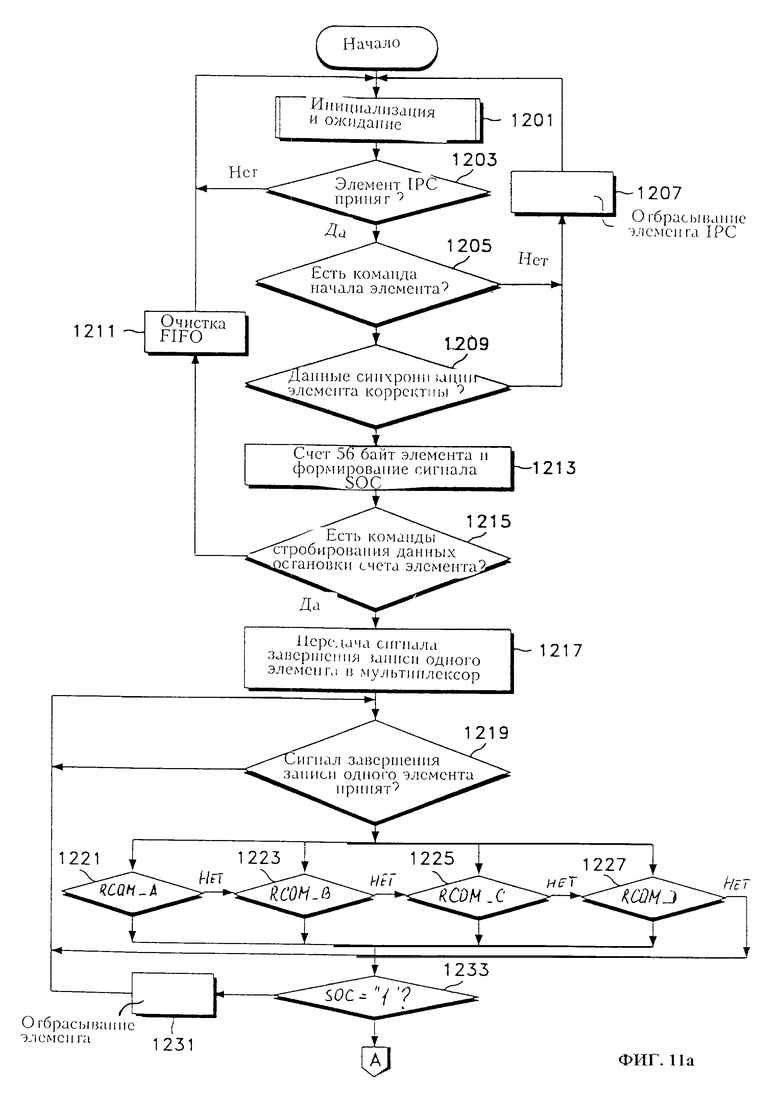

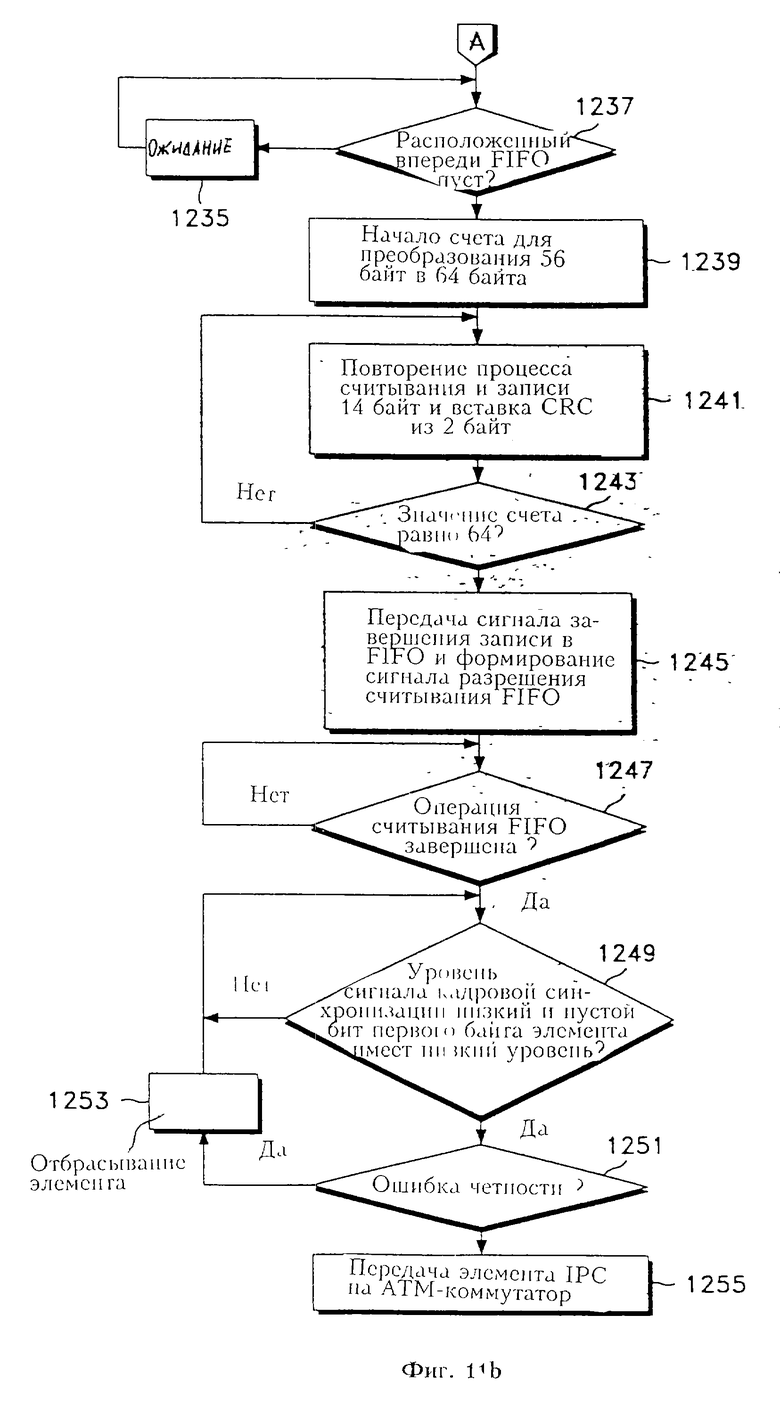

фиг. 11a-11b изображают последовательность операций при процедуре мультиплексирования согласно настоящему изобретению,

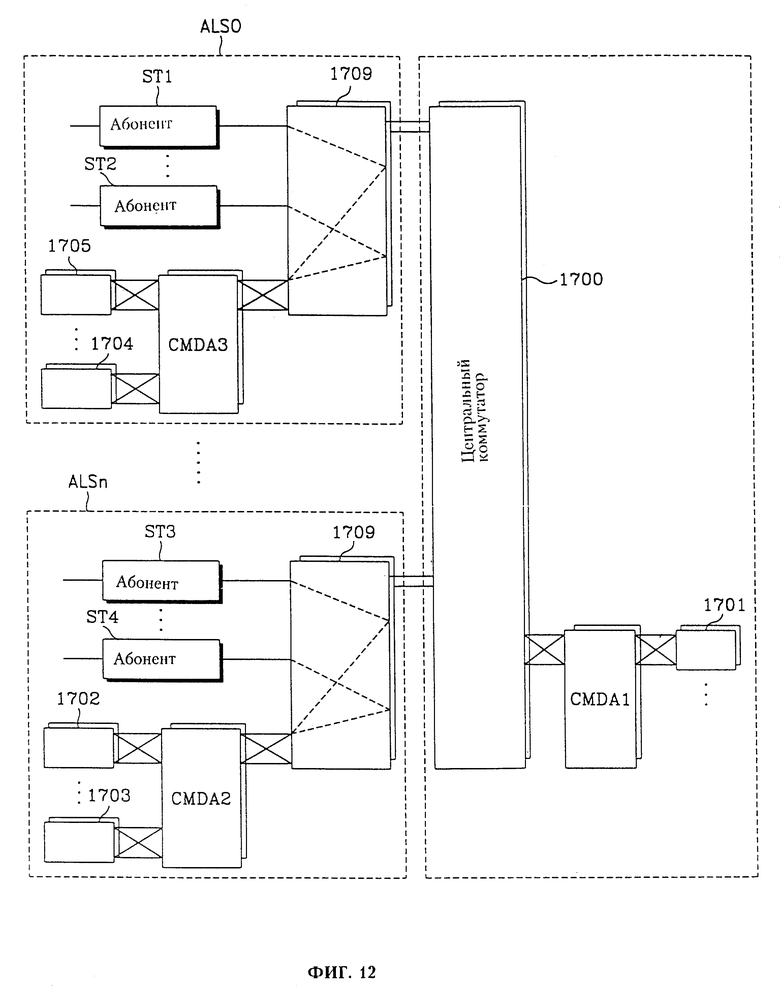

фиг. 12 - диаграмма, изображающая пример применения схемы мультиплексирования/демультиплексирования в соответствии с настоящим изобретением.

Подробное описание наилучшего варианта осуществления

Как изображено на фиг. 3, схема 300 мультиплексирования/демультиплексирования данных межпроцессорного обмена IPC включена между OMP 200, с первого по третий SCF 202-206 и ATM-коммутатором 100. Если данные IPC приняты от ATM-коммутатора 100, то схема 300 мультиплексирования/демультиплексирования данных IPC считывает значение VPI (идентификатора виртуального пути) принятых данных IPC для выбора процессора с целью передачи в него данных IPC, передает данные IPC в соответствующий процессор со скоростью 100 Мбит/сек. Между тем, данные IPC, принятые от конкретного процессора через OMP 200 к с первые по третьи IPC 202-206, коммутируются через схему 300 мультиплексирования/демультиплексирования и передаются в ATM-коммутатор 100.

Фиг. 4 подробно изображает схему 300 мультиплексирования/демультиплексирования, изображенную на фиг. 3. Схемы 401 и 402 согласования первого и второго процессоров согласованы с OMP и с первым по третий SPC 202-206 для передачи управляющих сигналов и данных. Второй процессор 404 сохранения данных IPC временно сохраняет данные, принятые или те, что должны быть переданы к первой и второй схемам 401 и 402 согласования процессоров. Мультиплексор 407 коммутирует данные IPC, поступающие из второго процессора 404 сохранения данных IPC. Четвертый процессор 404 сохранения данных IPC временно сохраняет выходной сигнал мультиплексора 407. Память 406 хранит данные для определения пути передачи данных IPC. Схема 410 согласования ATM-коммутатора согласована с АТС-коммутатором. Третий процессор 408 сохранения данных IPC временно сохраняет данные IPC, поступающие из схемы 410 согласования ATM-коммутатора. Демультиплексор 405 коммутирует выходной сигнал третьего процессора 408 сохранения данных IPC и передает скоммутированный выходной сигнал в направлении, заданном из памяти 406. Первый процессор 403 сохранения данных IPC временно сохраняет выходной сигнал демультиплексора 405.

Фиг. 5 изображает формат 56-байтных данных IPC. Обозначение IDL устанавливает, являются ли переданные данные IPC пустыми (обозначенными 1) или занятыми (0). MTC указывает, что переданные данные IPC являются данными IPC при широковещательной передаче (0). CDP устанавливает приоритет задержки данных IPC (0 означает высокий приоритет). CET служит для различения между данными IPC информации пользователя и данными IPC системы. CET, равный 00, обозначает данные IPC информации пользователя, CET, равные 01, обозначают данные IPC, имеющие адресную информацию широковещательной рассылки для обновления таблицы адресов вещательной компании в коммутаторе доступа во время установки запроса в начальное состояние, CET, равные 10, обозначают данные IPC, имеющие адресную информацию широковещательной рассылки для обновления таблицы адресов вещательной компании в центральном коммутаторе во время установки вызова в начальное состояние, и CET, равные 11, обозначают данные IPC сообщения IPC. Обозначение ASW_ORG указывает физический адрес коммутатора исходного обращения, CSW физический адрес центрального коммутатора, ASW ORG указывает физический адрес коммутатора входящего обращения, CLP -приоритет потери данных IPC, GFC -групповое управление потоком, PT - полезные данные, HEC - управление ошибками заголовка, VPI - идентификатор виртуального пути, a VCi - идентификатор виртуального канала.

Фиг.6 изображает формат 64-байтных данных IPC. Данные IPC из 56 байт разделяются на равные подблоки по 14 байт каждый. Циклический избыточный код проверки (CRC) действительных данных для подблоков из 14 байт вычисляется и сохраняется.

Фиг. 7 является подробной схемой первой и второй схемы согласования процессоров 401 и 402, изображенных на фиг. 4. Устройство 701 проверки состояния передачи данных IPC считывает данные с выводов COUT0 (0) - COUT0 (3) и COUT1 (0) - COUT1 (3) данных команды синхронно со стробирующими сигналами синхронизации данных IPC с выводов CSTRB0 и CSTRB1 для передачи командных данных, сформированных в процессоре, формирует сигнал контроля, сигнал начала передачи данных IPC и сигнал завершения передачи данных IPC и т.д. Дискриминатор 702 определяет, есть ли сигнал контроля, сформированный в устройстве 701 проверки состояния передачи данных IPC. Детектор 703 состояния передачи данных IPC определяет, являются ли входные командные данные сигналом начала передачи данных IPC или сигналом начала приема данных IPC, и правильно ли приняты данные IPC из 56 байт. Формирователь 704 сигнала управления записью и полсчета ячеек формирует счетный сигнал для подсчета 56 байт из детектора 703 состояния передачи данных IPC, формирует сигнал SOC (Начало элемента), который может правильно опознать начальную точку данных IPC, и формирует сигнал управления записью, который должен быть передан на процессор сохранения данных IPC на следующем этапе. Входной селектор 705 выбирает выводы A или B RFFD0 -RFFD1 для приема данных, исходя из данных на выводах дискриминатора 702 контроля. Формирователь 706 сигнала завершения записи формирует сигнал завершения записи, указывающий, точно ли записаны принятые данные IPC из 56 байт, сформированные детектором 703 состояния передачи данных IPC.

Фиг. 8 является подробной схемой мультиплексора 407, изображенного на фиг. 4. Счетчик 801 преобразования байтов формирует счетный сигнал для преобразования 56 байтов и 63 байта и счетный сигнал для разделения данных IPC из 56 байт на блоки по 14 байт. Кольцевой счетчик-мультиплексор (MUX), FIFO (первым пришел - первым ушел) 802 принимает сигнал завершения записи, указывающий, что данные IPC из 56 байт записаны в любой FIFO второго процессора 404 сохранения данных IPC, подтверждает количество данных IPC, которые находятся в текущем FIFO, и формирует сигналы посредством подтвержденного номера. Контроллер мультиплексора 803 принимает сигнал завершения записи, указывающий, что запись завершена в любой из FIFO, и формирует сигнал управления считыванием, требуемый для формирования сигнала для считывания конкретного FIFO. Мультиплексор 804 с фиксацией состояния считывает 64 байта с вывода MC1 шины с помощью сигнала управления считыванием, сформированного контроллером 803 мультиплексора для формирования действительных данных, и добавляет бит четности для 64 байт для повышения надежности действительных данных.

Фиг. 9 является подробной схемой демультиплексора 407, изображенного на фиг. 4. Счетчик 901 демультиплексирования формирует счетный сигнал для преобразования принятых 64 байт а 56 байт. Процессор 902 управления демультиплексированием проверяет состояние третьего и первого процессоров 408 и 403 сохранения данных IPC. Если данные IPC присутствуют, то процессор 902 управления демультиплексированием считывает первый байт данных IPC для проверки, являются ли существующие данные IPC верными, с помощью сигнала SOC и определяет порт записи с помощью использования поля VPI в структуре данных IPC из 64 байт для выбора одного конкретного FIFO. Процессор 902 управления демультиплексированием преобразует также 64 байта в 56 байт с помощью выходного сигнала счетчика 901 демультиплексирования. Схема 903 демультиплексирования с фиксацией состояния фиксирует 5 байт выходного сигнала процесса 902 управления демультиплексированием, формирует адрес для считывания значения VPI посредством обращения к таблице памяти 406, и записывает входные данные IPC с помощью сигнала разрешения записи, сформированного процессором 902 управления демультиплексированием. Формирователь 904 сигнала управления записью при демультиплексировании формирует адресный сигнал так, чтобы схема 904 демультиплексирования с фиксацией состояния могла считать данные памяти 406, формирует сигналы WR0-WR4 управления записью с помощью выходных сигналов схемы 903 демультиплексирования с фиксацией состояния и процессора 902 управления демультиплексированием и формирует сигналы RCOM1_A - RCOM_D завершения записи одних данных IPC.

Фиг. 10a - 10c изображает последовательность операций процедуры демультиплексирования. На этапах 1011-1015 принимаются данные IPC и проверяется, пуст ли расположенный впереди FIFO. Если FIFO пуст, то счетчик на 64 байта начинает счет, и на этапе 1017 формируются сигналы SOC и синхронизирующий сигнал записи FIFO. Сигнал разрешения записи FIFO формируется на этапе 1019. На этапе 1110 проверяется, завершились ли операции счета и записи. Если да, то на этапе 1115 проверяется, пуст ли FIFO. Если FIFO пуст, то на этапе 1117 считывается первый байт данных IPC и проверяется состояние SOC. Пуст ли FIFO проверяется на этапе 1125. Если FIFO пуст, то считывается пятый байт для декодирования VPI, данные памяти вставляются из таблицы поиска и счетчика на 56 байт начинает отсчет на этапе 1127. Декодированное значение VPI сравнивается на этапе 1129 с загружающимся значением из таблицы поиска. Равно ли значение VPI "01", "02", "04" или "08", проверяется на этапах 1131-1137. В соответствии со значением VPI выбирается канал передачи FIFO. На этапе 1139 формируется сигнал записи FIFO и 14 байт считываются и записываются, а два байта не подвергаются записи и считыванию. На этапе 1141 проверяется, повторились ли 4 раза процессы считывания/записи и пропуска 4 раза. Если да, то на этапе 1143 формируется сигнал завершения считывания/записи. На этапах 1149- 1157 проверяется, соответствует ли сигнал завершения считывания/записи RCOM_A - RCOM_D. Данные контроля передаются на выбранный процессор на этапе 1161. На этапе 1163 проверяется, принят ли сигнал контроля. Если принят, то формируются команды начала стробирования данных и данных IPC, и сигнал считывания с расположенного сзади FIFO формируется на этапе 1167. На этапе 1169 отсчитываются 56 байт, а на этапе 1171 считывается расположенный сзади FIFO. На этапе 1175 выполняется операция считывания/записи для TAXI (прозрачного интерфейса асинхронной приемопередачи). На этапе 1177 проверяется, завершилось ли обращение. На этапе 1179 команда 0011 остановки одних данных IPC передается в TAX1.

Фиг. 11a и 11b изображают последовательность операций процедуры мультиплексирования. Установка в начальное состояние и ожидание приема выполняются на этапе 1201. Приняты ли данные IPC, проверяется на этапе 1203. На этапе 12-5 проверяется, есть ли команда начала данных IPC. Если команда начала данных IPC есть, то на этапе 1209 проверяется, правильна ли синхронизация стробирования данных IPC. Если да, то на этапе 1213 отсчитываются 56-байтные данные и генерируется сигнал SOC. Ha этапе 1215 проверяется, есть ли команды остановки отсчета данных IPC и стробирования данных. Если этих команд нет, то на этапе 1211 очищается FIFO. Если эти команды есть, то в мультиплексор на этапе 1207 передается сигнал завершения записи одних данных IPC. Проверка на этапе 1219 осуществляется для просмотра, принят ли сигнал завершения записи одних данных IPC. Если сигнал завершения записи одних данных IPC принят на выводы RCOM_A - RCOM_D, то на этапе 1233 проверяется сигнал SOC. Если сигнал SOC равен 0, то на этапе 1231 данные IPC отбрасываются. Если сигнал SOC равен 1, то на этапе 1237 проверяется, заполнен ли расположенный впереди FIFO. Если он пуст, то на этапе 1239 начинается отсчет для преобразования 56 байт в 64 байта. Процесс считывания 14 байт и вставки CRC из двух байт проверяется. На этапе 1234 осуществляется проверка, достигло ли подсчитанное значение 64. Если да, то на этапе 1245 сигнал завершения записи передается в расположенный впереди FIFO и генерируются сигнал разрешения записи FIFO. На этапе 1247 проверяется, завершено ли считывание FIFO. Если да, то на этапе 1249 проверяется, имеет ли нарастающий сигнал MCLK кадровой синхронизации низкий уровень, и имеет ли незанятый бит первого байта элемента низкий уровень. Если да, то на этапе 1251 осуществляется проверка на четкость. Если есть ошибка при проверке на четность, то данные IPC отбрасываются на этапе 1253. Если ошибки нет, то данные IPC передаются на ATM-коммутатор.

На фиг. 12 блок мультиплексирования/демультиплексирования включен между процессорами и локальным коммутатором.

Подробное описание мультиплексирования и демультиплексирования приводится ниже со ссылкой на фиг. 3-12.

Мультиплексирование

Для сопряжения каждого процессора из OMP 200 и с первого по третий SCP 200 - 206 с первой или второй схемой согласования процессора 401 или 402, данные IPC преобразуются в последовательные данные со скоростью 100 Мбит/сек с уровнем ЭСЛ- логики. Преобразованные данные подаются на первую или вторую схемы 401 или 402 согласования процессора, которая является интерфейсом приема. Среди преобразованных данных 4 бита образуют сигнал контроля и сигнал качала или завершения передачи данных IPC в качестве данных команды от устройства 701 проверки состояния передачи данных IPC, дискриминатора 702 контроля и формирователя 706 сигнала завершения записи.

На фиг. 7 выводы COUT0 (1) - COUT0 (3) данных команды подаются на выводы "A", a COUT1 (1) - COUT1 (3) на выводы "B". Устройство 701 проверки состояния передачи данных IPC выделяет сигнал контроля, сигнал начала передачи данных IPC и сигнал завершения передачи данных IPC синхронно с сигналами выводов данных команды COUT0 (1) - COUT0 (3) и COUT1(l) - COUT1 (3), сигналами с выводов стробирования CSTRB0 и CSTRB1 и сигнала синхронизации с вывода TCLK. Сигнал контроля, сформированный в устройстве 701 проверки состояния передачи данных IPC, подается на дискриминатор 702 контроля для определения выводов A или B посредством проверки этого сигнала контроля.

Формирователь 704 сигнала управления записью и подсчета данных IPC формирует счетный сигнал для подсчета 56 байт с помощью сигналов с выводов DSTRB0 и DSTRB1 и формирует SOC сигнал, который может правильно опознать начальную точку данных IPC во время мультиплексирования, и формирует сигнал управления записью для записи данных IPC в расположенный впереди FIFO.

С помощью сигналов с выводов CSTRB0 и CSTRB1 стробирования данных IPC, сигнала с вывода записи RESET, выходных сигналов формирователя 704 сигнала управления записью и подсчета данных IPC и сигналов выводов данных команды COUT0 (1) - COUT0 (3) и COUT1 (1) - COUT1 (3) проверяется, должна начинаться передача данных IPC или прием данных IPC и правильно ли приняты данные IPC из 56 байт. Если подсчитано количество, отличающееся от 56 байт, то формирователь 704 сигнала управления записью и подсчета данных IPC формирует сигнал записи. Формирователь 706 сигнала завершения записи формирует сигнал RCOM завершения записи, если принятые данные IPC из 56 байт точно записаны в FIFO. Выходной сигнал из дискриминатора 702 контроля подается на входной селектор 705. Входной селектор 706 выбирает или данные с выводов A или B данных RFFD0 (0) - RFFD0 (7) с помощью сигналов выбора A или B дискриминатора 702 контроля, и передает выбранные данные в FIFO на следующем этапе. FIFO соответствует второму процессору 404 сохранения данных IPC, изображенному на фиг. 4. Второй процессор 404 сохранения данных IPC записывает S-битные данные, которые выдаются из входного селектора 705, и SOC сигнал из одного бита в соответствующий FIFO в виде блока из одного элемента из 56 байт. Выходной сигнал второго процессора 404 сохранения данных IPC подается на мультиплексор 407. Счетчик 801 преобразования байтов мультиплексора 407 формирует счетный сигнал для преобразования 56 байт в 64 байта и формирует счетный сигнал для разделения данных IPC из 56 байт на блоки по 14 байт.

Кольцевой счетчик 802 MUX FIFO определяет сигналы выводов EF0 - EF4 состояния, указывающих, является ли каждый FIFO второго процессора 404 сохранения данных IPC пустым, и определяет количество данных IPC в FIFO. Кольцевой счетчик 802 MUX FIFO подает сигналы в виде подтвержденного количества в контроллер 803 мультиплексора.

Контроллер 803 мультиплексора принимает сигнал завершения записи, указывающий, что запись завершена в любой из FIFO из кольцевого счетчика 802 MUX FIFO и формирует сигналы, требуемые для формирования сигнала считывания конкретного FIFO. Для этого считанное значение счета вычисляется с помощью 14 байт для преобразования данных IPC из 56 байт в 64 байта, и значение подсчета вставки пустых данных из 2 байт добавляется к считанному подсчитанному значению. Таким образом, сигналы, необходимые для преобразования 56 байт в 64 байта, формируются и подаются в мультиплексор 804 с фиксацией состояния. Для оценки безошибочности данных IPC из 56 байт проверяется сигнал SOC. Контроллер 803 мультиплексора проверяет состояние расположенного впереди FIFO для записи данных IPC в расположенный впереди FIFO сразу, как только мультиплексор 804 с фиксацией состояния считывает данные IPC из FIFO. Если FIFO пуст, то контроллер 803 мультиплексора посылает сигнал записи, а если FIFO не пуст, то сигнал записи не посылается. То есть, если расположенный впереди FIFO пуст, то контроллер 803 мультиплексора записывает данные, считанные мультиплексором 804 с фиксацией состояния, в расположенный впереди FIFO и передает сигнал завершения записи в расположенный впереди интерфейс.

Мультиплексор 804 с фиксацией состояния должен передавать принятые данные RDX для считывания данных из FIFO в FIFO. Эти данные RDX приема формируются посредством комбинирования сигнала считывания 64 байт, принятых от контроллера 803 мультиплексора. Мультиплексор 804 с фиксацией состояния передает принятые данные RDX в соответствующий FIFO. Мультиплексор 804 с фиксацией состояния считывает данные IPC из FIFO и одновременно передает действительные данные в расположенный впереди FIFO синхронно с сигналом, принятым от контроллера 803 мультиплексора. Для того чтобы повысить надежность действительных данных, при передаче добавляется бит четности для 64 байт.

Выходной сигнал мультиплексора 407 обрабатывается в четвертом процессоре 409 сохранения элемента IPC и подается на схему 410 согласования ATM-коммутатора. Схема 410 согласования ATM-коммутатора принимает данные IPC из 64 байт из четвертого процессора 409 сохранения данных IPC и служит в качестве интерфейса для передачи 56 байт со скоростью 100 Мбит/сек, а не 187,7 Мбит/сек. То есть, данные записываются со скоростью последовательной передачи 187.7 Мбит/сек, и считываются со скоростью параллельной передачи 12.5 Мбит/сек во время демультиплексирования.

Демультиплексирование

Выходные данные, состоящие из 64 байт, из схемы 410 согласования ATM-коммутатора обрабатываются в третьем процессоре 408 сохранения данных IPC. Счетчик 901 демультиплексирования (фиг. 9) демультиплексора 405 формирует сигнал подсчета для преобразования 64 байт в 56 байт и формирует сигнал CON2, необходимый для счетного сигнала. Процессор 902 управления демультиплексированием оценивает, приняты ли данные IPC в FIFO посредством проверки состояния FIFO в третьем процессоре 408 сохранения данных IPC. Если данных IPC нет, то процессор 902 управления демультиплексированием возвращается в состояние ожидания. Если данные IPC есть, то процессор 902 управления демультиплексированием считывает первый байт данных IPC. Процессор 902 управления демультиплексированием проверяет сигнал SOC для просмотра корректности данных IPC. Если данные IPC некорректны, они отбрасываются. Если данные IPC корректно, то процессор 902 управления демультиплексированием последовательно считывает 4 байта. Для выбора конкретного FIFO из 4-х FIFO расположенных на входе демультиплексора 405, используется поле VPI, расположенное в четвертой и пятой восьмерках структуры из 64 байт элемента. Если значение VPI равно 00000001, то выбирается первый FIFO если 00000010, то выбирается второй FIFO, если 00000100, то выбирается третий FIFO, а если 00001000, то выбирается четвертый FIFO.

Для вставки значения VPI из данных IPC процессор 902 управления демультиплексированием фиксирует пятый байт и считывает значение из DPRAM (двухпортовой памяти со случайным доступом) памяти 406, хранящей значение VPI.

Порт записи определяется так, чтобы записать данные IPC в FIFO с помощью проверки, равно ли считанное значение из DPRAM значению VPI, выделенному из данных IPC. Если они не равны, то данные IPC отбрасываются. После того, как порт записи определен, выполняется считывание и запись посредством использования значения счета, переданного из счетчика 901 демультиплексирования для преобразования 64 байт в 56 байт. То есть, с первого по 14 байты считываются, а 15-й и 16-й отбрасываются. 14 байт, начиная с 17-го считываются, а следующие 2 отбрасываются. Таким образом, 64 байта преобразуются в 56 байт. Процессор 902 управления демультиплексированием формирует сигнал CIFRD считывания FIFO, а DPRAM выбирает сигналы считывания и записи. Схема 903 демультиплексирования с фиксацией состояния фиксирует 5 байт, требуемых в процессоре 902 управления демультиплексированием. Схема 903 демультиплексирования с фиксацией состояния коммутирует значение VPI из зафиксированного значения для формирования адреса для считывания значения VPI из таблицы просмотра памяти 406. Схема 903 демультиплексирования с фиксацией состояния принимает сигнал разрешения записи WREN от процессора 902 управления демультиплексированием и записывает входные данные IPC в FIFO. Формирователь 904 сигнала управления записью при демультиплексировании формирует адресный сигнал так, что демультиплексор 405 может считывать данные из памяти 406. При записи данных IPC в расположенный впереди FIFO формирователь 904 сигнала управления записью при демультиплексировании принимает сигналы от схемы 903 демультиплексирования с фиксацией состояния и процессора 902 управления демультиплексированием и формирует сигналы WR0-WR4 управления записью. После записи одних данных IPC в FIFO формирователь 904 сигнала управления записью при демультиплексировании формирует сигналы RCOM1_A - RCOM1_D завершения записи одних данных IPC, которые должны быть переданы в расположенный впереди передающий интерфейс связи.

Выходной сигнал демультиплексора 405 подается на первый процессор 403 сохранения данных IPC так, чтобы записать данные IPC из 56 байт в FIFO. Выходные данные из 56 байт первого процессора 403 сохранения данных IPC считываются счетчиком первой схемы 401 согласования процессора после того, как сигнал завершения записи обнаружен. Для выдачи и приема процессором сигнала контроля, который должен быть передан, формируются команды контроля завершения передачи данных IPC и начала передачи данных IPC. Для передачи данных IPC проверяется сигнал контроля, принимается сигнал RCOM завершения записи, и выход счетчика устанавливается в исходное состояние. Передаются 56 байт в линию связи посредством согласования синхронизации с сигналом стробирования данных. После передачи 56 байт посылается команда завершения передачи. Если данные IPC переданы, то поддерживается состояние ожидания.

Подробные последовательности операций при мультиплексировании/демультиплексировании приводятся на фиг. 10A-10C и 11a и 11b.

Фиг. 12 изображает пример применения схемы мультиплексирования/демультиплексирования. Для передачи какой-либо информации в процессор 1705 из процессора 1701 первой локальной подсистемы ALSO процессор 1701 формирует данные IPC. В этом случае значение VPI 00000001 вставляется в процессор назначения, т.е. в процессор 1705. Так как процессор 1701 соединяется через центральный коммутатор 1700 и локальный коммутатор 1709, то задаются значения ASW_ ORG, CSW, ASW_DES в первой, второй и третьей восьмерках из 56 байт так, чтобы осуществлялось переключение в каждом из коммутаторов. Информация, требуемая в процессоре, вставляется, и данные IPC длиной - 56 байт передаются в CMDA1 из процессора 1701. CMDA1 принимает данные IPC длиной 56 байт от процессора 1701, изменяет формат данных IPC до 64 байт и передает данные IPC в центральный коммутатор 1700. Центральный коммутатор 1700 переключает данные IPC посредством CSW из верхних 3 восьмерок формата данных IPC, измененного до 64 восьмерок. В первой локальной подсистеме доступа ALSO локальный коммутатор 1709 коммутирует данные IPC из 64 восьмерок с помощью ASW_DES. Данные IPC, проходящие через локальный коммутатор 1709, передаются на CMDA3. CMDA3 считывает верхние 5 восьмерок из 64 восьмерок и фиксирует значение VPI. Демультиплексор выбирает значение VPI из таблицы просмотра DPRAM. Фиксированное значение VPI сравнивается со значением VPI, выбранным мультиплексором. Данные IPC записываются в FIFO, если значения VPI равны друг другу. Демультиплексор преобразует данные IPC из 64 байт в данные IPC из 56 байт посредством повторяющегося считывания 14 байт и отбрасывания 2 байт. Если записаны 56 байт, они передаются в линию связи TAXI и поступают в процессор 1705 конечного назначения.

Как описано выше, конструкция аппаратного обеспечения приемопередатчика IPC, согласованная с процессором, может быть упрощена. Поэтому, размер системы уменьшается и ресурсы коммутации эффективно управляются. Кроме того, облегчается высокая интеграция схемы.

Должно быть ясно, что настоящее изобретение не ограничено частным воплощением, раскрытым в нем в качестве наилучшего варианта воплощения настоящего изобретения, а скорее, настоящее изобретение не ограничивается конкретными вариантами воплощения, приведенными в описании, за исключением определенных в прилагаемой формуле изобретения.

Изобретение относится к вычислительной технике и может быть использовано для осуществления мультиплексирования/демультиплексирования данных межпроцессорного обмена. Техническим результатом является сокращение аппаратных затрат. Для этого устройство содержит процессор обслуживания и работы, процессоры управления абонента, коммутатор асинхронной передачи и схему мультиплексирования/демультиплексирования данных межпроцессорного обмена. 4 з. п. ф-лы, 12 ил.

| US 5182801 A, 26.01.93 | |||

| Устройство для централизованного управления вычислительной системой | 1987 |

|

SU1674146A1 |

| US 5191651 A, 02.03.93 | |||

| ЖЕВАТЕЛЬНАЯ ПИЩЕВАЯ КОМПОЗИЦИЯ С РАЗБУХШЕЙ ТЕКСТУРОЙ | 2014 |

|

RU2667748C1 |

Авторы

Даты

1999-12-10—Публикация

1997-08-12—Подача