О VI

Ь;

Ј О

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для централизованного управления вычислительной системой | 1985 |

|

SU1259261A1 |

| Устройство для связи процессоров | 1986 |

|

SU1481785A1 |

| Периферийный процессор для обработки сигналов | 1985 |

|

SU1368889A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство для сопряжения ЦВМ с накопителями на магнитной ленте | 1985 |

|

SU1288708A1 |

| Устройство для обмена двухмашинного вычислительного комплекса | 1981 |

|

SU991403A1 |

| Многоканальный преобразователь угла поворота вала в код | 1983 |

|

SU1144190A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Адаптивная система обработки данных | 1985 |

|

SU1312596A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения высокопроизводительных многопроцессорных вычислительных систем. Целью изобретения является повышение производительности вычислительной системы. Предлагаемое устройство содержит управляющий процессор 1, группу процессоров 2, формирователь циклов 3, узлы обмена 4 и два коммутатора 5 и 6. Цель изобретения достигается за счет введения в каждый процессор 2 группы элементов ИЛИ и интерфейсного блока, что позволяет организовать загрузку как отдельного процессора, так и параллельную загрузку группы процессоров. 1 з.п. ф-лы, 5 ил.

Фиг. /

Изобретение относится к вычислительной технике и может быть использовано для построения высокопроизводительных многопроцессорных вычислительных систем, предназначенных для обработки данных в реальном масштабе времени

Целью изобретения является повышение производительности вычислительной системы.

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема управляющего процессора; на фиг. 3 - структурная схема процессора; на фиг. 4 - структурная схема интерфейсного блока; на фиг. 5 - структурная схема формирователя циклов.

Системи о / . Т . фи 1) управляю щий процессор 1, процессоры 2i-2n, формирователь циклов 3, узлы обмена , коммутатор 5 внешних обменов, коммутатор 6 межпроцессорных обменов, шины 7 и 8 управления коммутаторами 5 и 6, шины 9 и 10 управления формирователем 3 циклов, выходную шину 11 формирователя 3 циклов, шины 12-15 управления процессорами 2.

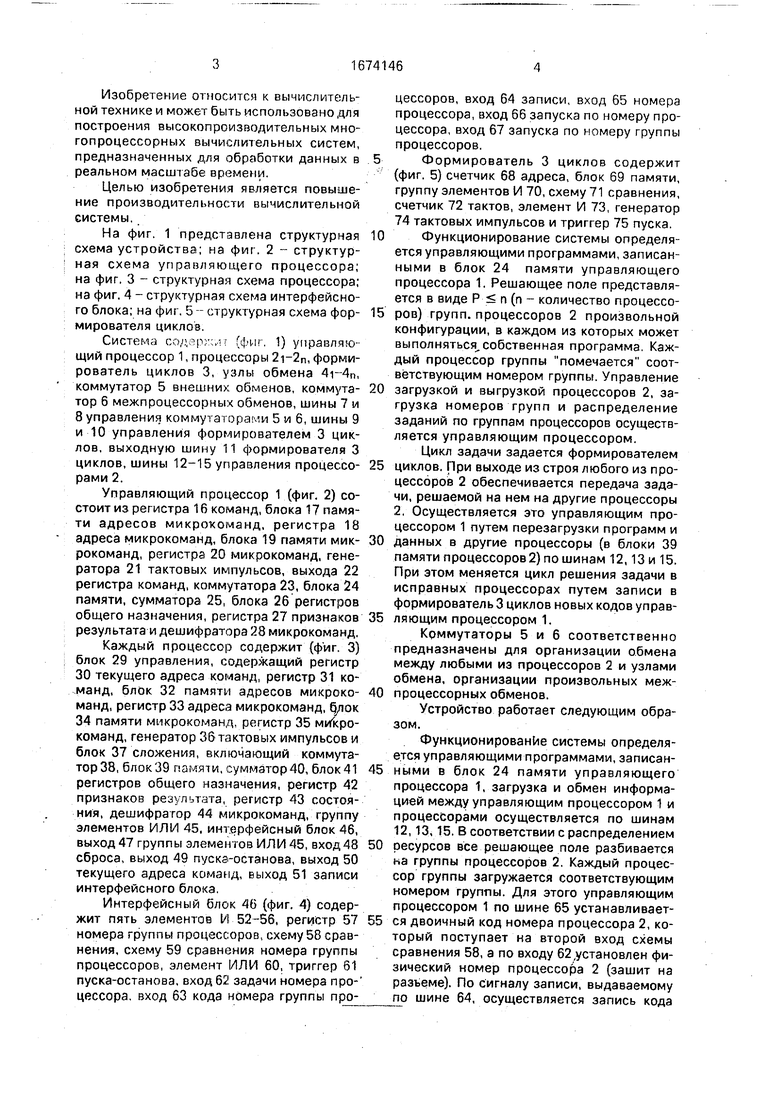

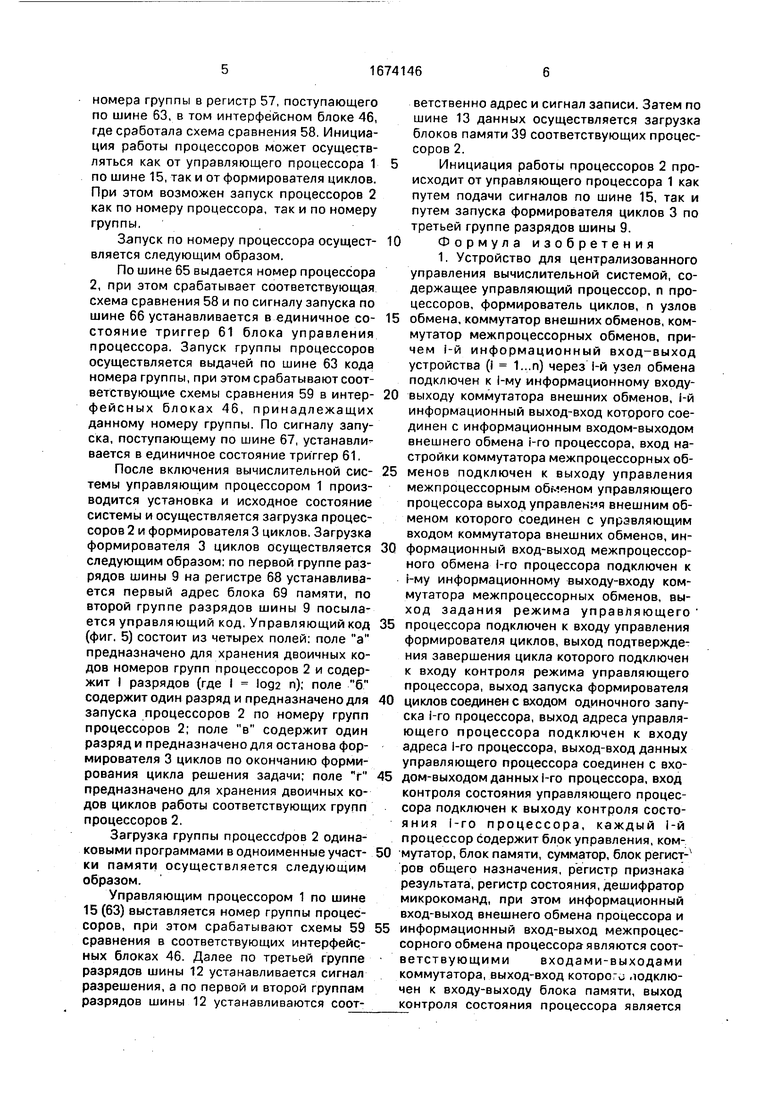

Управляющий процессор 1 (фиг. 2) состоит из регистра 16 команд, блока 17 памяти адресов микрокоманд, регистра 18 адреса микрокоманд, блока 19 памяти микрокоманд, регистра 20 микрокоманд, генератора 21 тактовых импульсов, выхода 22 регистра команд, коммутатора 23, блока 24 памяти, сумматора 25, блока 26 регистров общего назначения, регистра 27 признаков результата и дешифратора 28 микрокоманд. Каждый процессор содержит (фиг. 3) блок 29 управления, содержащий регистр 30 текущего адреса команд, регистр 31 команд, блок 32 памяти адресов микрокоманд, регистр 33 адреса микрокоманд, блок 34 памяти микрокоманд, регистр 35 микрокоманд, генератор 36 тактовых импульсов и блок 37 сложения, включающий коммутатор 38, блок 39 памяти, сумматор40, блок 41 регистров общего назначения, регистр 42 признаков ре- льтата, регистр 43 состояния, дешифратор 44 микрокоманд, группу элементов ИЛИ 45, интерфейсный блок 46, выход 47 группы элементов ИЛ И 45, вход 48 сброса, выход 49 пуска-останова, выход 50 текущего адреса команд, выход 51 записи интерфейсного блока.

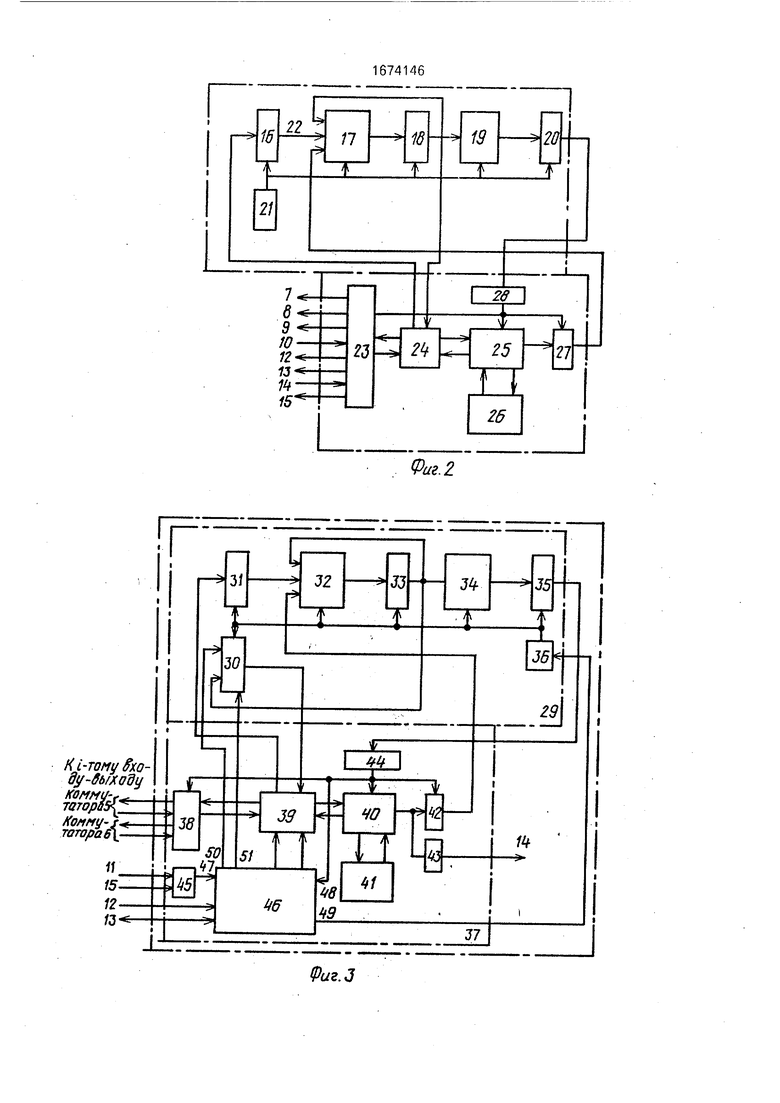

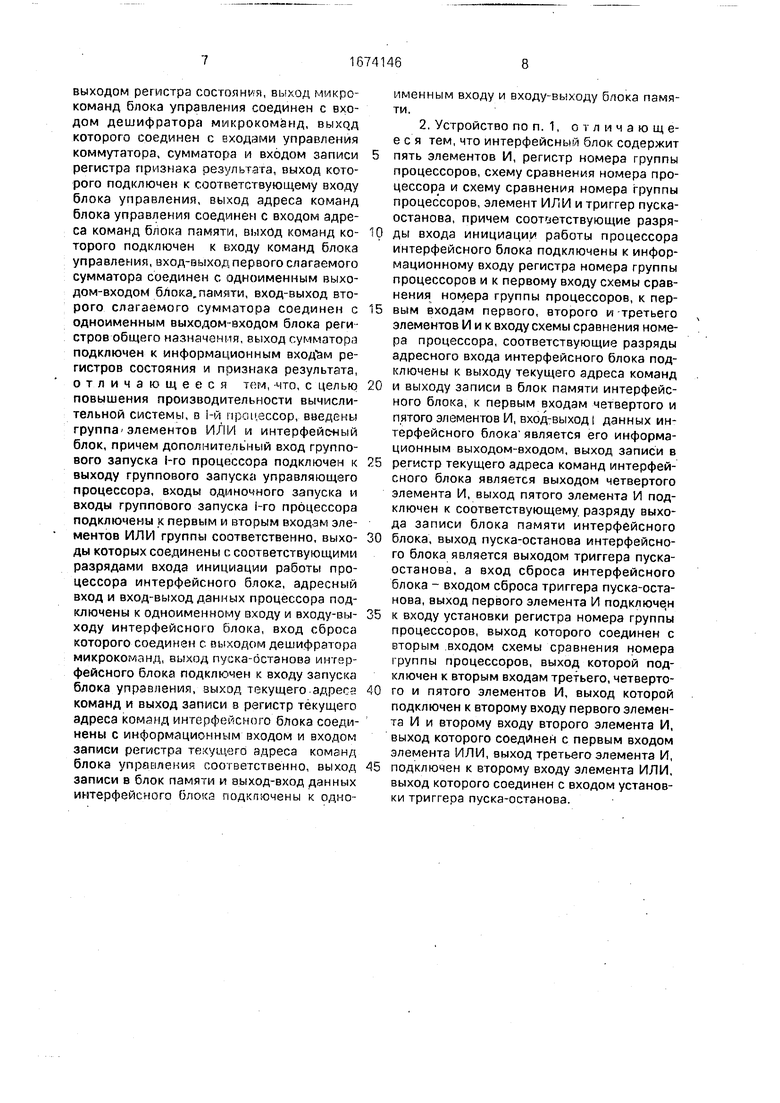

Интерфейсный блок 46 (фиг. 4) содержит пять элементов И 52-56, регистр 57 номера группы процессоров, схему 58 сравнения, схему 59 сравнения номера группы процессоров, элемент ИЛИ 60, триггер 61 пуска-останова, вход 62 задачи номера процессора, вход 63 кода номера группы процессоров, вход 64 записи, вход 65 номера процессора, вход 66 запуска по номеру про цессора, вход 67 запуска по номеру группы процессоров.

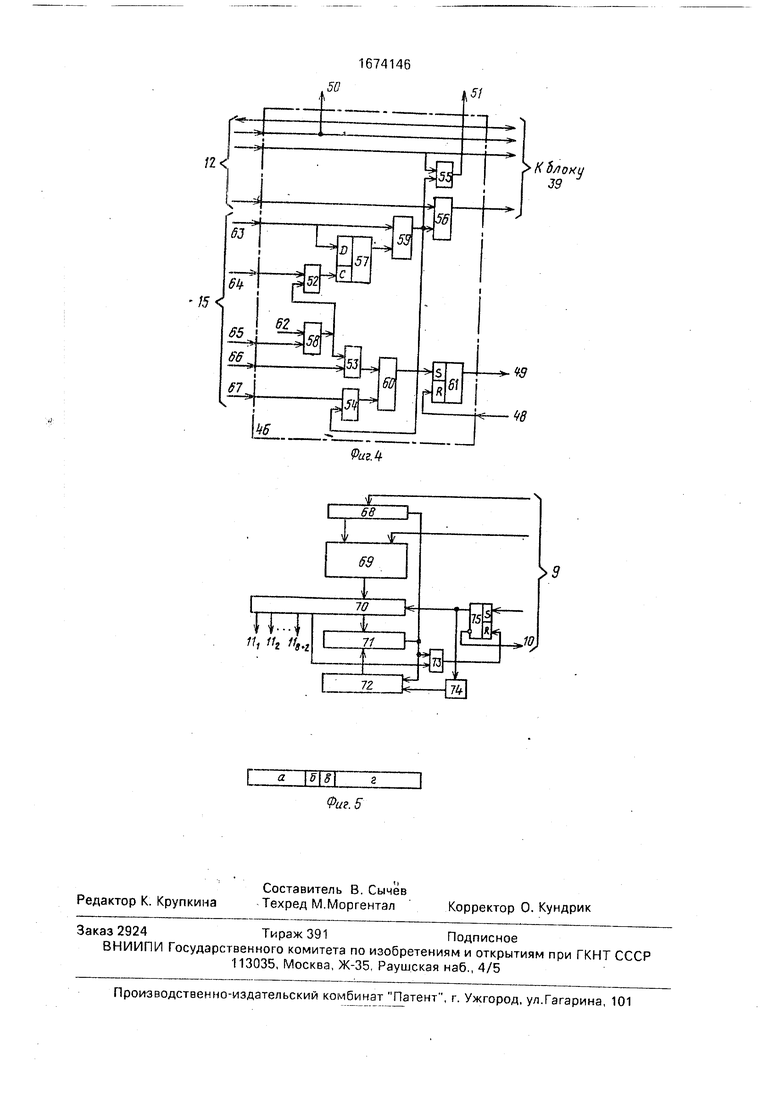

Формирователь 3 циклов содержит

(фиг. 5) счетчик 68 адреса, блок 69 памяти, группу элементов И 70, схему 71 сравнения, счетчик 72 тактов, элемент И 73, генератор 74 тактовых импульсов и триггер 75 пуска

0 Функционирование системы определяется управляющими программами, записанными в блок 24 памяти управляющего процессора 1. Решающее поле представляется в виде Р п (п - количество процессо5 ров) групп, процессоров 2 произвольной конфигурации, в каждом из которых может выполняться,собственная программа Каждый процессор группы помечается соответствующим номером группы. Управление

0 загрузкой и выгрузкой процессоров 2, загрузка номеров групп и распределение заданий по группам процессоров осуществляется управляющим процессором.

Цикл задачи задается формирователем

5 циклов. При выходе из строя любого из процессоров 2 обеспечивается передача задачи, решаемой на нем на другие процессоры 2. Осуществляется это управляющим процессором 1 путем перезагрузки программ и

0 данных в другие процессоры (в блоки 39 памяти процессоров 2) по шинам 12,13 и 15. При этом меняется цикл решения задачи в исправных процессорах путем записи в формирователь 3 циклов новых кодов управ5 ляющим процессором 1.

Коммутаторы 5 и 6 соответственно предназначены для организации обмена между любыми из процессоров 2 и узлами обмена, организации произвольных меж0 процессорных обменов.

Устройство работает следующим образом.

Функционирование системы определяется управляющими программами, эаписан5 ными в блок 24 памяти управляющего процессора 1, загрузка и обмен информацией между управляющим процессором 1 и процессорами осуществляется по шинам 12,13,15. В соответствии с распределением

0 оесурсов все решающее поле разбивается на группы процессоров 2. Каждый процессор группы загружается соответствующим номером группы. Для этого управляющим процессором 1 по шине 65 устанавливает5 ся двоичный код номера процессора 2, который поступает на второй вход схемы сравнения 58, а по входу 62;установлен физический номер процессора 2 (зашит на разъеме). По сигналу записи, выдаваемому по шине 64, осуществляется запись кода

номера группы в регистр 57, поступающего по шине 63, в том интерфейсном блоке 46, где сработала схема сравнения 58. Инициация работы процессоров может осуществляться как от управляющего процессора 1 по шине 15, так и от формирователя циклов. При этом возможен запуск процессоров 2 как по номеру процессора, так и по номеру группы.

Запуск по номеру процессора осуществляется следующим образом.

По шине 65 выдается номер процессора 2, при этом срабатывает соответствующая схема сравнения 58 и по сигналу запуска по шине 66 устанавливается в единичное состояние триггер 61 блока управления процессора. Запуск группы процессоров осуществляется выдачей по шине 63 кода номера группы, при этом срабатывают соответствующие схемы сравнения 59 в интерфейсных блоках 46, принадлежащих данному номеру группы. По сигналу запуска, поступающему по шине 67, устанавливается в единичное состояние триггер 61.

После включения вычислительной системы управляющим процессором 1 производится установка и исходное состояние системы и осуществляется загрузка процессоров 2 и формирователя 3 циклов. Загрузка формирователя 3 циклов осуществляется следующим образом; по первой группе разрядов шины 9 на регистре 68 устанавливается первый адрес блока 69 памяти, по второй группе разрядов шины 9 посылается управляющий код. Управляющий код (фиг. 5) состоит из четырех полей: поле а предназначено для хранения двоичных кодов номеров групп процессоров 2 и содержит I разрядов (где I Iog2 п); поле б содержит один разряд и предназначено для запуска процессоров 2 по номеру групп процессоров 2; поле в содержит один разряд и предназначено для останова формирователя 3 циклов по окончанию формирования цикла решения задачи; поле г предназначено для хранения двоичных кодов циклов работы соответствующих групп процессоров 2.

Загрузка группы процессоров 2 одинаковыми программами в одноименные участки памяти осуществляется следующим образом.

Управляющим процессором 1 по шине 15 (63) выставляется номер группы процессоров, при этом срабатывают схемы 59 сравнения в соответствующих интерфейсных блоках 46. Далее по третьей группе разрядов шины 12 устанавливается сигнал разрешения, а по первой и второй группам разрядов шины 12 устанавливаются соответственно адрес и сигнал записи. Затем по шине 13 данных осуществляется загрузка блоков памяти 39 соответствующих процессоров 2.

5Инициация работы процессоров 2 происходит от управляющего процессора 1 как путем подачи сигналов по шине 15, так и путем запуска формирователя циклов 3 по третьей группе разрядов шины 9.

0Формула изобретения

5 обмена, коммутатор внешних обменов, коммутатор межпроцессорных обменов, причем 1-й информационный вход-выход устройства (I 1...п) через 1-й узел обмена подключен к i-му информационному входу0 выходу коммутатора внешних обменов, 1-й информационный выход-вход которого соединен с информационным входом-выходом внешнего обмена i-ro процессора, вход настройки коммутатора межпроцессорных об5 менов подключен к выходу управления межпроцессорным обменом управляющего процессора выход управления внешним обменом которого соединен с управляющим входом коммутатора внешних обменов, ин0 формационный вход-выход межпроцессорного обмена 1-го процессора подключен к 1-му информационному выходу-входу коммутатора межпроцессорных обменов, выход задания режима управляющего

5 процессора подключен к входу управления формирователя циклов, выход подтверждения завершения цикла которого подключен к входу контроля режима управляющего процессора, выход запуска формирователя

0 циклов соединен с входом одиночного запуска i-ro процессора, выход адреса управляющего процессора подключен к входу адреса 1-го процессора, выход-вход данных управляющего процессора соединен с вхо5 дом-выходом данных 1-го процессора, вход контроля состояния управляющего процессора подключен к выходу контроля состояния 1-го процессора, каждый 1-й процессор содержит блок управления, ком0 мутатор, блок памяти, сумматор, блок регистров общего назначения, регистр признака результата, регистр состояния, дешифратор микрокоманд, при этом информационный вход-выход внешнего обмена процессора и

5 информационный вход-выход межпроцессорного обмена процессора являются соответствующими входами-выходами коммутатора, выход-вход которое .юдклю- чен к входу-выходу блока памяти, выход контроля состояния процессора является

выходом регистра состояния, выход микрокоманд блока управления соединен с входом дешифратора микрокоманд, выхо.д которого соединен с входами управления коммутатора, сумматора и входом записи регистра признака результата, выход которого подключен к соответствующему входу блока управления, выход адреса команд блока управления соединен с входом адреса команд блока памяти, выход команд которого подключен к входу команд блока управления, вход-выход первого слагаемого сумматора соединен с одноименным выходом-входом блока.памяти, вход-выход второго слагаемого сумматора соединен с одноименным выходом-входом блока регистров общего назначения, выход сумматора подключен к информационным вход ам регистров состояния и признака результата, отличающееся тем, что, с целью повышения производительности вычислительной системы, в i-й процессор, введены группа элементов ИЛИ и интерфейсный блок, причем дополнительный вход группового запуска 1-го процессора подключен к выходу группового запуска управляющего процессора, входы одиночного запуска и входы группового запуска 1-го процессора подключены к первым и вторым входам элементов ИЛИ группы соответственно, выходы которых соединены с соответствующими разрядами входа инициации работы процессора интерфейсного блока, адресный вход и вход-выход данных процессора подключены к одноименному входу и входу-выходу интерфейсного блока, вход сброса которого соединен с выходом дешифратора микрокоманд, выход пуска-останова интерфейсного блока подключен к входу запуска блока управления, выход текущего адреса команд и выход записи в регистр текущего адреса команд интерфейсного блока соединены с информационным входом и входом записи регистра текущего адреса команд блока управления соответственно, выход записи в блок памяти и выход-вход данных интерфейсного блока подключены к одноименным входу и входу-выходу блока памяти.

пять элементов И, регистр номера группы процессоров, схему сравнения номера процессора и схему сравнения номера группы процессоров, элемент ИЛИ и триггер пуска- останова, причем соответствующие разряды входа инициации работы процессора интерфейсного блока подключены к информационному входу регистра номера группы процессоров и к первому входу схемы сравнения номера группы процессоров, к первым входам первого, второго и третьего элементов И и к входу схемы сравнения номера процессора, соответствующие разряды адресного входа интерфейсного блока подключены к выходу текущего адреса команд

и выходу записи в блок памяти интерфейсного блока, к первым входам четвертого и пятого элементов И, вход-выход данных интерфейсного блока является его информационным выходом-входом, выход записи в

регистр текущего адреса команд интерфейсного блока является выходом четвертого элемента И, выход пятого элемента И подключен к соответствующему разряду выхода записи блока памяти интерфейсного

блока, выход пуска-останова интерфейсного блока является выходом триггера пуска- останова, а вход сброса интерфейсного блока - входом сброса триггера пуска-останова, выход первого элемента И подключен

к входу установки регистра номера группы процессоров, выход которого соединен с вторым входом схемы сравнения номера (руппы процессоров, выход которой подключен к вторым входам третьего, четвертого и пятого элементов И, выход которой подключен к второму входу первого элемента И и второму входу второго элемента И, выход которого соединен с первым входом элемента ИЛИ, выход третьего элемента И,

подключен к второму входу элемента ИЛИ, выход которого соединен с входом установки триггера пуска-останова.

Puz.J

Фиг. 2

11

4

63

6k

15

62

fLr

I-J SO

k..

К блоки J9

SB

53

Г

61

W 48

Авторы

Даты

1991-08-30—Публикация

1987-10-02—Подача