Изобретение относится к технике автоматизированных систем управления, а точнее к устройствам передачи данных и может найти применение при обмене информацией между удаленными автоматизированными рабочими местами (АРМи).

Известно устройство для выбора канала с экстремальным средним напряжением [1]. Устройство содержит N каналов, в которые входят интегрирующий блок, ключ, компаратор и триггер, а также совокупность управляющих элементов. Сущность работы данного устройства заключается в обеспечении формирования сигнала "Оценка" в случаях, когда достоверность выбора канала с экстремальным средним напряжением меньше заданной, и в формировании сигнала степени достоверности выбора этого канала. Данное устройство имеет следующие недостатки:

работа устройства осуществляется в режиме индикации (не осуществляет автоматическую коммутацию каналов);

узкая область применения (аналог приемлем только для систем, в которых осуществляется аналоговая обработка сигналов).

Наиболее близким по технической сущности и выполняемым функциям к предлагаемому устройству является устройство для автоматического переключения каналов связи по авт. св. СССР N 1826136, кл. H 04 L 12/12 от 7.07.93 [2].

Устройство содержит первые коммутаторы, первый, второй входы которых являются входами устройства, первые выходы которого через последовательно соединенные приемники информации и блоки контроля, первые выходы которых являются выходами устройства, а вторые выходы блока контроля соединены с первыми входами элемента запрета, выходы которых соединены с первыми входами регистров, первые выходы которых соединены с третьими входами первых коммутаторов, вторые выходы которых соединены с первыми входами вторых коммутаторов, первые выходы которых через последовательно соединенные контрольный приемник и дополнительный блок контроля соединены с вторыми входами вторых коммутаторов, третьи входы которых соединены с вторыми выходами регистров, соединенных также с входами элемента ИЛИ, выход которого соединен с первым входом дополнительного элемента запрета, второй вход которого и вторые входы регистров соединены с выходом генератора импульсов. Выход дополнительного элемента запрета соединен с входом кольцевого регистра. Выходы кольцевого регистра соединены с входами блока элементов запрета, управляющий вход которого соединен с выходом элемента ИЛИ, выходы блока элементов запрета присоединены к четвертым входам вторых коммутаторов, вторые выходы которых соединены с первыми входами дополнительных элементов ИЛИ. Вторые выходы регистров соединены с вторыми входами дополнительных элементов ИЛИ, кроме последнего. Выходы дополнительных элементов ИЛИ соединены с вторыми входами элементов запрета.

Данное устройство в зависимости от качества каналов связи осуществляет автоматическую коммутацию. Качество канала определяется по статическим характеристикам принимаемой информации.

Недостатком прототипа является относительно невысокое качество контроля, которое обусловлено неоднозначностью сравнения основного и резервного каналов, из-за отсутствия анализа полученной информации о качестве каждого канала, кроме того, не учитывается интервал времени определения качества резервного канала.

Технической задачей изобретения является разработка устройства автоматической коммутации каналов связи, обеспечивающего более качественный контроль качества каналов связи, который достигается за счет ввода блока сравнения и регулирующего элемента.

Техническая задача достигается тем, что в известное устройство автоматической коммутации каналов связи, содержащее k линейных узлов, где k =2, 4, 6, ... четное число, входы основного и резервного каналов i-го линейного узла, где i = 1,...,k являются соответственно i-ми входами основного и резервного каналов устройства, а информационный выход i-го линейного узла является i-м информационным выходом устройства, кольцевой регистр, k выходов которого подключены к соответствующим k входам блока элементов запрета, i-й управляющий выход которого соединен с входом "выбор узла" i-го линейного узла, а запрещающий вход блока элементов запрета подключен к входу дополнительного элемента запрета и выходу элемента ИЛИ, выход дополнительного элемента запрета соединен с входом кольцевого регистра, первый вход элемента ИЛИ подключен к блокирующим входам каждого (2j-1)-го и блокирующим выходам каждого (2j)-го линейных узлов, где j = 1, 2, ... k/2, а второй вход элемента ИЛИ подключен к блокирующим выходам каждого (2j-1)-го и блокирующим входам каждого (2j)-го линейных узлов, синхронизирующий вход каждого линейного узла подключен к выходу тактового генератора, к которому также подключен тактовый вход дополнительного элемента запрета, а контрольные выходы линейных узлов подключены к входу контрольного приемника, выход которого подключен к входу дополнительного блока контроля, выход которого соединен с контрольными входами всех линейных узлов, дополнительно введен регулирующий элемент. Выход регулирующего элемента соединен со входом тактового генератора. Тактовый вход дополнительного блока контроля соединен с выходом тактового генератора. Каждый i-й линейный узел состоит из входного коммутатора, первый и второй входы которого являются входами основного и резервного каналов линейного узла, а управляющий вход входного коммутатора подключен к первому управляющему выходу регистра. Второй управляющий выход регистра подключен к управляющему входу контрольного коммутатора и является одновременно блокирующим выходом линейного узла. Тактовый вход регистра является синхронизирующим входом линейного узла и соединен с тактовым входом блока контроля. Информационный вход регистра подключен к выходу элемента запрета. Управляющий и информационные входы которого подключены соответственно к выходу блока сравнения и выходу дополнительного элемента ИЛИ. Вход дополнительного элемента ИЛИ является блокирующим входом линейного узла. Контрольный вход дополнительного элемента ИЛИ подключен к контрольному выходу контрольного коммутатора. Контрольный вход контрольного коммутатора соединен с первым информационным входом блока сравнения и является контрольным входом линейного узла. Информационный выход контрольного коммутатора является контрольным выходом линейного узла. Информационный вход контрольного коммутатора подключен к второму выходу входного коммутатора. Первый выход входного коммутатора подключен к приемнику информации, который каскадно соединен с блоком контроля, цифроаналоговым преобразователем, причем выход цифроаналогового преобразователя является информационным выходом линейного узла. Второй информационный выход блока контроля подключен к второму информационному входу блока сравнения. Исполнительный вход контрольного коммутатора является входом "выбор узла" линейного узла.

Благодаря новой совокупности существенных признаков за счет введения блока сравнения устраняется неоднозначность сравнения качества основного и резервного канала связи, вследствие этого более качественно осуществляется контроль, кроме того, ввод регулирующего элемента позволил учитывать интервал времени определения качества резервного канала.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественными всеми признаками заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности "новизна". Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

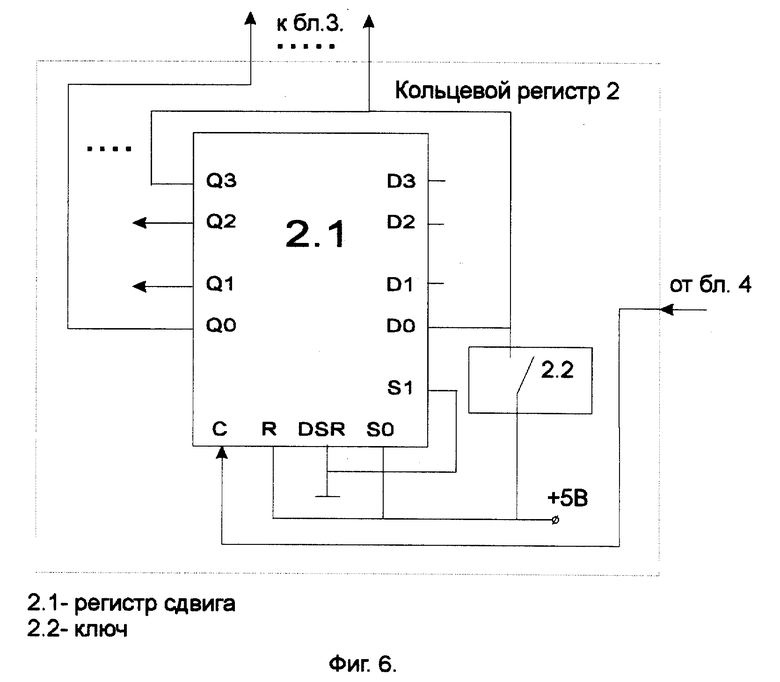

Заявленное устройство поясняется схемами:

фиг. 1 - структурная схема устройства;

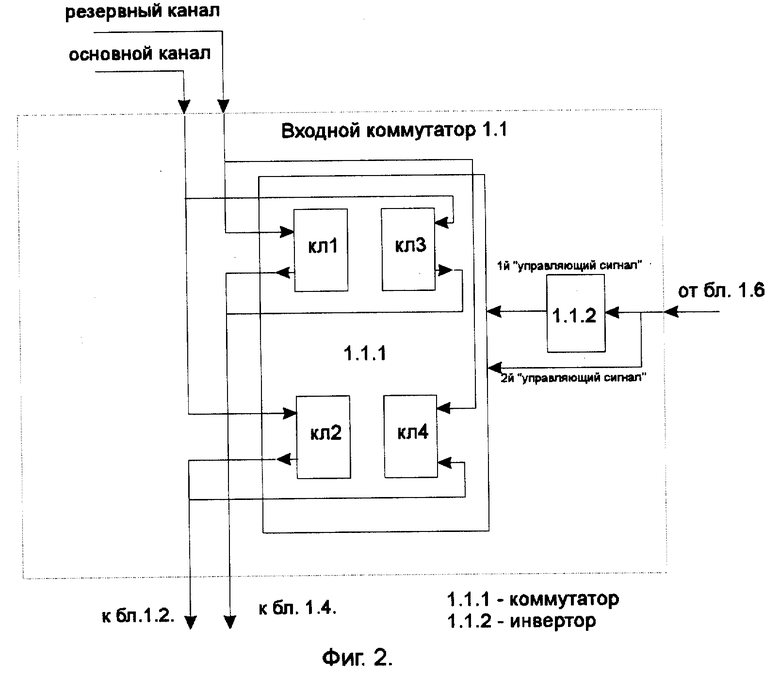

фиг. 2 - схема входного коммутатора;

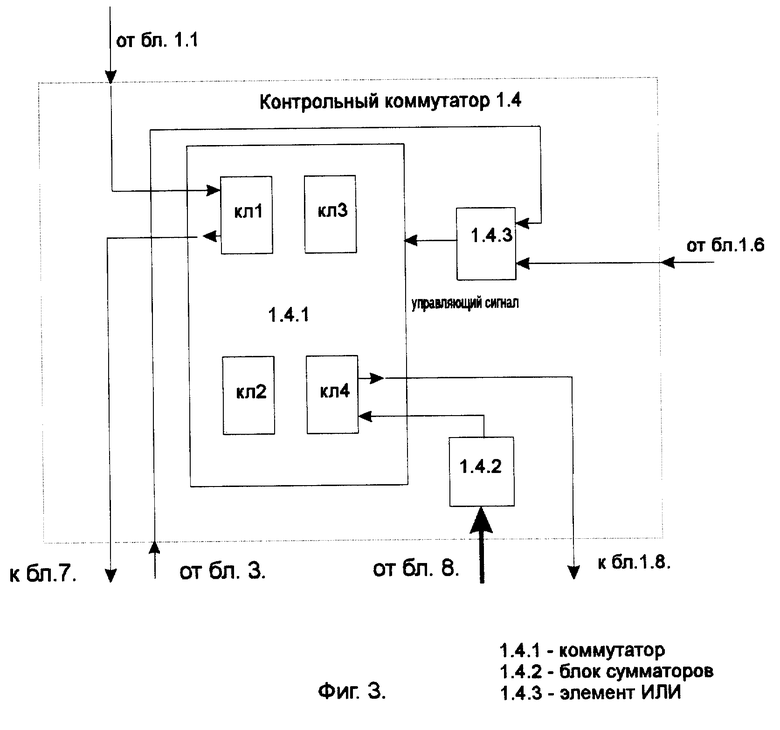

фиг. 3 - схема контрольного коммутатора;

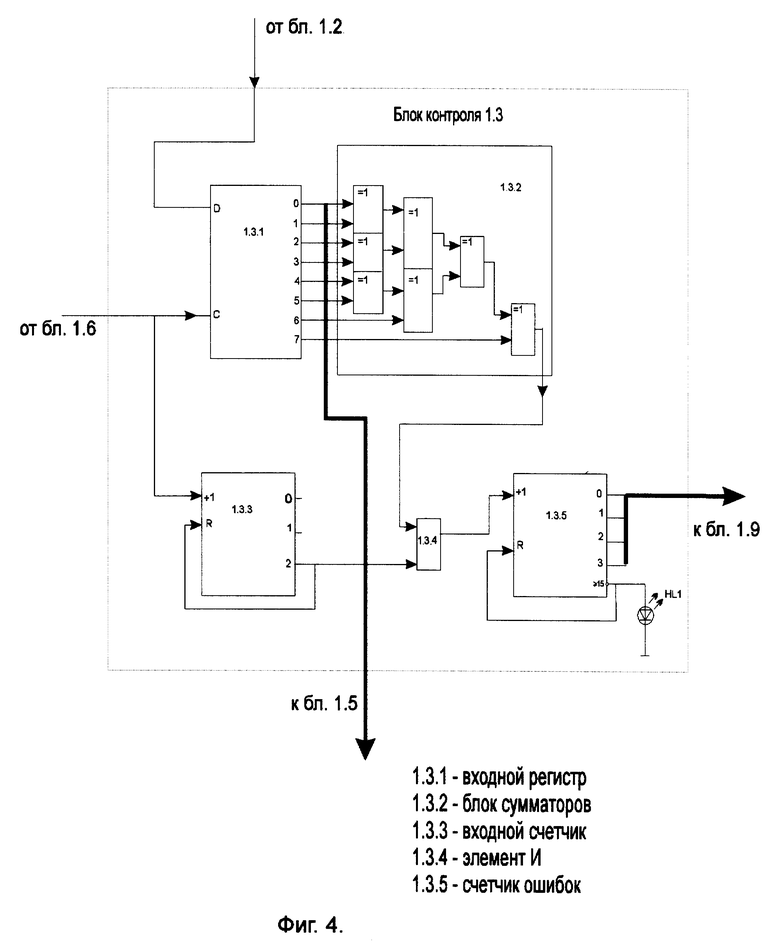

фиг. 4 - схема блока контроля;

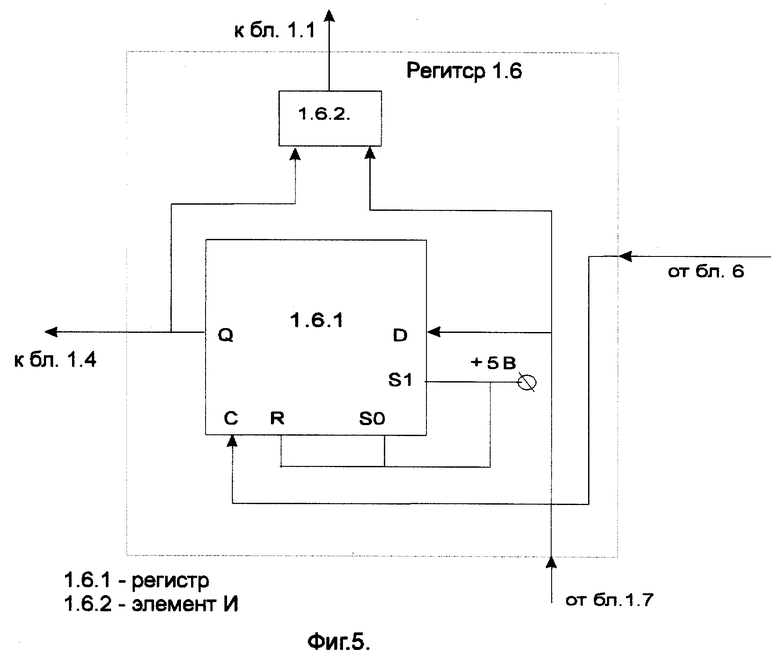

фиг. 5 - схема регистра;

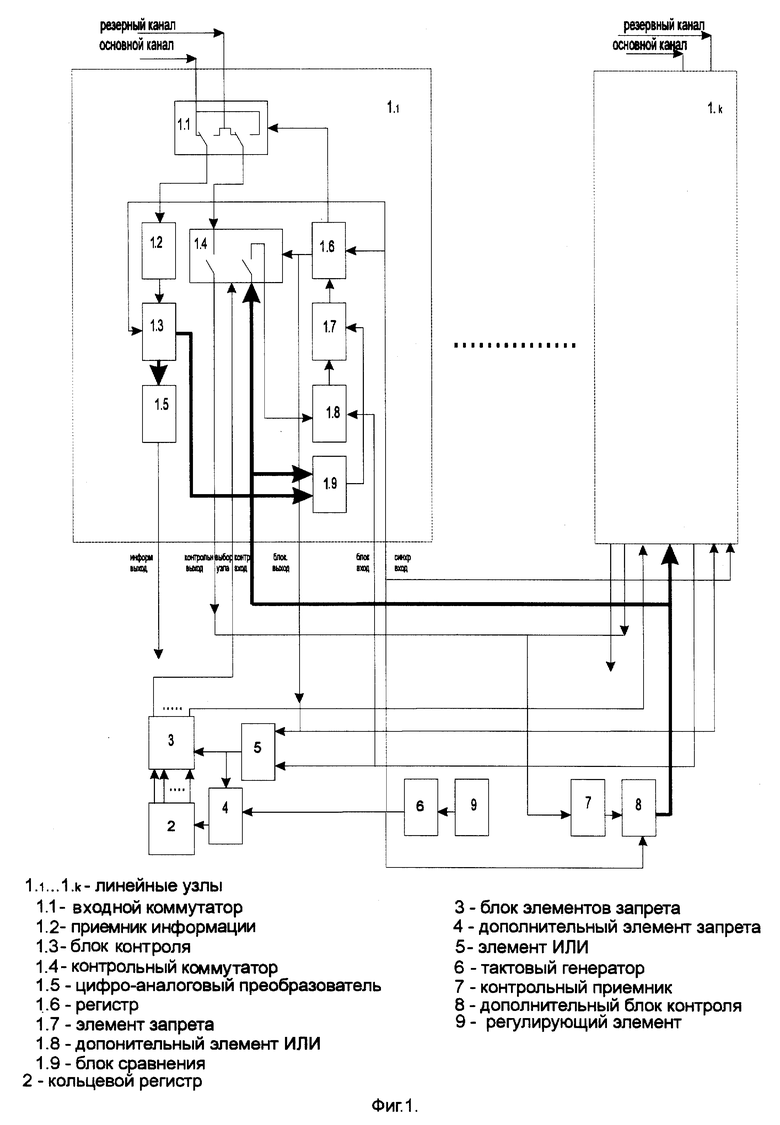

фиг. 6 - схема кольцевого регистра.

Заявленное устройство, структурная схема показана на фиг. 1, состоит из k-линейных узлов 1i-1k, где k = 2, 4, 6.., четное число, кольцевой регистр 2, блок элементов запрета 3, дополнительный элемент запрета 4, элемент ИЛИ 5, тактовый генератор 6, контрольный приемник 7, дополнительный блок контроля 8 и регулирующий элемент 9.

Входы основного и резервного каналов каждого из линейных узлов 1i-1k являются соответствующими основными и резервными входами устройства. Информационные выходы линейных узлов является выходами устройства. Выходы кольцевого регистра 2 подключены к соответствующим входам блока элемента запрета 3. Управляющие выходы блока элементов запрета 3 соединены с входами "выбор узла" соответствующих линейных узлов. Запрещающий вход блока элементов запрета 3 соединен с входом дополнительного элемента запрета 4 и с выходом элемента ИЛИ 5. Выход дополнительного блока запрета 4 соединен с входом кольцевого регистра 2. Первый вход элемента ИЛИ 5 соединен с блокирующими входами каждого (2j-1)-го и с блокирующими выходами каждого (2j)-го линейных узлов, где j = 1, 2, ... k/2. Второй вход элемента ИЛИ 5 соединен с блокирующими выходами каждого (2j-1)-го и с блокирующими входами каждого (2j)-го линейных узлов, где j = 1, 2, ... k/2. Синхронизирующий вход каждого линейного узла соединен с выходом тактового генератора 6 и тактовым входом дополнительного элемента запрета 4. Контрольные выходы линейных узлов 1i-1k подключены к входу контрольного приемника 7. Выход контрольного приемника 7 подключен к входу дополнительного блока контроля 8 Выход дополнительного блока контроля 8 соединен шиной из четырех проводников с контрольными входами всех линейных узлов 1i-1k. Выход регулирующего элемента 9 соединен с входом тактового генератора 8. Тактовый вход дополнительного блока контроля 8 соединен с выходом тактового генератора 6.

Все линейные узлы 1i-1k идентичны, а входящие в них элементы одинаковы. В состав каждого линейного узла входят входной коммутатор 1.1, приемник информации 1.2, блок контроля 1.3, контрольный коммутатор 1.4, цифроаналоговый преобразователь 1.5, регистр 1.6, элемент запрета 1.7, дополнительный элемент ИЛИ 1.8, блок сравнения 1.9. Первый и второй входы входного коммутатора 1.1 являются входами основного и резервного каналов линейного узла. Управляющий вход входного коммутатора 1.1 соединен с первым управляющим выходом регистра 1.6. Второй управляющий выход регистра 1.6 подключен к управляющему входу контрольного коммутатора 1.4 и является одновременно блокирующим выходом линейного узла 1i-1k. Тактовый вход регистра 1.6 является синхронизирующим входом линейного узла 1i-1k и соединен с тактовым входом блока контроля 1.3. Информационный вход регистра 1.6 соединен с выходом элемента запрета 1.7. Информационный вход элемента запрета 1.7 подключен к выходу дополнительного элемента ИЛИ 1.8. Управляющий вход элемента запрета 1.7 подключен к выходу блока сравнения 1.9. Вход дополнительного элемента ИЛИ 1.8 является блокирующим входом линейного узла 1i-1k. Контрольный вход дополнительного элемента ИЛИ 1.8 подключен к контрольному выходу контрольного коммутатора 1.4. Контрольный вход контрольного коммутатора 1.4 является шиной из четырех проводников и соединен с первым информационным входом блока сравнения 1.9 и является контрольным входом линейного узла 1i-1k. Информационный выход контрольного коммутатора 1.4 является контрольным выходом линейного узла 1i-1k. Информационный вход контрольного коммутатора 1.4 подключен к второму выходу входного коммутатора 1.1. Первый выход входного коммутатора 1.1 подключен к входу приемника информации 1.2. Выход приемника информации 1.2 подключен к информационному входу блока контроля 1.3. Первый информационный выход блока контроля 1.3 соединен шиной из восьми проводников с входом цифроаналогового преобразователя 1.5. Выход цифроаналогового преобразователя 1.5 является информационным выходом линейного узла 1i-1k. Второй информационный выход блока контроля 1.3 соединен шиной из четырех проводников с вторым информационным входом блока сравнения 1.9. Исполнительный вход контрольного коммутатора 1.4 является входом "выбор узла" линейного узла.

Входной коммутатор 1.1 предназначен для переключения входных информационных потоков и управляющих сигналов. Он может быть реализован по известным схемам, в частности, по схеме четырех канального коммутатора, показанной на фиг. 2. Входной коммутатор 1.1 состоит из коммутатора 1.1.1, содержащего первый кл. 1, второй кл. 2, третий кл.3, четвертый кл.4 ключи и инвертор 1.1.2. Входы первого ключа кл.1 и второго ключа кл.2 являются соответственно первым и вторым входами входного коммутатора 1.1. Вход первого ключа кл.1 соединен с входом четвертого ключа кл.4, а вход второго ключа кл.2 соединен с входом третьего ключа кл.3. Выход первого ключа кл.1 соединен с выходом третьего ключа кл.3, а выход второго ключа кл.2 соединен с выходом четвертого ключа кл. 4. Выходы первого ключа кл.1 и второго ключа кл.2 являются соответственно первым и вторым выходами входного коммутатора 1.1. Вход инвертора 1.1.2 является управляющим входом входного коммутатора 1.1 и подключается к второму входу "управляющий сигнал" коммутатора 1.1.1, а выход инвертора подключается к первому входу "управляющий сигнал" коммутатора 1.1.1. Первый вход "управляющий сигнал" коммутатора 1.1.1 подключен к исполнительным элементам первого ключа кл.1 и второго ключа кл.2 (на фиг. 2 не показано). Второй вход "управляющий сигнал" коммутатора 1.1.1 подключен к исполнительным элементам третьего ключа кл.3 и четвертого ключа кл.4 (на фиг. 2 не показано). Описанная схема входного коммутатора может быть реализована на микросхеме К174КТ1 [3].

Приемники 1.2,7 предназначен для приема и преобразования информации из аналогового сигнала в цифровой вид. Их схемы построения известны и описаны, например, в работе [4].

Блок контроля 1.3 предназначены для определения в данных ошибок. Реализовать его возможно различным способом, например, с помощью совокупности счетчиков, регистра и блока сумматоров. Схема блока контроля 1.3 представлена на фиг. 4. Он состоит из входного регистра 1.3.1, блока сумматоров 1.3.2, входного счетчика 1.3.3, элемент И 1.3.4, счетчика ошибок 1.3.5 и светодиода HL1. Вход ("D") входного регистра 1.3.1 является информационным входом блока контроля 1.2. Вход ("C") входного регистра 1.3.1 соединен с входом ("+1") входного счетчика 1.3.3 и является тактовым входом блока контроля 1.3. Вход ("R") входного счетчика 1.3.3 соединен с его выходом ("2") и с вторым входом элемента И 1.3.4. Выходы ("0-7") входного регистра 1.3.1 образуют общую шину из восьми проводников, которая соединена с входами блока сумматоров 1.3.2 и является первым информационным выходом блока контроля 1.3. Выход блока сумматоров 1.3.2 соединен с первым входом элемента И 1.3.4. Выход элемента 1.3.4 соединен с входом ("+1") счетчика ошибок 1.3.5, а его вход ("R") соединен с его выходом (">15") и с световым индикатором например, в виде светодиода HL1. Выходы ("0-3") счетчика ошибок 1.3.5 образуют общую шину из четырех проводников, которая является вторым информационным выходом блока контроля 1.3. Блок сумматоров 1.4.2 выполняется стандартным образом, который подробно изложен на стр. 57 в [3].

Схема дополнительного блока контроля 8 может быть реализована аналогично схеме блока контроля 1.3, но так как дополнительный блок контроля 8 снабжен одним информационным выходом, то соответственно выходы ("0-7") входного регистра в схеме дополнительного блока контроля 8 подключены только к входам блока сумматоров 1.3.2.

Контрольный коммутатор 1.4 предназначен для переключения информационных потоков и управляющих сигналов. Реализовать его возможно по различным схемам, в частности по схеме четырех канального коммутатора, показанной на фиг. 3. Контрольный коммутатор состоит из коммутатора 1.4.1, блока сумматоров 1.4.2, элемента ИЛИ 1.4.3. Схема коммутатора 1.4.1 аналогична схеме коммутатора 1.1.1, отличие состоит лишь в том, что задействовано только первый кл. 1 и четвертый кл.4 ключи. Блок сумматоров 1.4.2 выполняется стандартным образом, который подробно изложен на стр. 57 в [3]. Вход первого ключа кл.1 коммутатора 1.4.1 является информационным входом контрольного коммутатора 1.4, а выход первого ключа кл.1 коммутатора 1.4.1 является информационным выходом контрольного коммутатора 1.4. Первый вход элемента ИЛИ 1.4.3 является исполнительным входом контрольного коммутатора 1.4. Второй вход элемента ИЛИ 1.4.3 является управляющим входом контрольного коммутатора 1.4. Выход элемента ИЛИ 1.4.3 соединен с входом "управляющий сигнал" коммутатора 1.4.1. Вход "управляющий сигнал" подключен к исполнительным элементам первого ключа кл.1 и четвертого ключа кл.4 (на фиг. 3 не показано). Входы блока сумматоров 1.4.2. являются (шина из четырех проводников) контрольным входом контрольного коммутатора 1.4. Выход блока сумматоров 1.4.2 соединен с входом четвертого ключа кл.4, выход которого является контрольным выходом контрольного коммутатора 1.4.

Цифроаналоговый преобразователь 1.5 предназначен для преобразования информации из цифрового в аналоговый вид. Его схема построения известна и описана, например, в работе [5].

Регистр 1.6 предназначен для временного хранения информации под действием которой осуществляется переключение коммутаторов 1.1 и 1.4. Реализовать его возможно различно, например на базе микросхем. Схема регистра представлена на фиг. 6. Он состоит из регистра хранения 1.6.1 и элемента И 1.6.2. Вход ("C") регистра 1.6.1 является тактовым входом регистра 1.6. Вход ("D") регистра 1.6.1 является информационным входом регистра 1.6 и соединен с первым входом элемента И 1.6.2. Выход ("Q") регистра 1.6.1 является вторым управляющим выходом регистра 1.6 и соединен с вторым входом элемента И 1.6.2. Входы ("R"), ("S0") и ("S1") регистра 1.6.1 соединены с +5В. Выход элемента И 1.6.2 является первым управляющим выходом регистра 1.6.

Блок сравнения 1.9 предназначен для сравнения информации, поступающей от блока контроля 1.3 и дополнительно блока контроля 8. Это осуществить возможно любым способом, например, с помощью микросхемы К155ИП2. Она предназначена для проверки принимаемых данных на четность. Ее схема и описание работы представлены на стр. 171 в [3].

Кольцевой регистр 2 предназначен по импульсам, вырабатываемым тактовым генератором 6, производить периодическое подключение резервных каналов к контрольному приемнику. Он может быть реализован различным способом, например на микросхемах. Его схема представлена на фиг. 5. Кольцевой регистр состоит из регистра сдвига 2.1 и ключа 2.2, который необходим для записи в первоначальный момент времени "1" в младший разряд регистра сдвига 2.1. Реализовать ключ 2.2 возможно любым способом, например с помощью выключателя типа Д701. Вход ("D0") регистра сдвига 2.1 соединен с его выходом ("Q3"). Выходы ("Q0-Q3") регистра сдвига 2.1. являются соответствующими выходами кольцевого регистра 2. Вход "C" регистра сдвига 2.1 является входом кольцевого регистра 2. Входы ("R") и ("S0") регистра сдвига 2.1 и второй контакт ключа 2.2 соединены с +5В. Входы ("S1") и ("DSR") регистра сдвига 2.1 соединены с корпусом.

Тактовый генератор 6 предназначен для выработки тактовых импульсов, под управлением которых осуществляется синхронизация регистров, блоков контроля и дополнительного блока контроля. Схемы построения тактового генератора 6 известны и описаны, например, в работе на стр. 50 рис. 1.30а, в [3].

Элемент запрета 1.7, дополнительный элемент ИЛИ 1.8, блок элементов запрета 3, дополнительный элемент запрета 4, элемент ИЛИ 5 реализованы могут быть различным способом, например, на микросхемах К155ЛП11 и К155ЛЛ1, схемы которых представлены на соответствующих стр. 31 и 46, рис. 1.15в и 1.27з в [3].

Регулирующий элемент 9 необходим для регулировки тактовой частоты задающего генератора 6 и представляет собой резистор с переменным сопротивлением 0-50 мОм. Регулирующий элемент 9 подключается последовательно с резистором R1 тактового генератора 6 (см. стр. 50 рис. 1.30а в [3]).

Работает данное устройство следующим образом.

Данные, поступившие по основным каналам на первые входы входных коммутаторов 1.1, через соответствующие ключи коммутатора 1.1.1 поступает на соответствующие приемники информации 1.2. Данная процедура осуществляется посредством сигнала от регистра 1.6, который проходит через инвертор 1.1.2 на первый вход "управляющий сигнал" коммутатора 1.1.1 (см. фиг. 2). Приемники информации 1.2 осуществляют прием и преобразование данных. Это происходит аналогично, что и в приемнике двоичных сигналов, см. [4], исключение состоит лишь в том, что не используется сигнал "начальная установка". Далее, информация с выходов приемника поступает на соответствующие блоки контроля 1.3, где осуществляют ее накопление до байта и постоянный контроль. Это осуществляется следующим образом (см. фиг. 4). Данные последовательно поступают на вход ("D") входного регистра 1.3.1, который работает в режиме сдвига. Накопление осуществляется под действием тактовых импульсов от регистра 1.6, которые одновременно поступают на вход ("C") входного регистра 1.3.1 и на вход ("+1") входного счетчика 1.3.3, который "считает" до восьми. Если входной счетчик 1.3.3 досчитал до восьми, то происходит его сброс, посредством подачи сигнала с его выхода (2) на его вход ("R"). При этом на выходах (0-7) входного регистра 1.3.1 находится байт информации, который одновременно поступает на цифроаналоговый преобразователь 1.5 и на блок сумматоров 1.3.2. Блок сумматоров складывает по модулю два полученный байт. Следовательно, на выходе блока сумматоров 1.3.2 получается контрольная сумма принятого байта, если ее значение рано "0", то байт принялся правильно, если "1", то с ошибкой. При ошибке, значение "1" от блока сумматоров 1.3.2 поступает на первый вход элемента И 1.3.4, а на второй вход сигнал "1" с выхода (2) входного счетчика 1.3.3, в результате значение счетчика ошибок 1.3.5 увеличивается на единицу. Если байт принялся без ошибки, то на выходе элемента 1.3.4 находится "0" и значение счетчика ошибок 1.3.5 не изменится. При значение счетчика ошибок 1.3.5, равном 16 (счетчик считает от 0 до 15), на выходе счетчика (>15) появляется сигнал, который одновременно устанавливает счетчик ошибок 1.3.5 в начальное состояние, посредством подачи сигнала с его выхода (3) на его вход ("R") и уведомляет обслуживающий персонал посредством светового индикатора HL1. На выходах (0-3) счетчика ошибок 1.3.5 в любой момент времени находится значение числа байт принятых с ошибкой.

Данные, уже побайтно (параллельно), поступают с выходов (0-7) входного регистра на цифроаналоговый преобразователь 1.5, который осуществляет преобразование байта данных из цифрового вида в аналоговый. Данное преобразование осуществляется аналогично работе цифроаналогового преобразователя, изложенной в [5] . Далее, преобразованные данные через информационный выход, поступают потребителю информации.

Одновременно с этим данные, поступают по дублирующим каналам через соответствующие ключи коммутатора 1.1.1, и подаются на соответствующие контрольные коммутаторы 1.4, в которых с помощью кольцевого регистра 2 производится периодическое подключение дублирующих каналов через контрольный выход к контрольному приемнику 7. Это проходит следующим образом. Тактовые импульсы от тактового генератора 6, через дополнительный элемент запрета 4, поступают на кольцевой регистр 2. Под действием тактовых импульсов регистр сдвига 2.1 работает в режиме "бегущая единица". Предварительно в младший разряд D0 регистра сдвига 2.1 с помощью ключа 2.2 записывается логическая единица "1". Данная логическая единица через блок элементов запрета 3 поступает на вход "выбор узла" соответствующего линейного узла, где подключает соответствующий коммутатор 1.4.1 через управляющий сигнал элемента ИЛИ 1.4.3, контрольный выход каждого линейного узла к контрольному приемнику.

Контрольный приемник осуществляет прием и преобразование данных, аналогично приемникам 1.2 (только периодически).

Сигнал неисправности какого-либо линейного узла вырабатывается в соответствующем блоке контроля 1.3, в случае, если пришло N байтов (эмпирическое значение, которое устанавливается с помощью регулирующего элемента 9) с ошибкой. Значение числа байт, принятого с ошибкой из счетчика ошибок 1.3.5 выходы (0-3), поступает на первый вход блока сравнения 1.9, на второй вход поступает сигнал от дополнительного блока контроля 8, который формируется следующим образом. Под действием тактовых импульсов от генератора 6 через элемент запрета 4, кольцевой регистр 2, блок элементов запрета 3 формируется сигнал, который подключает приемник 7 к резервному каналу и к дополнительному блоку контроля 8. Блок 8 определяет его качество аналогично блоку 1.3 (см. фиг. 4) и выдает значение числа байт, принятого с ошибкой на второй вход блока сравнения 1.9, и через контрольный вход линейного узла поступает на контрольный вход контрольного коммутатора 1.4, где данное значение суммируется благодаря блоку сумматоров 1.4.2 и через четвертый ключ кл.4, посредством элемента ИЛИ 1.4.3, поступает на контрольный вход дополнительного элемента ИЛИ 1.8, с выхода которого сигнал поступает на информационный вход элемента запрета 1.7 (при правильной работе дополнительного блока контроля значение соответствует "0"). Блок сравнения 1.9 определяет, какой канал имеет наилучшие характеристики, путем суммирования 8 бит (4 бита от 1.3 и 4 бита от 8). Если на выходе блока сравнения 1.9 находится "0", то качество основного канала лучше, чем резервного, и переключения не происходит, так как на управляющем входе элемента запрета 1.7 и на контрольном входе находятся "0", следовательно, осуществляется блокировка регистра 1.6. Если на выходе блока сравнения 1.9 находится "1", то данный сигнал через элемент запрета 1.7 поступает в регистр 1.6. Регистр 1.6 запрещает работу кольцевого регистра 2 по импульсам генератора с помощью сигнала, который поступает через элемент ИЛИ 5, элемент запрета 4 на блок элементов запрета 3. Кроме этого, сигнал с выхода регистра 1.6 блокирует работу других линейных узлов, воздействуя через соответствующие входы дополнительных элементов ИЛИ 1.8 и соответственно на элементы запрета 1.7 других блоков, и таким образом блокирует прием сигналов аварии от всех остальных блоков контроля 1.3 на период переключения каналов.

При неисправности основного канала и исправности дублирующего, регистр 1.6 формирует сигнал переключения, который поступает через элемент 1.6.2 на коммутатор 1.1.1, и посредством входа второй "управляющий сигнал" производится автоматическое переключение каналов. Основной канал становится резервным, а резервный основным, и эта процедура может последовательно повторяться. В случае неисправности основного и резервного каналов регистр 1.6 не выдает сигнал на переключение и автоматическое переключение каналов не производится.

С помощью регулирующего элемента 9 осуществляется регулировка устройства, при этом необходимо добиться минимального свечения световых индикаторов всех блоков контроля 1.3 и дополнительного блока контроля 8. Регулирование частоты можно осуществлять в пределах от 1 мГц до 1 Гц. Благодаря этому улучшается не только контроль, но и эффективность принимаемых данных.

По сравнению с прототипом предлагаемое техническое решение позволяет расширить область применения устройств для автоматического переключения каналов связи.

Источники информации

1. Авт. св. СССР N 1408539, кл. H 04 L 12/22.

2. Авт. св. СССР N 1826136, кл. H 04 L 12/12.

3. В. Шило. Популярные цифровые микросхемы: Справочник. - Челябинск: Металлургия, Челябинское отделение, 1988. - 352 с.

4. В. Солохин. Приемник двоичных сигналов. Радио, 1989, N 11, с. 32-34.

5. П. Полянский, Н. Ширковский. Электроника БК-0010 в системах управления технологическими объектами. Микропроцессорные средства и системы,1987, N4, с. 33.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1996 |

|

RU2107995C1 |

| СПОСОБ ОБСЛУЖИВАНИЯ ЗАПРОСОВ ПОЛЬЗОВАТЕЛЕЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ (ВАРИАНТЫ) | 1998 |

|

RU2140666C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

| УСТРОЙСТВО ДИАГНОСТИКИ СОСТОЯНИЯ СИСТЕМ СВЯЗИ | 1996 |

|

RU2103819C1 |

| АВТОМАТИЧЕСКОЕ УСТРОЙСТВО ОБХОДА ДЛЯ СЕТЕЙ СВЯЗИ | 1998 |

|

RU2133080C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2115165C1 |

| АВТОМАТИЧЕСКОЕ УСТРОЙСТВО ОБХОДА СЕТЕЙ СВЯЗИ | 2005 |

|

RU2298284C1 |

| ГЕНЕРАТОР РАВНОМЕРНО РАСПРЕДЕЛЕННЫХ СЛУЧАЙНЫХ ИМПУЛЬСОВ | 1996 |

|

RU2107941C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА РАДИОСТАНЦИЙ | 1994 |

|

RU2099868C1 |

Изобретение относится к технике автоматизированных систем управления, а точнее к устройствам передачи данных и может найти применение при обмене информацией между удаленными ПЭВМ. Технической задачей изобретения является разработка устройства, обеспечивающего более качественный контроль каналов связи, который достигается за счет ввода блока сравнения и регулирующего элемента. Устройство содержит k - линейных узлов, где k = 2,4,6 ..., кольцевой регистр, блок элементов запрета, дополнительный элемент запрета, элемент ИЛИ, тактовый генератор, контрольный приемник, дополнительный блок контроля и регулирующий элемент. Каждый линейный узел содержит входной коммутатор, приемник информации, блок контроля, контрольный коммутатор, цифроаналоговый преобразователь, регистр, элемент запрета, дополнительный элемент ИЛИ, блок сравнения. Технический результат заключается в устранении неоднозначности сравнения качества основного и резервного каналов связи, вследствие этого более качественное осуществление контроля, кроме того, ввод регулирующего элемента позволил учитывать интервал времени определения качества резервного канала. 6 ил.

Устройство автоматической коммутации каналов связи, содержащее k линейных узлов, где k = 2, 4, 6 ..., входы основного и резервного каналов i-го линейного узла, где i = 1, ..., k, являются соответственно i-ми входами основного и резервного каналов устройства, а информационный выход i-го линейного узла является i-м информационным выходом устройства, кольцевой регистр, k выходов которого подключены к соответствующим k входам блока элементов запрета, i-й управляющий выход которого соединен с входом "Выбор узла" i-го линейного узла, а запрещающий вход блока элементов запрета подключен к входу дополнительного элемента запрета и выходу элемента ИЛИ, выход дополнительного элемента запрета соединен с входом кольцевого регистра, первый вход элемента ИЛИ подключен к блокирующим входам каждого (2j - 1)-го и блокирующим выходам каждого (2j)-го линейных узлов, где j = 1, 2, ... k / 2, а второй вход элемента ИЛИ подключен к блокирующим выходам каждого (2j - 1)-го и блокирующим входам каждого (2j)-го линейных узлов, синхронизирующий вход каждого линейного узла подключен к выходу тактового генератора, к которому также подключен тактовый вход дополнительного элемента запрета, а контрольные выходы линейных узлов подключены к входу контрольного приемника, выход которого подключен к входу дополнительного блока контроля, выход которого соединен с контрольными входами всех линейных узлов, отличающееся тем, что дополнительно введен регулирующий элемент, выход которого соединен со входом тактового генератора, а тактовый вход дополнительного блока контроля соединен с выходом тактового генератора, каждый i-й линейный узел состоит из входного коммутатора, первый и второй входы которого являются входами основного и резервного каналов линейного узла, а управляющий вход входного коммутатора подключен к первому управляющему выходу регистра, второй управляющий выход которого подключен к управляющему входу контрольного коммутатора и является одновременно блокирующим выходом линейного узла, тактовый вход регистра является синхронизирующим входом линейного узла и соединен с тактовым входом блока контроля, информационный вход регистра подключен к выходу элемента запрета, управляющий и информационные входы которого подключены соответственно к выходу блока сравнения и выходу дополнительного элемента ИЛИ, выход которого является блокирующим входом линейного узла, контрольный вход дополнительного элемента ИЛИ подключен к контрольному выходу контрольного коммутатора, контрольный вход которого соединен с первым информационным входом блока сравнения и является контрольным входом линейного узла, информационный выход контрольного коммутатора является контрольным выходом линейного узла, а информационный вход контрольного коммутатора подключен к второму выходу входного коммутатора, первый выход которого подключен к приемнику информации, который каскадно соединен с блоком контроля, цифроаналоговым преобразователем, причем выход цифроаналогового преобразователя является информационным выходом линейного узла, а второй информационный выход блока контроля подключен к второму информационному входу блока сравнения, причем исполнительный вход контрольного коммутатора является входом "Выбор узла" линейного узла.

| Устройство для автоматического переключения каналов связи | 1991 |

|

SU1826136A1 |

| Устройство выбора канала с экстремальным средним напряжением | 1986 |

|

SU1408539A1 |

| Устройство для комбинированного тушения пожаров и пожаровзрывопредотвращения пеной низкой и средней кратности | 2018 |

|

RU2693612C1 |

| Измеритель нелинейного пилообразного напряжения | 1977 |

|

SU652504A1 |

| DE 19701911 A1, 23.07.98. | |||

Авторы

Даты

1999-12-27—Публикация

1998-10-01—Подача