Изобретение относится к технике электросвязи и передачи данных, может быть использовано на главной станции для приема и обмена дискретной информацией в виде кодограмм в группе радиостанций с ведением радиомониторинга в регионе для обеспечения электромагнитной совместимости радиоэлектронных средств и рационального использования выделенного частотного ресурса.

Известный аналог предлагаемого устройства (а.с. СССР N 1083382, кл. H 04 B 7/26, 1984) содержит в составе устройства в передающей части последовательно соединенные блок ввода сообщений, первый кодер и передатчик, а в приемной части последовательно соединенные приемник, блок контроля занятости каналов и первый элемент, а также хронизатор, декодер и блок формирования приоритета.

Однако аналог при его работе не обеспечивает требуемой пропускной способности и полноты охвата наблюдением совокупности РЭС, находящихся в зоне связи, так как прием кодограммы одновременно возможен только на одной из частот, выделенных на группу станций или подлежащих радиомониторингу, тогда как по условиям работы необходимо обеспечить одновременный прием сигналов на разных частотах группы станций в заданном районе.

Ближайшее устройство передачи и приема информации (прототипа) [4] содержит приемопередающий блок, состоящий из передатчика, хронизатора, формирователя кода частоты, приемника, первого кодера, блока контроля занятости канала, первого элемента И, блока формирования приоритета, блока ввода сообщения, блок маршрутизации, состоящий из блока контроля качества сигнала и блока выбора маршрута, блок памяти, состоящий из второго и третьего кодеров, второго, третьего и четвертого элементов И, компаратора, первого и второго регистров памяти, блока запоминания, а также декодер и пятый элемент И.

Недостатком данного устройства является низкая пропускная способность, что, в частности, обусловливает низкую эффективность радиомониторинга из-за невозможности одновременного приема кодограмм, передаваемых на разных частотах находящимися в контролируемой зоне РЭС, так как прототип реализует прием кодограмм методом последовательной перестройки по заданным рабочим частотам. Под пропускной способностью устройства, на которое поступает поток кодограмм, понимается величина нагрузки, которая может поступать на устройство при обеспечении заданного качества обслуживания.

Целью изобретения является разработка устройства передачи и приема информации, обеспечивающего повышение пропускной способности и полноты наблюдения за каналами передачи информации радиостанций, работающих в группе, а также более эффективное решение задач радиомониторинга.

Цель достигается тем, что в известное устройство передачи и приема информации, содержащее блоки: приемопередающий, памяти, маршрутизации, а также декодер и пятый элемент И, дополнительно введены следующие элементы: n приемников (n≤7), адаптер мультиплексного канала, коммутатор.

Устройство передачи и приема информации содержит приемопередающий блок, состоящий из передатчика, хронизатора, формирователя кода частоты, приемника, первого кодера, блока контроля занятости канала, первого элемента И, блока формирования приоритета, блока ввода сообщения, блок маршрутизации, состоящий из блока контроля качества сигнала и блока выбора маршрута, блок памяти, состоящий из второго и третьего кодеров, второго, третьего и четвертого элементов И, компаратора, первого и второго регистров памяти, блока запоминания, а также декодер и пятый элемент И, выход первого элемента И соединен с входами управления блока ввода сообщения и передатчика, первый, второй и третий выходы хронизатора соединены с синхровходами блока контроля занятости канала, через формирователь кода частоты - с входами перестройки приемника и передатчика, а через формирователь приоритета - со вторым входом первого элемента И, сигнальный выход приемника соединен со вторым входом блока контроля занятости канала, выход которого соединен с первым входом первого элемента И, первый выход блока ввода сообщений соединен с кодером, выход которого соединен с передатчиком, а второй выход соединен с первым входом блока формирования приоритета, последовательно соединены блок контроля качества сигнала, блок выбора маршрута, второй элемент И, второй кодер, первый регистр памяти, компаратор, и третий элемент И, а также четвертый и пятый элементы И, второй регистр памяти, третий кодер и блок запоминания, причем выход третьего элемента И соединен с входом разрешения блока ввода сообщения, второй выход компаратора соединен с первым входом четвертого элемента И, выход которого объединен с выходом третьего элемента И, а второй вход через второй регистр памяти соединен со вторым входом компаратора, выход первого элемента И через блок запоминания соединен с входом первого регистра памяти, второй выход которого соединен со вторым входом третьего элемента И, второй выход блока выбора маршрута соединен с первым входом пятого элемента И, второй вход которого соединен со вторым выходом второго элемента И, входом блока контроля качества сигнала и соединен с адресным выходом декодера, выход второго служебного сигнала которого соединен со вторым входом блока выбора маршрута, третий выход которого через третий кодер соединен с входом записи первого регистра памяти, выход третьего служебного сигнала декодера соединен со вторым входом блока контроля качества сигнала, вход второго регистра памяти является первым входом устройства, а выход пятого элемента И является первым выходом устройства, отличающееся тем, что дополнительно введены адаптер мультиплексного канала, коммутатор и К приемников (1≤K≤7), вход каждого i-го приемника (i=1, 2,...,N), где N=K+1 подключен к соответствующей антенне, а их сигнальные и синхронизирующие выходы, а также аналогичные выходы приемника приемопередающего блока соединены с соответствующим i-м сигнальным и i-м синхронизирующим входом блока адаптера мультиплексного канала, N выходов которого подключены к N входам коммутатора, а также являются выходами устройства, выход коммутатора связан с входом декодера, третий выход которого соединен с третьим входом блока контроля занятости канала, N+1 и N+2 выходы адаптера мультиплексного канала являются выходами устройства, а входы с 2N+1 по 2N+3 являются входами устройства.

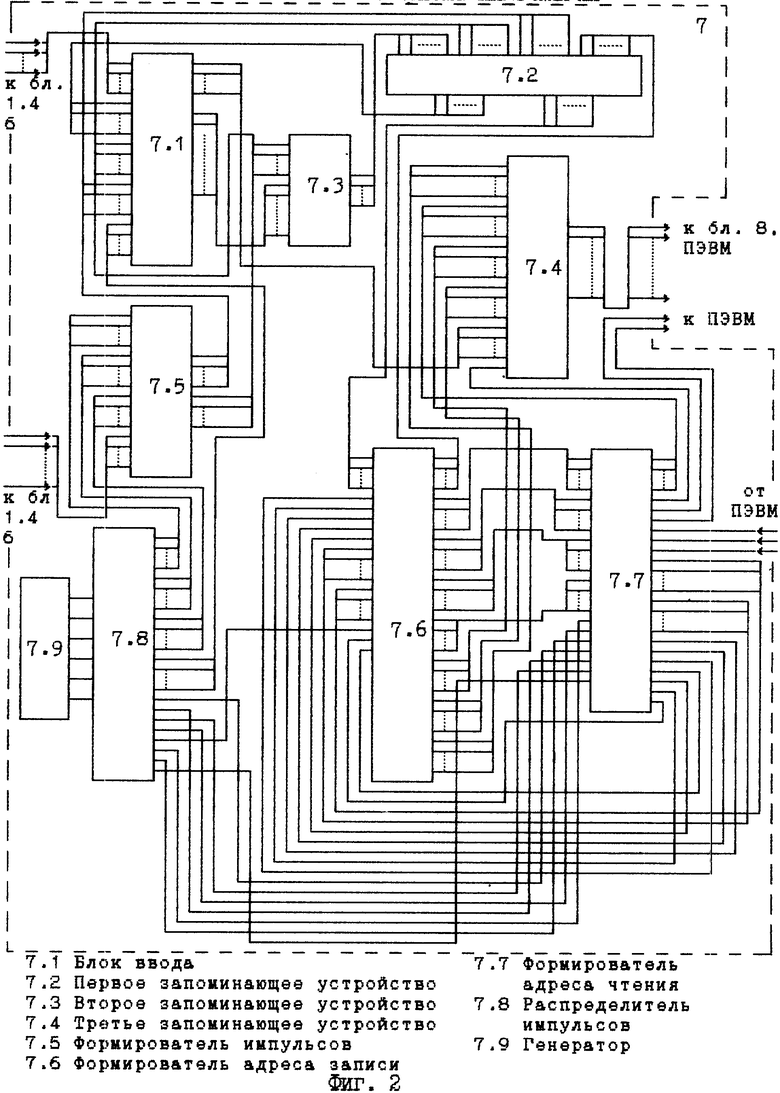

Адаптер мультиплексного канала содержит блок ввода, формирователь импульсов, формирователь адреса записи, формирователь адреса чтения, первое, второе, третье запоминающее устройство, распределитель импульсов, генератор, с первого по N выходы блока ввода соединены соответственно с 4N+1 по 5N входами третьего запоминающего устройства, а с N+1 по N+17 выходы блока ввода соединены соответственно с N+1 по N+17 входами второго запоминающего устройства, с первого по N выходы первого запоминающего устройства соединены соответственно с N+1 по 2N входами блока ввода, а выходы с N+1 по 2N соединены соответственно с 1 по N входами формирователя адреса записи, выходы с первого по N второго запоминающего устройства соединены соответственно с первого по N входами первого запоминающего устройства, с первого по N выходы формирователя импульсов соединены параллельно соответственно с 3N+1 по 4N входами блока ввода и с 2N+1 по 3N входами первого запоминающего устройства, а выходы с N+1 по 2N соединены параллельно соответственно с первого по N входами второго запоминающего устройства, с 2N+1 по 3N входами блока ввода и с N+1 по 2N входами первого запоминающего устройства, выходы с первого по N формирователя адреса записи соединены соответственно с 3N+1 по 4N входами первого запоминающего устройства, выходы с N+1 по 5N соединены соответственно с первого по 4N входами формирователя адреса считывания, выходы с 5N+1 по 6N, с 6N+1 по 7N, с 7N+1 по 8N соединены с 2N+1 по 3N, с 3N+1 по 4N, с первого по N входам третьего запоминающего устройства, соответственно, выходы с первого по N формирователя адреса чтения соединены соответственно с N+1 по 2N входами третьего запоминающего устройства, выходы с N+1 по 2N, с 2N+1 по 3N, 3N+3, 3N+4, 3N+5, 3N+6, 3N+7, 3N+8, 3N+9 соединены с входами с 3N+1 по 4N, с 2N+1 по 3N, 4N+3, 4N+4, 4N+1, 4N+8, 4N+5, 4N+2, 4N+7 формирователя адреса записи, соответственно, выход 3N+10 соединен с входом 5N+1 третьего запоминающего устройства, выходы 3N+1 и 3N+2 являются соответственно N+1 и N+2 выходами адаптера мультиплексного канала, выходы с первого по 3N распределителя импульсов соединены с первого по 3N входами формирователя импульсов, соответственно, выходы с 3N+1 по 4N соединены с 4N+1 по 5N входами блока ввода, выходы 4N+1, 4N+2, 4N+3, 4N+4, 4N+6, 4N+8 соединены с входами 4N+4, 4N+5, 4N+2, 4N+3, 4N+10 формирователя адреса чтения, соответственно, выход 4N+5 соединен с входом 4N+6 формирователя адреса записи, с первого по 6 выходы генератора соединены соответственно с первого по шестой входами распределителя импульсов, выходы с первого по N третьего запоминающего устройства являются соответственно с первого по N выходами адаптера мультиплексного канала, входы с первого по N блока ввода являются соответственно с первого по N сигнальными входами адаптера мультиплексного канала, входы с 3N+1 по 4N формирователя импульсов являются соответственно с N+1 по 2N синхронизирующими входами блока адаптера мультиплексного канала, входы с 4N+7 по 4N+9 являются соответственно с 2N+1 по 2N+3 входами адаптера мультиплексного канала, а также с N+3 по N+5 входами устройства.

Блок ввода содержит N регистров, первый вход i-го регистра является i-м входом блока, второй вход является N+i входом блока, третий вход является 2N+1 входом блока, четвертый вход является 3N+i входом блока, пятый вход является 4N+i входом блока, первый выход является i-м выходом блока, со второго по восемнадцатый выходы всех регистров соединены параллельно и являются с N+1 по N+17 выходами блока.

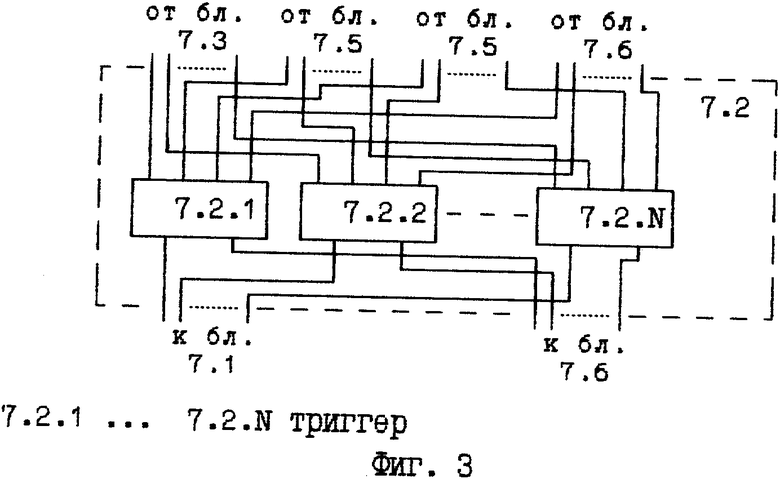

Первое запоминающее устройство содержит N триггеров, первый вход i-го триггера является i-м входом блока, второй вход является N+i входом блока, третий вход является 2N+i входом блока, четвертый вход является 3N+i входом блока, первый выход является i-м выходом блока, второй выход является N+i выходом блока.

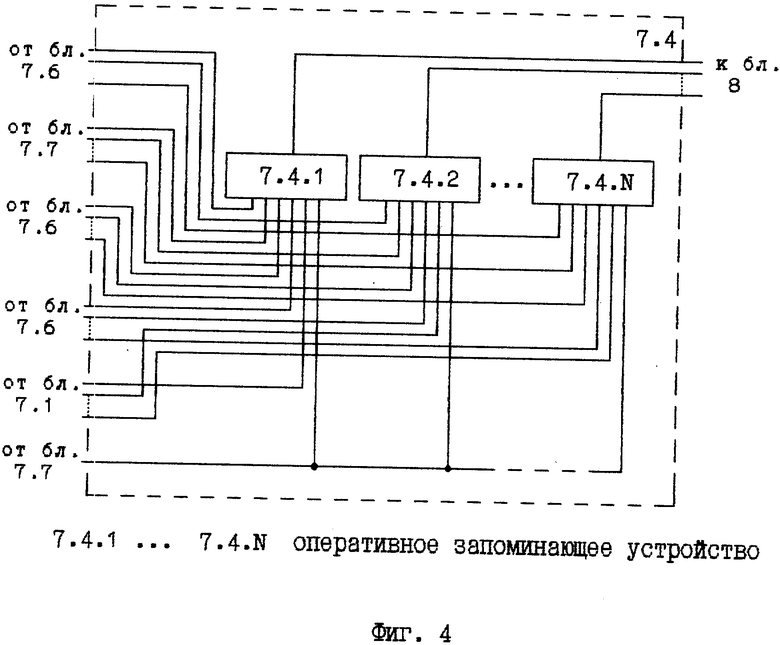

Третье запоминающее устройство содержит N оперативных запоминающих устройств, у каждого i-го оперативного запоминающего устройства первый вход является i-м входом блока, второй вход является N+i входом блока, третий вход является 2N+i входом блока, четвертый вход является 3N+i входом блока, пятый вход является 4N+i входом блока, шестые входы всех оперативных запоминающих устройств соединены параллельно и являются 5N+1 входом блока, первый выход является i-м выходом блока.

Формирователь адреса записи содержит N формирователей, первый вход i-го формирователя является i-м входом блока, вторые входы всех формирователей соединены параллельно и являются 4N+1 входом блока, третьи входы соединены параллельно и являются 4N+2 входом блока, четвертые входы всех формирователей соединены параллельно и являются 4N+3 входом блока, пятые входы всех формирователей соединены параллельно и являются 4N+4 входом блока, шестые входы всех формирователей соединены параллельно и являются 4N+5 входом блока, седьмой вход является 2N+i входом блока, восьмой вход является 3N+i входом блока, девятые входы всех формирователей соединены параллельно и являются 4N+6 входом блока, десятые входы всех формирователей соединены параллельно и являются 4N+7 входом блока, одиннадцатые входы всех формирователей соединены параллельно и являются 4N+8 входом блока, первый выход является i-м выходом блока, второй выход является N+i выходом блока, третий выход является 2N+1 выходом блока, четвертый выход является 3N+i выходом блока, пятый выход является 4N+i выходом блока, шестой выход является 5N+i выходом блока, седьмой выход является 6N+i выходом блока, восьмой выход является 7N+i выходом блока.

Формирователь импульсов содержит N формирователей, первый вход i-го формирователя является i-м входом блока, второй вход является N+i входом блока, третий вход является 2N+i входом блока, четвертый вход является 3N+i входом блока, первый выход является i-м выходом блока, второй выход является N+i выходом блока.

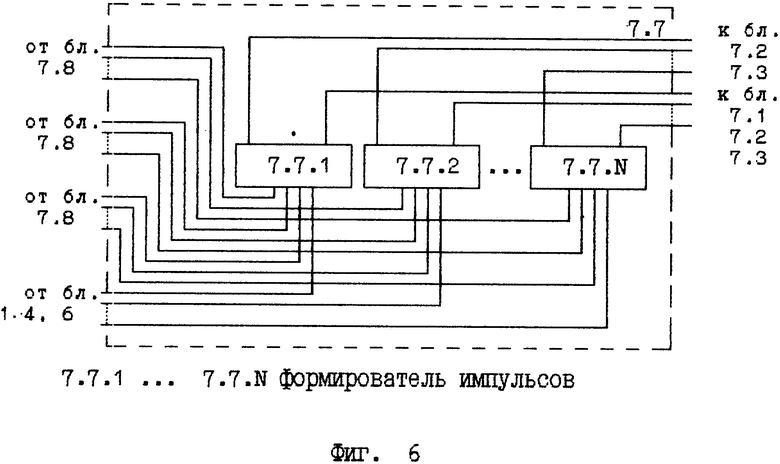

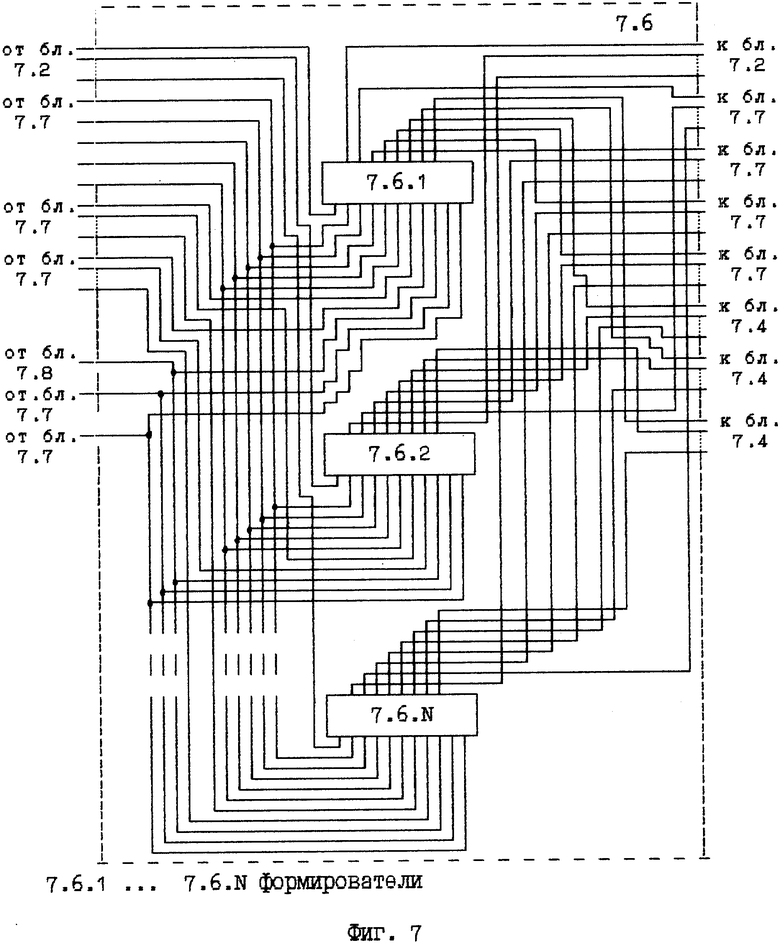

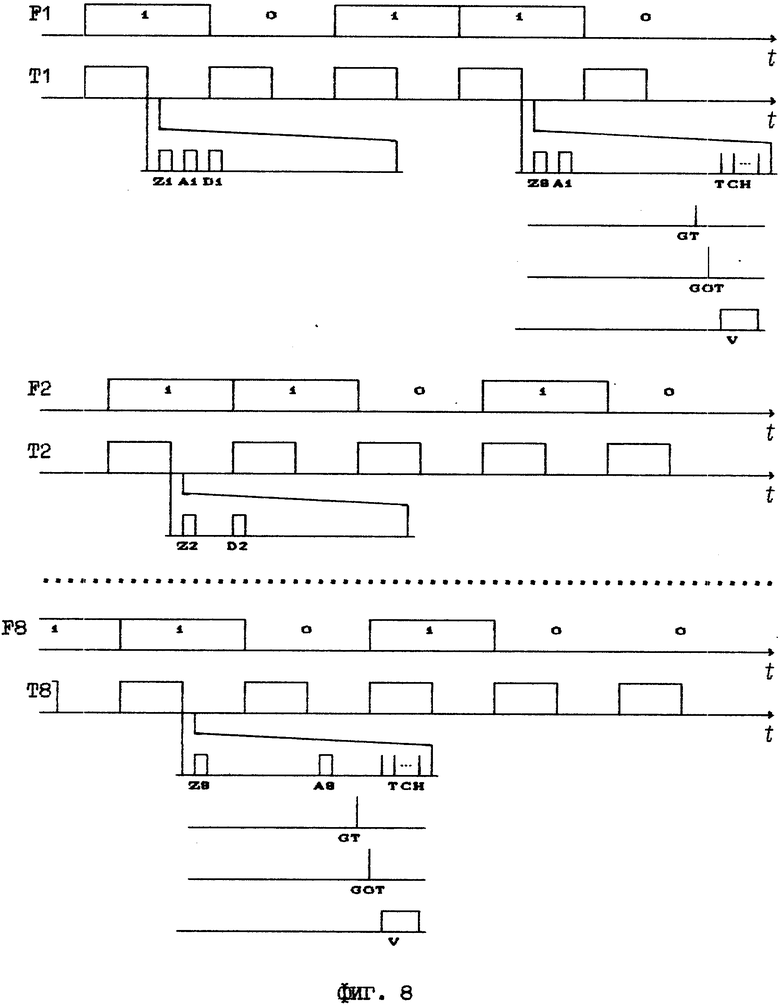

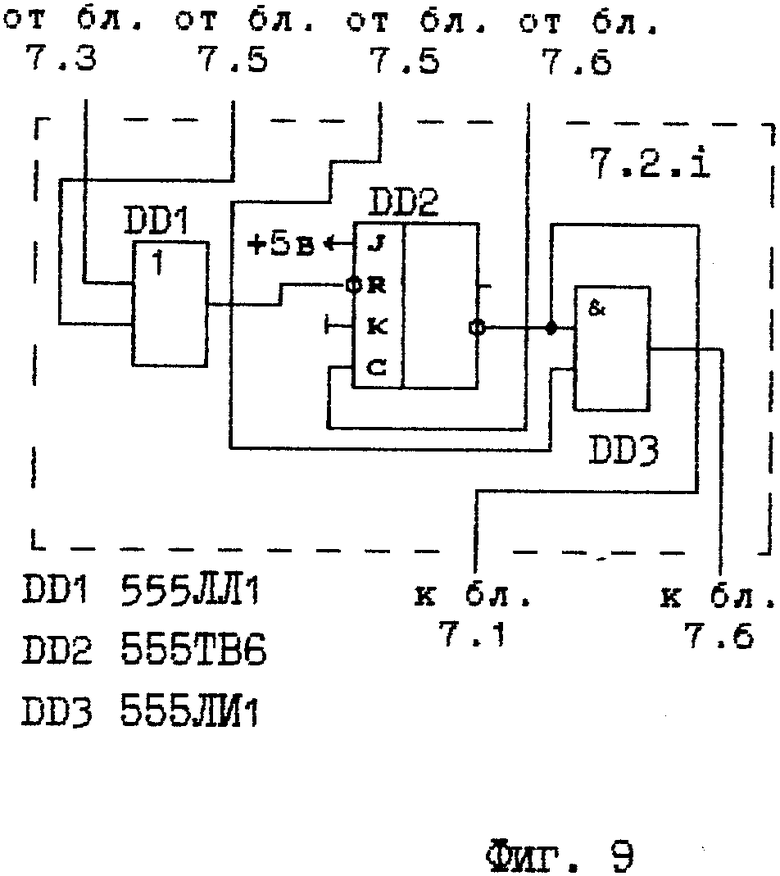

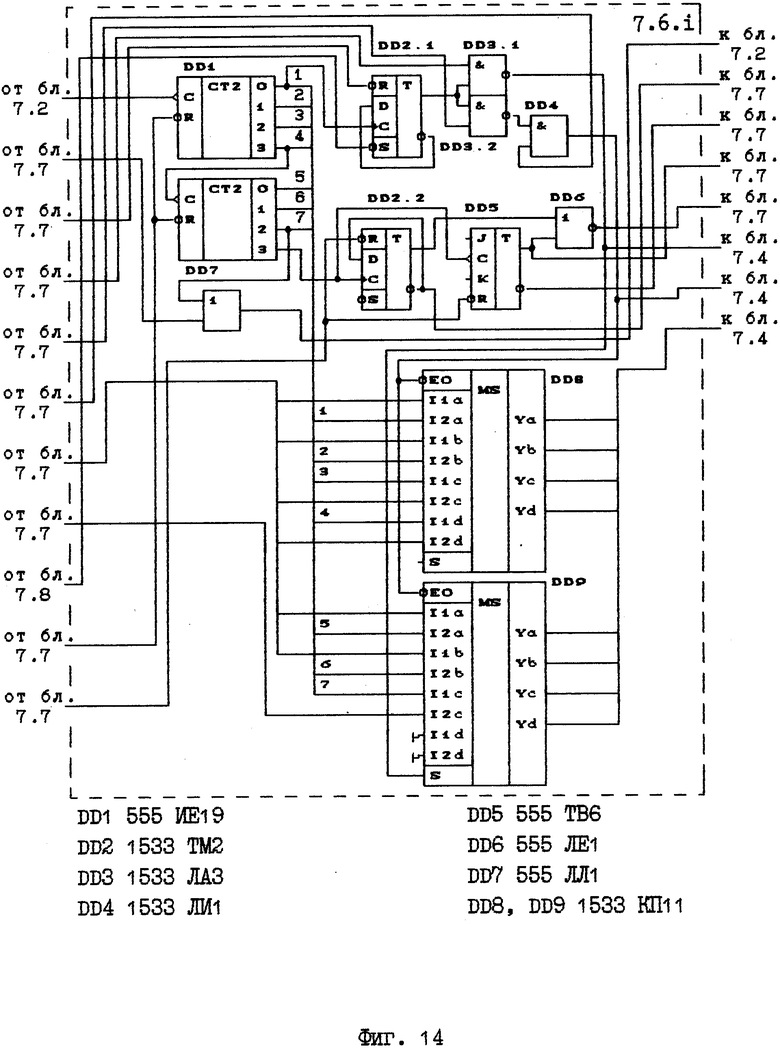

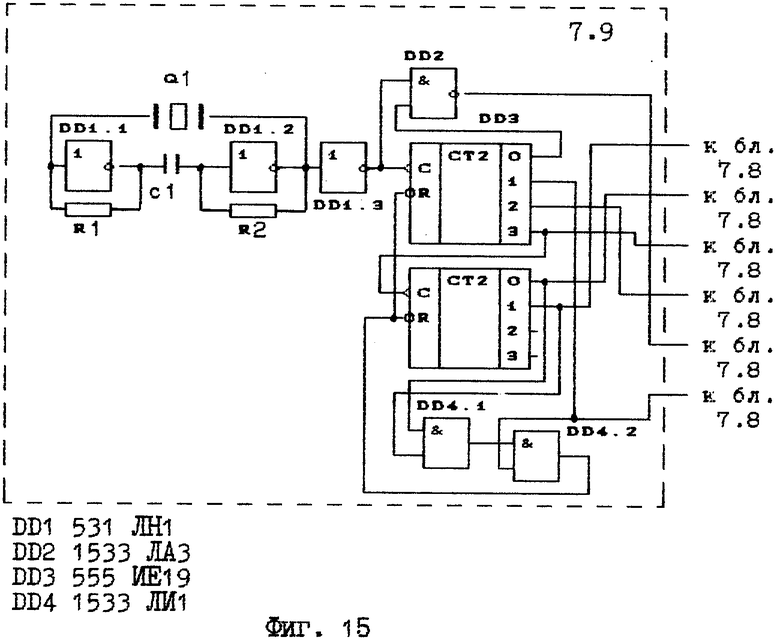

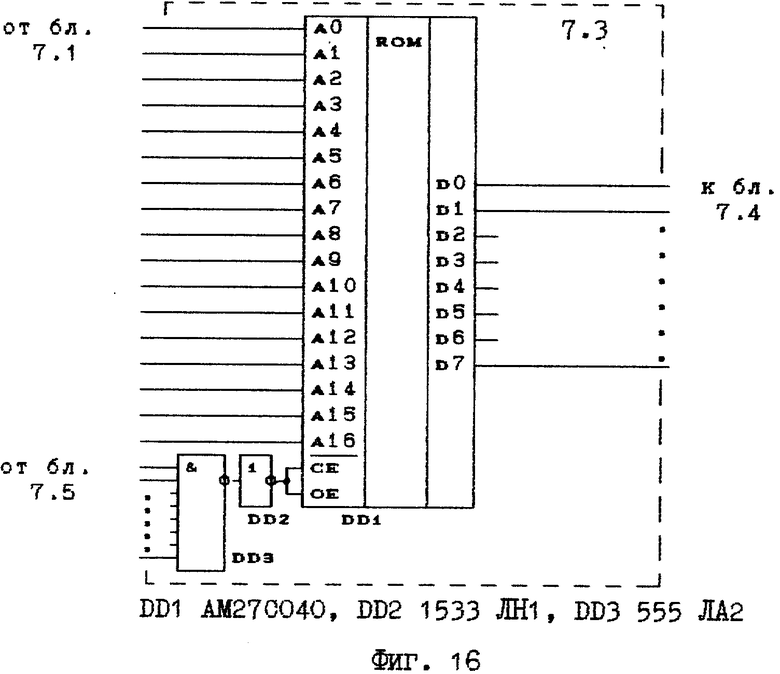

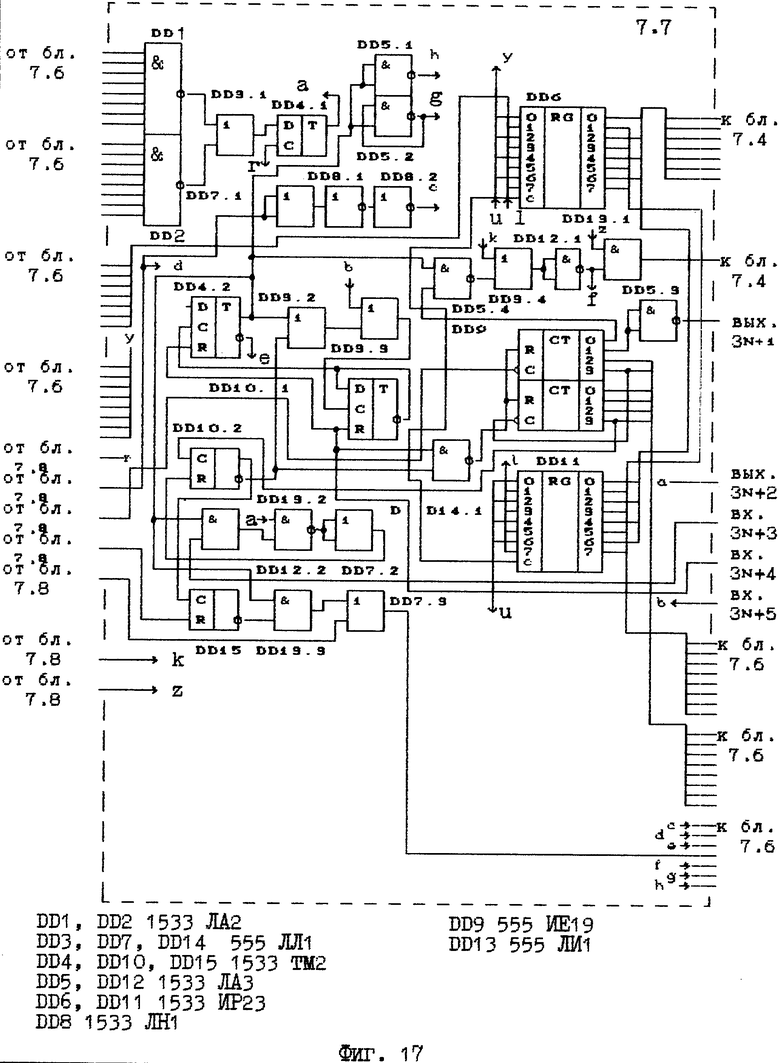

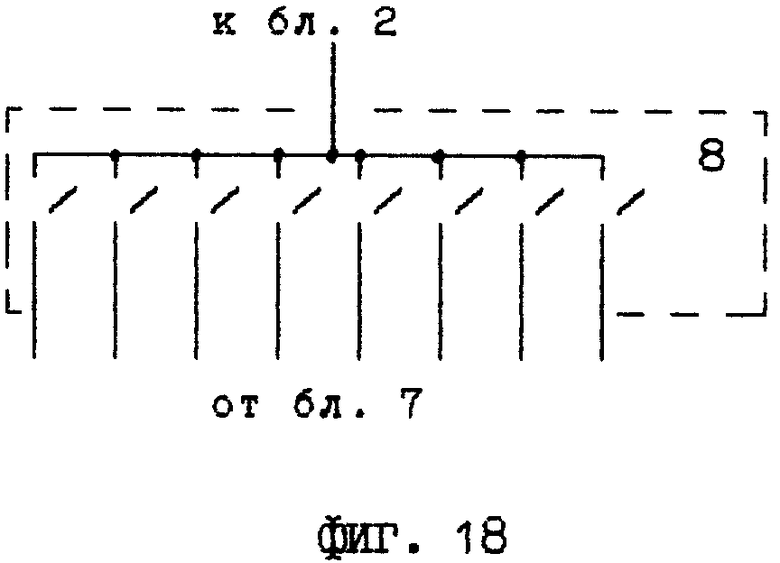

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - схема адаптера мультиплексного канала; на фиг. 5 - схема блока ввода; на фиг. 3 - схема первого запоминающего устройства; на фиг. 4 - схема третьего запоминающего устройства; на фиг. 7 - схема формирователя адреса записи; на фиг. 6 - схема формирователя импульсов; на фиг. 8 - временные диаграммы.

Устройство передачи и приема информации (фиг. 1) содержит блоки: приемопередающий 1 (ППБ), состоящий из передатчика 1.1 (ПРД), хронизатора 1.2 (ХР), формирователя кода частоты 1.3 (ФКЧ), приемника 1.4 (РПУ), первого кодера 1.5 (КД), блока контроля занятости канала 1.6 (БКЗК), первого элемента И 1.7, блока формирования приоритета 1.8 (ВФП), блока ввода сообщения 1.9 (БВС); памяти 3 (БП), состоящий из второго 3.1 и третьего 3.2 кодеров (КД), второго 3.3, третьего 3.4, четвертого 3.5 элементов И, компаратора 3.6 (КМП), первого 3.7 и второго 3.8 регистров памяти (РГП), блока запоминания 3.9 (БЗ); маршрутизации 4 (БМ), состоящего из блока контроля качества сигнала 4.1 (БККС) и блока выбора маршрута 4.1 (БВМ), а также декодер 2 (ДК), пятый элемент И 5, приемники 6 (РПУ), коммутатор 8 (К), адаптер мультиплексного канала 7 (АМК), состоящий из блока ввода 7.1 (БВВ), формирователя импульсов 7.5 (ФИ), формирователя адреса записи 7.6 (ФАЗ), формирователь адреса чтения 7.7 (ФАЧ), первого 7.2, второго 7.3 и третьего 7.4 запоминающих устройств (ЗУ), распределителя импульсов 7.8 (РИ), генератора 7.9 (Г).

Выход ПРД 1.1 соединен с передающей антенной, а вход РПУ 1.4 соединен с приемной антенной. Выход первого элемента И 1.7 соединен с входом управления БВС 1.9 и ПРД 1.1. Первый, второй и третий выходы хронизатора 1.2 соединены с синхровходами БКЗК 1.6, через ФКЧ 1.3 - с входами перестройки РПУ 1.4 и ПРД 1.1, а через БФП 1.8 - со вторым входом первого элемента И 1.7. Сигнальный выход РПУ 1.4 соединен со вторым входом БКЗК 1.6, выход которого соединен с первым входом первого элемента И 1.7. Первый выход БВС 1.9 соединен с первым КД 1.5 выход которого соединен с ПРД 1.1, а второй выход соединен с первым входом БФП 1.8. Последовательно соединены БККС 4.1, БВМ 4.2, второй элемент И 3.3, второй КД 3.1, первый РГП 3.7, КМП 3.6 и третий элемент И 3.4. Выход третьего элемента И 3.4 соединен с входом разрешения БВС 1.9, второй выход КМП 3.6 соединен с первым входом четвертого элемента И 3.5, выход которого объединен с выходом третьего элемента И 3.4, а второй вход через второй РГП 3.8 соединен со вторым входом КМП 3.6. Выход первого элемента И 1.7 через Б3 3.9 соединен с входом первого РГП 3.7, второй выход которого соединен со вторым входом третьего элемента И 3.4. Второй выход БВМ 4.2 соединен с первым входом пятого элемента И 5, второй вход которого соединен со вторым выходом второго элемента И 3.3, входом БККС 4.1 и соединен с адресным выходом ДК 2, выход второго служебного сигнала которого соединен со вторым входом БВМ 4.2, третий выход которого через третий КД 3.2 соединен с входом записи первого РГП 3.7. Выход третьего служебного сигнала ДК 2 соединен с вторым входом БККС 4.1. Вход второго РГП 3.8 является первым входом устройства, а выход пятого элемента И является первым выходом устройства. Вход каждого i-го РПУ 1.4, 6 (i=1, 2,...,N), где N=K+1 подключен к соответствующей антенне, а их сигнальный и синхронизирующий выходы соединены с соответствующим i-м сигнальным и i-м синхронизириющим входом АМК 7, N выходов которого подключены к N входам коммутатора 8, а также являются выходами устройствами. Выход коммутатора 8 связан с входом ДК 2, третий выход которого соединен с третьим входом БКЗК 1.6, N+1 и N+2 выходы АМК 7 являются выходами устройства, а входы с 2N+1 по 2N+3 являются входами устройствам.

С первого по N выходы БВ 7.1 соединены соответственно с 4N+1 по 5N входами третьего ЗУ 7.4, с N+1 по N+17 выходы БВ 7.1 соединены соответственно с N+1 по N+17 входами второго ЗУ 7.3. С первого по N выходы первого ЗУ 7.2 соединены соответственно с N+1 по 2N входами БВ 7.1, а выходы с N+1 по 2N соединены соответственно с первого по N входами ФАЗ 7.6. Выходы с первого по N второго ЗУ 7.3 соединены соответственно с первого по N входами первого ЗУ 7.2. С первого по N выходы ФИ 7.5 соединены параллельно соответственно с 3N+1 по 4N входами БВ 7.1 и с 2N+1 по 3N входами первого ЗУ 7.2, а выходы с N+1 по 2N соединены параллельно соответственно с первого по N входами второго ЗУ 7.3, с 2N+1 по 3N входами БВ 7.1 и с N+1 по 2N входами первого ЗУ 7.2. Выходы с первого по N ФАЗ 7.6 соединены соответственно с 3N+1 по 4N входами первого ЗУ 7.2, выходы с N+1 по 5N соединены соответственно с первого по 4N входами ФАЧ 7.7, выходы с 5N+1 по 6N, с 6N+1 по 7N, с 7N+1 по 8N соединены с 2N+1 по 3N, с 3N+1 по 4N, с первого по N входами третьего ЗУ 7.4, соответственно. Выходы с первого по N ФАЧ 7.7 соединены соответственно с N+1 по 2N входами третьего ЗУ 7.4, выходы с N+1 по 2N, с 2N+1 по 3N, 3N+3, 3N+4, 3N+5, 3N+6, 3N+7, 3N+8, 3N+9, соединены с входами с 3N+1 по 4N, с 2N+1 по 3N, 4N+3, 4N+4, 4N+1, 4N+8, 4N+5, 4N+2, 4N+7 ФАЗ 7.6, соответственно, выход 3N+10 соединен с входом 5N+1 третьего ЗУ 7.4, выходы 3N+1 и 3N+2 являются соответственно N+1 и N+2 выходами АМК 7. Выходы с первого по 3N РИ 7.8 соединены с первого по 3N входами ФИ 7.5, соответственно, выходы с 3N+1 по 4N соединены с 4N+1 по 5N входами ББВ 7.1, выходы 4N+1, 4N+2, 4N+3, 4N+4, 4N+6, 4N+7, 4N+8 соединены с входами 4N+4, 4N+5, 4N+6, 4N+2, 4N+1, 4N+3, 4N+10 ФАЧ 7.7, соответственно. Выход 4N+5 соединен с входом 4N+6 ФАЗ 7.6. С первого по 6 выходы Г 7.9 соединены соответственно с первого по шестой входами РИ 7.8. Выходы с первого по N третьего ЗУ 7.4 являются соответственно с первого по N выходами АМК 7. Входы с первого по N БВ 7.1 являются соответственно с первого по N сигнальными входами АМК 7. Входы с 3N+1 по 4N ФИ 7.5 являются соответственно с N+1 по 2N синхронизирующими входами АМК 7, входы с 4N+7 по 4N+9 являются соответственно с 2N+1 по 2N+3 входами АМК 7.

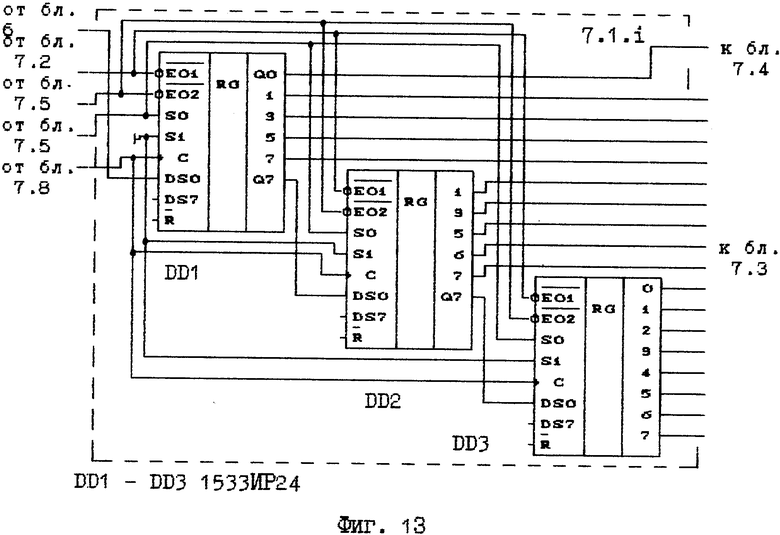

Блок ввода 7.1 содержит N регистров, первый вход i-го регистра 7.1. i-является i-м входом блока, второй вход является N+i-м входом блока, третий вход является 2N+i входом блока, четвертый вход является 3N+i входом блока, пятый вход является 4N+i входом блока, первый выход является i-м выходом блока со второго по восемнадцатый выходы всех регистров соединены параллельно и являются с N+1 по N+17 выходами блока.

Регистр предназначен для преобразования поступающего на вход последовательного битового потока в параллельный. Разрядность выходной комбинации определяется длиной комбинации "начало пакета". Принципиальная схема регистра представлена на фиг. 13.

Первое запоминающее устройство 7.2 содержит N триггеров, первый вход триггера 7.2i является i-м входом блока, второй вход является N+i входом блока, третий вход является 2N+i входом блока, четвертый вход является 3N+i входом блока, первый выход является i-м выходом блока, второй выход является N+i выходом блока.

Триггер предназначен для запоминания номера канала, принимающего пакет, на время, необходимое для записи пакета в ОЗУ. Схема триггера представлена на фиг. 9.

Второе запоминающее устройство 7.3 представляет собой постоянное запоминающее устройство и предназначено для обнаружения в поступающем на вход параллельном потоке комбинации "начало пакета". Второе ЗУ 7.3 реализовано по схеме, показанной на фиг. 16.

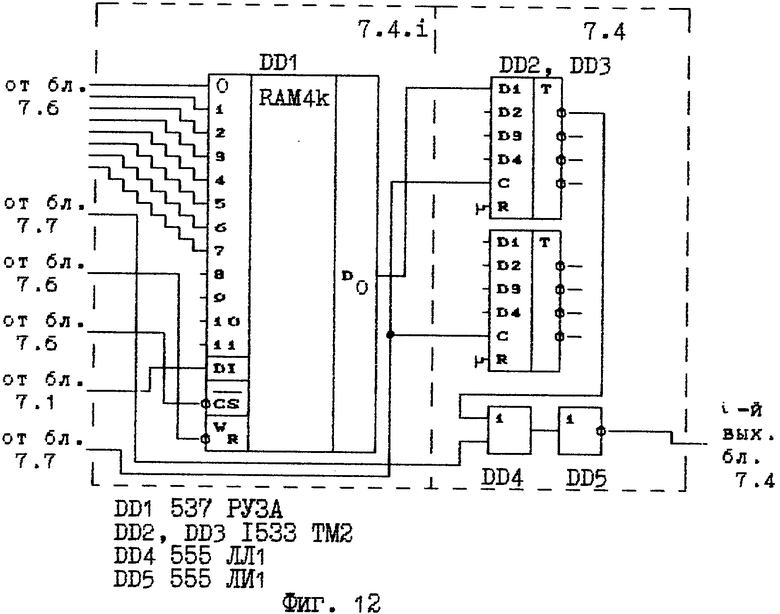

Третье запоминающее устройство 7.4 содержит N оперативных запоминающих устройств (ОЗУ), у каждого ОЗУ 7.4.i первый вход является i-м входом блока, второй вход является N+i входом блока, третий вход является 2N+i входом блока, четвертый вход является 3N+i входом блока, пятый вход является 4N+i входом блока, шестые входы всех ОЗУ соединены параллельно и являются 5N+1 входом блока, первый выход является i-м выходом блока.

ОЗУ 7.4 i предназначено для буферизации сообщений, принимаемых из низкоскоростных каналов, и последующего их вывода из устройства с более высокой скоростью. Схема ОЗУ показана на фиг. 12.

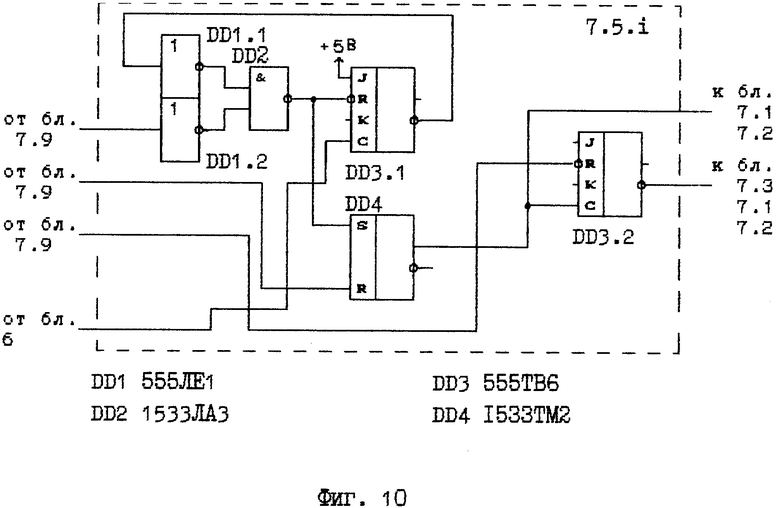

Формирователь импульсов 7.5 содержит N формирователей, первый вход формирователя 7.5 i является i-м входом блока, второй вход является N+i входом блока, третий вход является 2N+i входом блока, четвертый вход является 3N+i входом блока, первый выход является i-м выходом блока, второй выход блока является N+i выходом блока.

Формирователь 7.5 i предназначен для обеспечения регистра 7.1. i, триггера 7.2. i, второго ЗУ 7.3 вспомогательными сигналами, обеспечивающими обработку принимаемой информации. Схема формирователя представлена на фиг. 10.

Формирователь адреса записи 7.6 содержит N формирователей, первый вход формирователя 7.6. i является i-м входом блока. Вторые входы всех N формирователей соединены параллельно и являются 4N+1 входом блока, третьи входы соединены параллельно и являются 4N+2 входом блока, четвертые входы всех N формирователей соединены параллельно и являются 4N+3 входом блока, пятые входы всех N формирователей соединены параллельно и являются 4N+4 входом блока, шестые входы всех N формирователей соединены параллельно и являются 4N+5 входом блока, седьмой вход является 2N+i входом блока, восьмой вход является 3N+i входом блока, девятые входы всех N формирователей соединены параллельно и являются 4N+6 входом блока, десятые входы всех N формирователей соединены параллельно и являются 4N+7 входом блока, одиннадцатые входы всех N формирователей соединены параллельно и являются 4N+8 входом блока, первый выход является i-м выходом блока, второй выход является N+i выходом блока, третий выход является 2N+i выходом блока, четвертый выход является 3N+i выходом блока, пятый выход является 4N+i выходом блока, шестой выход блока является 5N+i выходом блока, седьмой выход является 6N+i выходом блока, восьмой выход является 7N+i выходом блока.

Формирователь адреса записи 7.6 предназначен для формирования адреса ячейки ОЗУ 7.4. i, в которую необходимо записать очередной бит принимаемого кадра. Адреса записи формируются индивидуально для каждого ОЗУ, осуществляющего запись информации. Схема формирователя показана на фиг. 14.

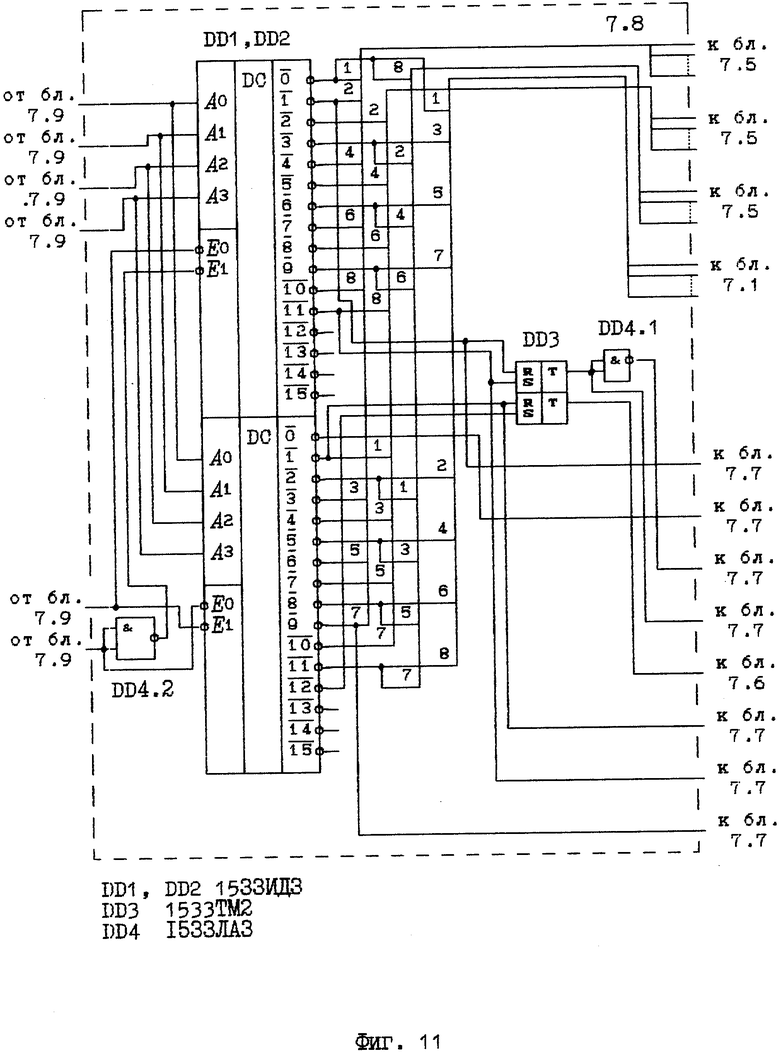

Формирователь адреса чтения 7.7 формирует адреса ячеек ОЗУ третьего ЗУ 7.4 для чтения из них бит записанных кадров. Вывод информации выполняется из всех ОЗУ одновременно. Схема формирователя 7.7 показана на фиг. 17.

Генератор 7.9 и распределитель импульсов 7.8 предназначены для формирования импульсных последовательностей, обеспечивающих прохождение принимаемой информации по блокам адаптера мультиплексного канала 7. Схемы генератора 7.9 и распределителя 7.8 представлены на фиг. 15 и 11, соответственно.

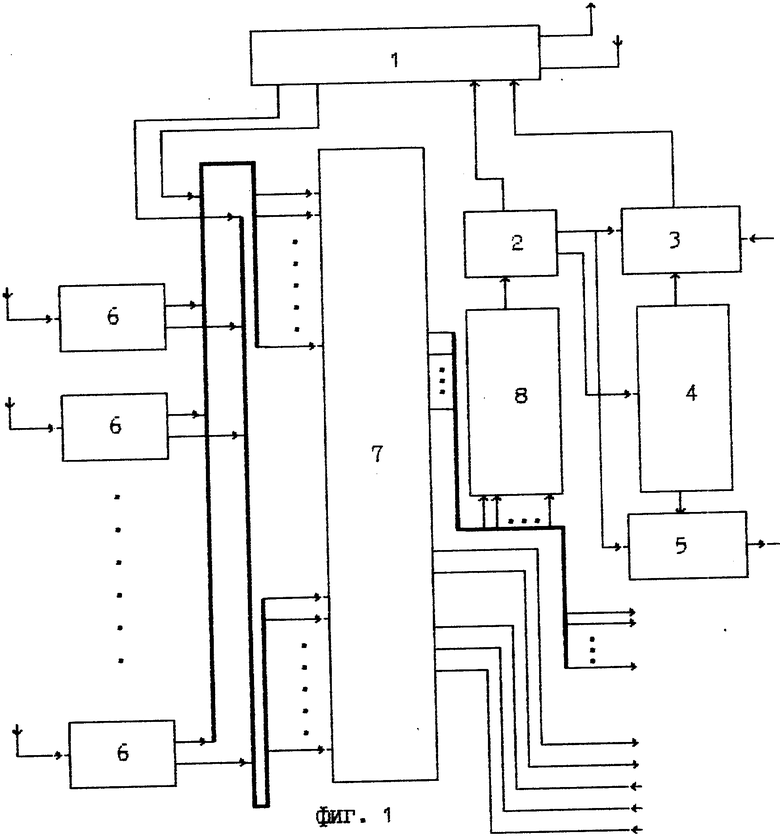

На фиг. 18 представлена схема коммутатора 8, который позволяет оператору подключать к декодеру 2 любой из приемников устройства.

Устройство передачи и приема информации работает следующим образом.

Для лучшего понимания работы устройства в целом рассмотрим работу адаптера мультиплексного канала отдельно на примере i-го канала.

В режиме приема демодулированный двоичный поток Fi с первого выхода i-го приемника 1.4, 6 поступает на i-й вход АМК 7. Со второго выхода РПУ 1.4, 6 на N+i вход АМК 7 поступают сопровождающие поток Fi импульсы тактовой синхронизации Ti. Для ввода бита информации в i-й регистр 7.1. i БВ 7.1 с 3N+i выхода распределителя импульсов 7.8 на 4N+i вход поступает импульс тактовой синхронизации Zi, а сигналы на остальных входах под воздействием импульса Ti устанавливаются в состояние разрешения записи. По окончании записи бита комбинация сигналов на входах N+i, 2N+i, 3N+i регистра 7.1.i переводит его в режим опроса состояния выходов с 5N+1 по 5N+17, подключенных ко второму запоминающему устройству 7.3, которое в момент опроса (по импульсу Ai на i-м входе второго запоминающего устройства 7.3), поступившей 17-разрядной комбинации, производит поиск кодовой комбинации "начало пакета". Данная процедура выполняется каждый раз после записи в регистр 7.1.i очередного бита потока Fi.

При обнаружении кодовой комбинации "начало пакета" на N+i выходе второго запоминающего устройства 7.3 появится логический ноль, который поступает на i-й вход первого запоминающего устройства 7.2, после чего триггер 7.2.i переходит в устойчивое состояние логического ноля, которое разрешает появление на 5N+i выходе первого запоминающего устройства 7.2 импульсов Ai, поступающих на i-й вход формирователя адреса записи 7.6. Формирователь 7.6.i начинает счет импульсов Ai.

Биты пакета с 5N+i выхода блока ввода 7.1 поступают на 4N+i вход третьего запоминающего устройства 7.4. Запись бит обеспечивается подачей соответствующих сигналов на входы оперативного запоминающего устройства 7.4.i третьего запоминающего устройства 7.4.i с выходов формирователя адреса записи 7.6 и формирователя адреса чтения 7.7. Запись производится побитно.

Как только количество импульсов Ai, поступивших в формирователь адреса записи 7.6, станет равно количеству бит пакета с 2N+i выхода формирователя, на 3N+i вход первого запоминающего устройства 7.2 поступает импульс обнуления триггера 7.2. i, и запись в оперативное запоминающее устройство 7.4.i прекращается.

В режиме вывода информации устройство работает следующим образом. Как только пакет записан в любое из N оперативных запоминающих устройств, на 7N+19 выходе формирователя адреса чтения 7.7 появляется сигнал готовности GT, который поступает на 3N+2 выход адаптера мультиплексного канала 7. В ответ на сигнал GT от ПЭВМ через вход 3N+3 адаптера мультиплексного канала 7 на вход 7N+9 формирователя адреса чтения 7.7 поступает сигнал GOT, который активизирует формирователь адреса чтения 7.7 а все N оперативных запоминающих устройств третьего запоминающего устройства 7.4 переходят в режим чтения информации. При этом на время чтения информации выходы оперативных запоминающих устройств, не содержащих пакетов, переводятся в высокоимпедансное состояние. Активизированный формирователь адреса чтения 7.7 формирует последовательность адресов чтения информации из оперативных запоминающих устройств, которая через формирователь адреса записи 7.6 поступает параллельно на входы с первого по N третьего запоминающего устройства 7.4. С выходов оперативных запоминающих устройств информация поступает на выходы с 5N+1 по 6N третьего запоминающего устройства 7.4, а затем на выходы с 2N+1 по 3N адаптера мультиплексного канала 7, соответственно. За один интервал чтения, равный длительности половины посылки из третьего запоминающего устройства 7.4, одновременно выводятся все записанные пакеты информации. Выводимая информация сопровождается импульсами тактовой синхронизации ТСН с 3N+1 выхода формирователя адреса чтения.

Коммутатор 8 обеспечивает возможность ручной коммутации любого из N выходов адаптера мультиплексного канала 7 на вход декодера 2.

В целом устройство передачи и приема информации работает следующим образом.

Хронизатор 1.2 устройства передачи и приема информации формирует периодическую последовательность импульсов временного цикла Tц, поступающих на формирователь 1.3 кода частоты, определенное число импульсов временных интервалов tп передачи сигнала, поступающих на блок 1.8 формирования приоритетов и импульсов временных интервалов ta анализа занятости канала, поступающих на блок 1.6 контроля занятости канала.

При поступлении сигналов Tц формирователь 1.3 кода частоты вырабатывает коды рабочих частот и выдает их на входы приемника 1.4 и передатчика 1.1.

По окончании настройки приемников 6 на фиксированные частоты с их выходов поступают импульсные последовательности на входы адаптера мультиплексного канала 7, осуществляющего мультиплексирование асинхронных входных потоков, выделение моментов начала передачи кадров, синхронный вывод кадров по шине, подключенной к ПЭВМ, которая решает задачи радиомониторинга согласно заданному предписанию.

С первого выхода адаптера мультиплексного канала 7 кадры побитно через коммутатор 8 поступают на вход декодера 2.

Декодер 2 осуществляет кодопреобразование поступающей на него последовательности и выделение адресной и информационной частей сообщения. Число выходов декодера 2 соответствует количеству разрядов в комбинациях преобразованного кода.

По результатам мониторинга с помощью коммутатора 8 выход любого из приемников 6 может быть подключен к входу декодера 2.

Блок 1.6 контроля занятости канала на интервалах времени проводит статистический контроль структуры, поступающей на него с приемника 1.4 импульсной последовательности, например, по параметрам распределения длительности импульсов и структуры преобразованной информации, поступающей на него с декодера 2.

При выявлении структуры случайных радиопомех блок 1.6 принимает решение о незанятости канала, в случае выявления структуры сигнала - решение о его занятости другими станциями. Соответствующие сигналы выдаются на вход элемента И 1.7.

Кодограмма, подлежащая передаче, содержит адресную часть, признак транзита, признак приоритета и информационную часть и вводится с помощью блока 1.9 ввода сообщения.

Кодограммы от абонентов поступают на второй регистр 3.8 памяти по входной шине, компаратор 3.6 сравнивает приоритет кодограммы от абонента с приоритетом транзитной кодограммы (если такая имеется), записанной в первый регистр памяти 3.7. Кодограмма с более высоким приоритетом через элементы И 3.5 или 3.4 поступает на блок 1.9 ввода сообщения.

Блок 1.9 выделяет на кодограммы признак приоритета и в соответствии с приоритетами организует обслуживание.

Код признака приоритета с выхода блока 1.9 поступает на блок 1.8 формирования приоритета, который вводит временную задержку передачи кодограммы путем сдвига фронта импульсов tn, поступающих на него с хронизатора 1.2 в данном временном цикле Tц, на определенную величину. При этом меньшему приоритету соответствует большее значение. Величина может задаваться переменной.

Введение задержек передачи кодограмм позволяет передавать на любом временном интервале tn кодограммы с различными приоритетами при отсутствии кодограмм более высокого приоритета, а также устранить возможность наложения сообщений от нескольких станций (наряду с контролем занятости канала).

Сигнал с выхода блока 1.8 формирования приоритета поступает на первый элемент И 1.7, который при совпадении сигналов с блока 1.8 формирования и сигнала о незанятости канала с блока 1.6 выдает сигнал на приемник 1.4, блок 1.9 ввода сообщения и передатчик 1.1. Этим сигналом запирается вход приемника 1.4, включается передатчик 1.1 и разрешается ввод кодограммы с блока 1.9 через первый кодер 1.5.

Если кодограмма не передана на первом интервале tn по причине занятости канала (нет совпадения сигнала на первом элементе И 1.7), то передача состоится при освобождении канала на следующем интервале.

При окончании кодограммы сигналом с выхода первого элемента И 1.7 отключается передатчик 1.1 и деблокируется вход приемника 1.4. Если в течение периода времени 2 Tц не приходит квитанция, подтверждающая получение кодограммы корреспондентом, то производится повторная передача кодограммы. В случае получения квитанции повторная передача не производится.

Переданная таким образом одним из абонентов кодограмма принимается всеми станциями группы, если по условиям распространения радиоволн между ними есть связь.

При приеме кодограмма с выхода коммутатора 8 поступает на вход декодера 2, осуществляющего ее декодирование, а также выделение адресной части, признака транзита, признака приоритета и информационной части кодограммы.

Адресная часть кодограммы записывается в блок 4.2 выбора маршрута. Если адрес данной станции совпадает с адресом принятой кодограммы, то с блока 4.2 поступает единица на вход пятого элемента И 5, разрешая выдачу кодограммы абоненту данной станции через выходную шину.

При выделении признака транзита с выхода блока 4.2 поступает единица на вход второго элемента И 3.3, разрешая запись кодограммы через второй элемент И 3.3 в блок 3.9 запоминания.

Одновременно сигналом с выхода второго элемента И 3.3 разрешается запись в первой регистр 3.7 памяти с второго кодера 3.1 номера передатчика и осуществляется запуск блока 4.2 выбора маршрута. Записываемая информация в блок 3.9 запоминания и первый регистр 3.7 памяти поступает в параллельном коде.

По сигналу с выхода второго элемента И 3.3 блок выбора маршрута 4.2 после определения номера приемника 1.4 выдает на один из входов третьего кодера 3.2 единицу, таким образом, адрес приемника 1.4 с выхода третьего кодера 3.2 записывается в адресную часть транзитного сообщения в первом регистре 3.7 памяти.

Блок 4.1 осуществляет подсчет искаженных кодовых комбинаций и при превышении порогового числа выдает сигнал "Ноль", а если качество канала в норме, то выдает сигнал "Единица". Этот сигнал с выхода блока 4.1 поступает на вход блока 4.2, разрешая или запрещая запись информации о состоянии каналов связи станций группы между собой.

Блоки, вошедшие в устройство из прототипа, могут быть реализованы по следующим схемам: передатчик 1.1 (рис. 5.25 [5]), хронизатор 1.2 (фиг. 15), формирователь кода частоты 1.3 (рис. 2 [6]), приемник 1.4, 6 (рис. 6.33 [7] ), первый кодер 1.5 (рис. 6.17 [1]); блок контроля занятости канала 1.6 (рис. 10.9 [3]), элемент И 1.7, 3.3 - 3.5, 5 (рис. 2.9 [2]), блок формирования приоритета 1.8 (рис. 9.26 [3]), блок ввода сообщения 1.9 (рис. 3.31 [1] ), второй 3.1 и третий 3.2 кодер (рис. 3.45 [1]), компаратор 3.6 (рис. 2.191 [2] ), первый 3.7 регистр памяти (рис. 3.1 [1]), второй 3.8 регистр памяти (рис. 2.129 [2]), блок запоминания 3.9 (рис. 9.1 [3]), блок контроля качества сигнала 4.1 (рис. 2.66 [2]), блок выбора маршрута 4.1 (фиг. 2 [4]), декодер 2 (рис. 6.18 [1]).

Введенный в предлагаемое устройство блок адаптера мультиплексного канала может быть реализован на микросхемах ТТЛ серий 555 и 1533.

Оценка положительного эффекта.

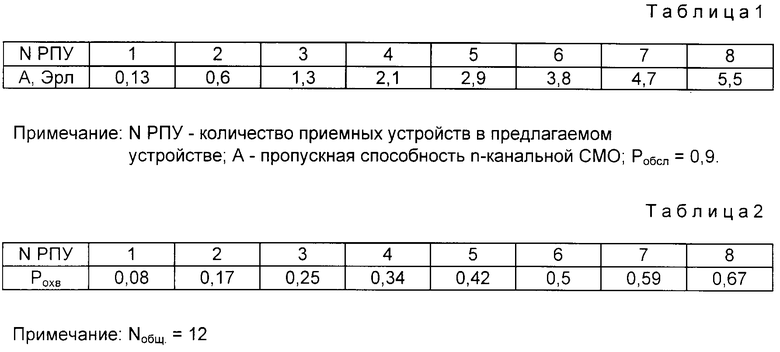

Аналог и прототип предлагаемого устройства являются одноканальными и могут быть представлены в виде системы массового обслуживания, пропускная способность которой для типовых условий функционирования при вероятности обслуживания не хуже 0,9 не превышает 0,15 Эрл. При наличии в рабочей зоне 10-12 источников передачи информации каждый создает нагрузку в канале до 0,4 Эрл. Одноканальная СМО с последовательным опросом источника не в состоянии обслужить суммарную нагрузку 5,5 Эрл. Следовательно, для достижения значения Pобсл= 0.9 требуется задействовать несколько одноканальных устройства приема и передачи информации.

Введение новых блоков и связей в устройство приема и передачи информации позволяет увеличить пропускную способность до 5,6 Эрл при Pобсл > 0.9 без существенного увеличения аппаратных затрат, как в случае использования нескольких самостоятельных одноканальных устройств приема и передачи информации (табл. 1).

Для обеспечения полного анализа радиоэлектронной обстановки в зоне связи предлагаемым устройством повышается вероятность охвата контролем источников информации Pохв=Nохв.ист./Nобщ. (табл.).

Таким образом, введение новых блоков и связей в предлагаемом устройстве передачи и приема информации повышает пропускную способность и охват наблюдения одновременно работающих радиостанций в группе. Следовательно, имеет место выигрыш в сравнении с известными устройствами аналога и прототипа.

Список литературы

1. Шляпоберский В.В. Основы техники передачи дискретных сообщений. - М.: Связь, 1973.

2. Цифровые интегральные микросхемы: Справочник./ Богданович М.И., Грель И.Н., Порхоменко В.А., Шалимо В.В. - Минск: Беларусь, 1991.

3. Ерофеев Ю.Н. Импульсная техника: Учебное пособие для радиотехн. спец. вузов. - М.: Высш. шк., 1984.

4. Авт. свид. СССР N 1453605, кл. H 04 B 7/26, 1989.

5. Воробьев И.М. Оборудование и эксплуатация радиостанций. - М.: Связь, 1977.

6. Прибор 1-ОМ. Техническое описание. ТЦ.2.081.126 ТО, кн. 1, редакция 2-68.

7. Радиоприемное устройство Р-155У. Техническое описание и инструкция по эксплуатации. ЦЛ2.003.001 ТО, ч. I. Изд. N 3/29579р-П3.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФИЛЬТРОВАЯ СИСТЕМА РАДИОПЕРЕДАТЧИКА | 1993 |

|

RU2076454C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ГРУППОВОГО СИГНАЛА | 1998 |

|

RU2144266C1 |

| УСИЛИТЕЛЬ С РАСПРЕДЕЛЕННЫМ УСИЛЕНИЕМ | 1998 |

|

RU2137288C1 |

| ГЕНЕРАТОР БЕЛОГО ШУМА (ВАРИАНТЫ) | 1997 |

|

RU2120179C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1998 |

|

RU2144267C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА РАДИОСТАНЦИЙ | 1994 |

|

RU2099868C1 |

| СПОСОБ ШИФРОВАНИЯ/ДЕШИФРОВАНИЯ СООБЩЕНИЙ ХЭШИРУЮЩЕЙ ФУНКЦИЕЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1998 |

|

RU2138126C1 |

| РЕЗЕРВИРОВАННЫЙ УСИЛИТЕЛЬ | 1996 |

|

RU2115275C1 |

| СПОСОБ СКРЕМБЛИРОВАНИЯ АНАЛОГОВОГО СИГНАЛА И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1997 |

|

RU2123764C1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ N-РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ | 1994 |

|

RU2080651C1 |

Изобретение относится к технике электросвязи и передачи данных. Целью изобретения является разработка устройства передачи и приема информации, обеспечивающего повышение пропускной способности и полноты наблюдения за каналами передачи информации радиостанций, работающих в группе, а также более эффективное решение задач радиомониторинга. Цель достигается тем, что в известное устройство передачи и приема информации дополнительно введены n приемников (n ≤ 7) адаптер мультиплексного канала, коммутатор, которые обеспечивают режим радиомониторинга радиостанций, работающих в группе. Адаптер мультиплексного канала производит объединение асинхронных низкоскоростных дискретных потоков, поступающих с выходов всех приемников устройства, их буферизацию и синхронный вывод по шине взаимодействия с персональной ЭВМ. Введение новых блоков и связей позволяет повысить пропускную способность устройства, а также процент охвата одновременным наблюдением работающих в группе радиостанций. 6 з.п. ф-лы, 2 табл., 18 ил.

| SU, авторское свидетельство, 1453605, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1998-03-27—Публикация

1996-02-19—Подача