Изобретение относится к области вычислительной техники и может быть использовано в качестве устройства для поиска детерминированных комбинаций в информационном массиве.

Известный аналог предлагаемого устройства описан в авт. св. СССР N 1621049, кл. G 06 F 15/40, заявленном 09.01.89, и содержит регистры границ, суммирующие и вычитающие счетчики, схемы сравнения, блоки памяти, блоки вычисления и ряд других элементов, позволяющих осуществлять поиск информации. Однако указанная операция реализуется в нем с низкой оперативностью.

Ближайшее устройство поиска информации (прототип) к предлагаемому описано в авт.св. СССР N 1711185, кл. G 06 F 15/40, заявленном 05.04.89. В указанном изобретении описано устройство поиска информации, содержащее регистры верхней и нижней границ, сумматор-вычитатель, регистр стратегии поиска, вычитающий и суммирующие счетчики, схемы сравнения, блок памяти, регистр ключа, выходной регистр, группы элементов И и ИЛИ, триггер, распределитель импульсов, вход запуска, входы адресов верхней и нижней границ, вход кода критерия смены стратегии поиска, вход ключа, выход адреса, выход признака отсутствия информации. Описанное устройство обладает более высокой оперативностью по сравнению с выше отмеченным.

Однако устройство-прототип реализует поиск раритетных информационных блоков в массиве посредством дихотомического метода, что является его недостатком в случае поиска в информационном массиве комбинаций, имеющих высокую вероятность появления, так как снижается оперативность поиска.

Действительно, математическая суть метода половинного деления (дихотомии) заключается в том, что, с целью определения некоторого Δf(x) на отрезке [a, b] , последний делится пополам и в его средней точке c=(a+b)/2 вычисляется значение f(c). Если f(c) = Δf(x) , то для последующего деления пополам выбирается один из следующих двух отрезков [a, c] и [c, b] и т.д. (А.М. Прохоров и др. Математический энциклопедический словарь. М.: Советская энциклопедия, 1988).

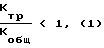

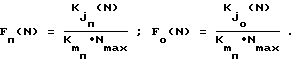

Указанная процедура реализована в уже описанном устройстве поиска требуемых информационных блоков в некотором массиве при условии:

где

Kтр - количество искомых блоков в массиве:

Kобщ - общее количество блоков в массиве.

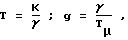

Пусть длина искомого блока - μтр . При этом μтр < μ , где μ - длина элементарной анализируемой реализации (базы анализа) в массиве объема S. В этом случае количество секторов поиска K определяется (В.А.Абчук, Ф.А. Матвейчук, Л.П.Томашевский. Справочник по исследованию операций. М.: Воениздат, 1979):

Следовательно, можно представить:

где

T - общее время поиска в массиве;

γ - скорость поиска;

Tμ = Tперестр. + Tанализа - время, необходимое для анализа одного сектора.

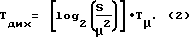

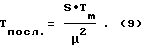

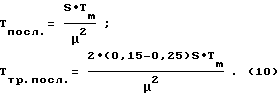

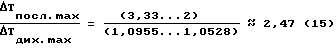

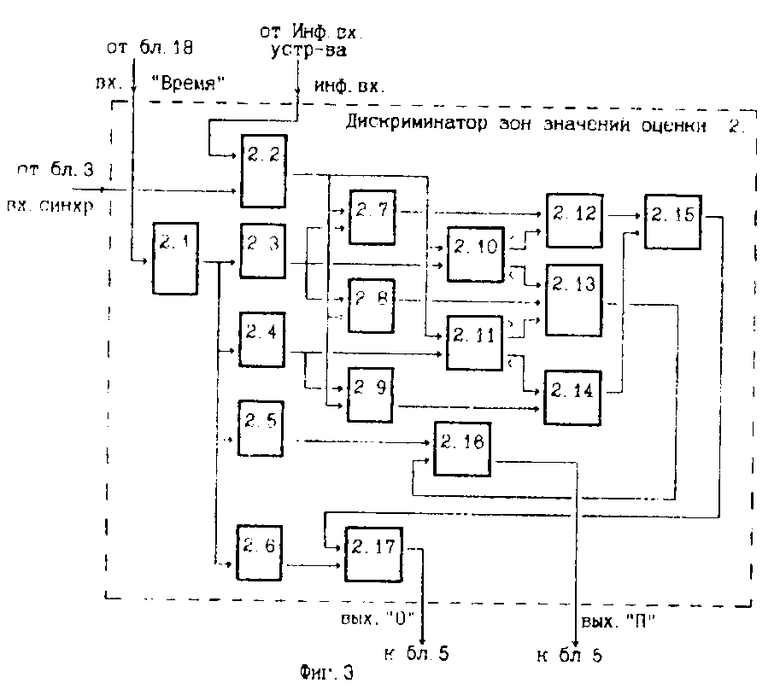

Для дихотомического метода:

Т. е. указанное устройство - прототип требует значительных временных затрат при заданной вероятности правильного решения.

Целью предлагаемого изобретения является построение устройства, обладающего более высокой оперативностью поиска информации при заданной вероятности правильного решения. Объектом распознавания для предлагаемого устройства является состояние обстановки на основании оценки входного трафика, рассматриваемого как информационный массив, в котором присутствуют некоторые детерминированные кодовые комбинации (в данном случае это комбинации начала сообщения - КНС). Именно по КНС оценивается интенсивность входного трафика и, как следствие, состояние обстановки. В дальнейшем этим состояниям соответствуют обозначения "О" - изменения отсутствуют и "П" - изменения присутствуют. Решение о состоянии "П" принимается в случае, когда интенсивность входного трафика имеет отклонение от среднего значения в большую или меньшую сторону, на величину, превышающую пороговое, в противном случае принимается решение о состоянии "О". В свою очередь, верхнее и нижнее значения порогов могут быть либо интервальными, либо точечными, что определяется стратегией поиска, принятой в устройстве поиска на данном этапе.

Поставленная цель достигается тем, что в известном устройстве поиска информации, включающем распределитель импульсов, сумматор-вычитатель, являющийся по существу формирователем переменной поиска, суммирующий счетчик, блок памяти и регистр стратегии поиска, дополнительно введены формирователь сигналов текущей оценки, дискриминатор зон значений оценки, счетчик временных интервалов, коммутатор, вторые формирователь переменной поиска, суммирующий счетчик и блок памяти, блок деления, классификатор, формирователь сигналов сброса, блок индикации, блок изменения пороговых сигналов и таймер текущих суток. Информационные входы формирователя сигналов текущей оценки и дискриминатора зон значений оценки объединены и являются информационным входом устройства. Первый выход распределителя импульсов подключен одновременно к входам синхронизации формирователя сигналов текущей оценки дискриминатора зон значений оценки, а также к тактовому входу счетчика временных интервалов, а второй, третий и четвертый выходы распределителя импульсов подключены соответственно к тактовым входам коммутатора, первого и второго блоков памяти и классификатора. Выход таймера текущих суток подключен одновременно к входам "Время" распределителя импульсов, формирователя сигналов текущей оценки, дискриминатора зон значений оценки и блока изменения пороговых сигналов, выходы значений порогов поиска которого "Пв" и "Пн" подключены к одноименным входам регистра стратегии поиска, выходы значений верхнего и нижнего порогов классификации которого "Пклв" и "Пклн" подключены к соответствующим входам классификатора. Выходы классификатора "П" и "О" подключены одновременно к соответствующим входам блоков индикации и формирователя сигналов сброса, выход которого подключен одновременно к входам "Сброс" первого и второго блоков памяти, счетчика временных интервалов и регистра стратегии поиска, вход "Nтекщ" которого соединен с выходом счетчика временных интервалов. Выход первого формирователя переменной поиска подключен к первому информационному входу первого суммирующего счетчика, второй информационный вход которого подключен к выходу первого блока памяти, а выход первого суммирующего счетчика соединен одновременно с информационным входом первого блока памяти и первым информационным входом блока деления. Выход блока деления соединен с информационным входом классификатора. Выход второго суммирующего счетчика подключен одновременно к второму информационному входу блока деления и информационному входу второго блока памяти, выход которого соединен с вторым информационным входом второго суммирующего счетчика, первый информационный вход которого подключен к выходу второго формирователя переменной поиска, информационный вход которого соединен с выходом "0" коммутатора, а выход "П" коммутатора соединен с информационным входом первого формирователя переменной поиска. Входы "Nmax" первого и второго формирователей переменной поиска, а также регистра стратегии поиска подключены одновременно к одноименному входу устройства. Входы "Зона 1" и "Зона 2" устройства являются входами "Зона" соответственно первого и второго формирователей переменной поиска. Управляющий вход коммутатора подключен к выходу формирователя сигналов текущей оценки, а входы коммутатора "П" и "О" подключены к соответствующим выходам дискриминатора зон значений оценки. Входы "Порог" и "Пуск" устройства соединены с одноименными входами блока изменения пороговых сигналов.

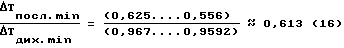

Формирователь сигналов текущей оценки состоит из дешифратора, первого и второго шифраторов коэффициента счета, первого и второго счетчиков, а также элементов НЕ и ИЛИ. Вход "Время" формирователя является входом дешифратора, а его выход соединен одновременно с входами первого и второго шифраторов. Сигнал с выходов этих шифраторов поступает на входы установки коэффициентов счета соответственно первого и второго счетчиков, счетные входы которых подключены одновременно к информационному входу, а тактовые - к входу синхронизации формирователя. Выход первого счетчика соединен с первым входом элемента ИЛИ, на второй вход которого через элемент НЕ поступает сигнал с выхода второго счетчика. Выход элемента ИЛИ является выходом формирователя.

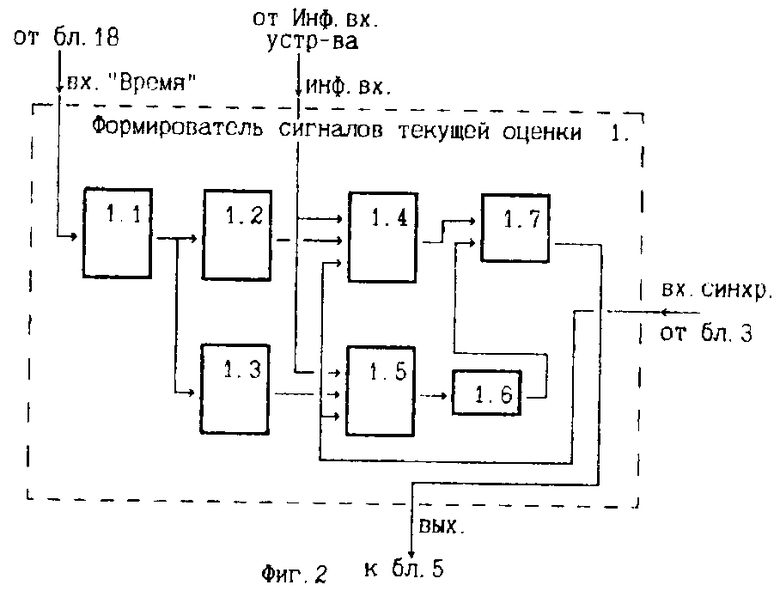

Дискриминатор зон значений оценки состоит из дешифратора, счетчика, первого, второго, третьего и четвертого шифраторов, первого, второго и третьего вычитателей, первого и второго компараторов, первого, второго и третьего ключей, схемы ИЛИ, а также первого и второго устройств деления. Вход "Время" дискриминатора является входом дешифратора, выход которого подключен одновременно к входам всех шифраторов. Информационный вход и вход синхронизации дискриминатора являются соответственно информационным и тактовым входами счетчика, выход которого подключен одновременно к входам уменьшаемого первого вычитателя, а также вычитаемого второго и третьего вычитателей и к информационным входам обоих компараторов. Пороговый вход первого компаратора, вход вычитаемого первого и вход уменьшаемого второго вычитателей объединены и подключены к выходу первого шифратора. А пороговый вход второго компаратора и вход уменьшаемого третьего вычитателя объединены и подключены к выходу второго шифратора. Выходы третьего и четвертого шифраторов соединены с входами делимого соответственно первого и второго устройств деления, входы делителя которых соединены соответственно с выходом второго ключа и выходом схемы ИЛИ. Выходы первого, второго и третьего вычитателей соединены с информационными входами соответственно первого, второго и третьего ключей, а выходы первого и третьего ключей соединены соответственно с первым и вторым входами схемы ИЛИ. Выходы "<" первого и второго компараторов соединены соответственно с первым управляющим входом второго и управляющим входом третьего ключей, а их выходы ">" соединены соответственно с управляющим входом первого ключа и с вторым управляющим входом второго ключа. Выходы первого и второго устройств деления являются соответственно выходами "П" и "О" дискриминатора.

Классификатор состоит из первого и второго компараторов и первого и второго ключей. Информационные входы первого и второго компараторов подключены одновременно к информационному входу блока, а их пороговые входы - соответственно к входам "Пклв" и "Пклн" блока. Выход ">" первого компаратора соединен с информационным входом первого ключа, а выход "<" второго компаратора - с информационным входом второго ключа. Управляющие входы ключей подключены одновременно к тактовому входу классификатора, а выходы первого и второго ключей являются соответственно выходами "П" и "О" классификатора.

Регистр стратегии поиска состоит из первого и второго регистров, первого и второго вычитателей, устройства деления на два, компаратора, первого, второго и третьего ключей, а также первой и второй схем ИЛИ. Информационный вход компаратора соединен с входом "Nтекщ", а пороговый вход - с входом "Nmax регистра стратегии поиска. Информационные входы первого и второго регистров соединены соответственно с входами "Пв" и "Пн" регистра стратегии поиска. Выход первого регистра соединен одновременно с входами уменьшаемого первого и второго вычитателей и информационным входом первого ключа, а выход второго регистра соединен одновременно с входом вычитаемого первого вычитателя и информационным входом третьего ключа. Выход первого вычитателя соединен с входом устройства деления на два, выход которого соединен с входом вычитаемого второго вычитателя. Выход второго вычитателя соединен с информационным входом второго ключа, управляющий вход которого соединен с выходом "≥" компаратора. Выход "<" компаратора соединен одновременно с управляющими входами первого и третьего ключей, выходы которых подключены к первым входам соответственно первой и второй схем ИЛИ. Вторые входы схем ИЛИ объединены и подключены к выходу второго ключа. Выходы первой и второй схем ИЛИ являются выходами соответственно "Пклв" и "Пклн" регистра стратегии поиска, а входы начальной установки обоих регистров подключены одновременно к входу "Сброс" регистра стратегии поиска.

Благодаря такой совокупности блоков и их соединений достигается возможность сокращения общего времени поиска T при различном процентном соотношении Ктр к Кобщ при условии равной вероятности правильного распознавания.

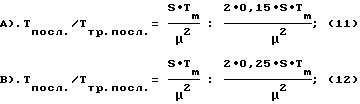

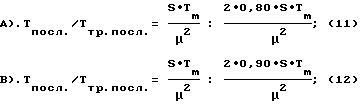

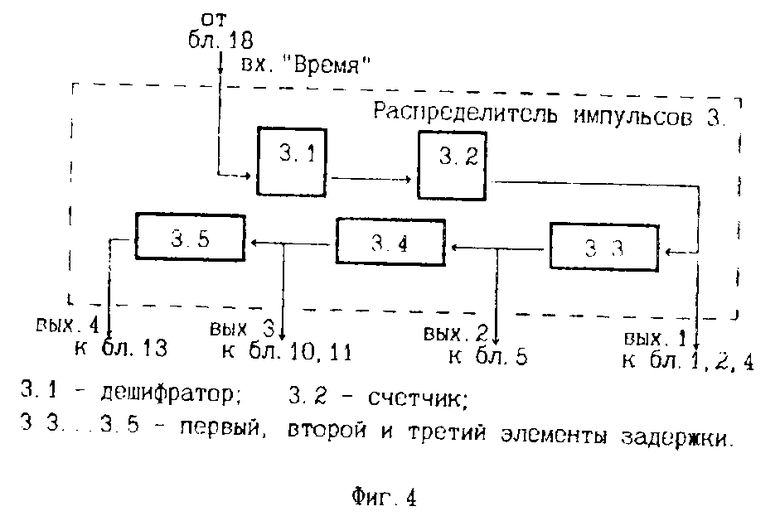

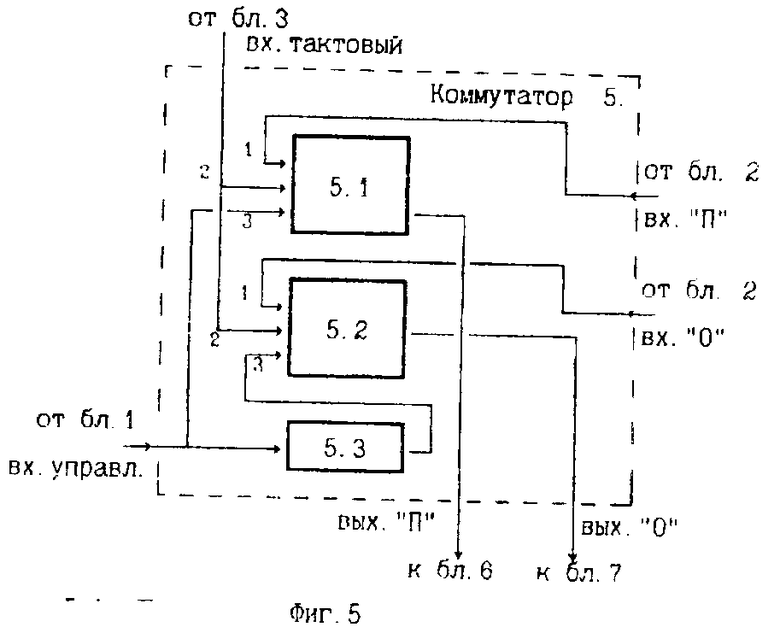

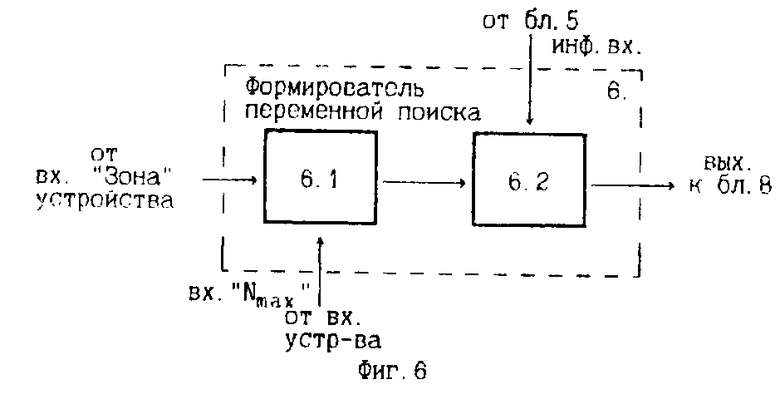

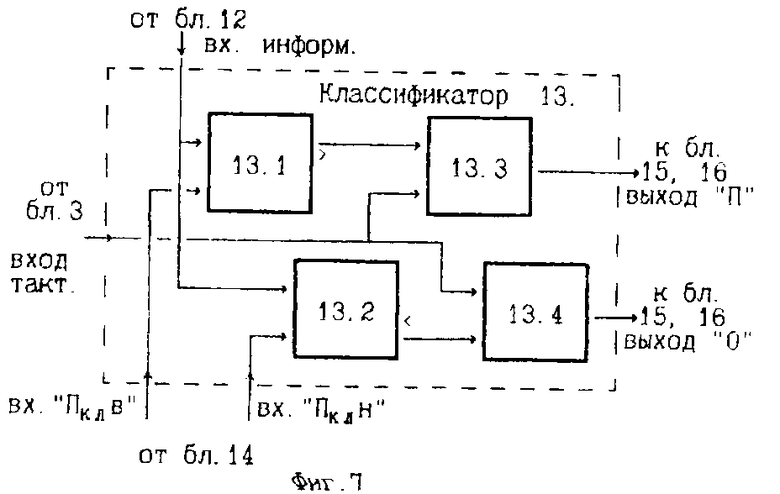

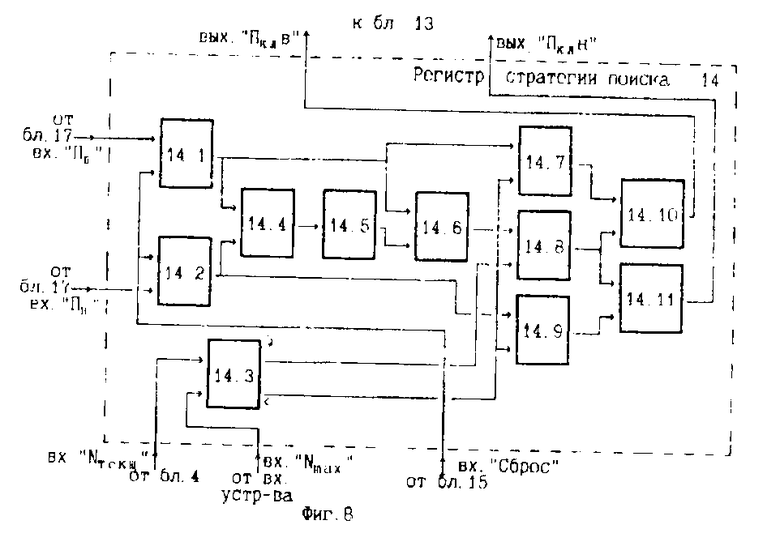

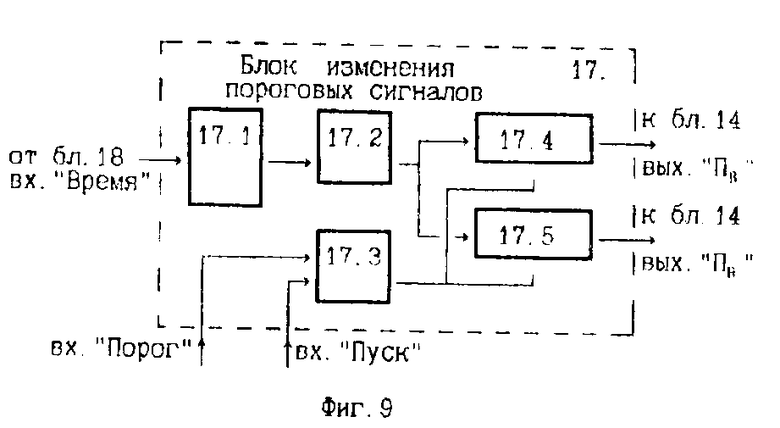

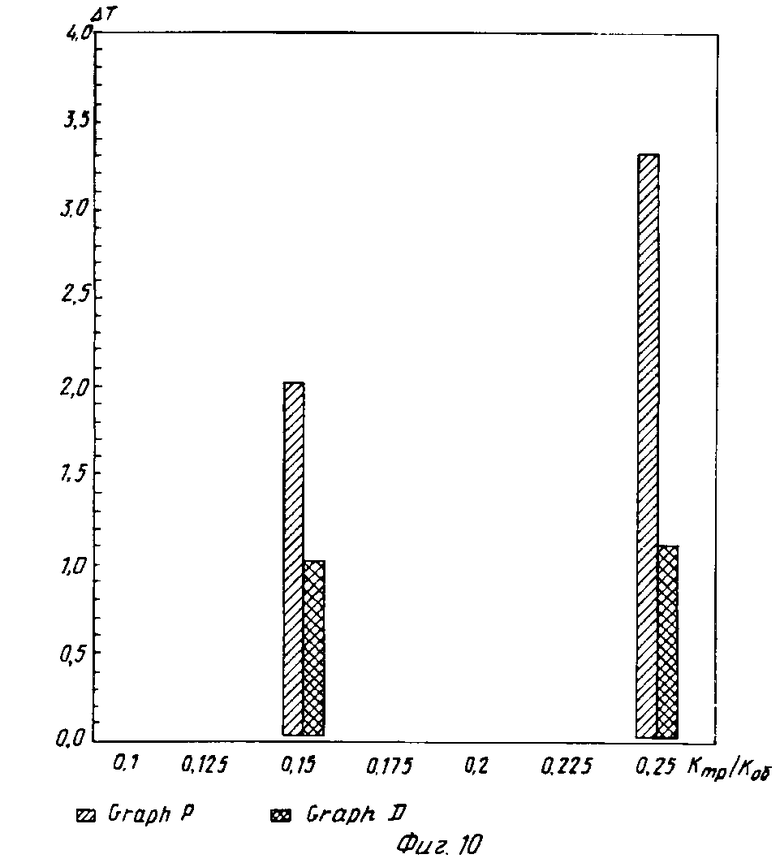

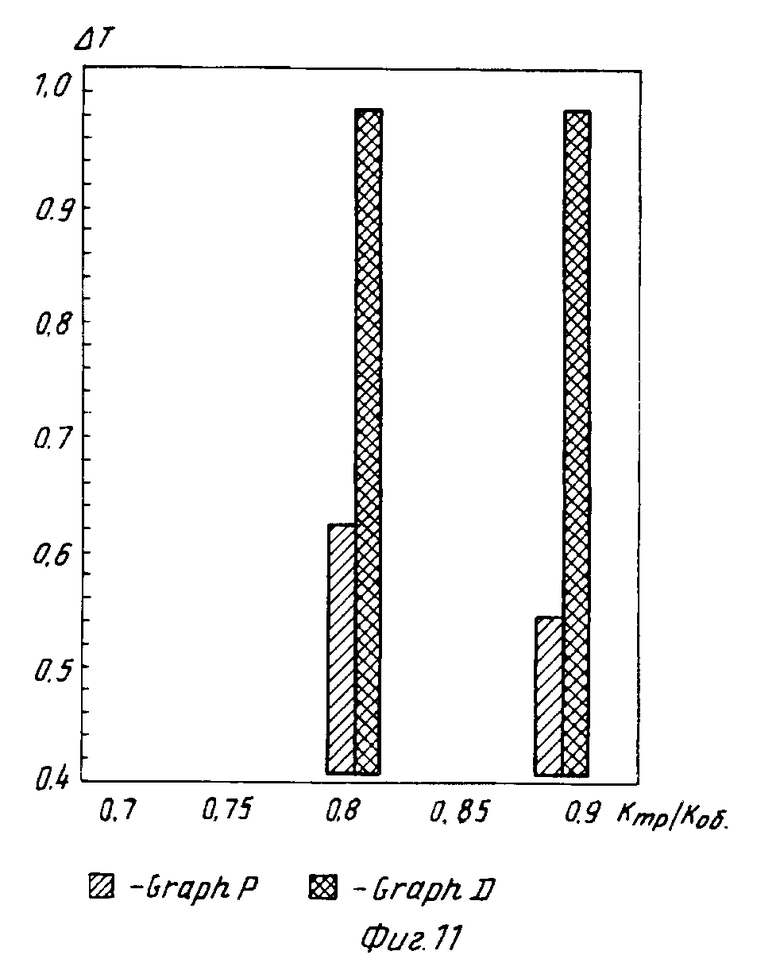

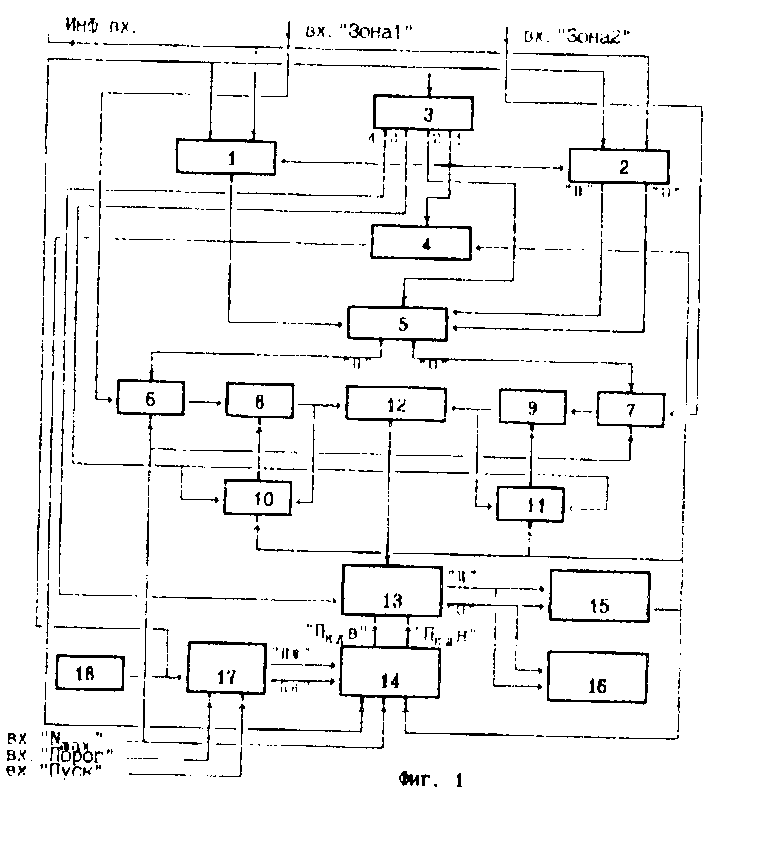

На фиг. 1 показана общая схема устройства поиска информации; на фиг. 2 - формирователь сигналов текущей оценки; на фиг. 3 - дискриминатор зон значений оценки; на фиг. 4 - распределитель импульсов; на фиг. 5 - коммутатор; на фиг. 6 - формирователь переменной поиска; на фиг. 7 - классификатор; на фиг. 8 - регистр стратегии поиска; на фиг. 9 - блок изменения пороговых сигналов; на фиг. 10 - сравнительный график последовательного и дихотомического методов поиска информации при Ктр=(0,15-0,25)Кобщ; на фиг. 11 - сравнительный график последовательного и дихотомического методов поиска информации при Ктр=(0,80-0,90)Кобщ.

Устройство, показанное на фиг. 1, содержит формирователь 1 сигналов текущей оценки, дискриминатор 2 зон значений оценки, распределитель 3 импульсов, счетчик 4 временных интервалов, коммутатор 5, первый 6 и второй 7 формирователи переменной поиска, первый 8 и второй 9 суммирующие счетчики, первый 10 и второй 11 блоки памяти, блок 12 деления, классификатор 13, регистр 14 стратегии поиска, формирователь 15 сигналов сброса, блок 16 индикации, блок 17 изменения пороговых сигналов, таймер 18 текущих суток.

Информационные входы формирователя 1 и дискриминатора 2 объединены и являются информационным входом устройства. Первый выход распределителя 3 импульсов подключен одновременно к входам синхронизации формирователя 1, дискриминатора 2, а также к тактовому входу счетчика 4. Второй, третий и четвертый выходы распределителя 3 подключены соответственно к тактовым входам блоков 5, 10-11 и 13. Выход таймера 18 подключен к входам "Время" формирователя 1 и дискриминатора 2, входам распределителя 3 и блока 17, выходы "Пв" и "Пн" порогов которого подключены к соответствующим входам регистра 14. Выходы "Пклв" и "Пклн" порогов классификации регистра 14 подключены к соответствующим входам классификатора 13, выходы которого "П" и "О" соединены одновременно с соответствующими входами блоков 15 и 16. Информационный вход классификатора 13 соединен с выходом блока деления 12. Выход формирователя 15 сигналов сброса подключен одновременно к входам "Сброс" счетчика 4, блоков 10-11 памяти и регистра 14. Входы "Nтекщ" и "Nmax" регистра 14 соединены соответственно с выходом счетчика 4 и входом "Nmax" устройства. Выход формирователя 6 подключен к первому информационному входу счетчика 8, второй информационный вход которого подключен к выходу блока 10. Выход счетчика 8 соединен одновременно с информационным входом блока 10 памяти и первым информационным входом блока 12 деления. Аналогично соединениям блоков 6, 8, 10 соединены и блоки 7, 9, 11 - выход формирователя 7 подключен к первому входу счетчика 9, второй вход которого подключен к выходу блока 11, выход счетчика 9 соединен одновременно с информационным входом блока 11 и вторым входом блока 12 деления. Информационные входы формирователей 6 и 7 соединены соответственно с выходами коммутатора "П" и "О", а их входы "Nmax" объединены и подключены к одноименному входу устройства. Вход "Зона" формирователя 6 соединен с входом "Зона 1" устройства, а вход "Зона" формирователя 7 - с входом "Зона 2" устройства. Управляющий вход коммутатора 5 соединен с выходом формирователя 1, а информационные входы коммутатора "П" и "О" - с соответствующими выходами дискриминатора 2.

Формирователь сигналов текущей оценки, показанный на фиг. 2, по окончании текущего интервала анализа вырабатывает двоичный сигнал, характеризующий состояние обстановки. Сигнал этот, принимая значения "П" или "О", поступает затем на управляющий вход коммутатора 5. Формирователь состоит из дешифратора 1.1, первого 1.2 и второго 1.3 шифраторов коэффициента счета, первого 1.4 и второго 1.5 счетчиков, элементов НЕ 1.6 и ИЛИ 1.7. Вход дешифратора 1.1 является входом "Время" формирователя, а выход дешифратора соединен с входом шифраторов 1.2 и 1.3, сигнал с выходов которых поступает на входы установки коэффициентов счета соответственно счетчиков 1.4. и 1.5. Счетные входы счетчиков подключены одновременно к информационному входу формирователя. Выход счетчика 1.4 соединен с первым входом элемента ИЛИ, на второй вход которого через элемент 1.6 поступает сигнал со счетчика 1.5. Выход элемента 1.7 является выходом формирователя, а вход начальной установки счетчиков соединен с входом синхронизации формирователя.

На фиг. 3 показан дискриминатор зон значений оценки, который вырабатывает сигнал о номере зоны того состояния, в котором находится входной поток соответствующей интенсивности, и состоит из дешифратора 2.1, счетчика 2.2, шифраторов 2.3, 2.4, 2.5 и 2.6, вычитателей 2.7, 2.8 и 2.9, компараторов 2.10 и 2.11, ключей 2.12, 2.13 и 2.14, схемы ИЛИ, а также устройств деления 2.16 и 2.17. Вход "Время" дискриминатора является входом дешифратора, выход которого подключен одновременно к входам всех шифраторов. Информационный вход и вход синхронизации дискриминатора являются соответственно информационным и тактовым входами счетчика, выход которого подключен одновременно к входам уменьшаемого вычитателя 2.7, вычитаемого вычитателей 2.8 и 2.9, а также к информационным входам обоих компараторов. Пороговый вход компаратора 2.10, вход вычитаемого вычитателя 2.7 и уменьшаемого вычитателя 2.8 объединены и подключены к выходу шифратора 2.3. Пороговый вход компаратора 2.11 и вход уменьшаемого вычитателя 2.9 объединены и подключены к выходу шифратора 2.4. Выходы шифраторов 2.5 и 2.6 соединены с входами делимого соответственно устройств деления 2.16 и 2.17, входы делителя которых соединены соответственно с выходом ключа 2.13 и выходом схемы ИЛИ. Выходы вычитателей 2.7, 2.8 и 2.9 соединены соответственно с информационными входами ключей 2.12, 2.13 и 2.14. Выходы ключей 2.12 и 2.14 соединены соответственно с первым и вторым входами схемы ИЛИ. Выходы "<" компараторов 2.10 и 2.11 соединены соответственно с первым управляющим входом ключа 2.13 и управляющим входом ключа 2.14, а выходы ">" этих компараторов соединены соответственно с управляющим входом ключа 2.12 и с вторым управляющим входом ключа 2.13. Выходы устройств деления 2.16 и 2.17 являются соответственно выходами "П" и "О" дискриминатора.

На фиг. 4 приведена схема распределителя импульсов, предназначенного для синхронизации работы всего устройства посредством формирования четырех импульсных последовательностей, сдвинутых друг относительно друга на некоторую величину Δt . Распределитель состоит из дешифратора 3.1, счетчика 3.2 и элементов задержки 3.3, 3.4, 3.5. Вход распределителя импульсов соединен с входом дешифратора, с выхода которого сигнал поступает на вход счетчика. Выход счетчика соединен с входом первого элемента 3.3 задержки, с выхода которого сигнал поступает на вход второго элемента 3.4 задержки, выход которого соединен с входом третьего элемента задержки. Выходы счетчика, а также первого, второго и третьего элементов задержки являются соответственно первым, вторым, третьим и четвертым выходами распределителя импульсов.

Коммутатор, показанный на фиг. 5, осуществляет коммутацию сигнала о номере зоны на вход соответствующего формирователя переменной поиска по сигналу управления, поступающему от блока 1, и принимающему значению "П" и "О". Коммутатор состоит из двух элементов И 5.1 и 5.2 и элемента НЕ 5.3, первые входы элементов И 5.1 и 5.2 соответственно соединены с входами "П" и "О" коммутатора, вторые - с тактовым входом коммутатора, вход управления коммутатора соединен с третьим входом элемента 5.1 и входом элемента НЕ 5.3, выход которого соединен с третьим входом элемента 5.2, выходы элементов И 5.1 и 5.2 являются соответственно выходами коммутатора "П" и "О".

Формирователи переменной поиска 6 и 7 (фиг. 6) предназначены для построения приращений апостериорных интегральных функций распределения вероятностей нормального Fo(N) (блок 6) и отклоненного Fп(N) (блок 7) состояния трафика на N-м интервале наблюдения. Так как схемы формирователей 6 и 7 индентичны, то здесь показан только формирователь 6, который состоит из умножителя 6.1, первый и второй входы которого соединены соответственно с входами "Зона" и "Nmax" формирователя, а также из устройства 6.2 деления, на вход делителя которого подается результат умножения от умножителя 6.1, а вход делимого соединен с информационным входом формирователя. Выход устройства деления соединен с выходом формирователя.

Классификатор, показанный на фиг. 7, вырабатывает сигнал "П" или "О" на основе сравнения входной информации с пороговыми значениями и состоит из первого 13.1 и второго 13.2 компараторов, первого 13.3 и второго 13.4 ключей. Информационные входы компараторов 13.1 и 13.2 подключены одновременно к информационному входу классификатора, а их пороговые входы - соответственно к входам "Пклв" и "Пклн" классификатора. Выход ">" компаратора 13.1 соединен с информационным входом ключа 13.3, а выход "<" компаратора 13.2 - с информационным входом ключа 13.4. Управляющие входы ключей подключены одновременно к тактовому входу классификатора, их выходы являются соответственно выходами "П" и "О" классификатора.

На фиг. 8 изображена схема регистра стратегии поиска, который формирует интервальное либо точечное значение порогов классификации в зависимости от того, является ли номер интервала поиска предельным, или нет. Он состоит из регистров 14.1, 14.2, компаратора 14.3, вычитателей 14.4 и 14.6, устройства деления на два 14.5, ключей 14.7, 14.8, 14.9, схем ИЛИ 14.10, 14.11. Информационный вход компаратора соединен с входом "Nтекщ", а его пороговый вход - с входом "Nmax" регистра стратегии поиска. Информационные входы регистров 14.1 и 14.2 соединены соответственно с входами "Пв" и "Пн" регистра стратегии поиска. Выход регистра 14.1 соединен одновременно с входами уменьшаемого вычитателей 14.4 и 14.6 и информационным входом ключа 14.7. Выход регистра 14.2 соединен одновременно с входом вычитаемого вычитателя 14.4 и информационным входом ключа 14.9. Выход вычитателя 14.4 соединен с устройством деления на два, выход которого соединен с входом вычитаемого вычитателя 14.6. Выход вычитателя 14.6 соединен с информационным входом ключа 14.8, управляющий вход которого соединен с выходом ">" компаратора. Выход компаратора "<" соединен одновременно с управляющими входами ключей 14.7 и 14.9, выходы которых подключены к первым входам схем ИЛИ соответственно 14.10 и 14.11. Вторые входы схем ИЛИ 14.10 и 14.11 объединены и подключены к выходу ключа 14.8, а их выходы являются соответственно выходами "Пклв" и Пклн" регистра стратегии поиска. Входы начальной установки обоих регистров подключены одновременно к входу "Сброс" регистра стратегии поиска.

Блок изменения пороговых сигналов (фиг. 9) предназначен для изменения значений пороговых сигналов в зависимости от времени суток и состоит из дешифратора 17.1, шифратора 17.2, регистра 17.3, сумматора 17.4 и вычитателя 17.5. Вход блока "Время" соединен с входом дешифратора, выход которого соединен с входом шифратора. Выход шифратора подключен одновременно к входу первого слагаемого сумматора и вычитаемого вычитателя. Информационный и тактовый входы регистра соединены соответственно с входом "Порог" и "Пуск" блока, а его выход подключен одновременно к входу второго слагаемого сумматора и уменьшаемого вычитателя. Выходы сумматора и вычитателя являются соответственно выходами "Пв" и "Пн" блока.

Блоки и устройства, не раскрытые в данном описании, могут быть реализованы известными из литературы способами (схемами), возможные варианты построения которых приводятся ниже.

Счетчики: 4, 1.4, 1.5, 2.2, 3.2. Суммирующий счетчик по модулю k=2m образуется путем соединения m триггеров. В качестве примера на рис. 10.4а (Гольденберг Л. М. Импульсные и цифровые устройства. Учебник для ВУЗов. М.: Связь, 1973, с. 496) приведена схема, состоящая из четырех каскадно соединенных триггеров. В таблице 10.4 того же учебника показаны состояния триггеров в зависимости от числа входных импульсов. Если на входе m-разрядного счетчика, состоящего из m последовательно соединенных триггеров, появилось в течение некоторого интервала времени n импульсов, причем:

N = n2m + am2m-1 +am-12m-2 +...+ a120,

где

a1 (i=1,2,3,4...m) =

Дешифраторы: 1.1, 2.1, 3.1, 17.1. Дешифратор имеет n входов и N выходов и выполняет следующую функцию: каждому входному слову (n разрядному входу), т. е. комбинации единиц и нулей на входе, соответствует сигнал "1" на одном определенном выходе; обычно сигнал "1" появляется на той выходной шине, номер которой в двоичной форме совпадает с входным n разрядным кодом. Структура дешифратора на 3 входа и 23=8 выходов показана в (Гольденберг Л.М. Импульсные и цифровые устройства. Учебник для ВУЗов. М.: Связь 1973, с. 496) на рис. 10.12. Аналогичным образом строится дешифратор на n входов и 2n=N выходов.

Шифраторы: 1.2, 1.3, 2.3. . .2.6, 17.2. Шифратор на N входов строится аналогично показанному в (Сикарев А.А., Лебедев О.Н. Микроэлектронные устройства формирования и обработки сложных сигналов. М.: Радио и связь, 1983, с. 216) на рис. 43, с. 49 шифратору на 10 входов и 4 выхода с использованием табл. 15 на с. 48. Причем число выходов n шифратора равно: ,

,

где - наименьшее целое, не меньшее чем X.

- наименьшее целое, не меньшее чем X.

Элементы задержки: 3.3...3.5. Являются линиями задержки (ЛЗ). Сигнал на выходе линии задержки воспроизводится с некоторой задержкой на определенный период времени t3. ЛЗ может быть построена путем последовательного соединения одновходовых схем ИЛИ, каждая из которых для определенного базиса (серии микросхем) имеет t3i. Тогда  .

.

Другая возможная реализация показана в (Гольденберг Л.М. Импульсные и цифровые устройства. Учебник для ВУЗов. М.: Связь., 1973, с. 496) на рис. 1.27.

Компараторы: 2.10. . .2.11, 13.1, 13.2, 14.3. Компаратор выполняет операцию сравнения двух n разрядных чисел A и B и формирует на одном из трех выходов (A<B, A>B, A=B) сигнал "1"; число входов компаратора равно 2n. При сравнении двухразрядных чисел компаратор строится на основе табл. 2.10 на с. 51 (Лебедев О. Н., Сидоров А.М. Импульсные и цифровые устройства. Цифровые узлы и их проектирование на микросхемах. Л.: ВАС, 1980, с.128) и реализован на рис. 2.33 (с. 52). Так как схемы сравнения обладают свойством наращиваемости, то компаратор для сравнения двух n-разрядных чисел строится по аналогии с табл. 2.11, рис. 2.35, с. 53-54, до требуемой величины n.

Регистры 14.1, 14.2, 17.3 и блоки памяти 10, 11 являются регистрами параллельного действия. Построение таких регистров из n входов и n выходов показано в (Шляпоберский В.И. Основы техники передачи дискретных сообщений. М. : Связь, 1973, с. 480) на рис. 3.1, с. 106. Указанные регистры используются также в качестве блоков памяти, хранящих один элемент (операнд) в течение одного интервала анализа.

Сумматор 17.4 и суммирующие счетчики 8,9 являются арифметическими сумматорами. Сумматор (параллельный) строится аналогично рис. 14.17, с.377 (Основы импульсной и цифровой техники. Учебное пособие для ВУЗов. М.: Советское радио, 1975, с. 440), где полусумматор показан на рис. 14.13, а полный сумматор - рис. 14.14.

Вычитатели: 2.7. ..2.9, 14.4, 14.6, 17.5. Вычитатель строится на основе сумматора, на один вход которого подается уменьшаемое, на другой - дополнение до единицы вычитаемого (отрицание вычитаемого - через схему НЕ - поразрядно складывается по модулю два с единицей).

Ключи: 2.12...2.14, 13.3, 13.4, 14.7, 14.8, 14.9. Ключ, в общем случае, строится в виде мультиплексора, принцип построения которого описан в (Лебедев О.Н., Сидоров А.М. Импульсные и цифровые устройства. Цифровые узлы и их проектирование на микросхемах. Л.: ВАС, 1980, с. 128) с.54. Реализация мультиплексора на 8 каналов, управляемых 3-элементным кодом, показана на рис. 2.36, с. 55 (построена на основе табл. 2.12, с.54). При одноразрядном управляющем входе мультиплексор вырождается в простейший ключ, который чаще всего реализуется n-входовыми схемами И.

Устройства деления: 12, 2.16, 2.17, 6.2. Устройство деления двух n-разрядных двоичных чисел строится на основе алгоритма деления без восстановления остатка, описанного в (Бочаров К.П., Немшилов Н.Н., Петров Е.И., Сулин Л.И. Вычислительные комплексы автоматизированных систем управления. Л.: ВАС, 1984, с.368), с.88-90, рис. 3.24 (а). Схема устройства деления представлена на с. 89, рис. 3.24 (б). Результат деления - n-разрядное двоичное число. В случае, когда разрядность поступающих на вход устройства деления чисел разная, за n принимаем большую разрядность. Число с меньшей разрядностью представляем n-разрядным, добавлением в старшие разряды нулей.

Устройство деления на два для двоичных чисел реализуется считыванием операнда с выхода предыдущего устройства без старшего разряда, что и является эквивалентом его деления на два.

Умножитель: 6.1. Умножитель двух n-разрядных двоичных чисел возможно реализовать на основе одной из четырех приведенных в (Бочаров К.П., Немшилов Н. Н. , Петров Е.И., Сулин Л.И. Вычислительные комплексы автоматизированных систем управления. Л. : ВАС, 1984, с.386) на с. 68-69, рис. 3.19, базовых схем умножения, которые описаны на с. 65-71. Результат умножения - 2n-разрядное двоичное число. В случае, когда разрядность перемножаемых чисел разная, за n принимаем большую разрядность. Число с меньшей разрядностью представляем n-разрядным, добавлением в старшие разряды нулей.

Формирователь сигналов сброса представляет собой схему объединения сигналов "П" и "О", а также их усиления и согласования с последующими блоками. Может быть выполнен в виде двухвходовой схемы ИЛИ с повышенной нагрузочной способностью.

Устройство поиска информации работает следующим образом.

Для минимизации объема выборки применяется последовательная процедура выбора решения. При этом размер выборки не фиксируется, а ограничивается в процессе работы в зависимости от результата предшествующих наблюдений. Процедура принятия решения становится многошаговой. Вначале наблюдается одно значение случайной величины и по заранее установленному правилу либо прекращается наблюдение и принимается решение, либо наблюдение продолжается. Если правило предписывает отказ от решения, то оценивают следующую выборку. Испытание заканчивается на той же выборке, на основании которой наблюдение в соответствии с правилом остановки прекращается и принимается решение (В.В. Поповский. Математическое моделирование сложных систем. Л., ВАС, 1990).

При использовании последовательного правила момент остановки процесса наблюдения является случайным, следовательно, размер выборки, при которой выносится окончательное решение, является величиной случайной. В конкретном случае размер выборки может оказаться чрезмерно большим и последовательная процедура более длительной, чем непоследовательная.

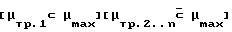

Для устранения этого недостатка в предлагаемом устройстве применяется усеченная последовательная процедура, при которой максимальный объем выборки ограничивается некоторым числом Nmax. При такой процедуре для всех N<Nmax устанавливаются, как и для неусеченного правила, интервальные значения порогов, с которыми сравнивается отношение правдоподобия. Если размер анализируемой выборки достигает Nmax, то устанавливаются точечные значения порогов, при которых в любом случае принимается решение, и цикл наблюдения повторяется. В свою очередь, значения порогов изменяются в зависимости от времени суток, поскольку этот фактор определяет количественные показатели входного трафика. Варьирование пороговыми значениями сокращает время принятия решения при обеспечении заданных требований по вероятности ложной тревоги (α) и пропуска сигнала (β).

Как уже отмечалось выше, состояние обстановки оценивается по интенсивности входного трафика на N+1 интервале наблюдения, которая определяется через интенсивность поступления комбинаций КНС. Степень интенсивности представляет собой информационный массив, разделенный на два класса "П" и "О", соответствующие оценкам "Присутствует" и "Отсутствует". Описанием класса состояний "П" является Fп(N) - эмпирическая интегральная функция распределения выборочных значений коэффициента разброса Kj, предшествующих оценкам "П"N+1. Описанием класса "0" является функция F0(N), построенная по значениям Kj, предшествующим оценкам "0"N+1.

Данными для статистических выводов являются случайные значения коэффициента разброса Kj, измеренные на некоторых интервалах времени tN, где 1 < N < Nmax (Э. Мушик, П. Мюллер. Методы принятия технических решений. М.: Мир, 1990).

Задача анализа выборки сводится к усеченной последовательной процедуре принятия решения, при которой после каждого наблюдаемого интервала времени tN вычисляется отношение правдоподобия:

и величина L(N) сравнивается с нижним и верхним порогами классификации:

где

α и β - заданные вероятности ложной тревоги и пропуска сигнала соответственно.

Входной информационный поток поступает на информационные входы формирователя 1 сигналов текущей оценки и дискриминатора 2 зон значений оценки.

В формирователе 1 (фиг.2) сигнал текущего времени суток с входа "Время" формирователя в виде кода времени поступает на вход дешифратора 1.1 и затем на шифраторы 1.2 и 1.3, которые формируют сигналы, соответствующие верхней и нижней границам диапазона поиска. Этими сигналами изменяются коэффициенты пересчета счетчиков 1.4 и 1.5 в соответствии с законом изменения интенсивности поступления КНС от времени суток, При превышении отклонения числа КНС от среднего значения в верхнюю или нижнюю сторону больше порогового на выходе соответствующего счетчика (1.4 или 1.5) формируется сигнал "П", в других случаях вырабатывается сигнал "О". В начале каждого интервала анализа осуществляется начальная установка счетчиков сигналом, поступающим с входа синхронизации формирователя.

В дискриминаторе зон значений оценки (фиг. 3) входной поток КНС подсчитывается счетчиком 2.2 за интервал времени, определяемый периодом тактируемой последовательности. Полученное значение числа КНС - SКНС сравнивается на компараторах 2.10 и 2.11 с верхним и нижним пороговыми значениями - SПВ и SПН, которые определяют области значений, соответствующих состояниям обстановки "П" и "О": область состояния "О" находится между верхним и нижним порогами, а область "П" - ниже нижнего порога и выше верхнего порога. SПВ формируется дешифратором и шифратором 2.3, а SПН - дешифратором и шифратором 2.4. SКНС сравнивается на компараторе 2.10 с SПВ, а на компараторе 2.11 - с SПН. Выход ">" компаратора 2.10 управляет ключом 2.12, а выход "<" компаратора 2.11 - ключом 2.14. На информационный вход ключа 2.12 поступает разность значений SКНС - SПВ с вычитателя 2.7, а на информационный вход ключа 2.12 - разность SПН - SКНС, что определяет область состояний обстановки "П". Ключ 2.13 управляется одновременно по двум входам (логическая функция И): с выхода "<" компаратора 2.10 и с выхода ">" компаратора 2.11. На информационный вход этого ключа поступает разность SПВ - SКНС, что определяет область состояния обстановки "О". Шифраторы 2.5 и 2.6 вместе с дешифратором 2.1 формируют ширину зоны оценки для областей соответственно "П" и "О", выражаемых числом КНС - SКНСП и SКНСО. Эти значения являются делителем в устройствах деления соответственно 2.17 и 2.16, делимым для которых являются разности соответственно SКНС - SПВ или SПН - SКНС и SПВ - SКНС. После операции деления номер зоны, соответствующий более точной оценке состояния обстановки, по сравнению с оценкой, получаемой в формирователе сигналов текущей оценки, появляется на выходе дискриминатора.

Счетчик 4 временных интервалов (фиг. 1) осуществляет подсчет количества наблюдаемых интервалов времени и выдает комбинацию о номере временного интервала на регистр 14 стратегии поиска. Коммутатор 5, в соответствии с поступающим на него сигналом управления от формирователя 1, обеспечивает подключение сигнала о номере зоны состояния "П" или "О" соответственно на вход формирователя переменной поиска 6 или 7, где на основе сигнала о номере зоны Kj (1 < j < m), наибольшего номера зоны Km и максимального числа наблюдений Nmax производится построение приращений Fп(N) или Fо(N) эмпирических интегральных функций распределения вероятностей отклоненного и нормального состояния трафика на N-м интервале наблюдения:

В суммирующих счетчиках 8 и 9 производится сложение значений приращений Fп(N) и Fо(N) с соответствующими значениями эмпирической интегральной функции распределения, вычисленной за N-1 временной интервал Fп(N-1) и Fо(N-1), которые поступают с выходов блоков памяти 10 и 11:

Fп(N) = Fп(N-1) + Fп(N);

Fо(N) = Fо(N-1) + Fо(N).

Значения Fп(N) и Fо(N) поступают на входы блока деления 12 и на запись в первый 10 и второй 11 блоки памяти. Блок деления 12 осуществляет операцию арифметического деления

и выдачу отношения правдоподобия на вход классификатора 13.

При значении входного сигнала классификатора (фиг. 7) меньше нижнего порога (Пклн) компаратора 13.2 на его выходе "<" формируется высокий потенциал, открывающий ключ 13.4, что соответствует состоянию обстановки "О". При значении входного операнда классификатора больше верхнего порога (Пклв) компаратора 13.1 на его выходе ">" формируется высокий потенциал, открывающий ключ 13.3, что соответствует состоянию обстановки "П". Промежуточные значения операнда на входе классификатора не приводят к выработке решения до тех пор, пока стратегия поиска сохраняется двухпороговой. При усечении процедуры поиска (при достижении предельного значения номера интервала поиска) пороги "сливаются", что в любом случае приводит к выработке решения о состоянии обстановки.

Изменение стратегии поиска, осуществляемое регистром 14 (фиг. 8), производится следующим образом. Значения порогов "Пв" и "Пн" с входа регистра стратегии поиска поступают соответственно на входы регистров 14.1 и 14.2, которые затем при значении номера текущего интервала поиска, меньшем предельно допустимого (Nтекщ < Nmax), подаются на соответствующие выходы регистра стратегии поиска через открытые ключи 14.7 и 14.9, а также схемы ИЛИ 14.10 и 14.11 в качестве значений порогов классификации "Пклв" и "Пклн". Такое состояние соответствует интервальному значению порога поиска, что необходимо для реализации процедуры поиска по критерию Вальда. При Nтекщ ≥ Nmax на выходе "<" компаратора устанавливается низкий потенциал, закрывающий ключи 14.7 и 14.8, а на выходе "≥" - высокий, открывающий ключ 14.8. При этом полученное на выходе вычитателя 14.4 значение разности порогов делится устройством деления 14.5 на два и, после его вычитания от значения верхнего порога в вычитателе 14.6, становится равным среднему значению между верхним и нижним порогами. Это значение через открытый ключ 14.8 поступает одновременно на оба выхода регистра стратегии поиска через схемы ИЛИ 14.10 и 14.11, что эквивалентно формированию точечного значения порога поиска. Инициализация регистра стратегии поиска осуществляется установкой всех регистров в начальное состояние сигналом "Сброс", поступающим с его одноименного входа.

Адаптация значений порогов поиска ко времени суток осуществляется в блоке 17 (фиг. 9). Код текущего времени, поступающий на его вход с таймера 18, с входа "Время" блока поступает на дешифратор и затем на шифратор, которые формируют сигнал, отображающий закон изменения интенсивности входного трафика, необходимый для управления зависимостью значений порогов от времени суток. С поступлением сигнала "Пуск" значение порога записывается в регистр 17.3 и одновременно появляется на его выходе в качестве вторых операндов сумматора 17.4 и вычитателя 17.5. Сигнал с дешифратора, пропорциональный девиации порогов, суммируется со средним значением порога в сумматоре 17.4 и вычитается от него в вычитателе 17.5. В результате на выходах блока формируются верхнее и нижнее значения порогов, зависящие от времени суток. Среднее значение порога является статистической априорной величиной и задается записью в регистр соответствующего значения с входа блока "Порог".

Сигнал с выхода классификатора 13 подается на вход блока индикации 16 и формирователя сигналов сброса 15, с выхода которого сигнал "Сброс" подается на сброс счетчика 4, первый 10 и второй 11 блоки памяти, а также регистр 14 для перевода их в исходное состояние.

Все блоки, устройства и элементы, обрабатывающие информационный сигнал, а также линии, их соединяющие, должны иметь разрядность, соответствующую разрядности входных операндов и точности их преобразований.

Оценка повышения оперативности поиска информации в предлагаемом устройстве проведена следующим образом.

Отметим, что при Kтр → min целесообразно μ → μmax (при условии  для минимизации Ттр. Указанное характеризует физический смысл формул (2) и (9).

для минимизации Ттр. Указанное характеризует физический смысл формул (2) и (9).

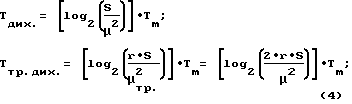

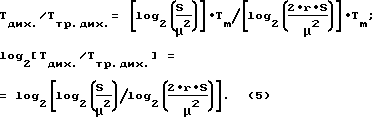

Дихотомический метод (используемый в прототипе).

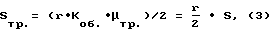

1. Ктр. = r • Коб., где r - коэффициент плотности (r ≥ 1).

Sтр.= Kтр.•μ;S = Kоб.•μ _→ Sтр.= r•Kоб.•μтр.

Так как для исключения пропуска или ложной тревоги должно выполняться условие: μтр.≤ μ/2 , то:

где Ттр.дих. _→ требуемое время поиска искомых блоков.

В общем случае соотношение Тдих. и Ттр.дих. оценивается:

Проведя упрощения и взяв антилогарифм в выражении (5), получаем (М.Я. Выгодский. Справочник по элементарной математике. М.: Наука, 1964):

Полагаем S = 106.

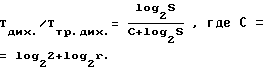

Оценим соотношение Тдих. и Ттр.дих. при Ктр. = (0,15 - 0,25).

Проведя упрощения и взяв антилогарифм в выражении (6), получим:

ΔTдих.max= Tдих./Tтр.дих.= 1,0528.

Т.е.: 1,0528 < ΔTдих.max< 1,0955

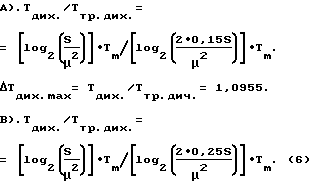

II. В нашем случае:

Последовательный метод, реализованный в предлагаемом устройстве, оценивается следующим образом.

III. Ктр. = (0,15 - 0,25) • Коб..

Проведем оценку соотношения Тпосл. и Ттр.посл. аналогично пункту (I).

Т.е.: 2,00 < ΔTпосл.max< 3,33

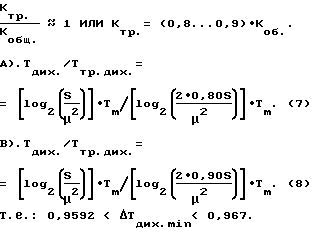

IV. Пусть Ктр. = (0,80 - 0,90) • Коб.

Проведем оценку соотношения Тпосл. и Ттр.посл. аналогично пункту (II).

Т.е.: 0,556 < ΔTпосл.min< 0,625

Сравним попарно полученные результаты.

Для Ктр. = (0,15 = 0,25) • Коб.

Иллюстрации приведены на фиг. 10.

Для Ктр. = (0,8 - 0,9) • Коб.

Иллюстрации приведены на фиг. 11,

где:

Graph D - гистограмма для дихотомического метода;

Graph P - гистограмма для последовательного метода.

Таким образом, полученные результаты позволяют сделать вывод о том, что при Kтр._→ Kоб. целесообразно использовать последовательный метод поиска информации как альтернативу дихотомическому, так как временной выигрыш первого метода по сравнению со вторым может составлять до 35 - 40%. Предлагаемое устройство, в котором для поиска информации в массиве и ее оценки используется совокупность новых блоков и последовательная процедура с ограничениями по критерию Вальда, обеспечивает достижение поставленной цели.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1999 |

|

RU2149446C1 |

| УСТРОЙСТВО МОНИТОРИНГА ИНФОРМАЦИОННОГО ТРАФИКА | 2005 |

|

RU2290691C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2004 |

|

RU2281549C1 |

| УСТРОЙСТВО МОНИТОРИНГА ИНФОРМАЦИОННОГО ТРАФИКА | 2020 |

|

RU2740534C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1998 |

|

RU2130644C1 |

| УСТРОЙСТВО МОНИТОРИНГА ИНФОРМАЦИОННОГО ТРАФИКА | 2021 |

|

RU2768543C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1998 |

|

RU2133500C1 |

| СПОСОБ ШИФРОВАНИЯ/ДЕШИФРОВАНИЯ СООБЩЕНИЙ ХЭШИРУЮЩЕЙ ФУНКЦИЕЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1998 |

|

RU2138126C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2115165C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1995 |

|

RU2094845C1 |

Изобретение относится к области вычислительной техники и может быть использовано в качестве устройства для поиска детерминированных комбинаций в информационном массиве. Техническим результатом является построение устройства поиска информации, обладающего более высокой оперативностью поиска при заданной вероятности правильного решения. Устройство содержит формирователь сигналов текущей оценки, дискриминатор зон значений оценки, распределитель импульсов, счетчик временных интервалов, коммутатор, первый и второй формирователи переменной поиска, первый и второй суммирующие счетчики, первый и второй блоки памяти, блок деления, классификатор, регистр стратегии поиска, формирователь сигналов сброса, блок индикации, блок изменения пороговых сигналов, таймер текущих суток. Устройство позволяет путем анализа входного потока обнаруживать в нем искомые детерминированные комбинации, вести с учетом времени суток подсчет их наличия или отсутствия, вычислять апостериорные интегральные функции Fп(N) и Fо(N) и вырабатывать отношение правдоподобия L(N) = Fп/Fо(N), значение которого затем сравнивается в классификаторе со значением порогов Пклв и Пклн, изменяющимися формирователем порога усечения в течение суток в зависимости от интенсивности входного потока, и принимается решение о состоянии обстановки по критерию Вальда. 4 з.п. ф-лы, 11 ил.

| Устройство для поиска информации | 1989 |

|

SU1711185A1 |

| Устройство для поиска информации | 1989 |

|

SU1621049A1 |

| SU 1832306 A1, 07.08.93 | |||

| СПОСОБ РЕГЕНЕРАЦИИ ВУЛКАНИЗОВАННЫХ ЭЛАСТОМЕРНЫХ ОТХОДОВ | 1991 |

|

RU2014339C1 |

| US 4611298 A, 09.09.86. | |||

Авторы

Даты

1998-07-27—Публикация

1997-04-07—Подача