Изобретение относится к области производства и эксплуатации интегральных схем и может быть использовано для их отбраковки по критериям: надежность и стойкость к электростатическим разрядам, а также для повышения достоверности других методов отбраковки, как в процессе производства, так и на входном контроле на предприятиях-производителях радиоэлектронной аппаратуры.

Известны методы отбраковки интегральных схем с использованием различных внешних воздействий (высокой температуры, электрических нагрузок и т.п.) [1, 2].

Недостатком данных методов является внесение в интегральные схемы неконтролируемых дефектов, сложность и энергоемкость аппаратуры испытаний.

Наиболее близким аналогом является схема испытаний с использованием радиации [3], сущность которой заключается в следующем. На интегральную схему воздействуют определенной дозой радиации, получат изменение информативного параметра, которое сравнивают с полем допуска, делая вывод о годности объекта испытаний. Затем производят отжиг дефектов при повышенной температуре. Недостатком данного способа является сложность и небезопасность аппаратуры испытаний.

Изобретение направлено на упрощение отбраковки интегральных схем без внесения неконтролируемых дефектов и с использованием простой и безопасной аппаратуры.

Это достигается тем, что в способе отбраковки интегральных схем, в том числе и на пластине, в соответствии с которым объект испытаний подвергают воздействию внешнего фактора, получают изменение информационного параметра, которое сравнивают с полем допуска, делая вывод о годности объекта испытаний, затем производят отжиг дефектов, для этого на интегральную схему подают единичный импульс электростатического разряда напряжения, составляющий половину опасного, отжиг дефектов производят при максимально-допустимой температуре p-n-перехода в течение 24 - 28 часов.

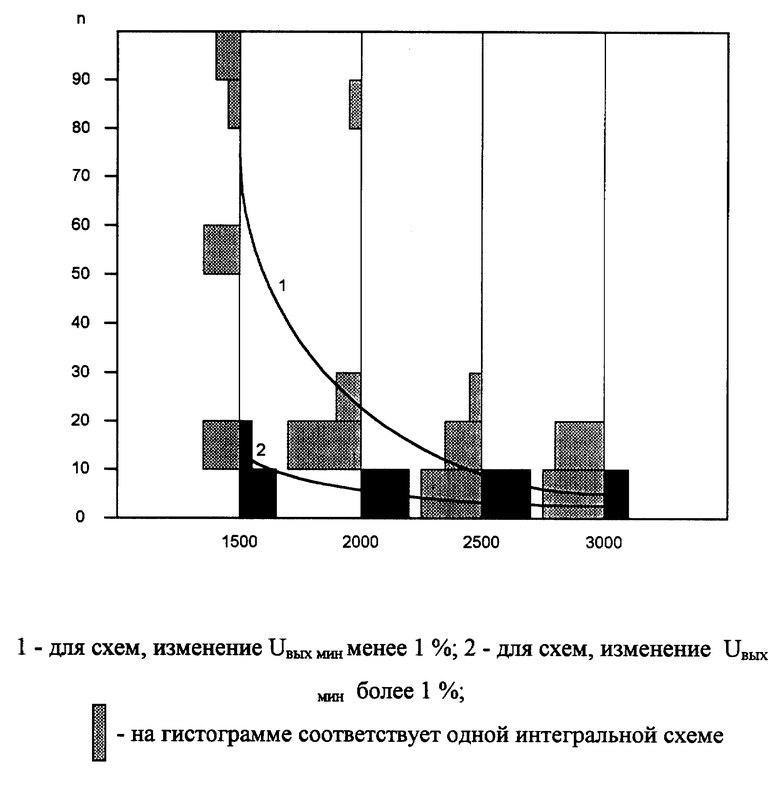

Сущность изобретения поясняется чертежом, на котором показан пример применения данного метода для отбраковки интегральных схем.

Сущность заявленного способа отбраковки заключается в следующем. Перед началом испытаний производится замер информационного параметра. Информационный параметр должен, по возможности, наиболее полно характеризовать функционирование интегральной схемы и значительно (но в пределах технических условий) изменяться под воздействием однократного электростатического разряда. Поле допуска должно быть таким, чтобы можно было эффективно разделять интегральные схемы на две партии с различной величиной стойкости к электростатическим разрядам и надежности. Если испытаниям подвергается большая или сверхбольшая интегральная схема, которая функционально сложна, то одного информативного параметра может оказаться недостаточно, при этом можно использовать комплекс параметров, каждый из которых со своим полем допуска. Отбраковка начинается с воздействия единичного импульса электростатического разряда. Напряжение электростатического разряда выбирается величиной, составляющей половину опасного, а последний - путем стандартных испытаний в режиме и на установке, указанной в [4]. Затем производится второй замер информативного параметра. После этого изменение значения информативного параметра каждой интегральной схемы сравнивается с полем допуска и производится разделение интегральных схем на две партии, т.е. отбираются схемы, имеющие более высокую стойкость к электростатическим разрядам и надежность. Затем производится отжиг дефектов при максимально-допустимой температуре перехода в течение 24 - 48 часов.

Максимально-допустимая температура перехода вычисляется по формуле:

Tmax = Pmax • RT;

где Pmax - максимальная мощность рассеяния; RT - тепловое сопротивление переход-корпус.

Эти параметры (Pmax, PT) указываются в технических условиях на каждую интегральную схему. В случае отсутствия по каким-либо причинам информации о них необходимо провести испытания для их нахождения по методике и на установке, описанной в [4].

Приведем пример применения предложенного способа для отбраковки интегральных схем типа КР142ЕН12 (аналоговые биполярные схемы с изоляцией элементов p-n-переходом). Для эксперимента взята партия из 50 схем. В качестве информативного использован параметр Uвыхмин, измерения которого производились с точностью 0,1%. Относительное изменение данного параметра по техническим условиям составляет 8%. Поле допуска было выбрано так, чтобы партия с пониженной чувствительностью к электростатическим разрядам и надежностью содержала около 20 - 30% схем, что достигается при относительном изменении информативного параметра до 1%. Затем после воздействия электростатического разряда напряжением 1000 В, составляющим половину опасного (при этом напряжении происходит изменение информативного параметра в пределах технических условий, в то же время катастрофических отказов не наблюдается), интегральные схемы разделялись на две партии и подвергались отжигу при повышенной температуре в течение 50 ч. Чтобы проверить эффективность разделения на партии, для каждой из них снималась зависимость напряжения электростатического разряда от числа их воздействий, приводящих к катастрофическим отказам интегральных схем, показанная на чертеже. Так как кривая, построенная для первой партии, лежит выше кривой, построенной для второй партии, следовательно, стойкость к электростатическим разрядам первой партии выше, чем второй.

Источники информации

1. Пат. ФРГ N 2833780, H 01 L 21/66, опубл. 1980.

2. Пат. США N 4816753, G 01 P 31/26, опубл. 1989.

3. Пат. России N 4900457/21, G 01 R 31/28, G 01 R 31/26, опубл. 1993.

4. ОСТ 11 073.013-83. Микросхемы интегральные. Методы испытаний.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ РАЗБРАКОВКИ БИПОЛЯРНЫХ ТРАНЗИСТОРОВ | 2001 |

|

RU2204143C2 |

| СПОСОБ РАЗДЕЛЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ | 2001 |

|

RU2230334C2 |

| СПОСОБ ВЫБОРОЧНОГО КОНТРОЛЯ НАДЕЖНОСТИ ТРАНЗИСТОРОВ В ПАРТИИ | 2001 |

|

RU2204142C2 |

| Способ сравнительной оценки стойкости партий интегральных схем к электростатическому разряду | 2022 |

|

RU2792841C1 |

| СПОСОБ ОТБРАКОВКИ ПОЛУПРОВОДНИКОВЫХ ИЗДЕЛИЙ ПОНИЖЕННОГО УРОВНЯ КАЧЕСТВА ИЗ ПАРТИЙ ИЗДЕЛИЙ ПОВЫШЕННОЙ НАДЕЖНОСТИ | 2011 |

|

RU2511633C2 |

| СПОСОБ РАЗБРАКОВКИ ИС | 1998 |

|

RU2143704C1 |

| СПОСОБ НЕРАЗРУШАЮЩЕГО ОПРЕДЕЛЕНИЯ СОДЕРЖАНИЯ ВЛАГИ В ПОДКОРПУСНОМ ОБЪЕМЕ ИНТЕГРАЛЬНЫХ СХЕМ | 2003 |

|

RU2263369C2 |

| СПОСОБ РАЗДЕЛЕНИЯ БИПОЛЯРНЫХ ТРАНЗИСТОРОВ ПО СТАБИЛЬНОСТИ ОБРАТНЫХ ТОКОВ | 2003 |

|

RU2242018C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ПОТЕНЦИАЛЬНО НЕНАДЕЖНЫХ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ | 2002 |

|

RU2230335C1 |

| СПОСОБ РАЗБРАКОВКИ ПОЛУПРОВОДНИКОВЫХ ИЗДЕЛИЙ ПО СТОЙКОСТИ К ЭЛЕКТРОСТАТИЧЕСКИМ РАЗРЯДАМ | 2008 |

|

RU2379698C1 |

Изобретение относится к области производства и эксплуатации интегральных схем (ИС). Способ отбраковки ИС, в том числе и на пластине, в соответствии с которым объект испытаний подвергают воздействию внешнего фактора, получают изменение информативного параметра, по величине которого делают вывод о годности объекта испытаний. На ИС подают единичный импульс электростатического разряда напряжением, составляющим половину опасного, затем производят отжиг дефектов при максимально допустимой температуре перехода в течение 24-48 ч. Техническим результатом является упрощение отбраковки ИС без внесения неконтролируемых дефектов и с использованием простой и безопасной температуры. 1 ил.

Способ отбраковки интегральных схем, в том числе и на пластине, в соответствии с которым объект испытаний подвергают воздействию внешнего фактора, получают изменение информативного параметра, которое сравнивают с полем допуска, делая вывод о годности объекта испытаний, затем производят отжиг дефектов, отличающийся тем, что на интегральную схему подают единичный импульс электростатического разряда напряжением, составляющим половину опасного, отжиг дефектов производят при максимально допустимой температуре p-n-перехода в течение 24 - 48 ч.

| RU 2005308 C1, 30.12.1993 | |||

| US 4816753 A, 23.03.1989 | |||

| US 4768195 A, 30.08.1988 | |||

| ЭКСПЕРТНАЯ СИСТЕМА НА БАЗЕ МЕДИЦИНСКОГО МАНИПУЛЯЦИОННОГО РОБОТА ДЛЯ ТРАНСПЕДИКУЛЯРНОЙ ФИКСАЦИИ ПОЗВОНОЧНИКА | 2023 |

|

RU2833780C1 |

Авторы

Даты

2000-03-20—Публикация

1998-03-19—Подача