Настоящее изобретение относится к устройствам для отбора аудио/видео компонент программ из потока сигналов, включающих множество программ, передаваемых с временным разделением, каждая из которых имеет множество компонент в форме пакетов.

Традиционные программы аналогового телевидения содержат компоненты сигнала с частотным уплотнением в относительно узких смежных полосах частот. Компоненты программы обнаруживаются полосовой фильтрацией требуемой полосы частот, с последующим разделением соответствующих компонент разными методами. В последнее время была значительно усовершенствована техника цифровой обработки сигналов, так что теперь возможно и целесообразно передавать телевизионные программы в цифровом виде. Цифровая обработка включает первое сжатие соответствующих компонент программы, например, процессором преобразования, группирование компонент в транспортные пакеты для обеспечения определенного уровня помехоустойчивости и передачу сжатых компонент как сигналов с амплитудно-импульсной модуляцией, с квадратурной фазовой модуляцией или с квадратурной амплитудной модуляцией.

Способы сжатия настолько эффективны, что возможно передавать несколько программ в полосе частот одного аналогового телевизионного сигнала, что может помочь расширить ограниченные ресурсы кабельного телевидения или прямого спутникового вещания. Система прямого спутникового вещания, разработанная фирмой "Thomson Consumer Electronics", которая должна быть введена в действие в 1994 году, мультиплексирует с временным разделением множество телевизионных программ в каждом ретрансляторе спутниковой системы. Каждая программа может включать множество компонент сигнала, таких как видеокомпонента, одна или две аудиокомпоненты, компонента данных для взаимодействия пользователя с программой или ее распространителем и другие возможные дополни тельные компоненты. Каждая компонента передается в пакетной форме, причем каждый пакет содержит полезные данные компоненты и идентификатор SCID компоненты сигнала. Идентификаторы компонент сигнала представляют собой просто двоичные числа. Для обеспечения максимальной гибкости системы идентификаторы, назначенные соответствующим компонентам одной программы, различны.

Поэтому для того, чтобы синтезировать передаваемую программу соответствующим приемным устройствам требуются средства отбора соответствующих пакетов компонент из принятого потока сигналов.

В настоящем изобретении представлено устройство для отбора заранее заданных пакетов компонент сигнала, содержащих передаваемую программу, из сигнального потока пакетов множества программ, мультиплексированных с временным разделением. Управляющее устройство, реагирующее на выбор пользователя и на переданный программный указатель, определяет из программного указателя коды идентификаторов пакета (SCID) для компонент сигнала соответствующей программы. Идентификаторы соответствующих компонент хранятся в программируемых регистрах. Идентификаторы соответствующих пакетов из потока сигналов последовательно загружаются в дополнительный регистр. С программируемыми регистрами связаны схемы сравнения, которые сравнивают хранимые идентификаторы с идентификаторами пакетов из потока сигналов. Выходные сигналы от соответствующих схем сравнения управляют использованием соответствующих пакетов компонент сигнала из потока сигналов.

Изобретение поясняется чертежами, где

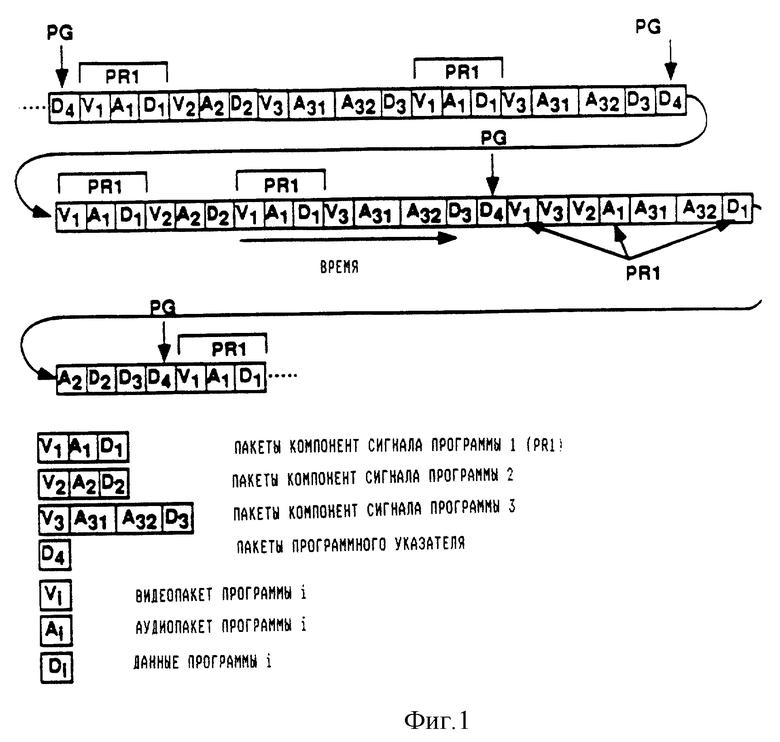

на фиг. 1 схематично представлен телевизионный сигнал в виде пакетов с временным разделением,

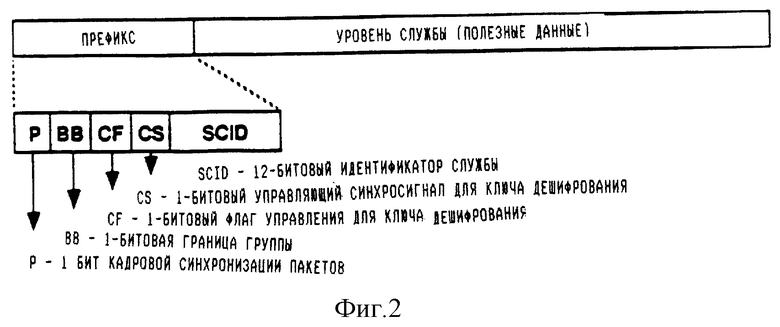

на фиг. 2 схематично представлены соответствующие пакеты сигнала,

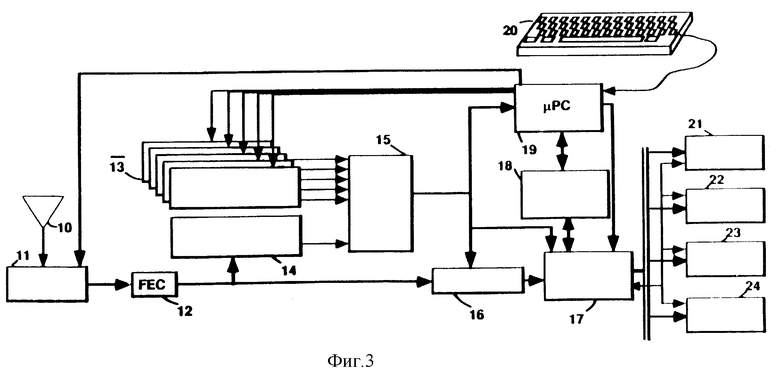

на фиг. 3 представлена блок-схема приемника, согласно изобретению, для отбора и обработки пакетов мультиплексированных сигналов компонент программы,

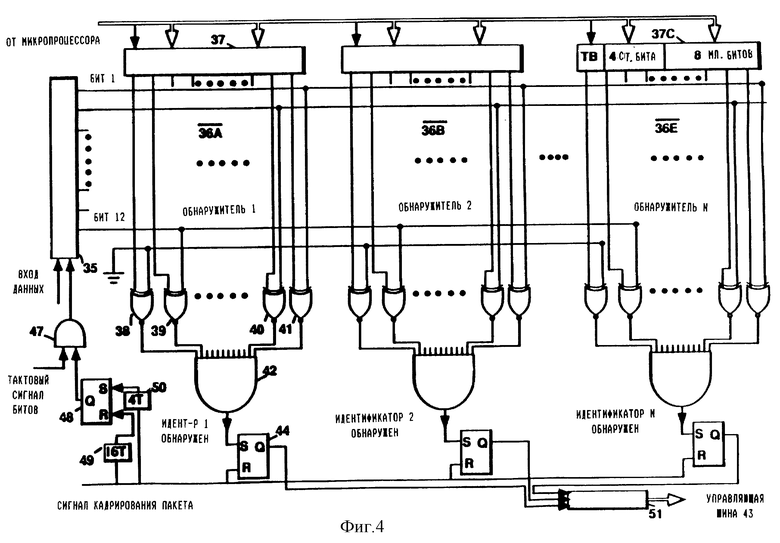

на фиг. 4 представлена схема набора обнаружителей идентификаторов компонент сигнала,

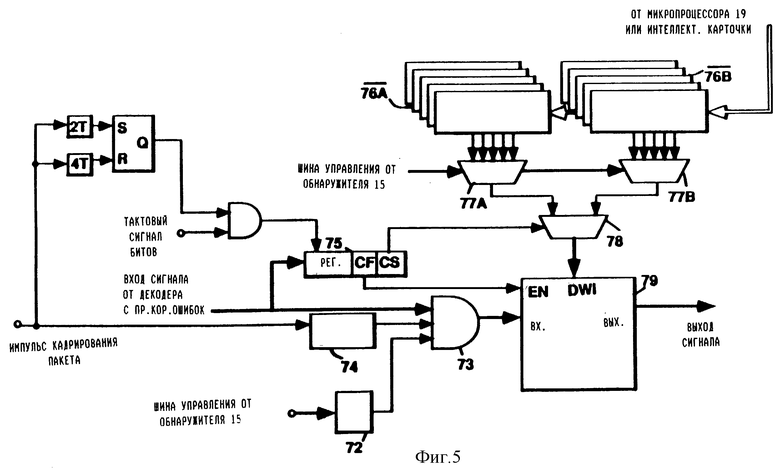

на фиг. 5 представлена блок-схема варианта устройства дешифрования для блока 16 на фиг. 3,

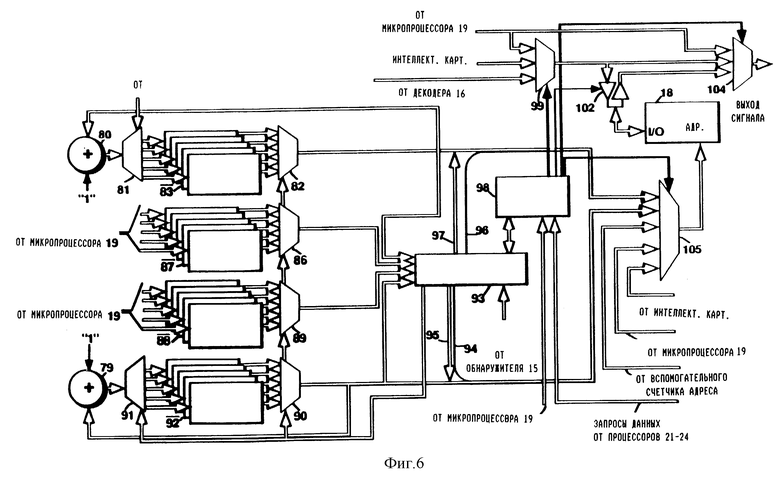

на фиг. 6 представлена блок-схема варианта устройства управления памятью, которое может быть использовано для блока 17 на фиг. 3,

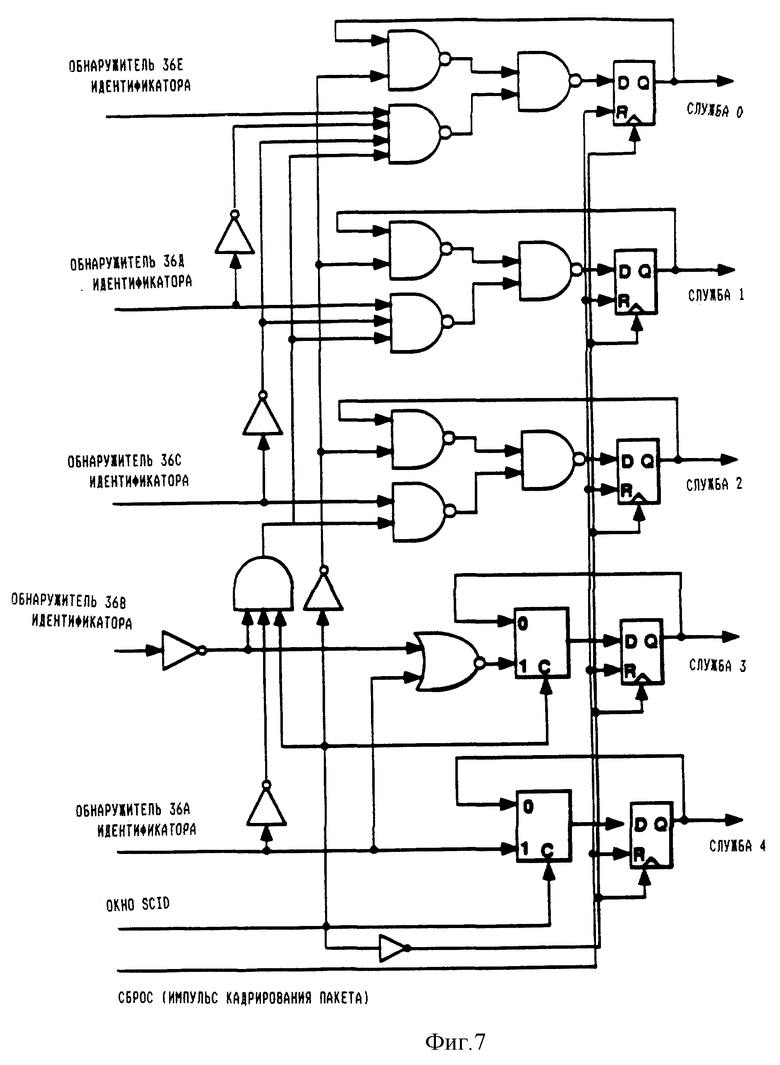

на фиг. 7 представлена схема устройства установления приоритета.

На фиг. 1 показан сигнальный поток, в виде последовательности квадратов, представляющих собой пакеты сигнала, являющиеся компонентами множества разных телевизионных или интерактивных телевизионных программ. Предполагается, что эти компоненты программ состоят из сжатых данных и, следовательно, количество видеоданных различно для различных изображений. Пакеты имеют фиксированную длину. Пакеты, обозначенные буквами с одинаковой первой цифрой индекса, соответствуют компонентам одной программы. Например, Vi, Ai и Di представляют соответственно видеопакеты, аудиопакеты и пакеты данных; пакеты, обозначенные V1, A1 и D1, представляют видеопакеты, аудиопакеты и пакеты данных программы 1, V3, A31, A32 и D3 представляют видеокомпоненту, аудиокомпоненту 1, аудиокомпоненту 2 и компоненту данных программы 3. В верхней строке пакетов соответствующие компоненты конкретной программы показаны сгруппированными вместе. Однако совершенно не обязательно, чтобы пакеты, соответствующие одной программе, были сгруппированы вместе, что иллюстрируется последовательностью пакетов в средней части строки пакетов. Не существует также какого-либо особого порядка расположения соответствующих компонент.

Строка пакетов, показанная на фиг. 1, представляет три программы, мультиплексированные с временным разделением - программу 1 (PR1) и программы 2 и 3, а также пакеты, представляющие программный указатель (пакеты D4). Программный указатель PG включает данные, которые взаимосвязывают компоненты программ. Соответствующим компонентам программ присвоены идентификаторы, по существу не зависящие от программ, все компоненты имеют различные идентификаторы компонент сигнала (SCID). Например, идентификаторы, назначенные видеопакетам, аудиопакетам и пакетам данных программы 2, могут быть числами 101111000110, 001101000111 и 101010101010 соответственно.

Пакеты включают префикс и полезные данные, как показано на фиг. 2. В данном примере префикс включает два 8-битовых байта, содержащие 5 полей, причем четыре из них (P, BB, CF, CS) являются 1-битовыми полями, а одно (SCID) - 12-битовым полем. Для целей настоящего описания представляют интерес только поля CF, CS и SCID. Поле SCID является идентификатором компоненты сигнала. Поле CF содержит флаг, показывающий, является ли полезная информация в пакете скремблированной, а поле CS содержит флаг, показывающий, какой из двух альтернативных ключей дескремблирования следует использовать для дескремблирования скремблированных пакетов. Префикс каждого пакета занимает заданное положение в начале пакета и, таким образом, позиции соответствующих полей легко идентифицировать.

Фиг. 3 иллюстрирует детектор пакетов во взаимосвязи с разными элементами приемника для цифрового телевидения. Сигнал принимается антенной 10 и подается на тюнер 11, который выделяет из принятого сигнала определенную полосу частот и формирует на выходе двоичный сигнал в полосе частот модуляции. Полоса частот, выделяемая тюнером, выбирается пользователем с помощью микропроцессора 19 известными способами. Обычно в вещательных цифровых сигналах используют кодирование с исправлением ошибок, например, кодирование Рида-Соломона с прямой коррекцией ошибок. Сигнал в полосе частот модуляции затем подается в декодер 12 с прямой коррекцией ошибок. Декодер 12 синхронизирует принятые видеосигналы и формирует поток пакетов сигнала, подобный изображенному на фиг. 1. Декодер 12 может выдавать пакеты через равные временные интервалы или по требованию, например, контроллера 17 памяти. В любом случае, схемой с прямой коррекцией ошибок формируется пакетный кодирующий или синхронизирующий сигнал, который отмечает моменты времени, когда соответствующая информация в пакетном виде передается от декодера 12.

В принятой полосе частот может содержаться множество программ в пакетной форме, мультиплексированных с временным разделением. Для дальнейшего использования на последующие элементы схемы следует пропустить только пакеты одной программы. Однако пользователь не располагает информацией о том, какие пакеты выбрать. Эта информация содержится в программном указателе, который сам является программой, состоящей только из данных, которые взаимосвязывают компоненты программ с помощью идентификаторов компонент сигнала. Программный указатель представляет собой список идентификаторов для видеокомпонент, аудиокомпонент и компонент данных всех программ. Программному указателю (пакет D4 на фиг. 1) назначен фиксированный идентификатор. При включении питания приемника микропроцессор 19 загружает идентификатор, соответствующий программному указателю, в один из регистров из набора одинаковых программируемых регистров 13 идентификаторов. Поля SCID из префиксов соответствующих пакетов сигнала из декодера 12 последовательно загружаются в дополнительный регистр 14 идентификаторов. Программируемые регистры и регистр принятых идентификаторов соединены с соответствующими входными портами схемы 15 сравнения и принятый идентификатор сравнивается с идентификатором программного указателя. Если идентификатор пакета совпадает с идентификатором программного указателя, схема 15 сравнения дает команду контроллеру 17 памяти направить этот пакет в заранее заданную область памяти 18 для использования его микропроцессором. Если же принятый идентификатор не соответствует идентификатору программного указателя, то соответствующий пакет просто отбрасывается. Элементы 13, 15 фактически образуют множество программируемых согласованных фильтров.

Микропроцессор ожидает команду от пользователя, поступающую через интерфейс 20, который показан в виде клавиатуры компьютера, но может быть обычным пультом дистанционного управления или органами управления на передней панели приемника. Например, пользователь может выбрать для просмотра программу канала 4 (в соответствии с терминологией, принятой для аналоговых телевизионных систем). Микропроцессор 19 программируется так, что просматривает список программного указателя, загруженный в память 18, в поисках идентификаторов компонент сигнала, соответствующих компонентам программы четвертого канала, и загружает их в программируемые регистры из набора программируемых регистров 13, которые связаны с трактами обработки сигналов соответствующих компонент.

Принятые пакеты аудиокомпонент, видеокомпонент и компонент данных желаемой программы должны в конечном счете быть поданы соответственно на процессор 23 аудиосигнала, процессор 22, видео сигнала или процессор 21 (24) сигнала вспомогательных данных. В варианте системы, представленном для примера на фиг. 3, соответствующие пакеты вначале направляются в заранее заданные ячейки памяти 18. Впоследствии соответствующие процессоры 21-24 запрашивают из памяти 18 соответствующие пакеты компонент. Следует понимать, что компоненты сигнала находятся в сжатом виде и что устройства декомпрессии не требуют поступления данных непрерывно. Маршрутизация компонент через память обеспечивает желаемое регулирование скорости выдачи данных.

Видеопакеты, аудиопакеты и пакеты данных загружаются в заранее заданные ячейки памяти для обеспечения устройствам обработки сигнала (процессорам) легкого доступа к данным компонент. Для того, чтобы нужные пакеты были загружены в соответствующие области памяти, соответствующие схемы сравнения идентификаторов должны быть связаны именно с этими областями памяти. Эта связь может быть осуществлена на физическом уровне в контроллере 17 памяти или может быть программируемой. В первом случае определенные программируемые регистры 13 всегда будут назначены определенным идентификаторам видеокомпонент, аудиокомпонент и компонент данных соответственно. Во втором случае идентификаторы видеокомпонент, аудиокомпонент и компонент данных могут быть загружены в любой из программируемых регистров 13, а требуемая связь будет установлена программированием контроллера 17 памяти в процессе загрузки в программируемые регистры соответствующих идентификаторов.

В установившемся режиме, после того как идентификаторы компонент соответствующей программы загружены в программируемые регистры 13, идентификаторы принятых пакетов сигнала сравниваются со всеми идентификаторами в программируемых регистрах идентификаторов. Если достигнуто совпадение с идентификатором или аудиосигнала, или видеосигнала, или сигнала данных, то соответствующие полезные данные пакета будут загружены в область памяти аудиосигнала, видеосигнала или сигнала данных соответственно.

Соответствующие пакеты сигналов из декодера 12 с прямой коррекцией ошибок через дешифратор 16 сигнала поступают на контроллер 17 памяти. Скремблированными являются только полезные данные сигнала. Флаг CF префикса пакета определяет, следует ли дескремблировать данный пакет, а флаг CS определяет, как данный пакет следует дескремблировать. В случае, если для соответствующего пакета не произошло совпадение ни одного из идентификаторов, дешифратор может просто остановить прохождение данных. Альтернативно, в такой же ситуации дешифратор может продолжать дешифрование в соответствии с последними установленными параметрами, а запись в память может быть блокирована, чтобы отбросить соответствующие пакеты.

Фиг. 4 иллюстрирует вариант регистровых-сравнивающих схем, которые могут быть использованы в качестве элементов 13-15 на фиг. 3. Фиг. 4 содержит множество одинаковых регистровых-сравнивающих схем 36A-36E. Каждая из них включает 13-битовый регистр 37 с параллельным выходом, в который из микропроцессора 19 загружается один из идентификаторов компонент. Параллельные выходы связаны с соответствующими первыми входами множества из 13 двухвходовых схем 38-41 ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ. В дополнительный регистр, который в настоящем примере является 12-битовым регистром 35 с последовательным входом и параллельным выходом, последовательно загружается 12-битовый идентификатор из текущего пакета компоненты сигнала. Выходы этого регистра соединены с вторыми входами соответствующих по битам двенадцати вентилей ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ всех схем 36A-36E. Второй вход тринадцатого вентиля ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ заземлен и его использование будет описано ниже. Каждая из схем 36A-36E содержит схему И с тринадцатью входами, которые соединены с выходами тринадцати вентилей ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ. Всякий раз, когда идентификатор, загруженный в регистр 35, совпадает с идентификатором, записанным в одном из регистров схем 36A-36E, на выходе вентиля И соответствующей схемы произойдет изменение уровня от низкого к высокому, указывающее на это совпадение.

Выходы соответствующих вентилей И соединены с входом S установки в "1" RS-триггера 44, который запускается фронтом сигнала. На вход R сброса RS-триггера подают импульс кадрирования (кадровой синхронизации) пакетов. В этом примере предполагается, что импульс кадрирования пакетов представляет собой импульс, уровень которого в начале пакета изменяется с низкого на высокий и остается высоким, пока длится пакет. Поэтому соответствующие RS-триггеры сбрасываются в состояние низкого уровня в начале каждого пакета и устанавливаются в состояние высокого уровня при изменении уровня сигнала на выходе соответствующего вентиля И с низкого на высокий, когда совпадение обнаружено. Предполагается, что пакеты имеют последовательно-битовый формат и выход соответствующих битов пакета от декодера 12 синхронизируется тактовым сигналом битов. Совпадение может произойти только после загрузки идентификатора в регистр 35, что происходит через 16 периодов тактового сигнала битов после переднего фронта импульса кадрирования пакетов.

Поступление идентификаторов пакетов в регистр 35 синхронизируется тактовым сигналом битов, который подается в регистр 35 через вентиль 47 И. Вентиль 47 И может пропускать тактовый сигнал битов только в течение того интервала времени, когда в потоке битов пакетов присутствует идентификатор SCID. Импульс разрешения генерируется RS-триггером 48, запускаемым фронтом сигнала. Установка этого триггера в "1" осуществляется копией сигнала кадрирования пакетов, задержанного на четыре периода тактового сигнала битов, а сброс осуществляется дополнительной копией сигнала кадрирования пакетов, задержанного на шестнадцать периодов тактового сигнала битов. RS-триггер 48 формирует на выходе сигнал разрешения, который имеет длительность, равную 12 периодам тактового сигнала битов, и который задержан на четыре периода тактового сигнала битов относительно начала соответствующего пакета.

Подобная схема может быть приспособлена и для загрузки сигналов, имеющих последовательно-байтовый формат, в текущий регистр идентификаторов, если данные на выходе декодера с прямой коррекцией ошибок являются последовательностью байтов. Для специалистов в области цифровых схем нетрудно приспособить схему сравнения к формату входного сигнала.

На фиг. 5 показан пример устройства дешифрования, которое может быть использовано в качестве дешифратора 16 на фиг. 3. Пакеты сигнала дешифруются обычным дешифратором 79, которым управляют так, что он осуществляет дескремблирование согласно словам дескремблирования, подаваемым на вход слов дескремблирования (DWI). Пакеты подаются на дешифратор 79 через вентиль 73 И, который открывается через 16 периодов тактового сигнала битов после начала импульса кадрирования пакетов. Таким образом отрезается префикс пакета, который далее не используется.

Вентиль 73 И открывается также схемой 72 ИЛИ, которая реагирует на сигнал от обнаружителя 15 идентификаторов. Если произошло совпадение с каким-либо запрограммированным идентификатором, то схема 72 ИЛИ формирует сигнал разрешения, который разрешает полезным данным пакета поступить на вход дешифратора. Если совпадения идентификатора не произошло, вентиль 73 И фактически отбрасывает текущий пакет данных.

Флаги дешифрования CF и CS подаются в регистр 75 и хранятся там. Флаг CF подается на вход EN разрешения дешифратора. Реагирующий на значение флага, равное логической единице, дешифратор пропускает сигналы от декодера с прямой коррекцией ошибок без изменения, то есть дескремблирования не производится. Если же флаг CF равен логическому нулю, то дешифратор производит дескремблирование.

Каждая компонента программы может иметь два уникальных кода дескремблирования. Эти коды дескремблирования хранятся в двух наборах регистров 76A и 76B дешифрования. Соответствующие выходы регистров 76A соединены с мультиплексором 77A, а соответствующие выходы регистров 76B соединены с мультиплексором 77B. Соответствующие выходы мультиплексоров 77A и 77B соединены с мультиплексором 78, осуществляющим преобразование 2-в-1. Мультиплексор 78 имеет управляющий электрод, подключенный так, что мультиплексор реагирует на флаг управления CS в регистре 75. В зависимости от высокого или низкого уровня флага CS ключ дешифрования выбирается из регистра в наборе 76A или 76B соответственно. Мультиплексоры 77A и 77B управляются сигналом с выхода обнаружителя идентификаторов для выбора регистра ключа дешифрования в наборах 76A и 76B в зависимости от текущего пакета на выходе детектора 12.

Регистры 76A и 76B могут быть загружены фиксированными значениями ключей дешифрования. Однако для обеспечения гибкости скремблирования в предпочтительном варианте выполнения изобретения в регистры 76A и 76B ключи дешифрования могут быть записаны программно микропроцессором 19 или интерфейсом интеллектуальной карточки (не показан).

На фиг. 6 представлен примерный вариант устройства для контроллера 17 памяти, показанного на фиг. 3. Этот чертеж приведен, чтобы показать элементы, которые участвуют в программировании регистров 13 на фиг. 3. Компоненты программ хранятся в разных смежных блоках памяти 18. Кроме того, в памяти 18 могут храниться и другие данные, например, формируемые микропроцессором 19 или интеллектуальной карточкой (не показана).

Адреса в память 18 подаются мультиплексором 105, а данные в память 18 поступают от мультиплексора 99. Выходные данные формируются дополнительным мультиплексором 104. Выходные данные мультиплексора 104 формируются из данных, поступающих от микропроцессора 19, памяти 18 или непосредственно от мультиплексора 99. Предполагается, что данные программы соответствуют стандартному качеству и разрешению изображения и поступают с определенной скоростью. С другой стороны, в приемник могут поступать сигналы телевидения высокой четкости, идущие со значительно большей скоростью. Практически все данные от декодера с прямой коррекцией ошибок проходят в память 18 через мультиплексор 99, за исключением высокоскоростных сигналов телевидения высокой четкости, которые могут направляться непосредственно на мультиплексор 104.

Адреса памяти поступают на мультиплексор 105 от схем 79-97 адресации программ, микропроцессора 19, блока интеллектуальной карточки и, возможно, от других вспомогательных устройств. Выбор конкретного адреса в любой конкретный момент времени осуществляется схемой 98 прямого доступа к памяти. Управляющие сигналы идентификаторов и сигналы "потребности в данных" от соответствующих процессоров сигнала поступают на схему 98, в результате чего разрешаются конфликты при доступе к памяти. Схема 98 прямого доступа к памяти взаимодействует с контроллером 93 указателей служб, чтобы обеспечить для сигнальных компонент программы соответствующие адреса считывания и записи.

Адреса для блоков памяти, соответствующих различным компонентам сигнала, формируются четырьмя группами регистров 83, 87, 88 и 92 указателей служб или компонент программы. Указатели на начало (начальные указатели) соответствующих блоков памяти, в которых хранятся соответствующие компоненты сигнала, содержатся в регистрах 87. Эти начальные указатели могут быть фиксированными или могут быть вычислены известными способами управления памятью в микропроцессоре 19.

Указатели последнего адреса для соответствующих блоков хранятся в наборе 88 регистров служб, по одному для каждой возможной компоненты программы. Подобно начальным адресам, адреса концов блоков (конечные адреса) могут иметь фиксированные значения или же могут быть вычислены микропроцессором 19. Использование вычисляемых значений для указателей начала и конца блоков является предпочтительным, поскольку позволяет создать более гибкую систему при меньшем объеме памяти.

Указатели записи в память, или головные указатели, формируются сумматором 80 и головными регистрами 83 служб. Для каждой возможной компоненты программы имеется свой головной регистр службы. Указатель записи в память или головной указатель хранится в регистре 83 и поступает на мультиплексор 105 адреса в течение цикла записи в память. Головной указатель подается также в сумматор 80, в котором он увеличивается на единицу, и увеличенный указатель хранится в соответствующем регистре 83 для следующего цикла записи. Регистры 83 выбираются контроллером 93 указателей служб для соответствующей компоненты программы, обслуживаемой в данный момент времени.

В этом примере предполагается, что указатели начала и конца блоков содержат 16 битов. Регистры 83 формируют 16-битовые указатели записи или головные указатели. С другой стороны память 18 имеет 18-битовые адреса, 18-битовые адреса формируются за счет присоединения к 16-битовым головным указателям двух старших битов указателя начала блока, причем эти два бита указателя начала блока помещаются в старшие разряды 18-битового адреса записи. Из соответствующих регистров 87 указатели начала блока поступают на контроллер 93 указателей служб. Контроллер указателей служб отделяет два старших бита указателей начала блока, хранящихся в регистрах 87, и объединяет эти биты с 16-битовой шиной головных указателей. Это иллюстрируется шиной 96, которая изображена соединяющейся с шиной головных указателей, выходящей из мультиплексора 85.

Аналогично, указатели считывания из памяти, или хвостовые указатели, формируются сумматором 79 и хвостовыми регистрами 92 служб. Для каждой возможной компоненты программы имеется хвостовой регистр службы. Указатель считывания, или хвостовой указатель, хранится в регистре 92 и поступает на мультиплексор 105 адреса в течение цикла считывания из памяти. Хвостовой указатель подается также в сумматор 79, в котором он увеличивается на единицу, и увеличенный указатель хранится в соответствующем регистре 92 для следующего цикла чтения. Регистры 92 выбираются контроллером 93 указателей служб для соответствующей компоненты программы, обслуживаемой в данный момент времени.

Регистры 92 формируют 16-битовые хвостовые указатели. 18-битовые адреса чтения формируются за счет присоединения к 16-битовым хвостовым указателям двух старших битов указателя начала блока, причем эти два бита указателя начала блока помещаются в старшие разряды объединенного 18-разрядного адреса. Контроллер указателей служб отделяет два старших бита указателей начала блока, хранящихся в регистрах 87, и объединяет эти биты с 16-битовой шиной хвостовых указателей. Это иллюстрируется шиной 94, которая изображена соединяющейся с шиной хвостовых указателей, выходящей из мультиплексора 90.

Данные хранятся в памяти 18 по вычисленному адресу. После записи байта данных головной указатель увеличивается на единицу и сравнивается с указателем конца блока для данной компоненты программы. Если они совпадают, то старшие биты головного указателя замещаются младшими 14 битами указателя начала блока, а в два младших разряда той части адреса, которая соответствуют головному указателю, записываются нули. Эта операция показана стрелкой 97, выходящей из контроллера 93 указателей служб и направленной к шине головных указателей, идущей от мультиплексора 82. Предполагается, что младшие 14 битов указателя начала блока пишутся поверх битов головного указателя. Замена в адресе старших битов головного указателя младшими битами указателя начала блока позволяет осуществить "прокрутку" блока памяти, задаваемого двумя старшими битами указателя начала блока, и таким образом избежать повторного программирования адресов записи в начале каждого пакета на какую-либо особую ячейку памяти в пределах блока.

В случае, если теперь головной указатель окажется равным хвостовому указателю (который указывает, где читать данные в памяти 18), в блок прерываний микропроцессора подается сигнал, сообщающий, что головной указатель и хвостовой указатель встретились. При этом дальнейшая запись в память 18 из этого программного канала блокируется, пока микропроцессор не разблокирует канал. Это очень редкая ситуация, и она не должна иметь место при нормальной работе.

Данные из памяти 18 извлекаются по требованию соответствующего процессора в соответствии с адресами, вычисленными с помощью сумматора 79 и регистров 92. После чтения байта хранимых данных хвостовой указатель увеличивается на единицу и сравнивается в контроллере 93 указателей служб с указателем конца блока данного логического канала. Если хвостовой указатель равен указателю конца блока, старшие биты хвостового указателя заменяются на младшие 14 битов указателя начала блока, а в два младших разряда записываются нули. Это иллюстрируется стрелкой 95, выходящей из контроллера 93 указателей служб и направленной к шине хвостовых указателей, идущей от мультиплексора 90. Если теперь хвостовой указатель окажется равным головному указателю, то соответствующий блок памяти считается пустым и выдача данных соответствующему процессору будет прекращена до тех пор, пока от декодера с прямой коррекцией ошибок не поступят дополнительные данные для данного программного канала.

Управление чтением/записью осуществляется контроллером 93 указателей служб и схемой 94 прямого доступа к памяти. Схема прямого доступа к памяти запрограммирована так, чтобы распределять циклы чтения и записи. Это распределение зависит от того, выдает ли декодер 12 данные для записи в память или нет. Операции записи данных декодера имеют приоритет. В примере устройства на фиг. 4 имеются четыре типа устройств, которые могут иметь доступ к памяти. Это интеллектуальная карточка (не показана), декодер 12 с прямой коррекцией ошибок (точнее, дешифратор 16), микропроцессор 19 и одно из устройств прикладного назначения, таких как процессоры для обработки аудиосигналов и видеосигналов. Конкуренция за доступ к памяти осуществляется следующим образом. Схема прямого доступа к памяти, реагирующая на запросы данных, поступающие от различных устройств обработки сигналов, перечисленных выше, распределяет доступ к памяти следующим образом. Доступ к памяти осуществляется в интервалы времени, равные 95 нс, в течение которых байт данных считывается из памяти 18 или записывается в нее. Существует два основных режима распределения доступа к памяти, которые характеризуются тем, что "декодер с прямой коррекцией ошибок выдает данные" и "декодер с прямой коррекцией ошибок не выдает данные" соответственно. Для каждого из этих режимов, в предположении, что максимальная скорость данных от декодера с прямой коррекцией ошибок составляет 5 Мбайт/с или 1 байт в каждые 200 нс, распределение временных интервалов осуществляется следующим образом:

"Декодер с прямой коррекцией ошибок выдает данные"

1) Запись данных декодера с прямой коррекцией ошибок;

2) Чтение устройством прикладного назначения/чтение микро процессором/запись микропроцессором;

3) Запись данных декодера с прямой коррекцией ошибок;

4) Чтение/запись микропроцессором.

"Декодер с прямой коррекцией ошибок не выдает данные"

1) Чтение/запись интеллектуальной карточкой;

2) Чтение устройством прикладного назначения/чтение микро процессором/запись микропроцессором;

3) Чтение/запись интеллектуальной карточкой;

4) Чтение/запись микропроцессором.

Поскольку запись данных декодера с прямой коррекцией ошибок не может быть отложена, доступ к памяти декодеру (точнее, дешифратору), когда он выдает данные, должен быть гарантирован в течение каждых 200 нс. Оставшиеся временные промежутки распределяются между устройствами прикладного назначения и микропроцессором. Если данных для запрашивающих устройств нет, то микропроцессор использует временные интервалы, выделенные устройствам прикладного назначения.

Контроллер 93 взаимодействует с обнаружителем идентификаторов, чтобы определить, какой из соответствующих регистров - регистр указателя начала блока, регистр головного указателя или регистр указателя конца блока - получит доступ к операциям записи в память. Контроллер 93 взаимодействует со схемой прямого доступа к памяти, чтобы определить, какой из соответствующих регистров - регистр указателя начала блока, регистр указателя конца блока или регистр хвостового указателя - получит доступ к операциям считывания из памяти. Схема 98 прямого доступа к памяти управляет выбором соответствующих адресов и данных посредством мультиплексоров 99, 104 и 105.

Пусть желательно перепрограммировать один из регистров 13 идентификаторов без изменения остальных регистров идентификаторов. Это может потребоваться, например, когда желательно заменить одну из нескольких аудиокомпонент на другую, не мешая обработке других компонент сигнала. Эти действия требуют изменения указателей в соответствующих регистрах 83, 87, 88 и 92, а также выделения пространства в памяти и т.д., что требует определенного времени. Так как перепрограммирование не может быть выполнено мгновенно, то, если оно не проводится в предписанной последовательности, имеется большая вероятность, что нежелательные данные, выдаваемые декодером с прямой коррекцией ошибок, могут вторгнуться в один из процессоров и вызвать "аварию" системы.

Предпочтительно, чтобы перепрограммирование производилось в следующей последовательности. Когда нужно отменить выбор программной компоненты путем удаления ее идентификатора из одного из регистров 13, микропроцессор программируется так, чтобы проверить выходную шину управления обнаружителя идентификаторов для определения, активен ли сейчас данный канал, т.е., обрабатывает ли он пакет данной компоненты программы. Если он активен, система ожидает, пока эта служба на выходе обнаружителя идентификаторов не перестанет быть активной. После того, как эта программная компонента перестанет быть активной, в соответствующий регистр загружаются четыре старших бита нового идентификатора. Вдобавок бит переключения TB, равный логической единице, загружается в разряд TB регистра (см. фиг. 4). Бит переключения подается на 13-ый вентиль ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и имеет иной логический уровень, нежели уровень на другом входе 13-ого вентиля ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ. Это гарантирует то, что блокируется вентиль 42 И и, следовательно, будет неактивной эта определенная программная служба или канал. (Отметим, что в этом примере не все 12 битов загружаются в регистр 37 одновременно, поскольку шина загрузки данных является только 8-разрядной). Кроме того, схемы управления памятью к этому моменту еще не реконфигурированы, чтобы приспособиться к изменению идентификатора. Поэтому перед загрузкой младших битов идентификатора в регистр 37, схемы управления памятью реконфигурируют с помощью микропроцессора 19, а затем в регистр 37 загружаются восемь младших битов идентификатора, после чего бит переключения устанавливается равным логическому нулю, чтобы вновь сделать активным этот программный канал или службу.

Авторы изобретения установили, что весьма разумно дать приоритет сигналам управления идентификаторов. Возможно, а иногда и желательно, чтобы один и тот же идентификатор загружался в более чем один регистр идентификаторов. Тогда необходимо обеспечить, чтобы система могла быть приспособлена к одновременному обнаружению идентификаторов двумя или более обнаружителями. Приоритет соответствующих идентификаторов задают согласно иерархии, установленной разработчиком системы. В настоящем примере приоритет соответствующих обнаружителей 36A-36E установлен в cледующем порядке A, B, C, D, E. Таким образом, если идентификатор обнаруживается обнаружителем 36A и остальными обнаружителями 36B-36E, то выходной сигнал управления будет подан от обнаружителя 36A, а выходные сигналы управления от всех остальных обнаружителей 36B-36E будут заблокированы. Если же обнаружитель 36A не обнаружил текущий идентификатор, а обнаружитель 36B и другие обнаружители 36C-36E обнаружили текущий идентификатор, то сигнал управления будет подан от обнаружителя 36B, а выходы обнаружителей 36C-36E будут заблокированы. Аналогично, если обнаружитель 36C имеет наивысший приоритет из обнаруживших идентификатор обнаружителей в вышеуказанной иерархии, то будут заблокированы выходные сигналы обнаружителей 36D-36E и т.д.

Установление приоритетов выходных сигналов управления обеспечивается элементом 51 схемы на фиг. 4. Вариант схемы, осуществляющей эту функцию, показан на фиг. 7. Это известный декодер термометра и нет необходимости описывать его подробно.

Устройство для отбора заранее заданных пакетов компонент сигнала из потока (12) пакетов сигнала включает устройство (19) управление, реагирующее на выбор (20) пользователя и на переданный программный указатель, для определения кодов идентификаторов пакетов (SCID), для компонент сигнала соответствующей программы. Идентификаторы соответствующих компонент хранятся в программируемых регистрах (13). Идентификаторы из соответствующих пакетов потока сигналов последовательно загружаются в дополнительный регистр (14). Схемы сравнения (15), связанные с программируемыми регистрами, сравнивают хранимые идентификаторы с идентификаторами пакетов из потока сигналов. Выходные сигналы от соответствующих схем сравнения управляют использованием (21-24) соответствующих пакетов компонент сигнала из потока сигналов. Программирование (19) идентификаторов в соответствующих программируемых регистрах осуществляется в определенной последовательности для предотвращения случайного принятия системой нежелательных данных. Техническим результатом изобретения является создание устройства для отбора заранее заданных компонент смысла, содержащих передаваемую программу. 10 з.п.ф-лы, 7 ил.

| Устройство выборки кадра при видеовоспроизведении | 1987 |

|

SU1425874A1 |

| МАГНИТОГИДРОДИНАМИЧЕСКИЙ СЕПАРАТОР ДЛЯ ОБОГАЩЕНИЯ ПОЛЕЗНЫХ ИСКОПАЕМЫХ | 0 |

|

SU184190A1 |

| СПОСОБ ПОЛУЧЕНИЯ ДИСТЕРОИДО | 0 |

|

SU239326A1 |

Авторы

Даты

2000-08-10—Публикация

1995-04-21—Подача