Настоящее изобретение относится к устройствам для обработки пакетов данных компонент программ из пакетного видеосигнала и для выделения соответствующих полезных данных различных сигнальных компонент программ. Оно включает устройство адресации для транспортной буферной памяти и реализует принцип использования общей транспортной буферной памяти.

Известно, например, из патента США N 5168356 или патента США N 5289276, что является предпочтительным передавать сжатый видеосигнал пакетами, при этом имеется возможность в соответствующих пакетах использовать меры защиты от ошибок/коррекции ошибок. Устройства, описанные в вышеупомянутых патентах, передают и обрабатывают одну телевизионную программу, хотя и состоящую из множества программных компонент, поступающую через соответствующие каналы передачи. Эти устройства используют обратный транспортный процессор для выделения видеосигнальной компоненты соответствующих программ для последующей обработки с получением пригодной для воспроизведения видеокомпоненты. В патенте N 5289276 рассмотрена обработка только видеосигнальной компоненты. В патенте N 5168356 описывается обратный транспортный процессор, который отделяет другие компоненты программ с помощью простого демультиплексора, который для распознавания соответствующих компонент сигнала реагирует на данные заголовка пакета. Выделенная видеокомпонента подается в буферную память, в то время как остальные компоненты сигнала подаются непосредственно на соответствующие схемы обработки.

Из патента США N 5233654 известно, что для осуществления интерактивного программирования вместе с телевизионными сигналами может передаваться машинная программа. Обычно такая машинная программа воздействует на компьютер, связанный с телевизионным приемником, или выполняется им.

В системах, где большая часть компонент программ сжата, необходимо создание буфера между каналом передачи и большинством устройств обработки (декомпрессии) соответствующих компонент. Таким образом, желательно большинство компонент, если не все, поместить в буферную память. Скорости передачи данных могут значительно различаться как для разных компонент программ, гак и для одной компоненты. Таким образом, предпочтительно организовать раздельное буферирование каждой компоненты. Буферная память, необходимая для буферирования сжатых данных компонент программ и для выполнения интерактивных программ, довольно значительна. Фактически она может значительно увеличить стоимость приемника.

Если обратный транспортный процессор размещен, например, в приставке, то объем памяти и схемы управления памятью должны быть сведены к минимуму, чтобы насколько возможно снизить цену для потребителя. Таким образом, с экономической точки зрения желательно для буферирования компонент программ, для управляющей работы процессора и для интерактивных программ использовать одну и ту же память и одни и те же схемы управления памятью.

Настоящее изобретение представляет собой обратный транспортный процессор для приемника пакетов сигнала при мультиплексной передаче с временным уплотнением. Это устройство включает средства для селективного выделения желаемых полезных данных из данных компоненты программы и подачу этих данных на входной порт данных общей буферной памяти. Микропроцессор формирует данные, которые также поступают на входной порт данных общей буферной памяти. Полезные данные соответствующих компонент и данные, сформированные микропроцессором, размещаются в соответствующих блоках общей буферной памяти в соответствии с адресами, которые подаются на входной порт адресов памяти мультиплексором адреса.

В конкретном варианте выполнения изобретения полезные данные пакета соответствующей компоненты программы мультиплексируются во входной порт данных памяти и направляются в выбранные области запоминающего устройства с произвольной выборкой в соответствии с множеством начальных и конечных указателей (указателей начала и конца блоков). Указатели начала и конца блоков хранятся в первой группе регистров, по одному на каждую программную компоненту. Адреса формируются частично посредством множества регистров указателей чтения, мультиплексированных с сумматорами для того, чтобы последовательно осуществлять приращение указателя для соответствующей компоненты программы. Указатели начала блока связаны с указателями чтения для адресов памяти так, чтобы осуществлять "прокрутку" в пределах блоков памяти, назначенных соответствующим компонентам программы.

В другом варианте выполнения в устройство входит дешифратор для осуществления дешифрования полезных данных сигнала в соответствии с ключами дешифрования, зависящими от содержания пакетов.

В еще одном варианте выполнения в устройство входит детектор для обнаружения полезных данных, содержащих данные, касающиеся прав пользования. Полезные данные, содержащие данные прав пользования, через общую буферную память направляются в интеллектуальную карточку, которая формирует соответствующие пакету ключи дешифрования.

Выход памяти подключен к шине, соединяющей между собой устройства обработки соответствующих компонент программы (процессоры). В соответствии с запросами данных от устройств обработки соответствующих компонент программы и с запросами записи данных от источника полезных данных компонент осуществляется арбитраж доступа к памяти для чтения и записи так, что не происходит потерь поступающих данных программы и обслуживаются все устройства обработки компонент.

Изобретение поясняется чертежами, где

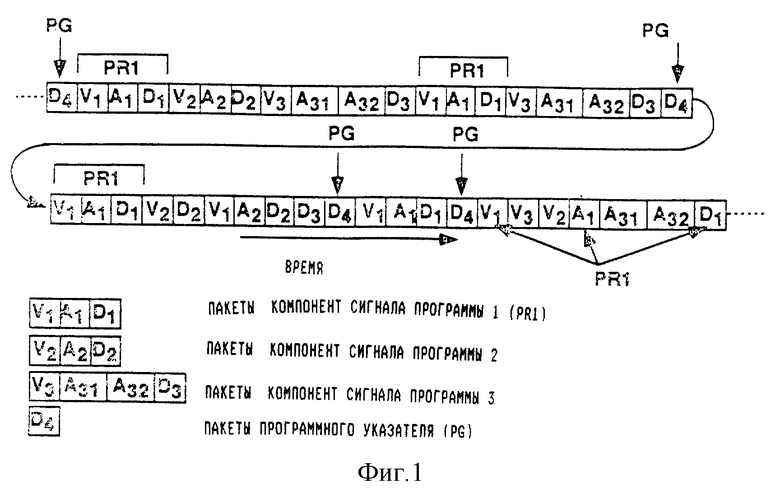

на фиг.1 схематично представлен телевизионный сигнал в виде пакетов при мультиплексной передаче с временным разделением,

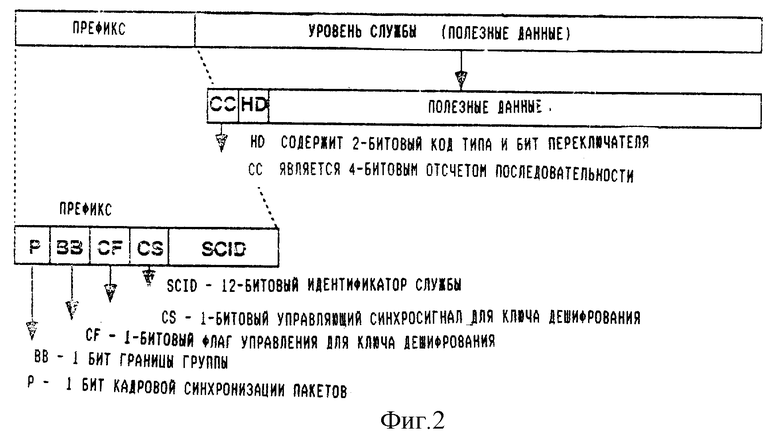

на фиг. 2 схематично представлены соответствующие пакеты сигналов,

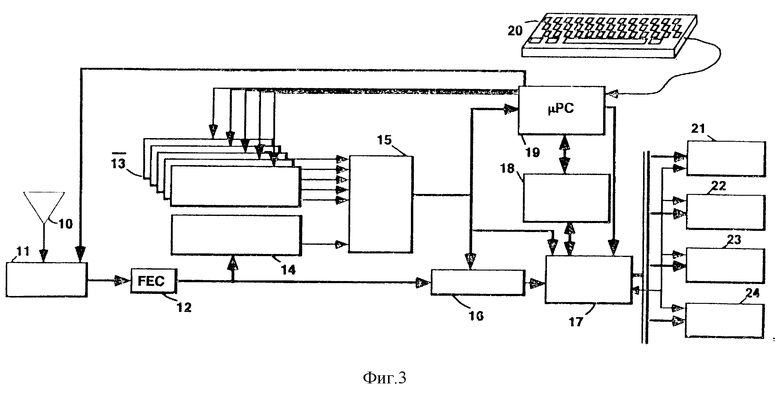

на фиг. 3 представлена блок-схема приемника для отбора и обработки пакетов мультиплексированных сигналов компонент согласно изобретению,

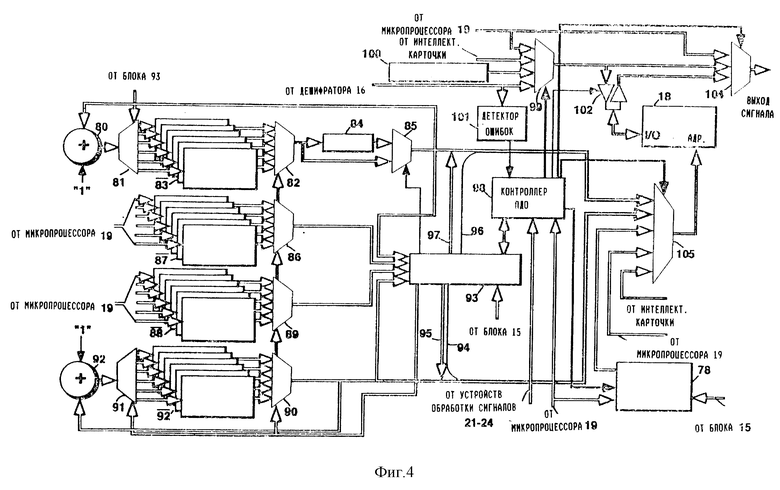

на фиг. 4 представлена блок-схема варианта схемы управления памятью, которая может быть использована в качестве элемента 17, показанного на фиг. 3,

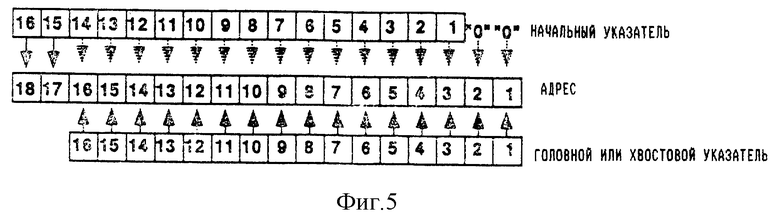

на фиг. 5 схематично показано, как формируется адрес памяти для данных каналов служб,

на фиг. 6 схематично представлено, как формируется адрес памяти для данных вспомогательных пакетов,

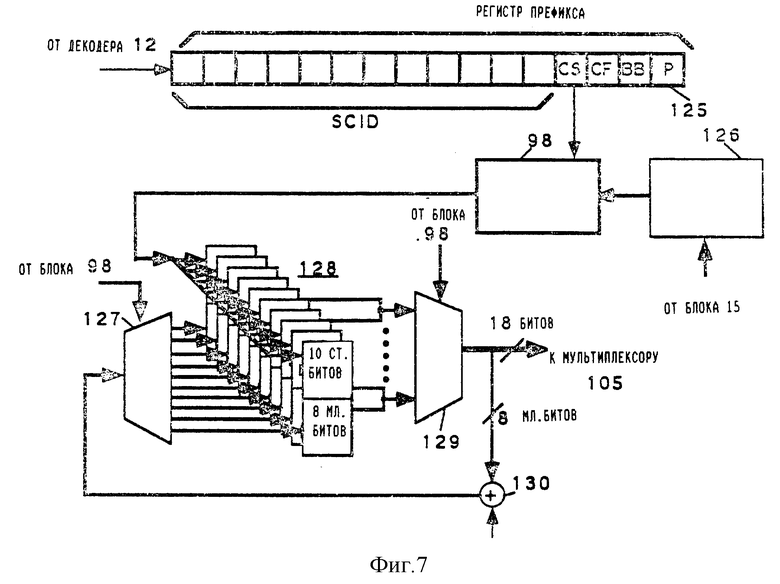

на фиг. 7 представлена блок-схема варианта схем формирования адресов памяти для вспомогательных пакетов,

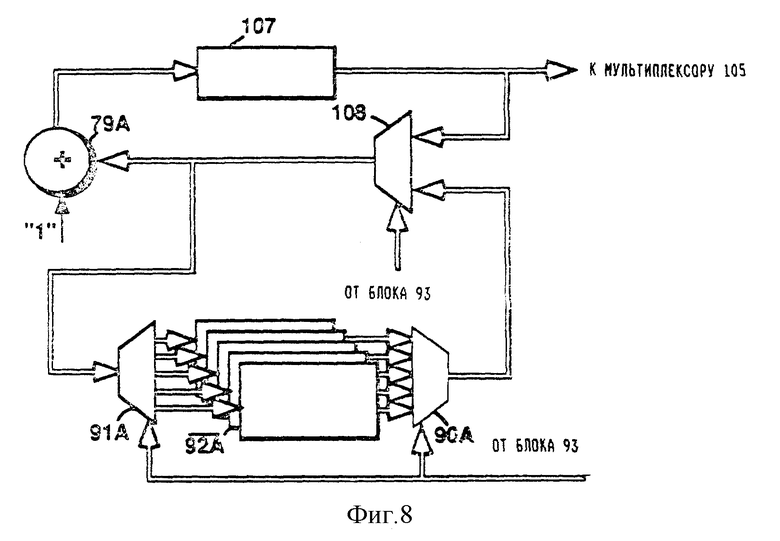

на фиг. 8 представлена блок-схема альтернативных схем регистров для приращения адресов памяти,

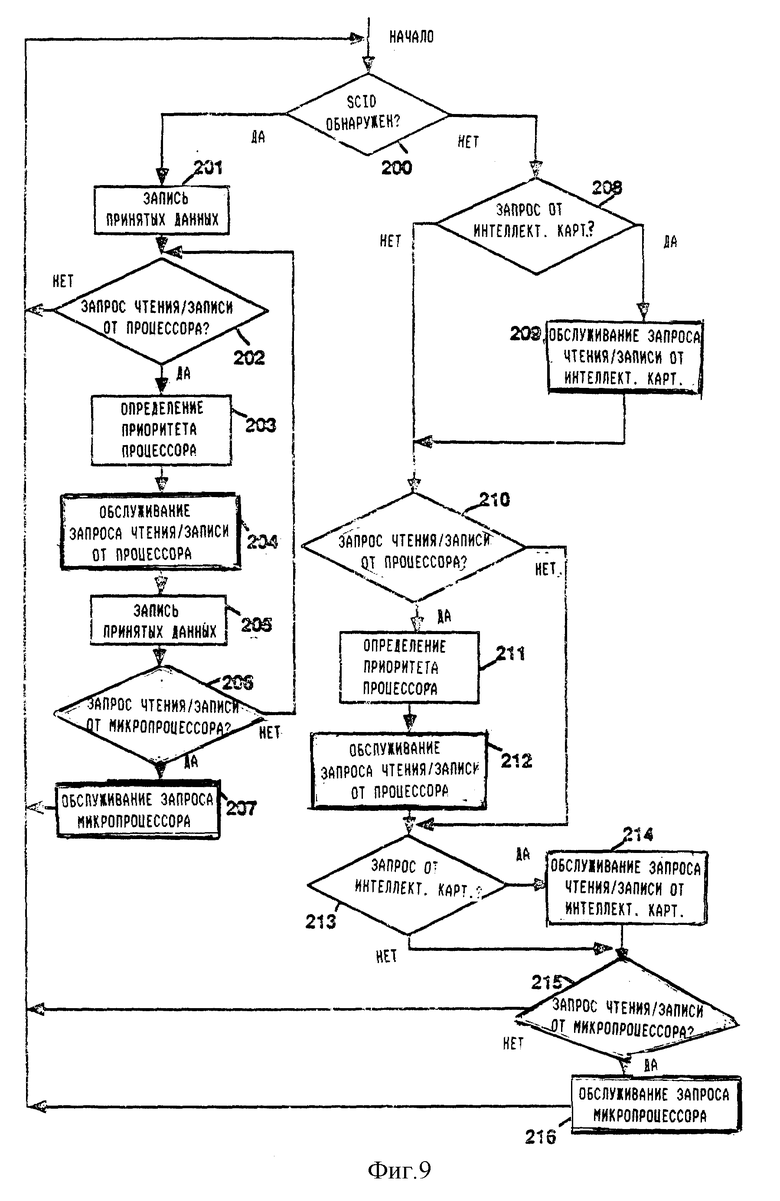

на фиг. 9 представлен алгоритм управления адресами памяти,

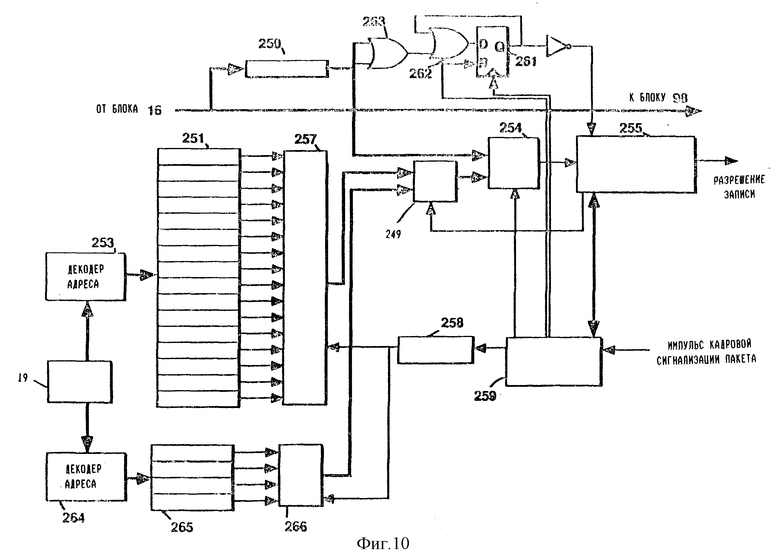

на фиг. 10 представлена блок-схема фильтра условного доступа/обнаружителя стартового кода.

На фиг. 1 показан сигнальный поток, где квадраты представляют собой пакеты сигнала, являющиеся компонентами множества различных телевизионных или интерактивных телевизионных программ. Предполагается, что эти компоненты программ состоят из сжатых данных и, следовательно, количество видеоданных меняется в зависимости от соответствующего изображения. Пакеты имеют фиксированную длину. Пакеты, обозначенные буквами с одинаковыми первыми цифрами индексов, соответствуют компонентам одной программы. Например, Vi, Ai и Di представляют соответственно видеопакет, аудиопакет и пакет данных; пакеты, обозначенные V1, A1 и D1, представляют соответственно видеокомпоненту, аудиокомпоненту и компоненту данных программы 1, а пакеты, обозначенные V3, A31, A32 и D3 представляют, соответственно, видеокомпоненту, аудиокомпоненту 1, аудиокомпоненту 2 и компоненту данных программы 3. Пакеты данных Di могут содержать, например, данные управления, инициирующие определенные действия в приемнике, или они могут содержать машинную программу, которая должна быть выполнена, например, микропроцессором, расположенным в приемнике или связанным с приемником.

В верхней строке потока пакетов компоненты конкретной программы показаны сгруппированными вместе. Однако совершенно не обязательно, чтобы пакеты, соответствующие одной программе, были сгруппированы именно так, как показано, в виде неразрывной последовательности. Не существует также какого-либо особого порядка расположения соответствующих компонент.

Соответствующие пакеты включают префикс и полезные данные, как показано на фиг. 2. В данном примере префикс включает два 8-битовых байта, содержащие 5 полей, причем четыре из них (P, BB, CF, CS) являются 1-битовыми полями, а одно (SCID) - 12-битовым полем. Поле SCID является идентификатором компоненты сигнала. Поле CF содержит флаг, показывающий, является ли полезная информация в пакете скремблированной, а поле CS содержит флаг, показывающий, какой из двух альтернативных ключей дескремблирования следует использовать для дескремблирования скремблированных пакетов. Префикс каждого пакета занимает определенное положение в начале соответствующего пакета, и таким образом положение каждого поля легко идентифицировать.

В полезных данных имеется заголовок, в котором содержатся отсчет последовательности (CC) по модулю 16 и флаговый бит переключателя, зависящие от компоненты программы. Отсчет CC является просто последовательной нумерацией последовательных пакетов, соответствующих одной и той же компоненте программы. Бит переключателя представляет собой однобитовый сигнал, который для видеокомпоненты изменяет свой логический уровень (переключается) в пакетах, определяющих начало нового изображения (кадра), то есть в пакетах, содержащих заголовок уровня изображения.

На фиг. 3 представлена блок-схема части приемника цифрового телевизионного сигнала, содержащая элементы обратного транспортного процессора. Сигнал принимается антенной 10 и подается на тюнер 11, который выделяет из принятого сигнала определенную полосу частот и выдает сжатый сигнал в полосе частот модуляции в двоичном формате. Полоса частот выбирается пользователем с помощью микропроцессора 19 известными способами. Обычно в вещательных цифровых сигналах используют кодирование с исправлением ошибок, например код Рида-Соломона с прямой коррекцией ошибок. Таким образом, сигнал в полосе частот модуляции подается в декодер 12 с прямой коррекцией ошибок. Декодер 12 с прямой коррекцией ошибок синхронизирует принятые видеосигналы и формирует поток пакетов сигнала, подобный изображенному на фиг.1. Декодер 12 может выдавать пакеты через равные временные интервалы или по требованию, например, контроллера 17 памяти. В любом случае схемой с прямой коррекцией ошибок формируется сигнал кадрирования (кадровой синхронизации) пакетов, который отмечает интервалы времени, когда соответствующая информация в пакетном виде передается из декодера 12.

В принятой полосе частот может содержаться множество программ в пакетной форме, мультиплексированных с временным уплотнением. Для дальнейшего использования на последующие элементы схемы следует пропустить только пакеты, соответствующие одной программе. В настоящем примере предполагается, что пользователь не располагает информацией о том, какие пакеты выбирать. Необходимая информация содержится в программном указателе, который сам является программой, состоящей из данных, которые взаимосвязывают компоненты передаваемых программ посредством идентификаторов компонент сигнала и могут включать информацию, относящуюся, например, к правам абонентов. Программный указатель представляет собой список идентификаторов компонент сигнала для видеокомпонент, аудиокомпонент и компонент данных для каждой программы. Программному указателю (пакет D4 на фиг.1) назначен фиксированный идентификатор компоненты сигнала. При включении питания приемника микропроцессор 19 в соответствии с заданной программой загружает идентификатор, соответствующий программному указателю, в один из регистров из набора одинаковых программируемых регистров 13 идентификаторов компонент сигнала. Поля идентификаторов компонент сигнала из префиксных частей соответствующих принимаемых сигнальных пакетов из декодера 12 последовательно загружаются в дополнительный приемный регистр 14 идентификаторов компонент сигнала. Программируемые регистры и приемный регистр соединены с соответствующими входными портами устройства, реагирующего на идентификаторы компонент сигнала в соответствующих пакетах для направления полезных данных соответствующих пакетов в определенные области общей буферной памяти, это устройство выполнено в виде схемы 15 сравнения, где принятый идентификатор сравнивается с идентификатором программного указателя. Программируемые регистры 13, приемный регистр 14 и схема сравнения 15 образуют обнаружитель идентификаторов компонент сигнала, соединенный с источником пакетированного сигнала с временным уплотнением для обнаружения пакетов, идентифицированных с помощью соответствующих заранее заданных идентификаторов компонент сигнала. Если идентификатор пакета соответствует идентификатору программного указателя, схема 15 сравнения дает команду контроллеру 17 памяти направить этот пакет в заранее заданную область памяти 18 (являющейся общей буферной памятью) для использования микропроцессором. Если же принятый идентификатор не соответствует идентификатору программного указателя, то соответствующий пакет просто игнорируется.

Микропроцессор ожидает поступления команды программирования от пользователя через интерфейс 20, который изображен в виде клавиатуры, но может являться обычным пультом дистанционного управления или органами управления на передней панели приемника. Например, пользователь выбирает для просмотра программу, передаваемую по четвертому каналу (если использовать терминологию, принятую для аналоговых телевизионных систем). Микропроцессор 19 программируется так, что просматривает список программного указателя, загруженный в память 18, в поисках идентификатора, соответствующего компонентам программы четвертого канала, и загружает их в соответствующие другие регистры набора программируемых регистров 13, связанных с соответствующими трактами обработки сигналов компонент.

Принятые пакеты аудиокомпонент, видеокомпонент и компонент данных желаемой программы должны в конечном счете быть поданы соответственно на устройство 23 обработки аудиосигнала, устройство 22 обработки видеосигнала или устройства 21 (24) обработки сигнала вспомогательных данных. Данные поступают с относительно постоянной скоростью, но процессор обычно требует входные данные отдельными порциями (в соответствии, например, с определенным способом декомпрессии сигнала). В варианте системы, представленном на фиг. 3, соответствующие пакеты вначале направляются в заданные области памяти 18. Впоследствии устройства 21-24 обработки сигналов запрашивают из памяти 18 пакеты компонент. Маршрутизация через память обеспечивает желаемую скорость накопления и вывода данных.

Видеопакеты, аудиопакеты и пакеты данных загружаются в соответствующие заранее заданные области памяти для обеспечения устройствам обработки сигнала удобного буферизованного доступа к данным компонент. Для того чтобы полезная информация из пакетов соответствующих компонент программы была загружена в надлежащие области памяти, соответствующие схемы сравнения идентификаторов SCID должны быть связаны с этими областями памяти. Эта связь может быть осуществлена на физическом уровне - путем соответствующего исполнения контроллера 17 памяти, или может быть программируемой. В первом случае программируемые регистры 13 всегда будут связаны с определенными идентификаторами видео, аудио и данных соответственно. Во втором случае идентификаторы видео, аудио и данных могут быть загружены в любой из программируемых регистров 13, а требуемая связь будет установлена программированием контроллера 17 памяти при загрузке в программируемые регистры соответствующих идентификаторов.

В установившемся режиме, после того как идентификаторы компонент сигнала соответствующей программы загружены в программируемые регистры 13, идентификаторы принятых пакетов сигнала сравниваются со всеми идентификаторами, хранящимися в программируемых регистрах идентификаторов. Если для аудиосигнала, видеосигнала или сигнала данных имеет место совпадение идентификаторов, то полезные данные соответствующего пакета будут загружены в область или блок памяти, выделенный для соответствующего аудиосигнала, видеосигнала или сигнала данных.

Соответствующие пакеты из декодера 12 через дешифратор 16 поступают на контроллер 17 памяти. Поскольку скремблированы только полезные данные, то заголовки пакетов пропускаются дешифратором без изменений. Флаг CF префикса пакета определяет, следует ли дескремблировать данный пакет, а флаг CS определяет, каким способом данный пакет следует дескремблировать. В случае, если для пакета не достигнуто совпадение идентификаторов, дешифратор может просто блокировать прохождение любых данных. Альтернативно в такой же ситуации дешифратор может осуществлять дешифрование в соответствии с последними установленными параметрами, а контроллер записи в память может быть блокирован, чтобы отбросить соответствующий пакет.

Программирование дешифратора осуществляется посредством ключей дешифрования, получаемых от блока 31 интеллектуальной карточки. Интеллектуальная карточка реагирует на информацию, касающуюся прав пользования, содержащуюся в определенных пакетах программного указателя, и формирует соответствующие ключи дешифрования. В данном примере система содержит два уровня шифрования или программного доступа: сообщения контроля, касающиеся прав пользования, и сообщения управления, касающиеся прав пользования. Информация контроля и управления, относящаяся к правам абонента на пользование программами, регулярно передается в пакетах, имеющих специальные идентификаторы, которые включены в поток пакетов, содержащий программный указатель. Информация сообщений контроля, содержащаяся в этих пакетах, используется интеллектуальной карточкой для формирования ключей дешифрования, используемых дешифратором. Информация сообщений управления, содержащаяся в этих пакетах, используется интеллектуальной карточкой конкретного абонента для определения программ, к которым данный абонент имеет право доступа. Эта информация может относиться к географическому расположению абонентов, к определенной группе абонентов или к определенному абоненту. Например, описываемая система включает модем (не показан) для передачи информации, относящейся к оплате, распространителю программ, например, обеспечивающему трансляцию через спутник. В интеллектуальную карточку могут быть запрограммированы, например, код зоны и телефонный номер пункта приема. Сообщения управления могут включать данные, которые после обработки интеллектуальной карточкой запретят или разрешат доступ к определенным программам в определенных районах.

Распространителю программ может понадобиться срочно отменить показ программы в определенных районах или для определенных групп пользователей. Например, может понадобиться срочно отменить трансляцию футбольного матча в районах, расположенных поблизости от стадиона, если билеты на матч не распроданы. Информация такого рода поступает непосредственно перед началом игры. Оставшегося короткого времени может не хватить для программирования сообщений управления так, чтобы отменить трансляцию в определенном районе. Для обеспечения мгновенного прекращения трансляции применяется дополнительное кодирование информации, касающейся прав пользования, в полезных данных, касающихся прав пользования.

Пакеты, содержащие данные, касающиеся прав пользования, включают заголовок, состоящий из 128 бит, которые распределены в 4 группы по 32 бита, имеющие специальное кодирование. Согласованный фильтр или декодер 30 E-кода устроен так, что обнаруживает определенные комбинации битов в пределах 128-битового заголовка. Если такая комбинация обнаружена, то декодер 30 передает сообщение контроллеру 17 и интеллектуальной карточке 31 (через память 18) для того, чтобы оставшаяся часть полезных данных, касающихся прав пользования, стала доступна для интеллектуальной карточки. Если такая комбинация не обнаружена, то полезные данные не принимаются конкретным приемником. Если согласованный фильтр 30 выполнен программируемым, то специальные коды могут периодически меняться. Эти коды могут периодически выдаваться с помощью интеллектуальной карточки. Более подробно работа интеллектуальных карточек, связанная с правами зрителей, рассмотрена в "THE SATELLITE BOOK, A COMPLETE GUIDE TO SATELLITE TV THEORY AND PRACTICE, Swift Television Publications, 17 Pittsfield, Cricklade, Wilts, England, Section 25."

Согласованный фильтр или декодер E-кода, выполнен так, что выполняет и вторую функцию: обнаруживает определенные заголовки, соответствующие стандарту передачи движущихся изображений MPEG. Эти заголовки или стартовые коды имеют длину 32 бита (именно поэтому заголовки полезных данных, касающиеся прав пользования, разделены на группы по 32 бита в каждом). Если видеоданные утеряны, то MPEG-видеодекодер может начать декомпрессию видеоданных только в определенных точках входа в данных. Эти точки входа совпадают со стартовыми кодами MPEG. Декодер может быть выполнен так, чтобы взаимодействовать с контроллером 17 памяти для воспрепятствования прохождению видеоданных в память после потерь видеопакетов и возобновления записи полезных видеоданных в память только после того, как декодер 30 зарегистрирует следующий стартовый код MPEG.

На фиг. 4 представлен вариант устройства контроллера 17 памяти, показанного на фиг. 3 и выполняющего функции схемы управления памятью. Компоненты программы хранятся в памяти 18 в различных смежных блоках. Кроме того, в памяти 18 могут быть помещены и другие данные, например данные, формируемые микропроцессором 19 или интеллектуальной карточкой (не показана).

Адреса в память 18 подаются из мультиплексора 105, а данные в память 18 поступают из средств для подачи соответствующих полезных данных, которые выполнены в виде мультиплексора 99. Выходные данные схемы управления памятью подаются на устройства обработки сигналов через дополнительный мультиплексор 104. Данные на выходе мультиплексора 104 формируются из данных, поступающих из микропроцессора 19, памяти 18 или непосредственно из мультиплексора 99. Предполагается, что данные программы соответствуют стандартному качеству и разрешению изображения и поступают с определенной скоростью. С другой стороны, приемник может выдавать сигналы, соответствующие телевидению высокой четкости, идущие со значительно большей скоростью. Практически все данные, вырабатываемые декодером с прямой коррекцией ошибок, проходят через память 18, через мультиплексор 99 и схему 102 записи/считывания памяти, за исключением высокоскоростных сигналов телевидения высокой четкости, которые могут направляться из мультиплексора 99 непосредственно на мультиплексор 104. На мультиплексор 99 данные поступают из дешифратора 16, из схем интеллектуальной карточки, включающих интерфейс для связи с интеллектуальной карточкой, из микропроцессора 19 и источника 100 кодов ошибки информации. Используемый здесь термин "коды ошибки информации" означает специальные кодовые слова, которые вводятся в поток данных для того, чтобы приостановить работу устройства обработки сигналов (декомпрессора) до обнаружения заранее определенного кодового слова, такого как стартовый код, а затем возобновить обработку, например, в соответствии с этим стартовым кодом.

Адреса памяти поступают на мультиплексор 105 из первых средств прямого доступа к памяти для формирования адресов памяти для хранения в ней полезных данных из основных пакетов, выполненных в виде схем 79-97 адресации программ, из микропроцессора 19, из блока 31 интеллектуальной карточки и из вторых средств прямого доступа к памяти для формирования адресов для хранения в памяти полезных данных из вспомогательных пакетов, которые выполнены в виде вспомогательного счетчика 78 адресов пакетов. Выбор конкретного адреса в конкретный момент времени осуществляется схемой 98 прямого доступа к памяти. Управляющие сигналы идентификатора SCID из схемы сравнения 15 и сигналы "потребности в данных" от соответствующих устройств обработки сигнала поступают в схему 98, в результате чего осуществляется арбитраж доступа к памяти. Схема 98 взаимодействует с контроллером 93 указателей служб, чтобы обеспечить для компонент сигнала программы, соответствующие адреса считывания и записи.

Адреса для блоков памяти, соответствующих различным компонентам сигнала, формируются четырьмя группами 83, 87, 88 и 92 регистров указателей служб или компонент программы. Указатели начала соответствующих блоков памяти (начальные указатели), в которых хранятся соответствующие компоненты сигнала, содержатся в регистре 87. Эти указатели начала блока могут быть фиксированными или могут быть вычислены известными способами управления памятью в микропроцессоре 19.

Указатели последнего адреса для соответствующих блоков памяти хранятся в наборе регистров 88 служб, по одному для каждой возможной компоненты программы. Подобно начальным адресам, конечные адреса могут иметь фиксированные значения или же могут быть вычислены микропроцессором 19. Использование вычисляемых значений для указателей начала и конца блоков является предпочтительным, поскольку позволяет создать более гибкую систему при меньшем объеме памяти.

Указатели записи в память или головные указатели формируются сумматором 80 и головными регистрами 83 служб. Для каждой возможной компоненты программы имеется свой головной регистр службы. Значение указателя записи в память или головного указателя хранится в регистре 83 и поступает на мультиплексор 105 адреса во время цикла записи в память. Головной указатель также подается в сумматор 80, где он увеличивается на единицу, увеличенное значение указателя хранится в соответствующем регистре 83 для использования в следующем цикле записи. Регистры 83 выбираются контроллером 93 указателей служб для соответствующей компоненты программы, обслуживаемой в данный момент времени.

В этом примере предполагается, что указатели начала и конца блоков содержат 16 битов. Регистры 83 формируют 16-битовые указатели записи в память или головные указатели, 16-битовые указатели были выбраны для того, чтобы облегчить использование 16-битовых или 8-битовых шин для загрузки указателей начала и конца блоков в регистры 87 и 88. С другой стороны, память 18 имеет 18-битовые адреса, 18-битовые адреса формируются за счет присоединения к 16-битовым головным указателям двух старших разрядов указателя начала блока, причем эти два разряда указателя начала блока помещаются в старшие разряды 18-битового адреса записи. Из соответствующих регистров 87 указатели начала блока поступают на контроллер 93 указателей служб. Контроллер указателей служб отделяет два старших бита от указателей начала блока, хранящихся в регистрах 87, и объединяет эти биты с 16-битовой шиной головных указателей. Это иллюстрируется шиной 96, которая изображена объединяющейся с шиной головных указателей, идущей от мультиплексора 85, а также на фиг. 5 сплошными стрелками.

На фиг. 5 верхний, средний и нижний ряды квадратов представляют разряды соответственно указателя начала блока, адреса и головного или хвостового указателя. Старшему биту соответствует большее число. Стрелками показано, из каких именно разрядов указателей начала блока или головных/хвостовых указателей берутся соответствующие биты адреса. Сплошные стрелки на чертеже соответствуют установившемуся режиму.

Аналогично указатели чтения из памяти или хвостовые указатели формируются сумматором 79 и хвостовыми регистрами 92 служб. Для каждой возможной компоненты программы имеется хвостовой регистр службы. Указатель чтения или хвостовой указатель хранится в регистре 92 и поступает на мультиплексор 105 адреса во время цикла считывания из памяти. Хвостовой указатель подается также на сумматор 79, где он увеличивается на единицу, увеличенное новое значение указателя хранится в соответствующем регистре 92 для использования в следующем цикле чтения. Регистры 92 выбираются контроллером 93 служебных указателей для соответствующей компоненты программы, обслуживаемой в данный момент времени.

Регистры 92 формируют 16-битовые хвостовые указатели. 18-битовые адреса чтения формируются за счет присоединения к 16-битовым хвостовым указателям двух старших битов начального указателя, причем эти два бита начального указателя помещаются в старшие разряды объединенного 18-разрядного адреса. Контроллер указателей служб отделяет два старших бита от указателей начала блока, хранящихся в регистрах 87, и объединяет эти биты с 16-битовой шиной хвостовых указателей. Это иллюстрируется шиной 94, которая изображена объединяющейся с шиной хвостовых указателей, идущей от мультиплексора 90.

Данные хранятся в памяти 18 по вычисленному адресу. После записи байта данных головной указатель увеличивается на единицу и сравнивается с указателем конца блока (конечным указателем) данной компоненты программы. Если они совпадают, старшие биты головного указателя заменяются на младшие 14 битов указателя начала блока, а в два младших разряда той части адреса, которая соответствуют головному указателю, записываются нули. Это иллюстрируется на фиг. 5 штриховыми стрелками между указателем начала блока и адресом. Эта операция показана стрелкой 97, выходящей из контроллера 93 служебных указателей (выполняющего функции средств, реагирующих на обнаружение равенства головного указателя и соответствующего конечного указателя) и направленной к шине головных указателей, идущей от мультиплексора 85. Предполагается, что 14 битов указателя начала блока пишутся поверх битов головного указателя. Замена в адресе старших битов головного указателя младшими битами указателя начала блока для данного одного цикла записи позволяет осуществить "прокрутку" внутри блока памяти, задаваемого двумя старшими битами указателя начала блока, и таким образом избежать перепрограммирования адресов записи в начале каждого пакета на какую-либо особую ячейку памяти в пределах блока.

Если когда-либо головной указатель окажется равным хвостовому указателю (который указывает, где расположены данные для чтения из памяти 18), в блок прерываний микропроцессора подается сигнал, сообщающий, что головной и хвостовой указатели встретились. При этом дальнейшая запись в память 18 из этого программного канала запрещается, пока микропроцессор не разблокирует канал. Это очень редкая ситуация и она не должна иметь место при нормальной работе.

Вывод данных из памяти 18 происходит по требованию соответствующего устройства обработки сигналов в соответствии с адресами, вычисленными с помощью сумматора 79 и регистров 92. После чтения байта хранимых данных хвостовой указатель увеличивается на единицу и сравнивается с указателем конца блока данного логического канала в контроллере 93 указателей служб. Если хвостовой указатель и указатель конца блока совпадают, старшие биты хвостового указателя замещаются на младшие 14 битов указателя начала блока, а в два младших разряда той части адреса, которая соответствуют хвостовому указателю, записываются нули. Это иллюстрируется стрелкой 95, выходящей из контроллера 93 служебных указателей и направленной к шине хвостовых указателей, идущей от мультиплексора 90. Если теперь хвостовой указатель окажется равным указателю начала блока, то соответствующий блок памяти считается пустым и выдача данных соответствующему устройству обработки сигналов (процессору) будет прекращена до тех пор, пока из декодера 12 с прямой коррекцией ошибок не поступят дополнительные данные для этого программного канала. Осуществление замены частей адресов чтения и записи, соответствующих головным и хвостовым указателям, 14-ю младшими битами указателя начала блока может быть осуществлено посредством соответствующего мультиплексирования или с помощью схем соединения с тремя состояниями.

Данные, передаваемые во вспомогательных пакетах, обычно являются каталогами, заголовками или управляющей информацией и таким образом их обработка происходит несколько иначе, чем обработка данных компонент программы. Данные во вспомогательных пакетах содержат информацию, необходимую для выделения участков памяти требуемого объема для хранения соответствующих компонент программ и любых других прикладных задач. Поэтому таким вспомогательным пакетам дается преимущество. Для каждой компоненты имеется два блока обслуживания. Каждый блок имеет 8-битовый последовательный адрес или ячейки для хранения 256 байт данных. Полный адрес каждого блока содержит 18 разрядов, как показано на фиг. 6. Восемь младших битов адреса формируются последовательным счетчиком. Девятый бит образован битом CS или битом ключа скремблирования из префикса транспортного пакета. Биты с 10 по 12 формируют, реагируя на конкретные идентификаторы, назначенные для обнаружения программ. Предположим, например, что система предназначена для обработки и приема пяти компонент программы (включая программный указатель) или служб. Таким образом, имеется пять идентификаторов, размещенных в соответствующих программируемых регистрах 13, и пять схем 15 сравнения идентификаторов. Каждая из пяти схем сравнения имеет выход, назначенный определенной компоненте программы. Пяти возможным программам, соответствующим пяти выходам схем сравнения, назначены трехбитовые коды, так как три бита являются минимальным количеством битов, необходимым для описания пяти состояний. Эти трехбитовые коды вводятся как десятый-двенадцатый биты адресов вспомогательных пакетов. Предположим, что идентификаторы для пяти соответствующих компонент программ назначены пяти программируемым регистрам, произвольно пронумерованным от 1 до 5. Трехбитовыми кодами, назначенными компонентам, связанным с программируемыми регистрами 1-5, являются 000, 001, 010, 011 и 100 соответственно. В зависимости от того, какая компонента программы обнаруживается в настоящий момент, трехбитовый код, связанный с программируемым регистром, содержащим идентификатор текущей компоненты программы, будет помещен в десятую-двенадцатую позиции адреса записи в память.

Шесть старших битов 18-разрядного вспомогательного адреса памяти формируются микропроцессором в соответствии с известными способами управления памятью.

На фиг. 7 представлен пример схемы формирования вспомогательного адреса памяти. На фиг. 7 изображен регистр 125 префикса, выполняющий функции обнаружителя ключа CS скремблирования в соответствующих вспомогательных пакетах и используемый для хранения бита CS префикса, который подается на контроллер 98 прямого доступа к памяти. Пять линий управления от обнаружителя 15 идентификаторов подаются на транслятор для формирования W-битовых кодов, соответствующих типу компоненты программы, с которой связаны соответствующие вспомогательные пакеты, выполненный в виде конвертера 126, преобразующего сигнал от пяти линий управления в три бита, что может быть осуществлено с помощью простого булева оператора. Три бита, сформированные конвертером 126, подаются на контроллер 98 прямого доступа к памяти, который формирует десять старших битов вспомогательных адресов. При обнаружении вспомогательного пакета, 10 старших битов адреса поступают на старшие разряды одного из регистров набора регистров 128. Восемь младших битов регистра 128 устанавливаются равными заранее заданному значению, обычно нулю, в начале каждого вспомогательного пакета с помощью средств для установки L-битового значения для компоненты равным заранее заданному значению в начале соответствующих пакетов, содержащих вспомогательные полезные данные указанной компоненты, указанные средства образованы мультиплексором 127 и контроллером 98 прямого доступа к памяти. Восемь младших битов прибавляются к десяти старшим битам и подаются на входной порт средств для присоединения L-битового значения к сцепленным Z-битовому указателю, W-битовому коду и ключу скремблирования, с формированием (N+M)-битового адреса памяти для вспомогательного пакета, эти средства выполнены в виде мультиплексора 129, осуществляющего преобразование 10-в-1. Восемь младших битов соответствующих адресов с выхода мультиплексора 129 подаются на сумматор 130, где 8-битовый адрес увеличивается на единицу и подается обратно на восемь младших разрядов регистра 128 через дополнительный мультиплексор 127. Эта увеличенная младшая часть адреса (совместно со старшей частью) служит следующим адресом для соответствующего вспомогательного пакета. Таким образом, сумматор 130, регистр 128 и мультиплексор 127 образуют накопитель для увеличения L-битового значения на единицу для каждого цикла адреса памяти. Мультиплексоры 127 и 129 управляются контроллером 98 прямого доступа к памяти для выбора текущего блока памяти для адресов. Отметим, что в альтернативном варианте по меньшей мере часть вспомогательных адресов может формироваться микропроцессором 19.

Обычно вспомогательные пакеты обрабатываются независимо и вся полезная информация, содержащаяся во вспомогательном пакете, загружается в память до того, как может быть использована. Если это так, то при нормальной работе в блок памяти, выделенный для записи в него текущего вспомогательного пакета, не будет обращений для записи и считывания одновременно. Поэтому для хранения адреса чтения и записи можно использовать одни и те же регистры. Как только вспомогательный пакет размещен в соответствующем блоке памяти, восемь младших битов адреса вновь устанавливаются на заранее заданный начальный адрес, чтобы приготовиться к чтению данных. В альтернативном варианте для формирования адреса чтения могут быть предусмотрены параллельный набор регистров, мультиплексоры и сумматор, аналогичные элементам 127-130. Эти адреса чтения из памяти могут быть мультиплексированы с временным уплотнением с помощью дополнительного мультиплексора, включенного каскадно с мультиплексором 129.

Управление чтением/записью осуществляется контроллером 93 указателей служб и контроллером 94 прямого доступа к памяти. Контроллер прямого доступа к памяти запрограммирован так, чтобы распланировать циклы чтения и записи. Это планирование зависит от того, выдает ли декодер 12 данные для записи в память или нет. Операции записи данных декодера 12 имеют приоритет, так что никакие входные данные компонент сигнала не теряются. В примере выполнения устройства, показанном на фиг.4, четыре типа устройств имеют доступ к памяти. Это интеллектуальная карточка (не показана), декодер 12 (точнее дешифратор 16), микропроцессор 19 и устройства целевого назначения (предназначенные для решения прикладных задач), такие как устройства обработки аудио- и видеосигналов. Конкуренция за доступ к памяти осуществляется следующим образом. Контроллер прямого доступа к памяти, реагирующий на требования доступа к памяти, поступающие от различных устройств обработки данных, перечисленных выше, распределяет блоки памяти для соответствующих компонент программы. Доступ к памяти осуществляется в интервалы времени длительностью 95 нс, в течение которых байт данных считывается из памяти 18 или записывается в нее. Существует два основных режима распределения доступа к памяти, характеризующиеся тем, что "декодер с прямой коррекцией ошибок выдает данные" и "декодер с прямой коррекцией ошибок не выдает данные" соответственно. В каждом из этих режимов, в предположении, что максимальная скорость данных от декодера с прямой коррекцией ошибок составляет 5 Мбайт/с или 1 байт в каждые 200 нс, распределение временных интервалов осуществляется согласно следующей очередности:

"Декодер выдает данные":

1) Запись данных декодера с прямой коррекцией ошибок;

2) Чтение устройством целевого назначения/чтение микропроцессором/запись микропроцессором;

3) Запись данных декодера с прямой коррекцией ошибок;

4) Чтение/запись микропроцессором.

"Декодер не выдает данные":

1) Чтение/запись интеллектуальной карточкой;

2) Чтение устройством целевого назначения/чтение микропроцессором/запись микропроцессором;

3) Чтение/запись интеллектуальной карточкой;

4) Чтение/запись микропроцессором.

Поскольку запись данных декодера с прямой коррекцией ошибок не может быть отложена, доступ декодера (точнее дешифратора) к памяти должен быть гарантирован в течение каждых 200 нс. Оставшиеся временные промежутки распределяются между устройствами целевого назначения и микропроцессором. Если данных для запрашивающих устройств нет, то микропроцессор использует временные интервалы целевого назначения.

Контроллер 93 взаимодействует с обнаружителем идентификаторов, чтобы определить, какому из соответствующих регистров - регистру указателя начала блока, головному регистру или регистру указателя конца блока - дать доступ к операциям записи в память. Контроллер 93 взаимодействует с контроллером прямого доступа к памяти, чтобы определить, какому из соответствующих регистров -регистру указателя начала блока, регистру указателя конца блока или хвостовому регистру - дать доступ к операциям считывания из памяти. Контроллер 98 прямого доступа к памяти управляет выбором соответствующих адресов и данных посредством мультиплексоров 99, 104 и 105.

Альтернативная предпочтительная схема для приращения адресов памяти представлена на фиг. 8. Она может быть использована в устройствах, изображенных на фиг. 4 и фиг. 7. Фиг. 8 иллюстрирует выполнение этой схемы для приращения хвостового указателя согласно фиг.4. В начале пакета указатель в соответствующем регистре 92А подается в сумматор 79А, в котором этот указатель увеличивается на единицу. Вместо того, чтобы хранить промежуточный увеличенный хвостовой указатель в регистрах 92А, показанных на фиг.8 (регистрах 92 на фиг.4), промежуточные значения увеличенного указателя последовательно помещают в рабочий регистр 107. После того, как для пакета сигналов сформировано последнее значение указателя, скорректированный указатель пересылается из регистра 107 в регистр 92А, связанный с идентификатором пакета.

Довольно часто возникает необходимость исключить данные из буфера памяти. Например, пакет может быть записан в память лишь частично, когда произошел системный сбой или прерывание поступления данных. Для экономии памяти исключение данных производят просто записью поверх частично записанного пакета данных. Запись поверх этих данных осуществляется путем установления соответствующего указателя равным значению, которое он имел в начале пакета. Такой сброс осуществляется путем непересылки значения, хранимого в регистре 107, в регистр указателя, то есть практически за счет отсутствия какого-либо действия вообще.

В случае, если произошла потеря пакета, предпочтительно помещать в поток сигналов видеокомпонент коды ошибок информации, чтобы заставить декомпрессор видеосигнала приостановить декомпрессию до того момента, когда в потоке данных появится определенная точка входа. Трудно предсказать заранее, где и в каком видеопакете может находиться следующая точка входа. Для того, чтобы обнаружить следующую точку входа как можно быстрее, необходимо вставить код ошибки информации в начало первого видеопакета, который поступит после обнаружения потери пакета. Схема на фиг. 4 помещает код ошибки информации в начало каждого видеопакета, а затем вырезает этот код ошибки информации в случае, если никакие потери в предшествующем пакете не обнаружены. Код ошибки информации помещается в первые М ячеек памяти, зарезервированных для полезных данных текущего видеопакета, путем записи в память 18 в течение М циклов записи, предшествующих поступлению полезных данных видеосигнала от дешифратора. Одновременно мультиплексор 99 управляется контроллером 98 прямого доступа к памяти так, что пересылает код ошибки информации от источника 100 к вводу/выводу (I/O) памяти 18. М является просто целым числом, равным количеству ячеек памяти, необходимому для хранения кода ошибки информации. Если предположить, что ячейка памяти может хранить 8-битовый байт, а код ошибки информации содержит 32 бита, то М равно 4.

Адреса для загрузки кода ошибки информации вырабатываются в соответствующем регистре 83 службы видеокомпоненты и выдаются через мультиплексор 82 и мультиплексор 85. Ясно, что первые М адресов, которые формирует регистр 83 указателей для загрузки кода ошибки информации в те ячейки памяти, которые в противном случае были бы заняты данными видеокомпоненты сигнала, представляют собой просто М последовательных адресов, которые в нормальной ситуации были бы получены с помощью головного указателя видеокомпоненты. Эти же адреса поступают на элемент 84 задержки на М циклов, поэтому сразу же после того, как последний байт кода ошибки информации записан в память 18, первые из М адресов появляются на выходе элемента 84 задержки.

Загрузка в память кода ошибки информации синхронизирована с обнаружением потерянного пакета. Загрузка кода ошибки информации одновременно с обнаружением потери пакета не накладывает никаких дополнительных временных ограничений на обработку потока сигналов.

Если обнаружена потеря пакета, то видеокомпонента текущего пакета загружается в память 18, начиная со следующей, то есть с (М+1)-й ячейки блока памяти, выделенного для этой компоненты сигнала. Это осуществляется с помощью устройства для выполнения корректирования при обнаружении потери пакетов, выполненного в виде мультиплексора 85, путем перевода мультиплексора 85 в режим, когда он продолжает пропускать незадержанные головные указатели из соответствующего регистра 83. Альтернативно, если потеря пакета не обнаружена, то первые М байтов видеокомпоненты текущего пакета помещаются в те ячейки памяти, где непосредственно до этого хранился код ошибки информации. Это осуществляется за счет того, что контроллер указателей служб переводит мультиплексор 85 в такой режим, когда он в течение М циклов записи пропускает задержанные головные указатели от элемента 84 задержки. По окончании М циклов записи контроллер 93 указателей служб переводит мультиплексор в такой режим, когда он опять пропускает незадержанные головные указатели. Когда мультиплексор переключается в прежний режим, соответствующий незадержанным указателям, первый незадержанный указатель соответствует (М+1)-му адресу.

Обнаружение ошибки в пакете или потери пакета осуществляется обнаружителем потери пакетов компонент программы, выполненным в виде детектора 101 ошибок, который реагирует на данные СС и HD (см. фиг. 2) в текущем пакете. Детектор 101 анализирует отсчет последовательности СС в текущем пакете, чтобы определить, отличается ли он на единицу от показаний отсчета последовательности в предыдущем пакете. Дополнительно анализируется бит переключателя в текущем пакете, чтобы определить, изменился ли он по сравнению с предыдущим пакетом. Если значение отсчета последовательности ошибочно, то анализируется бит переключателя. В зависимости от того, один или оба из битов отсчета последовательности и переключателя ошибочны или изменены, включается первый или второй режим коррекции. Во втором режиме, который включается, если отсчет последовательности ошибочен и бит переключателя изменился, система устанавливается на обработку пакета, содержащего заголовок уровня изображения. В первом режиме, когда только отсчет последовательности ошибочен, система устанавливается на обработку пакета, содержащего код начала вырезок (Уровень вырезок является подмножеством сжатых данных внутри кадра). Как в первом, так и во втором режиме код ошибки информации, записанный в память, сохраняется в соответствующих полезных данных, чтобы привести декомпрессор в готовность для осуществления коррекции.

В зависимости от конкретной конструкции данного приемника включение кодов ошибки информации в различные компоненты сигнала в случае, когда произошла потеря транспортных пакетов соответствующих компонент, может быть целесообразно или нет. Кроме того, может быть предпочтительным использовать разные коды ошибок информации для разных форматов компонент сигнала или разных процессов сжатия. Таким образом, могут понадобиться один или несколько источников кодов ошибки информации.

На фиг.9 представлен пример алгоритма доступа к памяти, осуществляемого контроллером 98. Контроллер 98 реагирует {200} на обнаружение или необнаружение принятого пакета, которое осуществляется путем обнаружения идентификаторов. Если идентификатор SCID обнаружен, что свидетельствует о наличии данных, поступивших из дешифратора 16, которые требуется записать в память, то один байт данных программы из дешифратора записывается {201} в буферную память 18. Блок памяти, в который он записывается, определяется процессором 93, реагирующим на текущий идентификатор SCID. Затем контроллер 98 определяет {202}, имеются ли запросы данных или запросы на доступ к памяти 18 для чтения/записи от устройств обработки компонент программы, в том числе от интеллектуальной карточки и микропроцессора. Если запросы данных отсутствуют, то контроллер возвращается к шагу { 200} . Если получен запрос на чтение/запись данных, то контроллер устанавливает {203} приоритет запроса. Это осуществляется с помощью известной процедуры прерывания или путем последовательного поочередного побайтового обслуживания устройств обработки сигналов, запрашивающих данные, в произвольном порядке. Например, предположим, что произвольный порядок приоритетов доступа следующий: видео, аудио I, аудио II, интеллектуальная карточка и микропроцессор. Предположим также, что запрос на доступ к памяти поступил от процессоров видео, аудио II и микропроцессора. Во время текущей операции на шаге {203} из памяти считывается байт видеосигнала. В течение следующей операции на шаге {203} из памяти считывается байт аудио II, а в течение следующей операции на шаге {203} в память 18 записывается или из памяти 18 считывается байт данных микропроцессора и т.д. Отметим, что адреса для доступа к памяти интеллектуальной карточки или микропроцессора формируются интеллектуальной карточкой или микропроцессором соответственно, однако адреса для видеосигналов, аудиосигналов и программного указателя формируются устройствами 80-93 формирования указателей адресов.

Когда приоритет доступа к памяти установлен {203}, то осуществляется { 204} обслуживание, требующего доступа к памяти устройства обработки сигналов путем записи в память 18 или считывания из памяти 18 одного байта данных. Затем в память записывается {205} байт данных от дешифратора 16. Производится {206} проверка, запрашивает ли доступ к памяти микропроцессор. Если микропроцессор запрашивает доступ к памяти, то он обслуживается {207} путем записи или чтения одного байта данных. Если микропроцессор не запрашивает доступ к памяти, процедура возвращается на шаг {202}, чтобы определить, запрашивает ли доступ к памяти какое-либо из устройств обработки сигналов. Таким образом гарантировано, что входящие данные всегда получат доступ к памяти в каждый период доступа к памяти через один, а остальные периоды доступа к памяти распределены между устройствами обработки сигналов программ.

Если данные от дешифратора 16 в настоящий момент не поступают, то есть в настоящий момент идентификатор SCID не обнаружен, то выполняются операции { 208-216} . Прежде всего проверяется {208}, запрашивает ли доступ к памяти интеллектуальная карточка. Если да, то она обслуживается {209} путем чтения или записи в память одного байта, в противном случае проверяется {210}, запрашивает ли доступ к памяти какое-либо из устройств обработки сигналов. Если запрос на чтение/запись имеется, то контроллер прямого доступа к памяти определяет { 211} приоритет запроса. Соответствующее устройство обработки сигналов обслуживается {212} путем считывания из памяти или записи в память одного байта данных. Если запрос на чтение/запись данных от устройств обработки сигналов не поступал, то процедура переходит к шагу {213}, где производится проверка, запрашивает ли доступ к памяти интеллектуальная карточка. Если да, то она обслуживается {216} путем чтения или записи в память одного байта, в противном случае процедура возвращается к шагу {200}.

Следует понимать, что в данном примере предпочтительного выполнения, в режиме, когда "декодер с прямой коррекцией ошибок не выдает данных", интеллектуальная карточка имеет приоритет доступа к памяти по сравнению с другими устройствами обработки сигнала в соотношении два к одному. Этот приоритет запрограммирован в программируемом конечном автомате, входящем в состав контроллера прямого доступа к памяти, и может быть изменен микропроцессором. Как отмечено ранее, система предназначена для обеспечения интерактивных служб и микропроцессор 19 в ответ на интерактивные данные по меньшей мере частично производит интерактивные операции. В этой роли микропроцессор 19 использует память 18 как в качестве запоминающего устройства целевого назначения (для прикладных задач), так и в качестве рабочей памяти. В этих случаях оператор системы может изменить приоритет доступа к памяти, чтобы обеспечить микропроцессору 19 доступ к памяти с большей частотой. Перепрограммирование приоритета доступа к памяти может быть включено в интерактивные прикладные программы.

На фиг. 10 представлен вариант устройства для обнаружения пакетов, которые включают информацию условного доступа или стартовые коды MPEG (декодер 30 на фиг. 3). Декодер 30 настраивается так, чтобы обнаруживать или полезные данные, касающиеся прав пользования, или же стартовые коды MPEG, что определяется принимаемым в данный момент идентификатором SCID. В отношении фиг. 10 предполагается, что данные, поступающие из дешифратора 16, представляют собой 8-битовые байты, занимающие определенные позиции в пакетах. То есть первый байт полезных данных, касающихся прав пользования, или первый байт стартового кода MPEG совпадает с началом полезных данных пакета, так что при обнаружении специального заголовка или начальных кодовых слов их позиция в потоке битов/байтов известна точно. С дешифратора 16 данные поступают на 8-битовый регистр 250, который имеет 8-битовый параллельный выходной порт, соединенный с соответствующими первыми входами схемы сравнения 254, которая может, например, представлять собой набор из восьми схем ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, соответствующие выходы которых соединены со схемой И и регистром-защелкой. Регистр-защелка может быть регистром-защелкой данных, выполненным так, чтобы фиксировать результат на выходе вентиля И в течение каждого байта.

32-битовый стартовый код MPEG хранится в виде четырех байтов в наборе 265 8-битовых регистров. Коды заголовка, касающегося прав пользования, хранятся как 8-битовые байты в наборе 251 из шестнадцати 8-битовых регистров. Загрузкой в наборы 251 и 265 регистров управляет микропроцессор 19 и/или интеллектуальная карточка. Регистры 265 стартового кода соединены с мультиплексором 266, осуществляющим преобразование 4-в-1, а регистры заголовка прав пользования соединены с мультиплексором 257, осуществляющим преобразование 16-в-1. Выходные порты мультиплексоров 257 и 266 соединены с мультиплексором 249, осуществляющим преобразование 2-в-1. Выходы мультиплексора 249 соединены с соответствующими вторыми входами схемы сравнения 254. Отметим, что входные и выходные соединения мультиплексоров 249, 257 и 266 представляют собой 8-разрядные шины. Если соответствующие значения сигнала на выходе регистра 250 совпадают с соответствующими значениями сигнала на выходе мультиплексора 249, то для соответствующего байта данных схема сравнения 254 вырабатывает сигнал ИСТИНА.

Для обнаружения стартового кода осуществляется сканирование мультиплексора 266 счетчиком 258 так, что синхронно с поступлением первых четырех байтов данных от дешифратора 16, к схеме ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ последовательно подключаются четыре разных регистра 265. Альтернативно для обнаружения заголовка полезных данных, касающихся прав пользования, осуществляется сканирование мультиплексора 257 счетчиком 258 так, что к схеме сравнения последовательно подключаются разные регистры 265.

Выход схемы сравнения соединен с устройством 255 накопления и проверки. Устройство 255 проверяет, произошло ли совпадение какого-либо заранее заданного количества байтов, и если произошло, то устройство 255 формирует сигнал разрешения записи данных, касающихся прав пользования, в исследуемой части конкретных полезных данных. В данной системе заголовок полезных данных прав пользования содержит 128 битов, сгруппированных в четыре 32-битовых сегмента. Устройства у разных абонентов будут выполнены так, чтобы искать разные комбинации байтов в этих 128 битах. Например, у одного абонента устройство может быть настроено на совпадение первых четырех байтов заголовка полезных данных, касающихся прав пользования. У другого абонента устройство может быть настроено на совпадение четырех следующих байтов заголовка полезных данных, касающихся прав пользования, и т.д. В любом из этих примеров устройство 255 определит, произошло ли совпадение соответствующих четырех последовательных байтов.

Устройство, представленное на фиг. 10, содержит также схему (элементы 261-263) обнаружения состояния, когда весь заголовок полезных данных прав пользования содержит нули. Биты соответствующих поступающих байтов данных подаются на соответствующие контакты 8-битового вентиля ИЛИ 263 . Если хотя бы один из битов равен логической единице, то вентиль ИЛИ 263 формирует на выходе логическую единицу. Выход вентиля ИЛИ 263 соединен с первым входом имеющего два входа вентиля ИЛИ 262, выход и второй вход которого соединены соответственно со входом данных и выходом Q защелки 261 с D-триггером. Защелка с D-триггером тактируется схемой 259 синхронизации синхронно с поступлением байтов входящих данных. Если хотя бы один бит в любом из байтов данных, поступивших после сброса защелки, равен единице, то на выходе Q защелки до прихода следующего импульса сброса будет логическая единица. Выход Q защелки 261 соединен с инвертором, на выходе которого устанавливается нуль, если на его вход подана единица. Таким образом, если после того, как через регистр 250 прошли 128 битов (16 байтов) заголовка, сигнал на выходе инвертора имеет высокий уровень, то все 128 битов равны нулю. Устройство 255, реагирующее на поступление сигнала высокого уровня от инвертора после прохождения заголовка полезных данных прав пользования, формирует сигнал разрешения записи.

Установлено, что особенно эффективным является размещение всей системы, включающей обнаружитель идентификаторов, дешифратор, схемы адресации, фильтр условного доступа и интерфейс интеллектуальной карточки в одной микросхеме. Это уменьшает число внешних трактов, которые могут ограничивать быстродействие системы.

Изобретение относится к устройствам для обработки пакетов данных компонент программ из пакетного видеосигнала и для выделения соответствующих полезных данных различных сигнальных компонент программ. Техническим результатом является расширение функциональных возможностей за счет использования памяти для буферирования компонент программ для управляющей работы процессора и для интерактивных программ. Система для обработки компонент программ содержит источник пакетированного сигнала с временным уплотнением, общую буферную память, множество устройств обработки компонент программы, обнаружитель идентификаторов компонент сигнала, средства для подачи соответствующих полезных данных, схему адресации. Схема управления памятью для транспортного процессора содержит первые и вторые средства прямого доступа к памяти для формирования адресов памяти для хранения полезных данных из основных пакетов в памяти. 2 с. и 17 з.п. ф-лы, 10 ил.

| УСТРОЙСТВО для ПРЕССОВАНИЯ ИЗДЕЛИЙ | 0 |

|

SU241946A1 |

| US 5168356 A, 01.12.1992 | |||

| US 5289276 A, 22.02.1994 | |||

| US 5233654 A, 03.08.1993 | |||

| Микроэлектронная вычислительная машина | 1979 |

|

SU1061606A1 |

| Микропроцессорная система | 1981 |

|

SU1172455A3 |

Авторы

Даты

2000-02-20—Публикация

1995-04-21—Подача