Данное изобретение относится к области аппаратуры для обработки данных, имеющей шину данных. Конкретнее, данное изобретение относится к такой аппаратуре, которая имеет схему задатчика шины (устройство управления передачей данных по шине -прим. перев.) и схему исполнителя шины.

Известны выполнения структур с ведущей и ведомой шинами, в которых задатчик шины ответственен за инициацию и управление передачей данных по шине данных, с одним или более исполнителями шины, служащими для реагирования на транзакции, инициируемые задатчиком шины. Такие структуры легко расширяются и позволяют одному задатчику шины управлять различными исполнителями шины. Недостатком таких структур является то, что задатчик шины должен иметь возможность приспосабливаться к разным параметрам работы в различных исполнителях шины, с которыми он осуществляет связь, например, скорость, с которой к конкретному исполнителю шины или от него могут передаваться данные, либо требования адресации каждого исполнителя шины.

Это особенно существенно с точки зрения режимов высокоэффективной передачи по шине данных, где не все исполнители шины одинаково способны к такой высокоэффективной работе. Это создает трудности в том, что при добавлении в систему нового исполнителя шины задатчик шины должен перепрограммироваться/переконфигурироваться для учета рабочих характеристик этого нового исполнителя шины. Это является неблагоприятным дополнительным усложнением при разработке новой системы, в которой желательно в идеале просто присоединять различные составляющие части к шине данных без необходимости изменения этих составляющих частей для такой конкретной комбинации.

Европейская патентная заявка EP-A-0348113 рассматривает контроллер программируемой памяти, который поддерживает пересылки в пакетном режиме, а когда пакетный режим должен закончиться, - сигналы к процессору.

Статья "Computer system chаnnel performance enhancement via address boundary release" ("Улучшение характеристик канала компьютерной системы с помощью версии адресной границы") в журнале IBM Technical Disclosure Bulletin, vol. 33, N 6B, Novemder 1990, New York, US, p. 422, рассматривает контроллер памяти, который вводит состояние ожидания, как это требуется на границах страниц.

Статья Amitoi et al. , "Burst mode memories improve cache design" ("Запоминающие устройства в пакетном режиме улучшают схему кэша") в журнале Wescon Conference Record, vol. 34, Novemder 1990, North Hollywood, US, pp. 29 - 32, рассматривает интегральную схему, содержащую задатчик шины и исполнителя шины.

В одном своем аспекте изобретение обеспечивает устройство для обработки данных, содержащее:

шину данных для переноса слов данных и слов адреса;

схему задатчика шины для инициации передачи в пакетном режиме по упомянутой шине данных, в которой упомянутый задатчик шины генерирует слово адреса, указывающее начальный адрес последовательности адресом, относящихся к соответствующим словам из множества слов данных, подлежащих передаче по упомянутой шине данных в следующие друг за другом циклы обработки;

и схему исполнителя шины для приема упомянутого множества слов данных при упомянутой передаче в пакетном режиме от упомянутой схемы задатчика шины по упомянутой шине данных; при этом:

упомянутая шина данных включает в себя линию сигнала запроса адреса;

упомянутая схема исполнителя шины включает в себя средство для генерирования сигнала запроса адреса, когда упомянутая схема исполнителя шины запрашивает слово адреса в следующем периоде обработки; и

упомянутая схема задатчика шины включает в себя средство, реагирующее на сигнал запроса адреса, принятый от упомянутой схемы исполнителя шины по упомянутой линии сигнала запроса адреса, для прерывания упомянутой передачи в пакетном режиме и генерирования дополнительного слова адреса в следующем периоде обработки.

Передача в пакетном режиме от схемы задатчика шины к схеме исполнителя является особенно действенным и высокоэффективным режимом работы. Если в схеме исполнителя шины передаваемые данные будут связаны с заданной последовательностью адресов, начинающейся с исходного указанного адреса, то необходимо указать только начальный адрес. Таким образом, за одним словом адреса могут следовать сотни и тысячи слов данных. Увеличение числа слов данных, передаваемых на одно подлежащее указанию слово адреса, имеет преимущество в снижении времени, потребного для передачи заданного блока слов данных.

К сожалению, не все исполнители шины способны работать с такими передачами в пакетном режиме. В качестве примера, рассмотрим динамическое оперативное запоминающее устройство (ДОЗУ) (DRAM) с режимом разбивки на страницы. Такие ДОЗУ могут поддерживать передачи в пакетном режиме кроме случаев, когда пересекается граница страницы. Когда пересекается граница страницы, это ДОЗУ запрашивает посылку нового слова адреса. Для того, чтобы работать с этим как обычно, хозяин шиной должен различать границы страниц в ДОЗУ, и не посылать передачи в пакетном режиме, которые переходят границу страницы.

Изобретение и распознает и решает эту и подобные трудности благодаря линии сигнала запроса адреса в шине данных, посредством чего схема исполнителя шины прерывает передачу в пакетном режиме от схемы задатчика шины и запрашивает дополнительное слово адреса, которое должно быть послано ей в следующем периоде обработки. Таким образом, схема задатчика шины не нуждается в адаптации к каждой присоединяемой схеме исполнителя шины и может просто обрабатывать с высокой эффективностью передачу в пакетном режиме, пока соответствующая схема исполнителя шины индицирует необходимость в дополнительном слове адреса. Таким образом, гибкость в модифицировании системы обеспечивается без обязательного компромисса за счет высокоэффективной передачи в пакетном режиме.

Предпочтительный признак изобретения, связанный в сильной степени с наличием линии сигнала запроса адреса, состоит в том, что упомянутая шина данных включает в себя линию сигнала запроса периода ожидания;

упомянутая схема исполнителя шины включает в себя средство для генерирования сигнала запроса периода ожидания, когда упомянутой схемой исполнителя шины запрашивается период ожидания в упомянутом следующем периоде обработки; и

упомянутая схема задатчика шины включает в себя средство, реагирующее на сигнал запроса периода ожидания от упомянутой схемы исполнителя шины по упомянутой линии сигнала запроса периода ожидания в упомянутом следующем периоде обработки.

Таким образом, скорость, с которой схема исполнителя шины может работать с принимаемыми словами данных, может подстраиваться так, чтобы схема исполнителя шины могла дать возможность схеме задатчика шины вставлять периоды ожидания перед обработкой передачи следующего слова данных. Примером такой работы мог быть случай, когда шина данных передает 32-разрядные слова, тогда как схема исполнителя шины способна работать лишь с 8-разрядными словами. В этом случае при приеме от схемы задатчика шины 32-разрядного слова схема исполнителя шины могла бы занять, по меньшей мере, четыре периода обработки, чтобы прервать и запомнить принятое слово данных, и в это время схема исполнителя шины может выдавать сигнал запроса периода ожидания, чтобы задержать передачу других слов данных от схемы хозяина шины.

Наиболее предпочтительный признак состоит в том, что упомянутый задатчик шины включает в себя средство, реагирующее на одновременный прием сигнала запроса адреса и сигнала запроса периода ожидания, для прекращения и повторения в более позднее время передачи в пакетном режиме.

Таким образом, схема исполнителя шины способна заставить полностью прекратить передачу в пакетном режиме, инициированную схемой задатчика шины. Это позволяет схемам исполнителя задатчика шины покинуть шину, как если бы передача не началась, в обстоятельствах, которые иначе могут вести к зависанию или сбою, в результате чего схема исполнителя шины стала бы недоступной.

Чтобы облегчить мутиплексирование слов адреса и слов данных на единственную шину данных, предпочтителен признак, состоящий в том, что упомянутая шина данных включает в себя линию сигнала, указания адреса или данных;

упомянутая схема задатчика шины содержит средство для генерирования сигнала указания адреса или данных, указывающего, должна упомянутая схема задатчика шины генерировать слово адреса или слово данных во время упомянутого следующего периода обработки как часть упомянутой передачи в пакетном режиме; и

упомянутая схема исполнителя шины включает в себя средство, реагирующее на сигнал указания адреса или данных, принятый от упомянутой схемы задатчика шины по упомянутой линии сигнала указания адреса или данных для управления обработкой упомянутой схемой исполнителя шины во время упомянутого следующего периода обработки.

Понятно, что схема задатчика шины и схема исполнителя шины могут быть отдельными структурными элементами. Однако имеется нарастающая тенденция к объединению, благодаря которой такие схемы задатчика шины и схемы исполнителя шины объединяются в интегральных схемах специального применения (ИССП) (ASIC). Настоящее изобретение особенно подходит для использования в ситуациях, где упомянутая схема задатчика шины и упомянутая схема исполнителя шины выполнены на единой интегральной схеме, т.к. количество вновь разрабатываемых различных схемных частей, необходимых для создания новой ИССП, снижается.

Понятно, что схема задатчика шины и одна или более схем исполнителя шины, присоединяемые к шине данных, могут принимать много форм. Однако изобретение особенно подходит для ситуаций, в которых схема задатчика шины является центральным блоком обработки, а одна или более схем исполнителя шины содержат оперативное запоминающее устройство с режимом разбиения на страницы или кэш (быстродействующее буферное запоминающее устройство большой емкости - прим. перев.).

В другом своем аспекте данное изобретение обеспечивает способ обработки данных, содержащий операции:

инициирование в схеме задатчика шины передачи в пакетном режиме по шине данных, в которой упомянутый задатчик шины генерирует слово адреса, указывающее начальный адрес последовательности адресов, относящихся к соответствующим словам из множества слов данных, подлежащих передаче по упомянутой шине данных в следующие друг за другом циклы обработки; и

прием в схеме исполнителя шины упомянутой передачи в пакетном режиме от упомянутой схемы задатчика шины по упомянутой шине данных; при этом:

когда упомянутой схемой исполнителя шины в следующем периоде обработки запрашивается адресное слово, упомянутая схема исполнителя шины генерирует сигнал запроса адреса на линии сигнала запроса адреса упомянутой шины данных; и

в ответ на упомянутый сигнал запроса адреса, принятый от упомянутой схемы исполнителя шины по упомянутой линии сигнала запроса адреса, упомянутая схема задатчика шины прерывает упомянутую передачу в пакетном режиме и генерирует дополнительное слово адреса в упомянутом следующем периоде обработки.

Сущность изобретения иллюстрируется ссылками на сопровождающие чертежи, в которых:

фиг. 1 схематически представляет устройство для обработки данных с шиной данных, подключенной к нескольким схемным элементам;

фиг. 2 представляет работу устройства в случае различных комбинаций сигналов на шине данных;

фиг. 3 - 5 иллюстрируют схемные части в различных типах исполнителей шины для генерирования шинных сигналов.

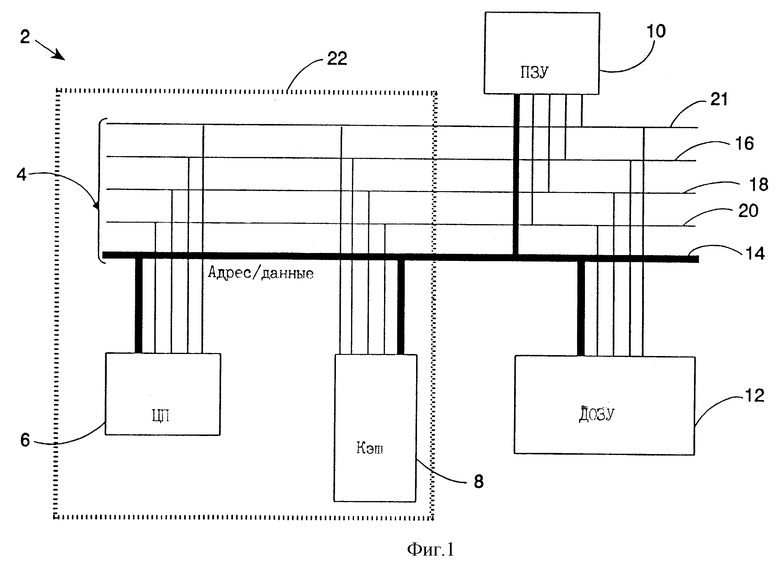

Фиг. 1 представляет устройство 2 обработки данных, содержащее несколько схемных элементов, соединенных между собой шиной 4 данных. Схемные элементы включают в себя центральный процессор (ЦП) (CPU) 6, который функционирует в качестве схемы задатчика шины, кэш 8, постоянное запоминающее устройство (ПЗУ) (ROM) 10 и динамическое оперативное запоминающее устройство (ДОЗУ) (DRAM) 12 с режимом разбивки на страницы, которые функционируют в качестве схем исполнителя шины.

Шина данных 4 содержит 32-разрядную линию 14 сигнала адреса/данных, линию 16 сигнала запроса адреса, линию 18 сигнала запроса периода ожидания, линию 20 сигнала указания адреса или данных и линию 21 сигнала шинной синхронизации. Следует иметь в виду, что шина данных обычно содержит и несколько других сигнальных линий, связанных с управлением, тактированием и другими функциями. Для простоты они не представлены на фиг. 1.

ЦП 6, действующий как схема задатчика шины, и кэш 8, действующий как схема исполнителя шины, изготовлены на единой интегральной схеме 22. Дополнительные схемы исполнителя шины, включающие в себя ПЗУ 10 и ДОЗУ 12, являются внешними для интегральной схемы 22 и подключены к общей шине 4 данных.

В процессе работы ЦП 6 инициирует передачу данных в пакетном режиме путем установки нулевого значения на линии указания сигнала адреса или данных в качестве сигнала B_REQ вместе с указанием соответствующей схемы исполнителя шины и адреса в этой схеме исполнителя шины на 32-разрядной линии 14 сигнала адреса/данных. Адресуемое устройство отвечает выставлением либо 0, либо 1 на линии 18 сигнала запроса периода ожидания в качестве сигнала B_WAIT. Если B_ WAIT равен 0, то это указывает ЦП 6, что он должен продолжить обработку и передавать слово данных в следующем периоде обработки. Если же B_WAIT равен 1, это указывает ЦП 6, что он должен ввести состояние ожидания для следующего периода, пока адресованный исполнитель шины работает с посланным ему адресным словом, и выполнять любую необходимую инициализацию.

Когда схема исполнителя шины индицирует, что она готова к обработке ЦП 6, посылает по линии 14 сигнала адреса/данных последовательность слов данных, относящихся к последовательности адресов в схеме исполнителя шины, начинающейся от заданного начального адреса. Во время этой передачи в пакетном режиме схема исполнителя шины может в любое время выставить единичное значение на линию 18 сигнала запроса периода ожидания и заставить ЦП 6 приостановить передачу в пакетном режиме.

В зависимости от характера соответствующей схемы исполнителя шины может оказаться, что она вообще неспособна поддерживать передачи в пакетном режиме или способа поддерживать передачи в пакетном режиме неполностью. В этом случае она может использовать линию 16 сигнала запроса адреса для установки сигнала B_ AREQ в единичное значение, чтобы заставить ЦП 6 передать слово адреса в следующем периоде обработки. Если значение сигнала B_AREQ равно 1, это позволяет ЦП 6 продолжать транзакцию в пакетном режиме.

В случае проиллюстрированных схем исполнителя шин кэш 8 может быть способен полностью поддерживать передачи в пакетном режиме, ДОЗУ 12 с режимом разбивки на страницы - частично поддерживать передачи в пакетном режиме, а ПЗУ 10 - вообще неспособно поддерживать передачи в пакетном режиме. Таким образом, в случае ПЗУ 10 слово адреса может требоваться для каждого слова данных, считываемого из ПЗУ 10. Кроме того, если ПЗУ представляет собой 8-разрядное устройство, то может потребоваться 4 периода обработки, чтобы ПЗУ 10 ответило на запрос считывания данных из него и скомпоновало 32-пазрядное слово для выставления на 32-разрядной линии 14 сигнала адреса/данных.

В случае ПЗУ 10 передачи данных всегда являются лишь операциями считывания из ПЗУ 10. В случае ДОЗУ 2 и кэша 8 передачи в пакетном режиме могут быть либо от ЦП 6 задатчика шины, либо к ЦП 6 задатчика шины. Это направление управляется дополнительным шинным сигналом B_WRITE (не показан на фиг. 1).

В случае ДОЗУ 12 с режимом разбивки на страницы сигнал запроса адреса должен выставляться, только когда пересекается граница страницы. В случае кэша 8 передачи в пакетном режиме могут полностью поддерживаться безотносительно к их длине, с циклическим возвратом адреса при необходимости.

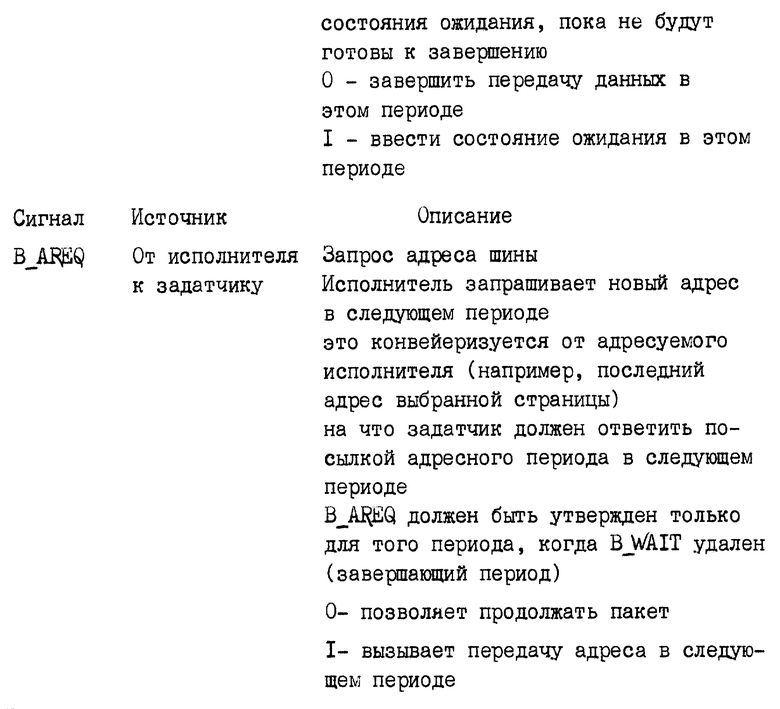

Фиг. 2 показывает таблицу истинности различных откликов системы на разные комбинации сигнала B_AREQ и сигнала B_WAIT. При использовании записи [B_ AREQ : B_WAIT] сигнал [0:0] обозначает, что передача в пакетном режиме может продолжаться, т.е. исполнитель шины способен не отставать от задатчика шины и не требует посылки себе каких-либо дополнительных слов адреса. Комбинация сигналов [0:1] обозначает, что схема исполнителя шины временно неспособна успевать за схемой задатчика шины, и пока пакет может продолжаться без необходимости в дополнительном слове адреса, процессор должен повторять текущий период, чтобы дать схеме исполнителя шины возможности захватить его. Комбинация сигналов [1:0] обозначает, что схема исполнителя шины запрашивает посылку ей дополнительного слова адреса перед тем, как она сможет продолжить обработку, т.е. ДОЗУ 12 находится на границе страницы.

Последняя комбинация [1: 1] является специально назначенным сигналом, который декодируется схемой задатчика шины для прерывания передачи в пакетном режиме. Для того, чтобы не происходило непредусмотренных прерываний передач в пакетном режиме, важно обеспечить такую структуру схем исполнителя шины, чтобы установка сигнала B_ AREQ в единичное значение происходила, только когда сигнал B_ WAIT имеет нулевое значение, пока действительно не потребуется прервать передачу в пакетном режиме. Ситуациями, в которых передача в пакетном режиме может подлежать прерыванию, могут быть такие, в которых шинный мост или повторитель уже включены в какую-то иную операцию и не в состоянии ответить на текущий запрос передачи в пакетном режиме от схемы задатчика шины. Таким образом, чтобы избежать возникающих ситуаций зависания, таким схемам исполнителя шины может придаваться способность выдачи подобной комбинации сигналов повторной трассировки, чтобы заставить задатчик шины прервать передачу в пакетном режиме, как если бы она не имела места, и повторить ее позднее в зависимости от логики более высокого уровня в схеме задатчика шины.

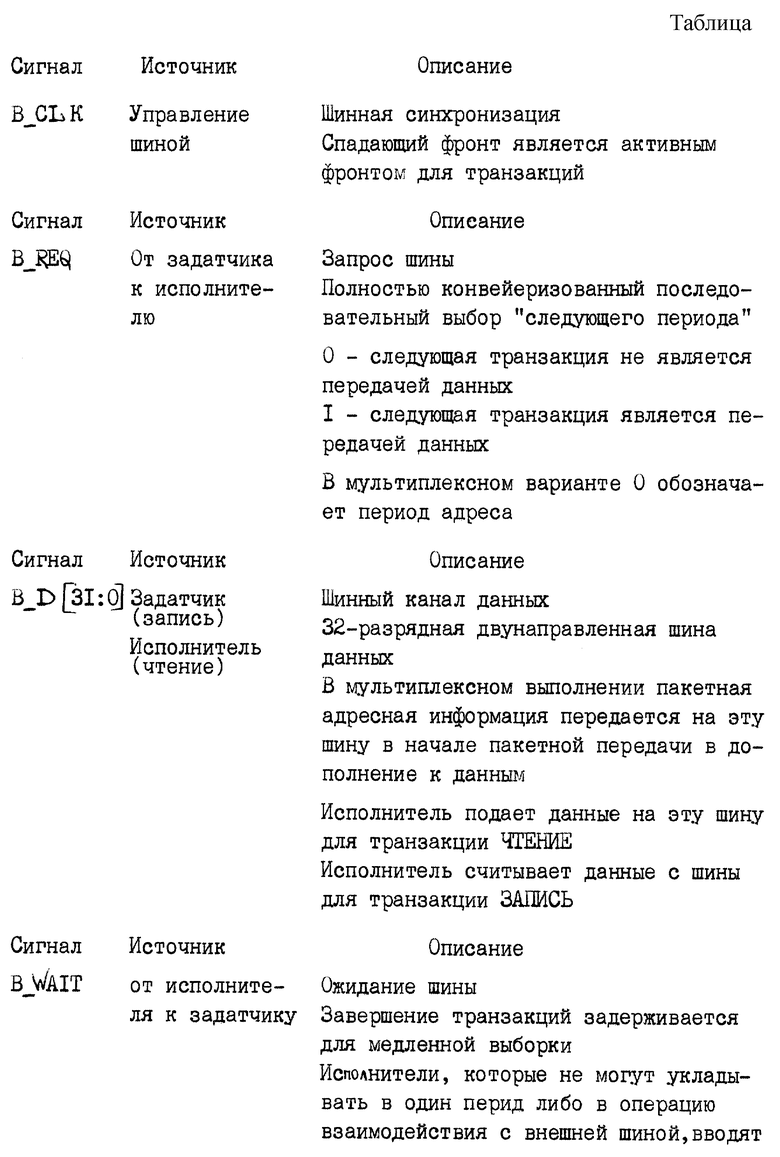

В таблице дан список различных используемых шинных сигналов.

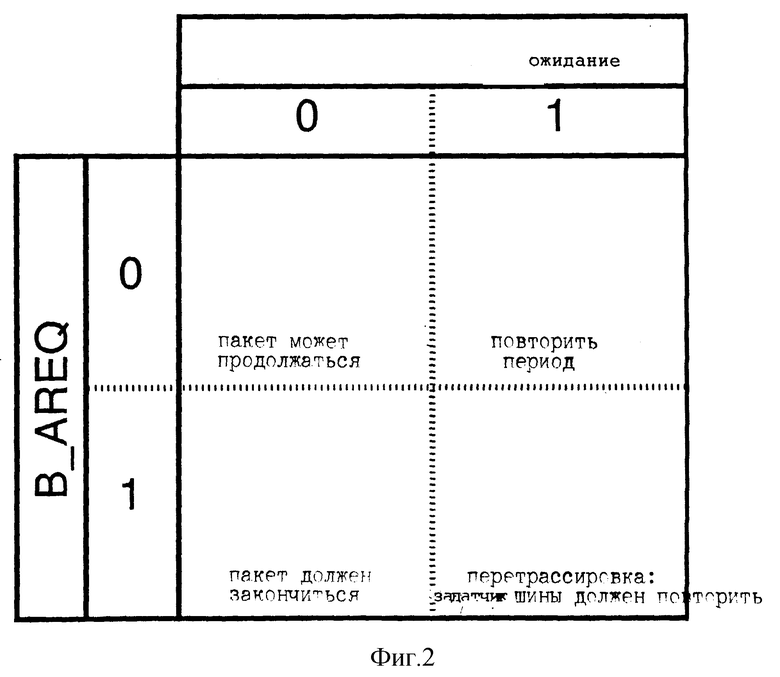

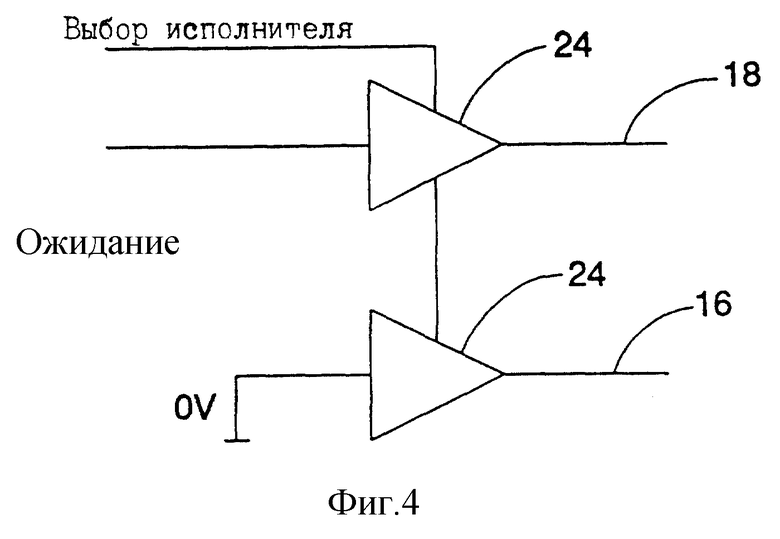

Фиг. 3 представляет схемную часть в простой схеме исполнителя шины, неспособного работать в пакетном режиме. Внутренний для исполнителя шины сигнал "Выбор исполнителя" имеет высокий уровень, когда этот исполнитель шины адресуется задатчиком шины на линии 4. Сигнал "Выбор исполнителя" включает пару буферов 24 с тремя состояниями (высокий импеданс при блокировке), которые возбуждают соответственно линию 16 сигнала запроса адреса и линию 18 сигнала запроса периода ожидания. Другой внутренний для исполнителя шины сигнал "Ожидание" обозначает, затребован ли период ожидания следующего периода. Инвертор служит для того, чтобы гарантировать, что сигналы B_WAIT и B_AREQ не утверждаются вместе этой частью схемы, а также генерирует сигнал запроса адреса для следующего периода путем удаления запроса ожидания каждый раз, когда исполнитель шины принимает слово данных. Таким образом, запроса адреса следует за приемом каждого слова данных в виде, приемлемом для исполнителя шины, неспособного работать в пакетном режиме.

Фиг. 4 иллюстрирует соответствующую часть схемы для исполнителя шины с полной способностью выполнения пакетного режима. В этом случае буфер 24, возбуждающий линию 16 сигнала запроса адреса, имеет на своем входе постоянно приложенное нулевое напряжение, так что сигнал запроса адреса никогда не генерируется этой схемной частью.

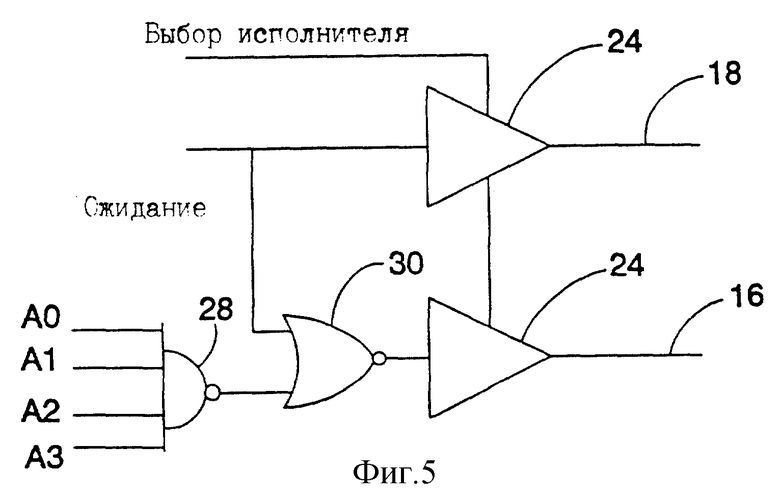

Фиг. 5 иллюстрирует исполнитель шины с частичной способностью выполнять пакетный режим, заключающийся в том, что он запрашивает слово адреса на границе страницы, приходящейся на каждые шестнадцать слов данных. Четыре младших разряда адреса A0, A1, A2 и A3 водятся в четырехвходовый вентиль 28 И-НЕ. По мере увеличения значения адреса эти четыре младших разряда адреса становятся единицами один раз на каждые шестнадцать адресов. Эти четыре единицы имеют место в адресе, предшествующем пересечению границы шестнадцатисловной страницы. Соответственно, появление всех четырех единиц обозначает, что в следующем периоде до того, как могут быть приняты какие-либо еще слова данных, будет запрошено слово адреса. Выход вентиля 28 И-НЕ переходит в 0, когда появляются все четыре единицы.

Выходной сигнал вентиля 28 И-НЕ вместе с внутренним сигналом "Ожидание" вводятся в вентиль 30 ИЛИ-НЕ. Когда сигнал "Ожидание" имеет низкий уровень, обозначающий, что исполнитель способен принять сигналы на линии 14 сигнала адреса/данных в следующем периоде, а выход вентиля 28 И-НЕ равен 0, выход вентиля 30 ИЛИ-НЕ переключится в 1. Этот выходной сигнал вентиля 30 ИЛИ-НЕ проходит через буфер 24 для возбуждения линии 16 сигнала запроса адреса, чтобы указать задатчик шины необходимость послать слово адреса в следующем периоде обработки.

Следующий адрес в последовательности будет иметь все нули для четырех младших разрядов, так что выход вентиля 28 И-НЕ перейдет в 1 сигнал B_AREQ будет равен 0.

Понятно, что исполнитель шины указывает хозяину шины, требуется ли ему слово адреса для следующего периода (B_AREQ), а фактически - готов ли он вообще принять сигналы (B_WAIT). Если задатчик шины закончил свою передачу этому исполнителю, то "Выбор исполнителя" будет снят и выход буфера 24 блокируется.

Вышеописанный вид шинных сигналов вносит симметрию в отношения между задатчиком шины и исполнителями шины. Вместо того, чтобы требовать от задатчика шины способности прогнозировать потребности каждого исполнителя шины в каждом периоде обработки, сами исполнители шины способны указать задатчику шины их потребности в словах адреса или словах данных и периодах ожидания для согласования скоростей обработки, - это является значительным преимуществом.

Данное изобретение относится к вычислительной технике и может быть использовано для обработки данных. Техническим результатом изобретения является увеличение числа передаваемых слов данных, объединенных в пакеты, и снижение времени обработки. Сущность изобретения заключается в том, что устройство для обработки данных содержит общую шину данных для подключения схемы задатчика шины к схемам исполнителя шины, линию сигнала запроса адреса, при этом слово адреса подлежит передаче в следующем периоде обработки вместо слова данных. Исполнители шины могут сами указывать, до каких пределов они способны поддерживать передачи в пакетном режиме и подавать сигнал запроса периода ожидания и комбинацию сигналов, указывающую, что передача в пакетном режиме должна быть полностью прервана. 2 с. и 7 з.п. ф-лы, 5 ил., 1 табл.

| AMITOI et al | |||

| Burst mode memories improve cache design | |||

| IEEE "Wescon conference Record" | |||

| North Hollywood | |||

| Способ приготовления консистентных мазей | 1919 |

|

SU1990A1 |

| Устройство для сопряжения цифровой вычислительной машины с внешними устройствами | 1984 |

|

SU1211743A2 |

| Устройство для сопряжения цифровой вычислительной машины с внешним устройством | 1984 |

|

SU1257656A1 |

| Computer system channel performance enhancement via address boundary release | |||

| IEEE "IBM Technical Disclousure Bulletin" | |||

| New York | |||

| US : IEEE November, 1990, v | |||

| Способ сопряжения брусьев в срубах | 1921 |

|

SU33A1 |

| 1969 |

|

SU348113A1 | |

| 0 |

|

SU278264A1 | |

Авторы

Даты

2000-08-27—Публикация

1994-08-04—Подача