Изобретение относится к устройству обработки данных и способу для доступа к памяти, имеющей множество ячеек памяти для хранения значений данных, и, в частности, к такому устройству и способу обработки данных, который защищаeт доступ к памяти. Термин "значение данных" относится здесь как к командам, так и элементам или блокам данных, к примеру словам данных.

Известно, что для управления доступом к областям памяти выполняют сегментирование памяти на ряд отдельных логических областей и задают атрибуты защиты для каждой из этих областей, при этом атрибуты, к примеру, определяют, являются ли эти области доступными только в режиме супервизора, могут ли они помещаться в кэш-память, являются ли они буферизируемыми в системе на основе кэш-памяти и т.п. Следовательно, если процессор выдает адрес памяти, который попадает в конкретную область памяти, то тогда для этой области могут быть использованы атрибуты защиты, определяющие, имеет ли право процессор в его текущем режиме работы обратиться к этому адресу памяти, и определяющие, могут ли значения данных, выбираемых из этой области памяти, быть помещены в кэш память, можно ли значения данных, записываемые в эту область памяти, буферизировать и т.п. Подобные механизмы защиты часто используются в системах виртуальной памяти вместе с трансляцией виртуальных адресов в физические адреса.

В большинстве реализаций гибкость, предусмотренная для определения логических областей, ограничена. Обычно логические области имеют фиксированный размер, к примеру по 4 Кбайта, хотя при некоторых способах гибкость в некоторой степени повышается, обеспечивая области с несколькими различными размерами, к примеру области размером 1 Кбайт, 2 Кбайта и 4 Кбайта. Обычно, если предусмотрены области с разными размерами, их различие по размеру ограничивается степенями числа два, поскольку аппаратура, необходимая для сравнения адресов для определения логических областей, содержащих эти адреса, оказывается менее сложной, если размеры этих областей различаются только степенью числа два.

Используя вышеописанный подход, можно задать зоны памяти пользователя и зоны памяти супервизора. Рассмотрим, например, случай, в котором предусмотрены логические области с фиксированным размером 4 Кбайта и в системе требуется 4 Кбайта для кода супервизора и 12 Кбайт для кода пользователя, причем оба кода должны быть отображены в ОЗУ с произвольной выборкой объемом 16 Кбайт. Для достижения этой цели должны быть определены четыре логические области, а именно одна область 4 Кбайта для кода супервизора и три области по 4 Кбайта для кода пользователя.

Было бы желательно обеспечить вышеуказанные функциональные возможности, выделяя при этом меньше областей, чем потребовалось бы в вышеописанных известных способах, в результате чего увеличится гибкость системы.

В ЕР-А-0700002 описана схема управления выбором модульного кристалла для микропроцессора. Схема выбора кристалла способна реализовать карту перекрывающейся памяти, так что субблок памяти может либо перекрывать, либо лежать полностью внутри границ основного блока. Для каждого блока памяти используются декодеры, и предусмотрена схема задания приоритета для приема выходных сигналов декодеров и определения на основе механизма приоритетов, следует ли активизировать внешний управляющий сигнал, к примеру сигнал разрешения использования кристалла.

В ЕР-А-0656592 описан блок управления памятью (БУП), имеющий один режим работы, при котором биты атрибута трансляции обеспечиваются либо первым регистром прозрачной трансляции (РПТ), либо вторым РПТ, либо ячейкой по умолчанию. Каждый РПТ может отображать разные адресные пространства и разные размеры адресуемой памяти, а ячейка по умолчанию покрывает всю память, которая не отображается ни одним из РПТ.

В US-A-3827029 описана малогабаритная цифровая компьютерная система, которая сконструирована таким образом, что к ней в качестве факультативной аппаратуры может быть добавлена аппаратная подсистема защиты от нарушения памяти.

Согласно первому аспекту настоящее изобретение обеспечивает устройство обработки данных для управления доступом к памяти, имеющей множество ячеек памяти для хранения значений данных, причем каждая ячейка памяти имеет соответствующий адрес, при этом устройство содержит запоминающее устройство диапазона адресов для хранения информации, идентифицирующей диапазоны адресов для множества логических областей в упомянутой памяти; запоминающее устройство атрибутов для хранения атрибутов для каждой логической области, используемых для управления доступом к ячейкам памяти в логической области; логическая схема компаратора адресов для сравнения адреса, выдаваемого процессором, соответствующего одной из ячеек памяти, с диапазонами адресов для множества логических областей и для генерации сигнала, указывающего те логические области, которые содержат данный адрес, если одна или более логических областей содержат данный адрес; логическая схема определения атрибутов, реагирующая на сигнал, генерируемый логической схемой компаратора адресов, для применения заранее заданных критериев приоритетности, чтобы определить, какая логическая область, содержащая указанный адрес, имеет наивысший приоритет, и вывести атрибуты в запоминающее устройство атрибутов, соответствующее этой области с наивысшим приоритетом, для использования при управлении доступом к ячейке памяти, определенной данным адресом; причем одна из логических областей является фоновой областью, покрывающей всю память, и имеет самый низкий приоритет из всех логических областей, в результате чего, если адрес, выданный процессором, соответствует ячейке памяти, которая находится вне любой из других логических областей, то тогда логическая схема определения атрибутов приспосабливается для вывода атрибутов, связанных с фоновой областью.

В соответствии с настоящим изобретением могут быть определены перекрывающиеся логические области и относительные приоритеты, присваиваемые каждой логической области. Если процессор задает адрес, который попадает в две или более логические области, то тогда для определения того, какая логическая область имеет наивысший приоритет, используются критерии приоритетности. Каждая логическая область имеет ряд атрибутов, заданных для этой области, которые используются для управления доступом к ячейкам памяти в этой логической области. Затем на основе определения области, имеющей наивысший приоритет, атрибуты для области с наивысшим приоритетом используются для управления доступом к конкретной ячейке памяти, заданной процессором.

Следовательно, если обратиться к вышеупомянутому примеру, где было необходимо обеспечить 4 Кбайта для кода супервизора и 12 Кбайт для кода пользователя в ОЗУ объемом 16 Кбайт, то согласно настоящему изобретению это можно достичь, обеспечив две перекрывающиеся области: область 4 Кбайта для кода супервизора и область 16 Кбайт для кода пользователя. Область супервизора задается с более высоким приоритетом, чем область пользователя, обеспечивая тем самым то, что любая попытка доступа к перекрывающейся области 4 Кбайта регулируется атрибутами, связанными с областью супервизора. Следовательно, согласно настоящему изобретению в этом примере должны быть определены только две области, а не четыре области, как это требуется в соответствии с известными способами.

В предпочтительных вариантах одна из логических областей может быть использована в качестве фоновой области, покрывающей всю память и имеющей самый низкий приоритет из всех логических областей, в результате чего, если адрес, выданный процессором, соответствует ячейке памяти, находящейся вне любой другой логической области, то тогда для управления доступом к ячейке памяти, заданной этим адресом, используются атрибуты, связанные с фоновой областью.

Возможно, что определенные области памяти не полностью заполняют адресное пространство памяти, и, следовательно, в карте отображения адресов появятся "дырки". Однако путем подбора конфигурации области с самым низким приоритетом для покрытия всего диапазона адресов памяти и задания соответствующих атрибутов для этой логической области памяти можно определить, что будет происходить при обращении к "дырке" (например, могут быть установлены атрибуты для полного доступа либо отсутствия доступа).

В предпочтительных вариантах диапазоны адресов для логических областей задаются базовым адресом, определяющим, с какой ячейки памяти начинается область, и атрибутом размера, определяющим размер логической области. В предпочтительных вариантах базовый адрес определяется как функция атрибута размера, так что область памяти с размером Х должна иметь базовый адрес, кратный значению X. Такой подход позволяет упростить требования к аппаратурным средствам. Базовый адрес и атрибут размера обычно программируются пользователем. В качестве альтернативы использования базового адреса и атрибута размера диапазоны адресов логических областей могут быть заданы начальным адресом и конечным адресом, определяющими начало и конец логической области.

Логическая схема компаратора адресов может быть выполнена любым подходящим способом. В предпочтительных вариантах логическая схема компаратора адресов содержит ряд компараторов, по одному для каждого диапазона адресов.

Запоминающее устройство диапазона адресов может быть обеспечено с помощью любого походящего запоминающего устройства. Однако в предпочтительных вариантах запоминающее устройство диапазона адресов содержит ряд регистров. Предпочтительно, чтобы отдельные регистры были связаны с каждым компаратором логической схемы компараторов адресов.

Запоминающее устройство атрибутов может иметь любой подходящий вид. Однако в предпочтительных вариантах запоминающее устройство атрибутов содержит множество регистров атрибутов, подсоединенных к мультиплексору, причем каждый регистр содержит атрибуты для логической области, логическая схема определения атрибутов выдает сигнал в мультиплексор, заставляя мультиплексор выводить атрибуты из регистра атрибутов, соответствующего области с наивысшим приоритетом, содержащей упомянутый адрес.

В предпочтительных вариантах логическая схема компаратора адресов имеет множество выходов, причем для каждой логической области предусмотрен один выход, и на этих выходах генерируется сигнал, указывающий, содержит ли соответствующая логическая область данный адрес, при этом логическая схема определения атрибутов имеет соответствующее множество входов для приема сигналов от указанного множества выходов, и это множество входов имеет относительные приоритеты, используемые логической схемой определения атрибутов для применения заранее заданных критериев приоритетности.

Однако весьма ценным является то, что для применения заранее заданных критериев приоритетности могут быть использованы альтернативные способы. Например, в запоминающем устройстве, доступном со стороны логической схемы определения атрибутов, в качестве информации о приоритетах могут храниться заранее заданные критерии приоритетности, причем информация о приоритетах определяет относительные приоритеты упомянутых логических областей.

В предпочтительных вариантах устройство обработки данных дополнительно содержит процессорное ядро для выдачи адресов, соответствующих ячейкам в памяти, где хранятся значения данных, необходимые процессору, либо должны храниться значения данных, обрабатываемые процессорным ядром. Кроме того, схема обработки данных может содержать кэш-память для хранения значений данных, доступных процессорному ядру. При таком устройстве для повышения эффективности определение атрибутов для области с наивысшим приоритетом предпочтительно выполнять одновременно с просмотром кэш-памяти.

Для хранения как команд, так и данных может быть предусмотрена единая кэш-память, причем она часто относится к кэш-памяти с архитектурой фон Неймана. Однако в качестве альтернативного варианта для хранения команд может быть предусмотрена первая кэш-память, а для хранения данных предусмотрена вторая кэш-память, причем такого рода кэш-память часто относится к кэш-памяти с архитектурой Гарварда; при этом упомянутая логическая схема компаратора адресов и упомянутая логическая схема определения атрибутов дублируются для каждой из первой и второй кэш-памяти. Следовательно, при использовании отдельных кэш-памятей для данных и команд элементы схемы обработки данных, необходимой для определения атрибутов, которые используются для управления доступом к памяти, предпочтительно дублируются для каждой кэш-памяти. Как упоминалось ранее, определение атрибутов для области с наивысшим приоритетом предпочтительно выполняется одновременно с просмотром кэш-памяти. Если имеются две кэш-памяти, то операция просмотра в кэш-памяти данных может происходить одновременно с операцией просмотра в кэш-памяти команд, и, следовательно, для определения атрибутов, используемых для доступа к адресам памяти, соответствующим операциям просмотра как в кэш-памяти команд, так и в кэш-памяти данных, потребуется два набора схем.

Согласно второму аспекту настоящее изобретение обеспечивает способ работы устройства обработки данных для управления доступом к памяти, имеющей множество ячеек памяти для хранения значений данных, причем каждая ячейка памяти имеет соответствующий адрес, при этом способ содержит следующие шаги: (а) хранение информации, идентифицирующей диапазоны адресов для множества логических областей в памяти; (б) хранение для каждой логической области атрибутов, используемых для управления доступом к ячейкам памяти в логической области; (в) сравнение адреса, выданного процессором, соответствующего одной из ячеек памяти, с диапазоном адресов для множества логических областей; (г) генерация сигнала, указывающего те логические области, которые содержат упомянутый адрес, если упомянутый адрес содержат одна или более логических областей; (д) применение, в соответствии с сигналом, генерируемым на шаге (г), заранее заданных критериев приоритетности для определения того, какая логическая область, содержащая упомянутый адрес, имеет наивысший приоритет; и (е) вывод хранящихся атрибутов, соответствующих области с наивысшим приоритетом, для использования при управлении доступом к ячейке памяти, заданной данным адресом; в котором одна из логических областей является фоновой областью, покрывающей всю память и имеющей самый низкий приоритет из всех логических областей, в результате чего, если сигнал, генерируемый на шаге (г), указывает, что адрес, выданный процессором, соответствует ячейке памяти, находящейся вне любых других логических областей, то на шаге (e) выводятся хранящиеся атрибуты, связанные с фоновой областью.

Далее только в качестве примера описывается вариант осуществления изобретения со ссылками на сопроводительные чертежи, на которых для одинаковых признаков используются одинаковые ссылочные обозначения и где

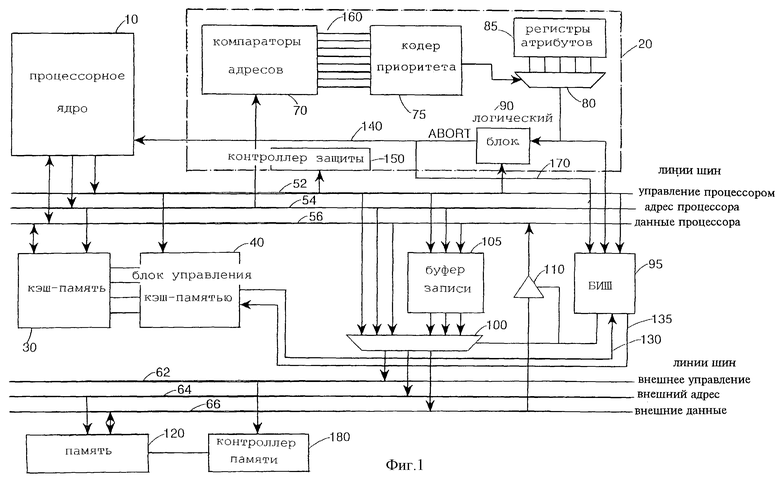

фиг. 1 - блок-схема, иллюстрирующая устройство обработки данных согласно предпочтительному варианту настоящего изобретения;

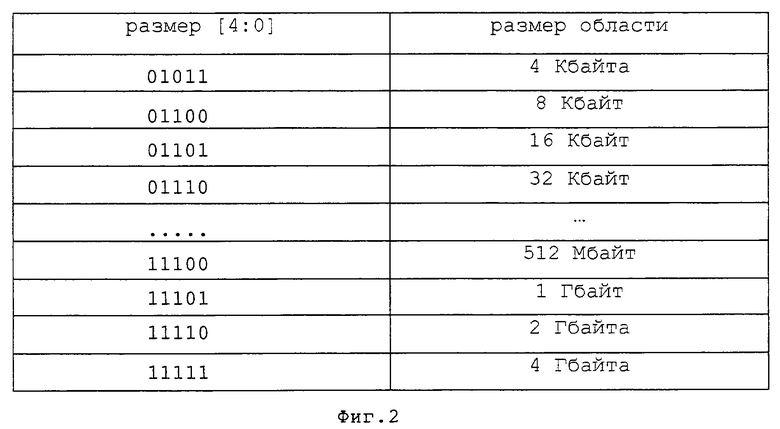

фиг.2 - таблица, показывающая, каким образом с помощью поля размером пять бит могут быть заданы логические области с разным размером памяти согласно предпочтительным вариантам настоящего изобретения;

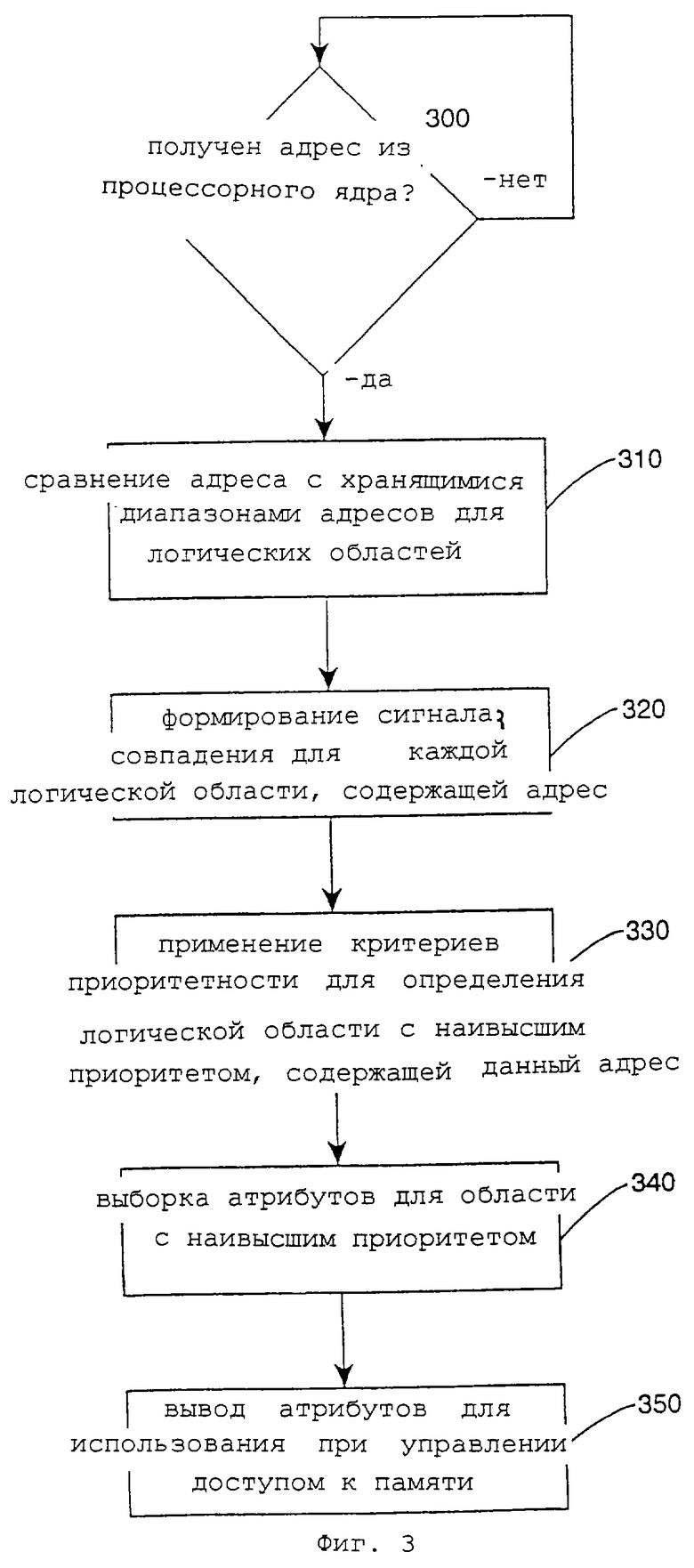

фиг. 3 - блок-схема, иллюстрирующая шаги обработки, выполняемые согласно предпочтительным вариантам настоящего изобретения с целью определения атрибутов, используемых для управления доступом к памяти; и

фиг. 4А, 4В - варианты настоящего изобретения, в которых используются отдельные кэш-памяти для данных и команд.

Устройство обработки данных согласно предпочтительному варианту настоящего изобретения описывается со ссылками на блок-схему по фиг.1. Как показано на фиг. 1, схема обработки данных имеет процессорное ядро 10, установленное для обработки команд, получаемых из памяти 120. Данные, необходимые процессорному ядру 10 для выполнения этих команд, также могут быть выбраны из памяти 120. Для хранения данных и команд, выбираемых из памяти 120, предусмотрена кэш-память 30, так что она фактически легко доступна процессорному ядру 10. Для управления запоминанием команд и данных в кэш-памяти 30 и для управления выборкой данных и команд из этой кэш-памяти предусмотрен также блок управления кэш-памятью 40.

Согласно предпочтительным вариантам настоящего изобретения в памяти 120 может быть определено множество логических областей, причем каждая логическая область имеет независимо программируемый размер. Для описания предпочтительного варианта рассматривается память 120, имеющая 4 Гбайта адресного пространства, и предполагается, что в этом адресном пространстве памяти может быть определено 8 логических областей. Специалистам в данной области техники очевидно, что действительный размер памяти и количество определяемых логических областей может варьироваться, чтобы удовлетворить конкретным требованиям схемы обработки данных.

Каждая логическая область предпочтительно определяется базовым адресом, который задает начало области в памяти, и полем размера, определяющим размер этой логической области. Для того чтобы упростить требования к аппаратуре компараторов в блоке защиты (блок защиты более подробно обсуждается ниже), вкладывается ограничение, состоящее в том, что базовый адрес должен соответствовать границе "размера". Следовательно, к примеру, логическая область размером 1 Мбайт будет установлена, начиная с базового адреса, соответствующего границе 1 Мбайт в памяти. Специалистам в данной области техники очевидно, что это ограничение, накладываемое на базовый адрес в предпочтительных вариантах, несущественно, и что, предусмотрев более сложные аппаратные средства в блоке защиты, можно будет иметь возможность начинать базовый адрес с ячейки памяти, отличной от границы размера.

Согласно предпочтительным вариантам размер логической области может выбираться в диапазоне от 4 Кбайт до 4 Гбайт. Однако очевидно, что этот диапазон выбора может быть при желании изменен. На фиг.2 представлена таблица, показывающая, каким образом может быть запрограммирован регистр размера, имеющий поле 5 бит, для различных размеров памяти. В примере, показанном на фиг.2, размер может варьироваться, отличаясь на величину степеней числа два. Однако специалистам в данной области техники очевидно, что нет необходимости ограничивать изменение размера степенями числа два, и, предусмотрев регистр размера с большим количеством бит, можно обеспечить дополнительную гибкость при программировании размера каждой области.

В качестве альтернативы использования регистров базы и размера для определения логических областей также могут быть использованы регистры начала и конца. В таких случаях информация, соответствующая действительным адресам начала и конца каждой логической области, хранится в регистрах, а не в базовом адресе и размере области.

Имея возможность определять логические области с использованием либо регистров базы и размера, либо регистров начала и конца, как обсуждалось выше, пользователь может запрограммировать в памяти перекрывающиеся логические области. В предпочтительных вариантах настоящего изобретения каждая логическая область имеет независимые атрибуты, такие как связанные с данной областью атрибуты защиты, атрибуты, указывающие на возможность помещения в кэш-память и возможность буферизации. Если имеется возможность перекрытия логических областей, несомненно, важно, чтобы любое обращение к памяти обрабатывалось предсказуемым образом. В предпочтительных вариантах это достигается путем использования блока защиты 20, показанного на фиг.1, и далее более подробно обсуждается работа этого блока защиты.

Когда процессорное ядро 10 запрашивает команду или элемент данных (здесь как команды, так и данные называются значениями данных), он помещает адрес памяти значения данных на линию 54 процессорной шины 50. Кроме того, процессорное ядро 10 выдает процессорный сигнал управления на линию шины 52. Процессорный сигнал управления содержит информацию, к примеру, соответствует ли адрес запросу на считывание или запись, тип доступа (например, последовательный), размер доступа (например, слово, байт), рабочий режим процессора (например, режим супервизора или режим пользователя) и т.п. Этот процессорный сигнал управления принимается блоком управления кэш-памятью 40 и приглашает этот блок управления кэш-памятью определить, хранится ли требуемое значение данных в кэш-памяти 30. Блок управления кэш-памятью 40 дает команду кэш-памяти 30 сравнить адрес на линии шины 54 с адресом в кэш-памяти, чтобы определить, хранится ли в кэш-памяти значение данных, соответствующее этому адресу. Если это так, то значение данных выводится из кэш-памяти 30 на линию шины данных 56, где оно затем считывается процессорным ядром 10. Если значения данных, соответствующего этому адресу, нет в кэш-памяти 30, то тогда блок управления кэш-памятью 40 посылает по линии 130 сигнал в блок интерфейса шины 95, указывая, что значение данных должно быть выбрано из памяти 120.

Одновременно с процессом просмотра кэш-памяти контроллер защиты 150 в блоке зашиты 20 также получает процессорный сигнал управления по линии шины 52 и, определив, что процессорный сигнал управления относится к потенциальному доступу для считывания или записи в память 120 или кэш-память 30, дает команду компараторам адресов 70 проверить адрес, помещенный процессорным ядром 10 на линию шины 54. В предпочтительных вариантах для каждой логической области имеется один компаратор адресов, и каждый из компараторов имеет соответствующий регистр, содержащий диапазон адресов для конкретной логической области. Каждый компаратор приспособлен для сравнения этого диапазона адресов с конкретным адресом на линии шины 54, чтобы определить, содержится ли адрес в соответствующей логической области. Всякий раз, когда компаратор определяет, что адрес находится в диапазоне адресов логической области, он по соответствующей линии 160 выводит на кодер приоритета 75 сигнал совпадения.

Кодер приоритета 75 получает сигналы, выводимые всеми компараторами 70. Если кодер приоритета получает один сигнал совпадения, то это указывает на то, что данный адрес находится только в одной логической области. В таком случае кодер приоритета 75 посылает в мультиплексор 80 сигнал, дающий команду мультиплексору 80 выбрать среди регистров атрибутов 85 атрибуты, соответствующие этой логической области. Затем эти атрибуты используются для управления доступом к памяти 120, либо для использования значения данных, выбираемых из кэш-памяти 30. В предпочтительных вариантах будет всегда генерироваться по меньшей мере один сигнал совпадения, поскольку одна из логических областей является фоновой областью, покрывающей все адресное пространство памяти 120. Однако определение фоновой области не является существенным, и, следовательно, в альтернативных вариантах возможна ситуация, когда компараторы адресов 70 не генерируют сигналы совпадения. В этом случае кодер приоритета 75 приспосабливается для получения сигнала, указывающего на то, что совпадения не были обнаружены, и этот сигнал будет выводиться из кодера приоритета 75 в логическую схему 90. То, каким образом схема обработки данных действует в этом случае, будет зависеть от того, как приспособлена действовать логическая схема 90. Например, эта логическая схема может быть приспособлена действовать так, что любая попытка доступа к адресу, не содержащемуся в какой-либо из логических областей, приведет к сигналу преждевременного прекращения, который направляется обратно в процессорное ядро 10 по линии 140.

Если предположить, что компараторы адресов 70 выдают более одного сигнала совпадения, то тогда кодер приоритета 75 приспосабливается для применения критериев приоритетности с целью определения относительных приоритетов каждой из определенных логических областей. Информация о приоритете, относящаяся к каждой логической области, может храниться в блоке защиты 20, и для каждой логической области, для которой компараторы адресов сформировали сигнал совпадения, кодер приоритета может быть приспособлен действовать так, чтобы использовать соответствующую информацию о приоритете для определения того, какая логическая область имеет наивысший приоритет.

Однако в предпочтительных вариантах относительные приоритеты логических областей определяются путем упорядочения входов в кодере приоритета 75. Если имеется восемь компараторов адресов 70 (компараторы 0-7), соответствующих восьми логическим областям (логические области 0-7), то тогда предпочтительно иметь восемь соответствующих проводов 160, подсоединенных к восьми входам (входы 0-7) кодера приоритета 75. Тогда входам, соответствующим логическим областям, могут быть присвоены приоритеты таким образом, что приоритет возрастает вместе с номером входа, то есть, номер входа 7 имеет наивысший приоритет, а номер входа 0 имеет самый низкий приоритет.

Тогда кодер приоритета приспосабливается для применения условной логики, определяющей сначала, получен ли сигнал совпадения на номере входа 1, соответствующем логической области 7. Если это так, то тогда из кодера приоритета 75 на мультиплексор 80 выводится сигнал, указывающий, что из регистров атрибутов 85 следует выводить атрибуты для логической области 7. Если сигнал совпадения на входе, соответствующем логической области 7, не получен, то тогда кодер приоритета 75 определяет, получен ли сигнал совпадения на номере входа 6, соответствующем логической области 6. Если это так, то тогда из кодера приоритета 75 в мультиплексор 80 выводится сигнал, указывающий, что из регистров атрибутов 85 следует вывести атрибуты для логической области 6. Если на входе, соответствующем логической области 6, сигнал совпадения не принят, то тогда аналогичный процесс повторяется для каждого входа по очереди, пока не будет найден вход с сигналом совпадения. Очевидно, что, хотя приведенное выше описание определяет процесс в логических терминах, действительный процесс обычно не будет выполняться последовательно, как это описано, а вместо этого могут быть предусмотрены подходящие логические схемы для приема всех восьми входных сигналов вместе и генерации выходного сигнала, идентифицирующего область с наивысшим приоритетом.

В предпочтительных вариантах сигнал совпадения всегда будет иметь место в области с самым низким приоритетом (область 0), поскольку она устанавливается как фоновая область, покрывающая адресное пространство памяти в целом. Следовательно, процесс обработки, выполняемой кодером приоритета 75, приведет к тому, что на мультиплексор 80 будет послан сигнал, указывающий этому мультиплексору выбрать из регистров атрибутов 85 атрибуты, соответствующие области с наивысшим приоритетом, содержащей адрес, выданный процессорным ядром 10. Затем атрибуты, выданные мультиплексором 80, поступают в логический блок 90 и блок интерфейса шины 95. Логический блок 90 получает также из линии шины 52 процессорный сигнал управления. Этот процессорный сигнал управления наряду с прочим определяет режим работы процессорного ядра 10. Следовательно, логический блок 90 может использовать эту информацию, чтобы определить, разрешают ли атрибуты, выведенные мультиплексором 80, процессорному ядру 10 в его текущем режиме работы иметь доступ к запрашиваемому адресу памяти. Например, если логический блок 90 определяет, что процессорное ядро 10 находится в режиме пользователя, а атрибуты, выводимые мультиплексором 80, указывают, что данный адрес памяти может быть доступен только в режиме супервизора, то тогда логический блок 90 может быть приспособлен для формирования сигнала преждевременного прекращения по тракту 140 к процессорному ядру 10 и по тракту 170 к блоку интерфейса шины 95.

Процесс обработки, выполняемый блоком защиты 20, предпочтительно происходит в то же самое время, что и просмотр кэш-памяти, с тем, чтобы поддерживать достаточную скорость обработки. Если запрашиваемое значение данных имеется в кэш-памяти 30 и логический блок 90 не формирует на линии 140 сигнал преждевременного прекращения, то тогда процессорное ядро 10 будет использовать данные, выбираемые из кэш-памяти 30. Однако, если запрашиваемое значение данных не имеется в кэш-памяти, то тогда, как обсуждалось ранее, по тракту 130 будет послан сигнал, дающий команду блоку интерфейса шины (БИШ) 95 обратиться к памяти 120 за этим значением данных.

БИШ 95 проверит процессорный сигнал управления на линии шины 52, чтобы определить, является ли команда, выданная процессорным ядром 10, командой считывания или командой записи. Если предположить, что это команда считывания и что по тракту 170 из логического блока 90 не принят сигнал преждевременного прекращения, то тогда БИШ 95 даст команду мультиплексору 100 послать адрес с линии шины 54 на линию внешней шины адресов 64 шины 60 (здесь предполагается, что команды записи в память 120 не задерживаются в буфере записи 105 - если же какие-либо команды задержки записи имеются, то они будут завершены до команды считывания. Действие буфера записи более подробно обсуждается ниже). На линии шины 62 также имеется сигнал управления, который используется контроллером памяти 180 для управления доступом к памяти 120. Контроллер памяти 180, исходя из сигнала управления на линии шины 62, определяет, что требуется считывание из памяти, и дает команду памяти вывести по линии шины данных 66 данные с адресом, указанным в линии шины адресов 64.

БИШ 95 посылает сигнал в буфер 110, заставляя буфер 110 послать данные, помещенные памятью 120 на линии внешней шины 66, в линию шины процессора 56. Вдобавок, если атрибуты, полученные БИШ 95 от мультиплексора 80 блока защиты 20, указывают, что адрес содержит значение данных, которое можно помещать в кэш-память, то тогда БИШ 95 пошлет по тракту 135 в блок управления кэш-памятью 40 сигнал, который дает команду блоку управления кэш-памятью запомнить выбранное значение данных в кэш-памяти 30. Значение данных, выбранное из памяти 120 и помещенное в линию шины 56, запоминается затем в кэш-памяти 30 и также поступает в процессорное ядро 10. В результате это значение данных становится легкодоступным со стороны процессорного ядра 10 непосредственно из кэш-памяти. Если атрибуты, полученные БИШ 95, указывают, что значение данных не может быть помещено в кэш-память, то тогда данные не будут запоминаться в кэш-памяти, и процессорное ядро 10 будет считывать значение данных с линии шины 56.

В вышеприведенном описании было показано, как используется блок защиты 20 для управления доступом к памяти 120 для считывания значений данных из памяти 120. В случае, когда адрес, выдаваемый процессорным ядром 10, представляет собой адрес, по которому процессор хочет записать значение данных, имеет место следующая процедура.

Процессорное ядро выдаст процессорный сигнал управления на линию шины 52, адрес - на линию шины 54, а значение данных, подлежащее запоминанию, - на линию шины 56. Контроллер защиты 150 в блоке защиты 20 произведет оценку процессорного сигнала управления на линии шины 52 и, определив, что процессорный сигнал управления имеет отношение к доступу к памяти 120 для записи, даст команду компараторам адресов 70 проверить адрес, помещенный процессорным ядром 10 на линии шины 54. Затем блок защиты выполнит ту же процедуру, которая была описана ранее в связи с командой считывания, для того, чтобы определить логическую область с наивысшим приоритетом, которая содержит этот адрес. Это приведет к тому, что атрибуты, соответствующие этой области, буду выведены в БИШ 95 и в логический блок 90.

БИШ 95 произведет оценку процессорного сигнала управления на линии шины 52, чтобы определить, является ли команда, выданная процессорным ядром 10, командой считывания или командой записи. Если предположить, что это команда записи, то БИШ определит, что должна быть выполнена процедура записи, и использует информацию об атрибутах, принятую от блока защиты 20, для управления процедурой записи.

Логический блок 90 по атрибутам, выведенным мультиплексором 80, и по процессорному сигналу управления определит, может ли процессорное ядро выполнить запись по конкретному адресу в его текущем режиме работы, и если нет, то выдаст сигнал преждевременного прекращения. Любой сигнал преждевременного прекращения посылается в БИШ 95 по тракту 170, давая ему команду игнорировать команду записи, а также посылается по тракту 140 в процессорное ядро 10, чтобы вызвать удаление информации о данных, адресах и управлении соответственно с линий шины 56, 54 и 52 и разрешить процессорному ядру 10 выполнить процедуру исключения, необходимую в случае такого преждевременного прекращения.

Однако, если предположить, процессорному ядру дано право записи до адресу, имеющемуся на линии шины 54, и, следовательно, БИШ 95 не получает сигнал преждевременного прекращения, то тогда БИШ 95 использует информацию об атрибутах от мультиплексора 80, чтобы определить, можно или нет буферизировать данные, подлежащие записи. Если эти данные буферизировать можно, то тогда БИШ 95 даст команду буферу записи 105 выбрать сигналы данных, адреса и управления с шины 50. Как только это будет выполнено, процессорное ядро 10 может обрабатывать следующую команду, не ожидая завершения команды записи.

Буфер записи предпочтительно является буфером типа "первым пришел - первым обслужен". Если внешняя шина 60 свободна, то БИШ 95 дает команду мультиплексору 100 вывести следующий элемент из буфера записи на внешнюю шину 60. Затем мультиплексор 100 выводит необходимые сигналы управления, адреса и данных на линии шины 62, 64 и 66 соответственно, причем контроллер памяти 180 использует сигнал управления для управления доступом для записи в память 120. В этот момент данные будут записаны в памяти 120. Когда данные, подлежащие записи, последовательно обрабатываются из буфера записи 105, то в это же самое время в памяти 120 будут записываться данные, соответствующие адресу, выданному процессором по линии шины 54.

Однако, если блок интерфейса шины 95 определит, что адрес, по которому должны быть записаны данные, не является буферизируемым, то тогда блок интерфейса шины 95 даст команду мультиплексору 100 выбрать информацию о процессорном управлении, адресе и данных непосредственно из линий шины 52, 54 и 56. Затем мультиплексор 100 выводит эту информацию на внешнюю шину 60, вызывая запись данных по соответствующему адресу в памяти 120. Однако, прежде чем это сделать, буфер записи 105 обычно освобождается от каких-либо записей в нем, с тем чтобы обеспечить обработку команд записи в правильном порядке. Как только будут записаны небуферизируемые данные, соответствующие текущей команде записи, может обрабатываться следующая команда.

Теперь со ссылками на фиг.3, где представлена блок-схема, показывающая шаги обработки, выполняемые в блоке защиты 20, будет рассмотрен процесс, выполняемый этим блоком защиты. На шаге 300 блок защиты 20 ожидает адрес, помещаемый процессорным ядром 10 на линию шины адресов 54. Как упоминалось ранее, контроллер защиты 150 в блоке защиты 20 реагирует на сигнал управления на шине PC 52, давая команду компараторам адресов 70 проверить адрес, помещенный процессорным ядром 10 на линии шины 54. В предпочтительных вариантах для каждой логической области предусматривается один компаратор адресов, и, следовательно, в предпочтительных вариантах в блоке компараторов адресов 70 имеется восемь компараторов адресов. Каждый компаратор адресов имеет соответствующий адресный регистр, содержащий диапазон адресов для соответствующей логической области. Адрес, полученный по линии адресов 54, сравнивается на шаге 310 с диапазоном адресов в соответствующем регистре, и если адрес лежит в этом диапазоне адресов, то на шаге 320 этот адресный компаратор выводит сигнал "совпадения" по соответствующему проводу 160.

Все сигналы, генерируемые компараторами адресов 70, проходят в кодер приоритета 75, где на шаге 330 применяются критерии приоритетности, чтобы определить логическую область, содержащую адрес, которая имеет наивысший приоритет. Как упоминалось ранее, в предпочтительных вариантах это выполняется путем того, что кодер приоритета настраивается на выполнение условных логических операций, определяя сначала, был ли принят сигнал совпадения на входе, соответствующем области с наивысшим приоритетом. Если этот сигнал не был принят, то тогда проверятся вход, соответствующий области со следующим высшим приоритетом, и так далее, пока не будет идентифицирован сигнал совпадения. Поскольку кодер приоритета 75 осуществляет логическую проверку входов в порядке убывания приоритета, первый идентифицированный сигнал совпадения будет соответствовать логической области с наивысшим приоритетом, которая содержит адрес, выданный процессорным ядром 10. Очевидно, что этот процесс нет необходимости выполнять последовательно по одному входу за раз, и в предпочтительных вариантах могут быть использованы подходящие логические схемы для приема всех восьми входных сигналов вместе и генерации выходного сигнала, идентифицирующего область с наивысшим приоритетом.

В предпочтительных вариантах всегда будет по меньшей мере один сигнал совпадения, поскольку либо все адресное пространство будет покрыто различными логическими областями, либо одна из логических областей будет являться фоновой областью, покрывающей все адресное пространство памяти 120. Однако определять фоновую логическую область нет необходимости, и, следовательно, есть возможность не формировать сигналы совпадения, что указывает на то, что адрес, выданный процессорным ядром 10, соответствует "дырке" в памяти 120. В таких случаях, при отсутствии фоновой области, система обычно снабжается аппаратными средствами, определяющими обработку доступа к дыркам; например, может быть устроено так, что любой доступ к дырке будет приводить к генерации логическим блоком 90 сигнала преждевременного прекращения. С другой стороны, если логическая фоновая область определена, то тогда на это полагаться нет необходимости, поскольку для управления доступом будут использоваться атрибуты, соответствующие этой фоновой области.

Если предположить, что фоновая область должна быть определена как область с самым низким приоритетом, эта фоновая область может быть выполнена с фиксированным монтажом так, что она будет покрывать все адресное пространство. Тогда эта область с самым низким приоритетом может быть исключена из процесса сравнения, выполняемого компараторами адресов 70, в результате чего уменьшается на единицу количество компараторов и проводов 160 к кодеру приоритета 75. Если компараторы адресов 70 не генерируют сигналы совпадения, указывая тем самым, что ни одна из логических областей не содержит упомянутый адрес, то тогда кодер приоритета 75 может быть приспособлен для посылки сигнала в мультиплексор 80, чтобы дать ему команду вывести атрибуты, связанные с областью самого низкого уровня. Такой подход может повысить эффективность, хотя при этом несколько уменьшается гибкость, поскольку компараторы адресов не сравнивают адрес с диапазонам адресов для области с самым низким приоритетом, при этом атрибуты для этой области с самым низким приоритетом используются в виде прямой последовательности компараторов адресов, определяющих, что ни одна из логических областей не содержит упомянутый адрес.

Как только кодер приоритета 75 определит, какая логическая область, содержащая данный адрес, имеет наивысший приоритет, то тогда он выводит в мультиплексор 80 сигнал, давая команду мультиплексору выбрать на шаге 340 атрибуты из регистра атрибутов 85, содержащего атрибуты для этой логической области. Как только атрибуты будут выбраны мультиплексором 80, эти атрибуты выводятся на шаге 350 для использования при управлении доступом к памяти или к кэш-памяти.

В предпочтительных вариантах логическим блоком 90 выполняется окончательная проверка, чтобы определить, указывают ли атрибуты, выводимые на шаге 350, что процессорное ядро 10 в его текущем режиме работы не должно иметь доступ к данному адресу памяти в логической области, определенной этими атрибутами. Например, если процессорное ядро 10 работает в режиме пользователя и один из атрибутов, выводимых на шаге 370, указывает, что адрес является доступным только в режиме супервизора, то логический блок 90 выдаст по тракту 140 в процессорное ядро 10 сигнал преждевременного прекращения, указывая на то, что процессорное ядро 10 не может получить доступ к этой области памяти, а также пошлет по тракту 170 в БИШ 95 сигнал преждевременного прекращения.

В вышеприведенном описании обсуждалось устройство обработки данных, в котором можно определить множество логических областей памяти и в котором эти логические области памяти могут перекрываться, чтобы повысить гибкость устройства.

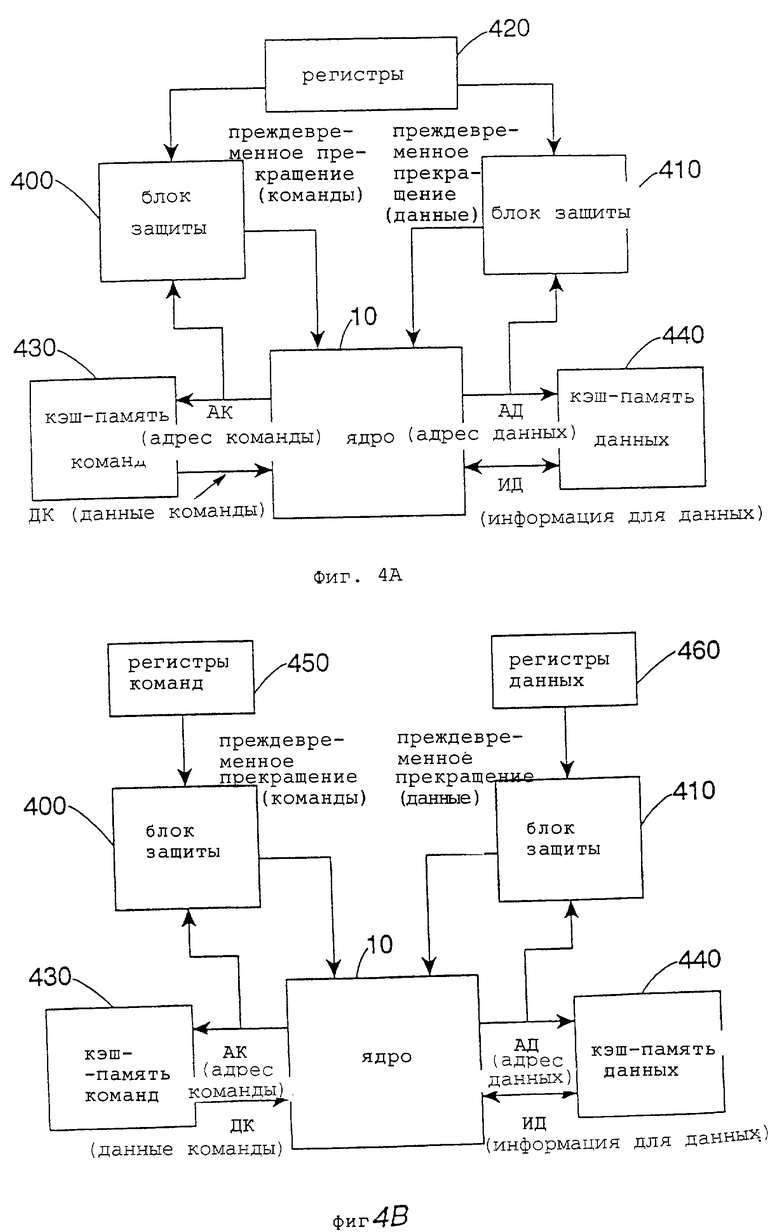

Хотя здесь обсуждался конкретный вариант, очевидно, что изобретение к нему не сводится и что в рамках объема изобретения может быть выполнено множество его модификаций и дополнений. Например, кэш-память 30 может быть использована для хранения как команд, так и данных, как это показано на фиг. 1, либо, как вариант, одна кэш-память может быть использована для хранения команд, а отдельная кэш-память предусмотрена для хранения данных. В последнем случае предпочтительно использовать два блока защиты 20, один для команд и один для данных. Оба варианта, по которым это может быть реализовано, показаны на фиг. 4А и 4В.

На фиг. 4А кэш-память команд 430 и кэш-память данных 440 одновременно доступны процессорному ядру 10. Когда для просмотра кэш-памяти в кэш-памяти команд 430 используется адрес команды, то этот адрес подается также в блок защиты 400, чтобы определить атрибуты, которые должны быть использованы для управления доступом к памяти, если это потребуется. Подобным же образом, когда для просмотра в кэш-памяти данных 440 используется адрес данных, то этот адрес подается также в блок защиты 410 для определения атрибутов, которые следует использовать для управления доступом к памяти, если это потребуется. Блоки защиты 400 и 410 предпочтительно иметь такими же, как блок защиты 20, показанный на фиг.1, за исключением того, что регистры атрибутов и регистры, определяющие логические области, обеспечиваются теперь одним набором регистров 420. Следовательно, на фиг.1 как для доступа к данным, так и для доступа к командам в памяти используются одни и те же логические области и атрибуты.

Однако при альтернативном подходе, показанном на фиг.4В, для блоков защиты 400 и 410 должны быть предусмотрены отдельные регистры 450 и 460 соответственно, что позволяет задавать для доступа к данным и доступа к командам логические области с разными размерами, которые имеют разные атрибуты. Это обеспечивает большую гибкость, поскольку, к примеру, может потребоваться иметь для областей команд области данных разного размера.

Изобретение относится к устройству обработки данных и способу для доступа к памяти, имеющей множество ячеек памяти для хранения значений данных. Техническим результатом является расширение функциональных возможностей. Устройство обработки данных для управления доступом к памяти содержит запоминающее устройство диапазона адресов для хранения информации, идентифицирующей диапазоны адресов для множества логических областей в памяти, запоминающее устройство атрибутов для хранения атрибутов, используемых для управления доступом к ячейкам в логической области, логическую схему компаратора, логическую схему определения атрибутов. Способ описывает работу указанного устройства. 2 c. и 14 з.п. ф-лы, 5 ил.

| ЕР 0700002 А1, 06.03.1996 | |||

| RU 94045887 А1, 20.11.1996 | |||

| Установка для производства биомассы водорослей | 1976 |

|

SU656592A1 |

| 0 |

|

SU150522A1 | |

Авторы

Даты

2003-10-27—Публикация

1998-02-03—Подача