Данное изобретение относится к области обработки данных. Конкретно, данное изобретение относится к системам обработки данных, имеющим процессор и запоминающее устройство данных, между которыми передаются командно-информационные слова, слова считывания данных и слова записи данных.

Известны системы обработки данных, которые содержат процессор, соединенный с памятью данных, такой как кэш-память, которая хранит командно-информационные слова, слова считывания данных и слова записи данных. Специалистам в данной области будет понятно, что различение разных информационных слов зависит от доступа, которое в данное время выполняют с помощью данного информационного слова, например, информационного слова, которое в данное время записывают в память данных, может считаться словом записи данных в это время, и в то же самое информационное слово, считываемое затем из памяти данных, может рассматриваться как слово считывания данных.

Передача информационных слов между памятью данных и соответствующим процессором подчас является критическим фактором рабочих характеристик работы такой системы обработки данных. Для улучшения общих рабочих показателей системы значительные усилия прилагают для проектирования механизма передачи этих информационных слов.

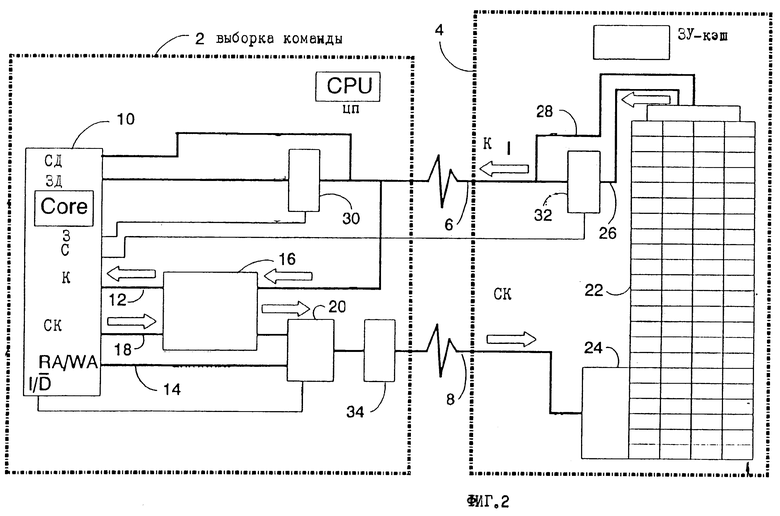

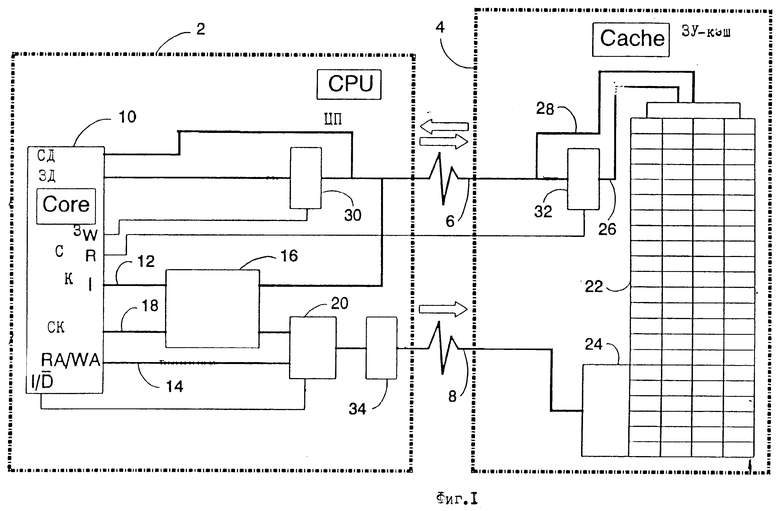

Фиг. 1-4 прилагаемых чертежей иллюстрируют типичную известную компоновку (аналогичную интегральной схеме ARM600 компании Эдванст РИСК Машина Лимитид (для передачи данных между центральным процессором 2 (ЦП) и кэш-ЗУ 4. Эта система содержит шину данных 6 и адресную шину 8, проходящую между ЦП 2 и памятью-ЗУ 4. ЦП 2 включает в себя сердечник 10, который реагирует на командно-информационные слова, поступающие к нему по шине командно-информационных слов 12. Сердечник 10 выводит слова записи данных (ЗД) по формирователю 30 на шину данных 6, а адреса записи (A3) - на адресную шину 14 считывания и записи. Адрес записи (ЗА) по получении его памятью-кэш 4 управляет местоположением, на котором слово записи данных (ЗД) хранится в памяти-кэш 4. Подобным же образом шина данных 6 и адресная шина 14 считывания и записи могут использоваться для считывания слов считывания данных (СД) из памяти-кэш 4 в сердечник 10 из местоположений в памяти-кэш 4, определенных адресом считывания (АС) на адресной шине 14 считывания и записи.

Командно-информационные слова, выбираемые из кэш-памяти 4, поступают через шину данных 6 в блок упреждающей выборки 16 (ARM600 не имеет блока упреждающей выборки). Блок упреждающей выборки 16 предназначен для того, чтобы способствовать ровной своевременной подаче командно-информационных слов в сердечник 10, и выполняет такие функции, как распознавание команды ветвления. Адреса в кэш-памяти 4, из которой выбираются командно-информационные слова, определяются адресом счетчика команд (СК), формируемым сердечником 10 и поступающим по шине 18 счетчика команд, блоку 16 упреждающей выборки и мультиплексору 20 в адресную шину 8. Мультиплексор 20 служит для выборочного соединения либо шины 18 счетчика команд, либо адресной шины 14 считывания и записи с адресной шиной 8 в зависимости от команды, а не сигнала флага данных (К/Д), генерируемого сердечником 10.

В качестве варианта блок упреждающей выборки 16 содержит регистр СК счетчика команд и подает величину счетчика команд назад в сердечник 10 вместе с соответствующей командой. В этом случае блок 16 упреждающей выборки осуществляет основной объем упреждающей выборки и нужен для формирования флага адреса ФА. Сердечник 10 обеспечивает возможности корректировки величины блока программы блока упреждающей выборки для эффективного управления своей собственной упреждающей выборкой.

В кэш-памяти 4 предусматривается матрица запоминающих ячеек 22, в которых хранятся командно-информационные слова, слова считывания данных и слова записи данных. Адресная шина B подается к дешифратору 24 адреса, который служит для отбора отдельной запоминающей ячейки или ряда запоминающих ячеек из матрицы запоминающих ячеек 22 в зависимости от адресного слова, считанного с адресной шины 8. Слова считывания данных, выбираемые из памяти-кэш 4, подаются по шине 26 считывания данных в шину данных 6. Слова записи данных, которые должны храниться в кэш 4, связываются из шины данных 6 по шине 28 записи данных в матрицу 22 запоминающих ячеек.

Для загрузки данных в кэш не через сердечник 10 требуется иной механизм. Для этого механизма потребуются его собственные формирователи для придания флаговым линиям надлежащих значений. Такой механизм мог бы работать, например, на безрезультатном обращении в кэш. Этот механизм будет работать, как правило, с гораздо меньшей скоростью, чем сердечник 10, но это не имеет решающего значения для рабочих характеристик системы.

Важным соображением в конфигурации такой системы, как показано на фиг. 1, является то, что шина данных 6 и адресная шина 8 имеют тенденцию к большей длине дорожки, и поэтому к относительно большой соответствующей емкости. Чтобы преодолеть эту сложность, помещаемые на этих шинах слова нужно активно формировать на шинах, чтобы тем самым ускорить период достижения величин правильного уровня сигнала отдельными линиями шины. Для этого схема 30 формирователя в ЦП 2 формирует слова записи данных на шине данных 6. Подобным же образом схема 32 формирователя в кэш 4 формирует слова считывания данных на шине данных 6. Преимущество здесь в том, что в каждый данный момент будет действовать только один из этих двух формирователей для шины данных 6. Сигнал флага считывания (С) и сигнал флага записи (3), генерируемые сердечником 10, служат для приведения в действие и выведения из действия этих двух формирователей 30, 32. Формирователь 34 в ЦП 2 служит для формирования адресных слов на адресной шине 8.

Фиг. 2 изображает работу системы фиг. 1 при выборке командно-информационных слов. В этом режиме мультиплексор 20 переключает величину СК на адресную шину 8 для отбора местоположения адреса команды из кэш-памяти 4. Командно-информационное слово К, доступ к которому осуществлен таким образом, подается в сердечник 10 по шине считывания 26, формирователю 32, шине данных 6, блоку 16 упреждающей выборки и шине 12 команд.

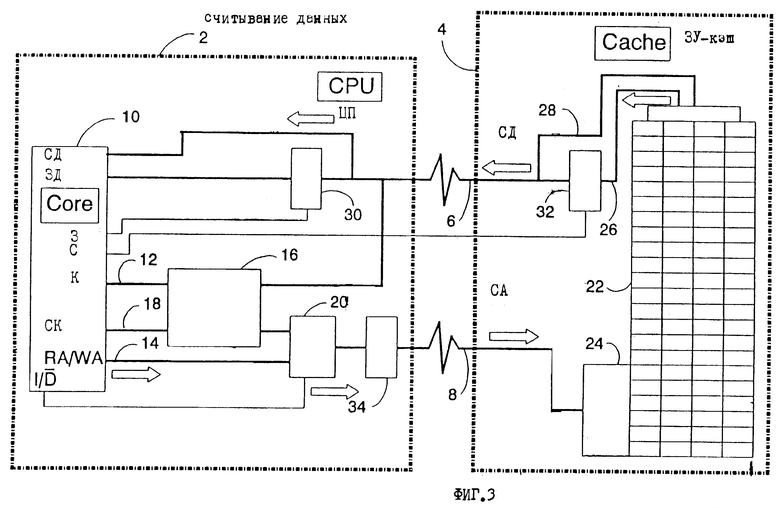

Фиг. 3 изображает работу системы по фиг. 1 в передаче слов считывания данных. В этом случае мультиплексор 20 отбирает адрес считывания АС из сердечника 10 для подачи по адресной шине 8 к дешифратору 24 адреса. Слово считывания данных, доступ к которому осуществлен таким образом, поступает назад к сердечнику 10 по шине 26 считывания, формирователю 32 и шине данных 6.

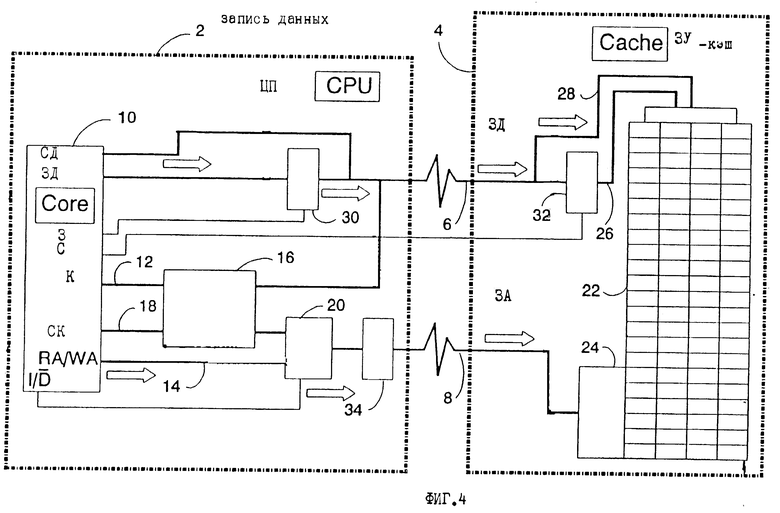

Наконец, фиг. 4 изображает работу системы по фиг. 1 в передаче слова записи данных. В этом случае адрес записи A3 поступает от сердечника 10 по мультиплексору 20 к адресной шине 8. Спустя один цикл сердечник 10 генерирует слово записи данных ЗД и подает его по формирователю 30, шине данных 6 и шине записи 28 в матрицу 22 запоминающих ячеек.

Можно заметить, что при передаче слова считывания данных формирователь 32 в кэш-памяти 4 формирует шину данных 6. Наоборот, во время передачи слова записи данных формирователь 30 в ЦП 2 формирует шину данных 6. Во избежание противоречий между двумя формирователями 30, 32 важно, чтобы они никогда не приступали к формированию шины данных 6 одновременно. Это противоречие может привести к повреждению схемы и будет потреблять неоправданно значительное количество энергии. Чтобы застраховаться от этих противоречий, должен быть выдержан период задержки между выключением одного из формирователей 30, 32 и включением другого формирователя 30 или 32. Для этого требуются два отдельных сигнала управления или точное хронирование в буферах (т.е. медленное включение и быстрое выключение).

Для общего улучшения рабочих характеристик систем, изображенных на фиг. 1-4, можно следовать различным решениям. Одно из них заключается в увеличении скорости генератора тактовых импульсов, с которой передаются данные, например, если для сердечника 10 используется частота "f" этого генератора, то для передачи можно использовать скорость генератора, равную "2f". Однако при этом решении возникают проблемы с выдерживанием и соответствующей синхронизацией достаточной задержки между формированием шины данных 6 формирователем 30 и формированием шины данных 6 формирователем 32. Помимо этого имеется потеря пропускной способности в связи с (повышенными) требованиями к синхронизации.

Еще одно решение проблемы улучшения рабочих характеристик могло бы заключаться просто в увеличении ширины шины. Более широкие шины позволяют передавать большее количество данных за данный период с данной скоростью тактовых сигналов. Недостаток этого решения в том, что нужно увеличивать физические размеры шины. Во многих случаях увеличение физического размера является недостатком с точки зрения изготовления, поскольку требуются более крупные интегральные схемы с соответствующей пониженной отдачей.

Первым объектом данного изобретения является интегральная схема, содержащая:

кэш-память данных;

процессор, реагирующий на считанные с адресов команды в упомянутой памяти данных командно-информационные слова для считывания слов считывания данных из адресов считывания в упомянутой памяти данных и для записи слов записи данных в адреса записи в упомянутой памяти данных;

однонаправленную шину считывания, непосредственно соединяющую упомянутую память данных и указанный процессор для передачи упомянутых командно-информационных слов и упомянутых слов считывания данных с указанной памяти данных в упомянутый процессор; и

однонаправленную шину записи и адреса, непосредственно соединяющую упомянутый процессор и упомянутую память данных для передачи слов записи данных, командно-адресных слов, слов считывания адреса и слов записи адреса с упомянутого процессора в упомянутую память данных;

в которой упомянутая память данных действует в режиме пакетного доступа, при котором адресное слово, передаваемое в упомянутую память данных, определяет начальный адрес для последовательности действий доступа для последующих адресов в упомянутой памяти данных.

Однонаправленные шины для потока данных в том или ином направлении имеют то преимущество, что не нужно предусматривать промежуток времени, необходимый для безопасного изменения направления шины на обратное. Тем самым скорость шины можно увеличить, не создавая при этом проблем синхронизации. Помимо этого данное изобретение воспользовалось тем обстоятельством, что данные адреса, подаваемые по шине адреса, изменяются относительно нечасто по сравнению с данными на шине данных. Таким образом, мультиплексирование данных записи на эту шину при помощи данных адреса для формирования шины записи и адреса более полно использует имеющуюся пропускную способность.

В соответствии с данным изобретением упомянутая память данных действует в режиме пакетного доступа, в котором адресное слово, передаваемое в упомянутую память данных, определяет начальный адрес для последовательности действий доступа для последующих адресов в упомянутой памяти данных.

Такой режим пакетного доступа особенно пригоден для используемой в данном изобретении структуры шины, поскольку слово данных адреса должно иметься только при пуске последовательности подлежащих выборке командно-информационных слов или слов считывания данных, либо подлежащих записи слов записи данных. Одно слово данных адреса запускает процесс выборки, который затем идет последовательно по следующим друг за другом адресам до окончания. Таким образом шина записи и данных адреса нужна для несения меньшего количества слов данных адреса, в результате чего освобождается пропускная способность для прохождения слов записи данных.

Как указывалось выше, можно предусмотреть схемы формирователей для шин данных, чтобы увеличить скорость, с которой надежно получают величины сигналов, несмотря на то, что данное изобретение имеет преимущество более интенсивного использования пропускной способности шины, подавая адресные данные даже без этих формирователей, эти формирователи хорошо подходят для использования в данном изобретении, так как они остаются постоянно активными для данной шины.

В предпочтительных осуществлениях данного изобретения указанный процессор содержит блок упреждающей выборки команд для получения упомянутых командно-информационных слов и схему получения слов считывания данных для получения указанных слов считывания данных, причем указанный блок упреждающей выборки команд и указанная схема получения слов считывания данных подключена параллельно к указанной шине считывания данных.

Наличие блока упреждающей выборки ускоряет обработку команды. Параллельное подключение схемы получения слов считывания данных и блока упреждающей выборки позволяет шине считывания подавать либо командно-информационные слова, либо слова считывания данных, не направляя их по мультиплексору; причем процессор избирательно приводит в действие либо блок упреждающей выборки, либо схему получения слов считывания данных сообразно с надобностью.

В предпочтительных осуществлениях данного изобретения упомянутая память данных содержит приемник адреса и декодер для получения и декодирования указанных командно-адресных слов, указанных слов считывания адреса и указанных слов записи адреса, и схему записи для записи указанных слов записи данных, и в ней линия сигнала флага адреса проходит между указанным процессором и указанными приемником адреса и декодером для приведения в действие указанных приемника адреса и декодера.

Мультиплексирование слов данных адреса и слов записи данных на адресной шине ставит проблему способа соответствующего распознавания и обработки этих различных данных памятью данных. Для этого удобная гибкость достигается сигналом флага адреса для управления соответствующей обработкой в памяти данных.

В качестве дополнения предпочтительно, чтобы упомянутый процессор содержал мультиплексор для отбора либо командно-адресных слов, либо слов считывания адреса и слов записи адреса, либо слов записи данных для подключения к упомянутой шине записи и адреса.

Таким образом обеспечивается механизм для размещения соответствующих данных на шине данных записи и адреса.

Предпочтительный способ управления работой памяти данных заключается в обеспечении линии сигнала флага считывания, проходящей между упомянутым процессором и упомянутой кэш-памятью данных для передачи сигнала флага считывания; причем линия сигнала флага записи проходит между указанным процессором и указанной кэш-памятью данных для передачи сигнала флага записи, а линия сигнала флага команды проходит между указанным процессором и указанной памятью-кэш данных для передачи сигнала флага команды; в этом способе упомянутые сигнал флага считывания, сигнал флага записи и сигнал команды выбирают режим доступа к упомянутой памяти данных, а указанный флаг считывания служит для того, чтобы пренебречь указанным сигналом флага команды, в результате чего передача слов считывания данных по указанной шине считывания имеет более высокий приоритет, чем передача командно- информационного слова.

Тем самым память данных можно ввести в надлежащий режим для выборки слов считывания данных или командно-информационных слов, либо для хранения слов записи данных. Помимо этого средняя скорость обработки повышается тем, что передаче слова считывания данных предоставляется более высокий приоритет, чем приоритет командно-информационного слова, поскольку командно- информационные слова обычно выбираются упреждающе и буферизируются в системе, в то время как выборка слов считывания данных имеет тенденцию происходить хаотично - как потребуют отдельные декодированные команды.

Другим объектом данного изобретения является способ обработки данных в интегральной схеме, который содержит следующие этапы:

хранение командно-информационных слов, слов считывания данных и слов записи данных в памяти данных;

передачу упомянутых командно-информационных слов и слов считывания данных из указанной памяти данных в процессор по однонаправленной шине считывания, непосредственно соединяющей указанную память данных и указанный процессор; и

передачу указанных слов считывания данных, командно-адресных слов, слов считывания адреса и слов записи адреса из указанного процессора в указанную память данных по однонаправленной шине записи и адреса, непосредственно соединяющей упомянутый процессор и упомянутую память данных;

и в котором указанная память данных работает в режиме пакетного доступа, при котором адресное слово, передаваемое в указанную память данных, определяет начальный адрес для последовательности действий доступа для последующих адресов в указанной памяти данных.

Сущность изобретения иллюстрируется в качестве примера ссылкой на сопроводительные чертежи, в которых

фиг. 1 - 4 изображают типичную известную систему процессора и памяти данных;

фиг. 5 изображает устройство системы процессора и памяти данных, содержащей однонаправленные шины в соответствии с одним осуществлением данного изобретения; и

фиг. 6-8 изображают работу варианта по фиг. 5 в различных режимах.

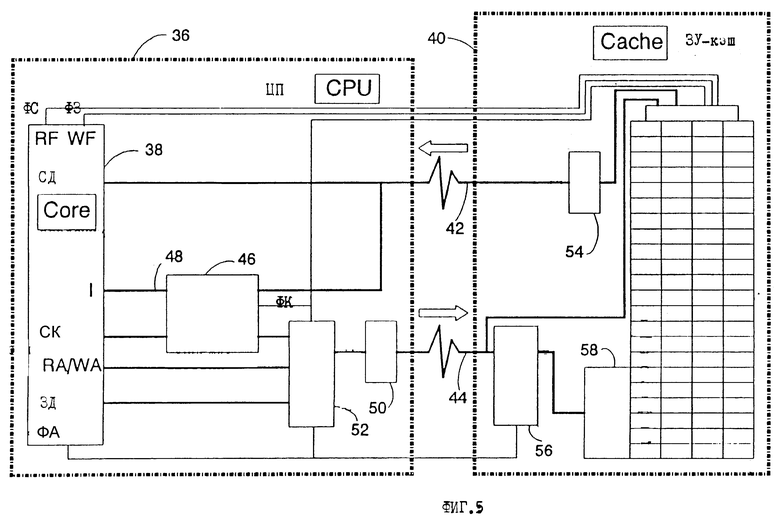

Фиг. 5 изображает ЦП 36 с сердечником 38, который получает слова считывания данных СД и командно-информационные слова К и формируют слова записи данных ЗД. Эти слова передаются между ЦП 36 и кэшем 40 по однонаправленной шине считывания 42 и однонаправленной шине считывания и адреса 44. Шина считывания 42 соединена параллельно с блоком 46 упреждающей выборки и схемой получения данных считывания в сердечнике 38.

Командно-информационные слова с блока упреждающей выборки 46 поступают в сердечник 38 по шине команд 48.

Шина 44 записи и адреса формируется формирователем 50 в ЦП 36, причем формирователь 50 получает свой вход из трехстороннего мультиплексора 52. Трехсторонний мультиплексор 52 производит отбор среди величин СК счетчика команд из блока 46 упреждающей выборки, адрес считывания АС или адрес записи A3 с сердечника 38, или данных записи ЗД с сердечника 38. Отбираемый трехсторонним мультиплексором 52 сигнал отбирается в зависимости от сигнала адреса флага АФ, генерируемого сердечником 38, и сигнала флага команды ФК, генерируемого блоком упреждающей выборки 46.

В кэш-памяти 40 формирователь 54 формирует величины сигнала на шине 42 считывания данных. Сигналы с шины 44 записи и адреса направляются и на схему 58 дешифратора адреса (по защелке 56 адреса, управляемой сигналом флага адреса ФА), и на схему получения данных записи.

Примечательно, что хотя описанный выше вариант воплощения изобретения использует схему 58 дешифратора адреса, возможны также и другие варианты воплощения на основе сочетательного кэша (т.е. поиск признака декодирования).

Выборка либо слов считывания данных, либо командно-информационных слов кэш-памятью 40 управляется через сигнал флага считывания ФС, генерируемый сердечником 38, и сигнал флага команды ФК. Кроме этого сигнал флага записи ФЗ, генерируемый сердечником 38, показывает, что слова записи данных должны быть получены и храниться памятью-кэш 40 из шины 44 записи и адреса.

В схеме по фиг. 5 - в противоположность схемам по фиг. 1-4 - шина 42 считывания является однонаправленной с формирователем 54 только на одном конце, и на этой шине не нужно изменять свое направление передачи. Соответственно, не тратится время на изменение направления, благодаря чему можно избежать возможного повреждения и лишнего расхода энергии из-за противоречий схем формирователей. Данные адреса и данные записи мультиплексируются с временным разделением на шине 44 записи и адреса трехсторонним мультиплексором 52.

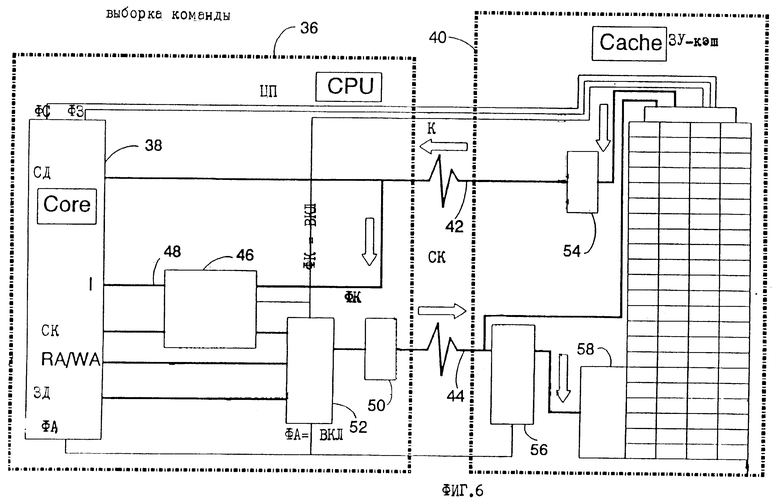

Фиг. 6 изображает систему, работающую в режиме упреждающей выборки команд. В этом режиме величина СК адреса счетчика команд подается к дешифратору 58 адреса по блоку 46 упреждающей выборки, трехстороннему мультиплексору 52, формирователю 50, шине 44 записи и адреса, и защелке 56 адреса. Сигнал флага адреса ФА ВКЛЮЧЕН и сигнал флага команды ФК ВКЛЮЧЕН. Это сочетание сигналов управляет трехсторонним мультиплексором 52 для отбора величины СК адреса счетчика команд из блока 46 упреждающей выборки для ее приложения через формирователь 50 к шине 44 записи и адреса. Флаг команды ФК, проходящий к памяти-кэш 40, также показывает, что командно-информационное слово должно быть выбрано из адреса, определенного на шине 44 записи и адреса. Это командно-информационное слово возвращается в ЦП 36 через формирователь 54, шину 42 считывания, блок 46 упреждающей выборки и шину команд 48.

Эта система действует в пакетном режиме, в котором одна величина СК начального адреса счетчика команд определяет адрес, из которого предшествуют последовательные выборки команд до тех пор, пока не будет подан следующий адрес. Защелка 56 адреса обеспечивает ввод в схему 58 дешифратора адреса; причем схема 58 дешифратора адреса включает в себя счетчик для приращения адреса во время работы в пакетном режиме.

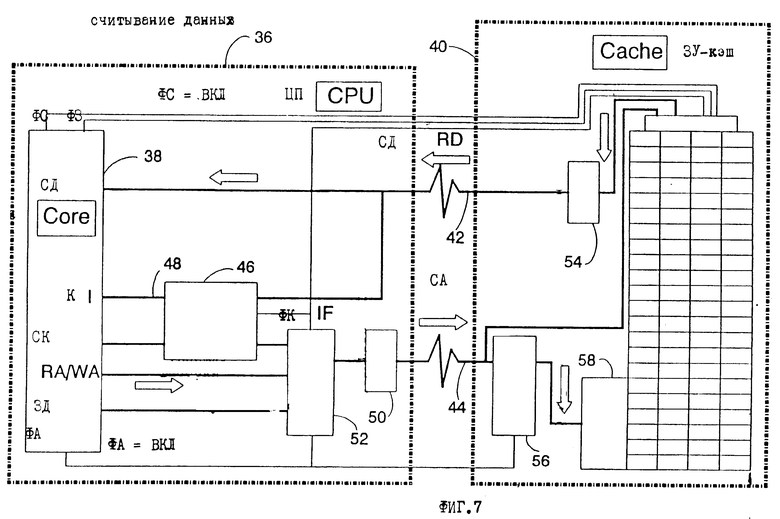

Фиг. 7 изображает действие считывания данных для системы по фиг. 5. В этом случае слова считывания данных направляют из памяти-кэш 40 к сердечнику 38 по формирователю 54 и шине 42 считывания данных. Адрес считывания АС отбирается трехсторонним мультиплексором 52 в ответ на сигнал флага адреса ФА, утверждающим ВКЛ, и флагом команды ФК, утверждающим ВЫКЛ. Соответственно, адрес считывания прилагается к кэшу 40 по формирователю 50, шине 44 записи и адреса, защелке 56 адреса и дешифратору 58 адреса. С ВКЛЮЧЕННЫМ флагом адреса, ВКЛЮЧЕННЫМ флагом считывания и ВЫКЛЮЧЕННЫМ флагом записи обусловливается обработка сигналов на шине 44 адреса и считывания кэшем 40 как адреса считывания.

Считывание данных приобретает приоритет над упреждающей выборкой команды. Поэтому, если блок упреждающей выборки 46 утверждает, что сигнал флага команды ФК ВКЛЮЧЕН, указывая на то, что он готов принять последующие командно-информационные слова, и если сердечник 38 утверждает, что сигнал флага считывания ФС ВКЛЮЧЕН, то логическая схема в кэш-памяти 40 воспринимает считывание как имеющее более высокий приоритет и возвращает по шине 42 считывания запрошенные слова считывания данных, а не командно-информационные слова.

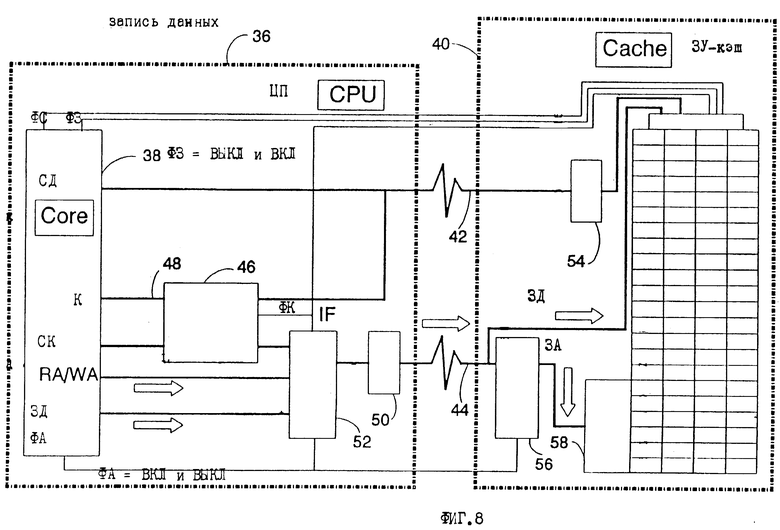

Фиг. 8 изображает систему по фиг. 5 в режиме запоминания слов записи данных в кэш-памяти 40. В этом режиме флаг сигнала адреса СА чередуется между утверждением ВКЛ и ВЫКЛ в зависимости от вывода в данное время сердечником 38 адреса записи A3 или слова записи данных. Сигнал флага команды ФК утверждается как ВЫКЛ, а сигнал флага адреса ФА управляет трехсторонним мультиплексором 52 для отбора надлежащего адреса записи (A3) или слова записи данных, и прилагает их к шине 44 записи и адреса по формирователю 50. Слова записи данных и слова записи адреса таким образом эффективно мультипрексируются с временным разделением на шине 44 записи и адреса. Благодаря передаче записи в пакетном режиме адрес записи нужен только в нечастых интервалах, например на границах страницы. Если бы была необходимость обеспечить адрес записи каждому слову записи данных, то это фактически привело бы к уменьшению пропускной способности для записи наполовину.

В кэш-памяти 40 приемник 56 адреса (защелка адреса) реагирует на величину сигнала флага адреса ФА для сбора адресных слов на шине 44 записи и адреса. Сигнал флага записи ФЗ утверждается как ВЫКЛ и ВКЛ (в противофазе флагу адреса ФА), указывая кэшу 40, что нужно запомнить слова записи данных из шины 44 записи и адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАЩИТА ДОСТУПА К ПАМЯТИ | 1998 |

|

RU2215321C2 |

| ОБРАБОТКА ДАННЫХ С ИСПОЛЬЗОВАНИЕМ НЕСКОЛЬКИХ НАБОРОВ КОМАНД | 2002 |

|

RU2281547C2 |

| АДРЕСАЦИЯ РЕГИСТРОВ В УСТРОЙСТВЕ ОБРАБОТКИ ДАННЫХ | 1997 |

|

RU2193228C2 |

| УСТРОЙСТВО И СПОСОБ ОБРАБОТКИ ДАННЫХ С ИСПОЛЬЗОВАНИЕМ НАБОРОВ КОМАНД | 1995 |

|

RU2137183C1 |

| ОГРАНИЧЕНИЕ ОБЛАСТЕЙ ПАМЯТИ ДЛЯ СЧИТЫВАНИЯ КОМАНД В ЗАВИСИМОСТИ ОТ АППАРАТНОГО РЕЖИМА И ФЛАГА БЕЗОПАСНОСТИ | 2010 |

|

RU2513909C1 |

| УСТРОЙСТВО И СПОСОБ ОБРАБОТКИ ДАННЫХ | 1994 |

|

RU2155375C2 |

| ОБРАБОТКА ДАННЫХ С ПОМОЩЬЮ СОПРОЦЕССОРА | 2001 |

|

RU2275678C2 |

| ВЫПОЛНЕНИЕ ИНСТРУКЦИИ ОБРАБОТКИ ДАННЫХ | 1994 |

|

RU2137182C1 |

| СИСТЕМА УПРАВЛЕНИЯ КОНВЕЙЕРИЗОВАННЫМ ЦИКЛОМ ПРОЦЕССОРА ШИРОКОГО КОМАНДНОГО СЛОВА | 2001 |

|

RU2184389C1 |

| АРХИТЕКТУРА ИНТЕГРАЛЬНОЙ МИКРОСХЕМЫ ДЛЯ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛА | 1997 |

|

RU2223535C2 |

Система обработки данных имеет центральный процессор (ЦП), соединенный однонаправленной шиной считывания и однонаправленной шиной записи и адреса с памятью данных (например, кэш, ЗУПВ или диск) в виде кэш-памяти. Шина считывания и шина записи и адреса формируются только в одном направлении. При этом технический результат заключается в устранении потерь времени из-за изменения направления на обратное прохождение сигнала по шине. Слова считывания данных (СД) и командно-информационные слова (К) передаются из кэш-памяти в сердечник ЦП по шине считывания. Командно-адресные (СК) слова, слова считывания адреса (СА), записи адреса (ЗА) и записи данных (ЗД) мультиплексируются с временным разделением на шине записи и адреса для поступления из сердечника в кэш-память. Система обеспечивает передачу в пакетном режиме, тем самым уменьшая число адресов, которые нужно передавать на шину записи и адреса, освобождая пропускную способность на этой шине для использования слов записи данных. 2 с. и 6 з.п.ф-лы, 8 ил.

| ПОЧВООБРАБАТЫВАЮЩАЯ ФРЕЗА | 0 |

|

SU398191A1 |

| EP 0409556 A2, 23.01.91 | |||

| Система пуска и реверса двигателя внутреннего сгорания | 1973 |

|

SU464708A1 |

| US 5086407 A, 04.02.92 | |||

| JP 57123453 A, 26.01.81 | |||

| Машина для формовки ребристых труб | 1932 |

|

SU32099A1 |

| Паулсен Э | |||

| Повышение быстродействия главных абонентов шины SCSI благодаря локальной памяти | |||

| Электроника | |||

| - М.: Мир, 1993, N 17, с.44 - 52. | |||

Авторы

Даты

1999-09-10—Публикация

1994-10-14—Подача