Изобретение относится, в общем, к аналого-цифровым преобразователям (ADC) и, в частности, к полностью дифференциальным параллельным ADC, в которых используются матрицы компараторов.

В стандартных параллельных ADC аналоговое входное напряжение сравнивается с опорными напряжениями, формируемыми цепью резисторов. Такой архитектуре присуща несимметрия по отношению к входам необходимой матрицы компараторов, которая вместе с высокой и нелинейной емкостью вызывает ухудшение характеристик известных параллельных ADC при высоких частотах аналогового сигнала.

Полностью дифференциальный параллельный ADC описан в статье Petschacher и др. под заголовком "А 10-b 75-MSPS Subranging A/D Converter with Integrated Sample and Hold" IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 25, N 6, DECEMBER 1990, pp. 1339-1346.

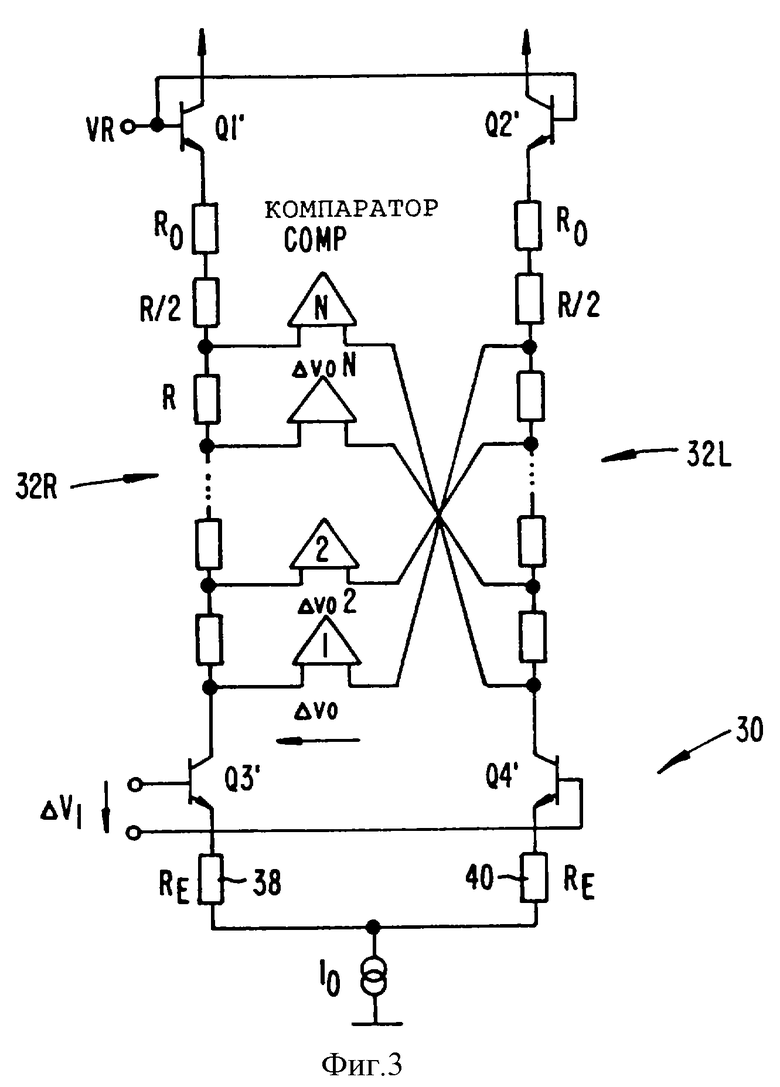

На фиг. 3 показана схема, описанная в этой статье. Схема включает "дифференциальную опорную ступенчатую схему" (DRL), включающую дифференциальный усилитель с общим эмиттером 30 с двумя идентичными резисторными цепями 32R и 32L, каждая из которых содержит нагрузочный резистор и битовые резисторы, заменяющие собой один подсоединенный к коллектору нагрузочный резистор.

Дифференциальный усилитель включает первый и второй n-p-n-транзисторы Q3' и Q4', базы которых подсоединены для приема дифференциального входного сигнала, а эмиттеры подсоединены соответственно к эмиттерным резисторам 38 и 40, каждый из которых имеет сопротивление RE и служит для обеспечения эмиттерной отрицательной обратной связи и установки общего коэффициента усиления ADC.

Как известно, соединенные по схеме с общими эмиттером транзисторы Q3' и Q4' и 36 имеют коэффициент усиления - RC/RE, где RC - суммарное сопротивление каждой цепи нагрузочных резисторов.

Базы транзисторов Q1' и Q2' подсоединены к опорному напряжению, а их эмиттеры подсоединены соответственно к резисторным цепям 32L и 32R для обеспечения VBE (эмиттерное напряжение смещения) компенсации транзисторов Q3' и Q4' в дифференциальном усилителе 30.

Хотя вышеописанная схема и обладает множеством желаемых характеристик, с ней возникают существенные проблемы. В частности, необходимость иметь эмиттерный резистор для обеспечения эмиттерной обратной связи увеличивает объем и сложность схемы в интегральном исполнении, поскольку резисторы занимают определенное место. Практически, если DRL состоит из 2N резисторов, тогда эмиттерные резисторы, RE, потребуют еще 2N резисторов, что в сумме составит 4N резисторов.

Кроме того, дифференциальный входной каскад с общим эмиттером ограничивает динамический диапазон и полосу пропускания входного сигнала, линейность выходного сигнала и минимальный уровень напряжения источника питания. Необходимость использования дополнительных транзисторов для обеспечения VBE компенсации еще больше усложняет схему.

Настоящее изобретение представляет собой полностью дифференциальный параллельный ADC, который использует входной каскад в виде повторителя напряжения для исключения необходимости иметь эмиттерный или истоковый резистор отрицательной обратной связи и транзисторы VBE компенсации и обеспечивает также другие преимущества функционирования.

Согласно одному аспекту изобретения дифференциальный входной каскад на повторителе напряжения воспринимает дифференциальный вход для его преобразования к цифровому значению и обеспечивает дифференциальный выходной сигнал на первом и втором выходах.

Дифференциальная резисторная ступенчатая схема (DRL) соединяет первый и второй выходы дифференциального входного каскада с первым и вторым источником тока. DRL имеет первую и вторую ветви, при этом каждая ветвь включает одинаковое число (N+1) последовательно соединенных резистивных элементов с выводами этих элементов, образующими множество полюсов.

Входной полюс каждой ветви представляет собой вывод резистивного элемента, соединенного с одним выходом дифференциального входного каскада, а выходной полюс представляет собой вывод резистивного элемента, подсоединенного к источнику тока.

Источник тока обеспечивает постоянный ток, Io, протекающий по каждой ветви и генерирующий постоянную разность уровней напряжений между соседними полюсами в зависимости от величины постоянного тока.

Полюса каждой ветви DRL подсоединены крест на крест к входам матрицы компараторов. Матрица содержит (N + 2) компараторов, где n-й компаратор, n = 0, 1,...,N, N+1, подсоединен своим первым входом к полюсу первой ветви, отстоящему на n полюсов от выходного полюса, а своим вторым входом подсоединен к полюсу во второй ветви, отстоящему от входного полюса второй ветви на n полюсов.

При биполярной реализации использование входного дифференциального каскада на повторителе напряжения исключает необходимость в эмиттерном резисторе отрицательной обратной связи и в схеме VBE компенсации. Такая конфигурация схемы увеличивает также динамический диапазон входного сигнала и полосу пропускания, линейность выходного сигнала и уменьшает необходимый уровень напряжения источника питания.

Сущность изобретения иллюстрируется ссылкой на сопроводительные чертежи, в которых:

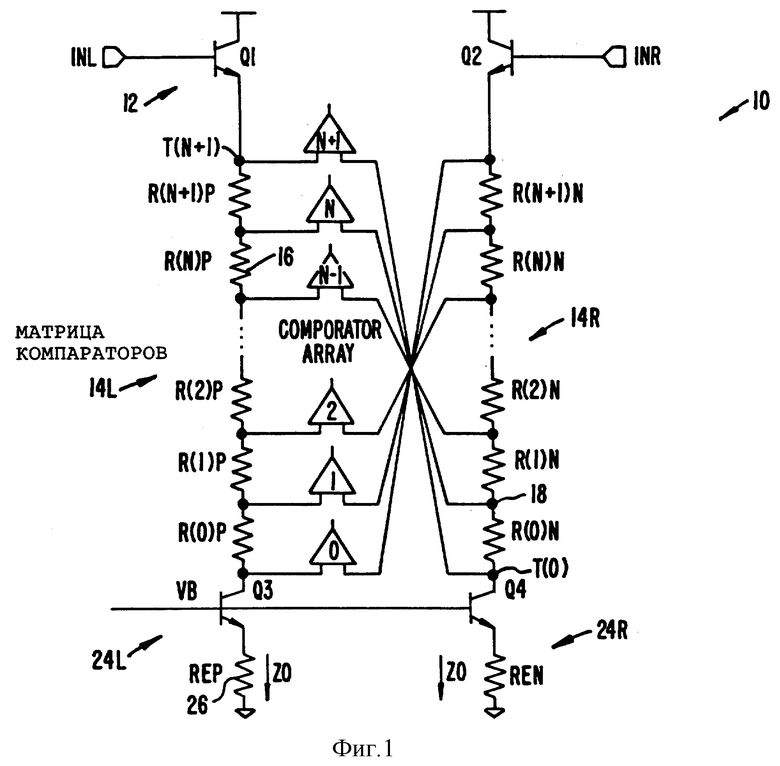

Фиг. 1 - схема предпочтительного варианта реализации изобретения,

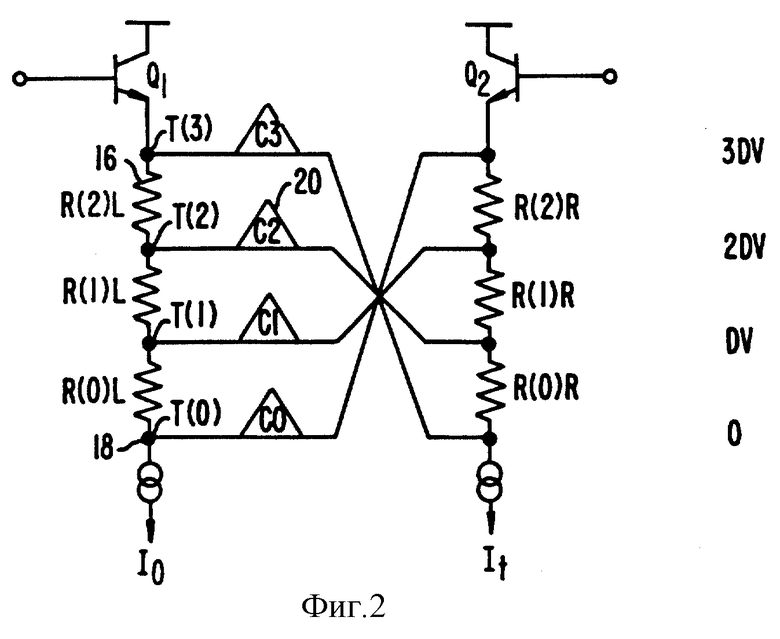

Фиг. 2 - схема варианта реализации с четырьмя компараторами,

Фиг. 3 - схема известной системы.

Описание предпочтительного варианта реализации

На фиг. 1 представлена схема предпочтительного варианта изобретения. Схема представляет собой полностью дифференциальный аналого-цифровой преобразователь (ADC) 10 на основе усилительной структуры с общим коллектором.

Дифференциальный входной каскад с общим коллектором (эмиттерный повторитель) 12 включает биполярные n-p-n-транзисторы Q1 и Q2, причем у каждого из них коллектор подсоединен к напряжению питания (VCC), база подсоединена для приема одной из частей (INL и INR соответственно) дифференциального входного сигнала, а эмиттер соединен с ветвью дифференциальной резистивной цепи (DRL) 14.

DRL 14 имеет левую ветвь 14L и правую ветвь 14R, каждая из которых включает (N + 1), где N - четное целое число, последовательно соединенных RBIT резисторов 16 (R(n)L и R(n)R соответственно) для n = 0, 1, 2,..,N. Выводы RBIT резисторов 16 образуют последовательность из (N+2) полюсов 18 (T(n)R и T(n)L) для n = 0, 1, 2,...,T + 2.

Каждая ветвь имеет входной полюс T(N+1), подсоединенный к эмиттеру Q1 или Q2, и выходной полюс T(0). Матрица компараторов 20 имеет входы, которые соединены крест на крест с полюсами 18 ветвей DRL 14. Например, у 0-го компаратора, C0, первый вход соединен с выходным полюсом T(0)L, а второй вход соединен с входным полюсом T(N+1)R.

В общем случае у компаратора Cn имеется левый вход, подсоединенный к полюсу T(n), отстоящему на n полюсов от выходного полюса T(0), а его правый вход соединен с полюсом T(N+1-n), отстоящим на n полюсов от входного полюса T(N+1).

Каждая ветвь DRL имеет выходной полюс T(0), подсоединенный к источнику тока 24L или 24R. Левый источник тока включает биполярный n-p-n-транзистор Q3, коллектор которого подсоединен к выходному терминалу T(0)L левой ветви DRL 14, база подсоединена для приема стабилизированного напряжения смещения (VB), а эмиттер подсоединен к резистору 26 (REL).

Как хорошо известно специалистам, источник тока 24 поддерживает постоянный ток, имеющий значение Io, равное (VB-VBE)/REL. Правый источник тока устроен подобным же образом и выдает тот же самый ток Io. Опорный ток Io подается от источника опорного напряжения с температурной компенсацией (не показан). В этом источнике опорного напряжения необходимо использовать тип резисторов, подобный RBIT резистору, используемому в DRL 14. Таким образом опорный ток адаптируется к разбросу значений RBIT.

Теперь опишем функционирование схемы, изображенной на фиг. 1. Каждый из RBIT резисторов 16 имеет одно и то же значение сопротивления (R), так что падение напряжения на каждом резисторе (равное разности потенциалов DV между соседними полюсами 18 DRL ветви) равно Io•R. Соответственно при равных входных сигналах на INL и INR, нулевом состоянии сигнала, если значение напряжения на полюсе T(0) равно 0, тогда напряжение на T(1) = DV, на T(2) = 2DV и на T(n) = nDV.

Напряжение, вводимое в компаратор, представляет собой разность между правым входом и левым входом компаратора. Для нулевого состояния сигнала вход в 0-й компаратор C0 равен (N+1)DV, вход в первый компаратор C1 равен (N-1)DV и вход во второй компаратор C2 равен (N-3)DV.

Теперь со ссылками на фиг. 2, где изображена схема, будут описаны общие принципы функционирования схемы, когда поступает ненулевой дифференциальный сигнал, при этом в схеме имеются 3 RBIT резистора 16, N = 2, и 4 компаратора 20(N+1) = 3. Как показано на фиг. 2, уровни напряжения на полюсах DRL для нулевого состояния сигнала равны nDV. Выходные сигналы на компараторах 20 представляют собой разность между уровнями напряжений на левом и правом входах компаратора.

При нулевом состоянии сигнала входные сигналы компараторов, то есть разность между уровнями напряжений на левом и правом входах компаратора, составляют:

C0 (вход) = -3DV

C1 (вход) = -1DV

C2 (вход) = 1DV

C3 (вход) = 3DV

Если выходной сигнал компаратора имеет высокий уровень (H, или логическая "1") при положительной разности входных сигналов и низкий (L, или логический "0") уровень при отрицательной разности входных сигналов, тогда при нулевом состоянии сигнала половина компараторов будет иметь выходные сигналы высокого уровня, а половина - низкого уровня.

Выходные сигналы компараторов подаются на кодер (не показан), который кодирует местоположение переключения с H на L, чтобы преобразовать в цифровой код значение дифференциального входного сигнала.

Если получен сигнал, который увеличивает уровень напряжения на INL на dv и уменьшает величину напряжения INR на dv, тогда, как известно, уровни напряжения на эмиттерах Q1 и Q2 изменятся на ту же величину. Однако ток через ветви DRL 14 не изменится, поскольку они подсоединены к источникам тока 24. Соответственно уровни входных напряжений на компараторах равны:

C0 (вход) = -3DV + 2dv

C1 (вход) = -1DV + 2dv

C2 (вход) = 1DV + 2dv

C3 (вход) = 3DV + 2dv

Входные сигналы на C1 станут положительными при dv = DV/2 и выход C1 переключится с L на Н. При изменении знака сигнала на противоположный выход C2 станет отрицательным, если dv = -DV/2, так что чувствительность LSB (младшего значащего разряда) АЦП равна DV. Если dv = DV/2, когда переключился C1, тогда входной уровень на C0 равен:

C0 (вход) = -3DV + 2(DV/2) = -2DV

Теперь, если dv еще возрастет по величине, входной сигнал на C0 будет:

C0 (вход) = -2DV + 2dv,

так что вход на C0 станет положительным, если dv возрастет еще раз на DV.

Использование в настоящем изобретении входного каскада с общим коллектором (эмиттерным повторителем) обеспечивает ряд существенных преимуществ по сравнению со схемой на фиг. 3. В частности, исключение необходимости в эмиттерной отрицательной обратной связи и дополнительных нагрузочных резисторах упрощает реализацию на интегральных микросхемах (IC) и делает подбор резисторов более легким. Кроме того, поскольку каждая ветвь DRL 14 работает при фиксированном токе, не требуется схема компенсации VBE модуляции, Q1' и Q2'.

Получается также ряд других преимуществ функционирования. Входной каскад с общим коллектором 12 исключает эффект емкостной обратной связи Миллера, что увеличивает полосу пропускания входного сигнала. Кроме того, диапазон входного сигнала шире, а требуемая мощность источника питания и искажение сигнала ниже благодаря такой конфигурации схемы и реализации единичного коэффициента усиления.

Теперь изобретение будет описано со ссылками на предпочтительные варианты реализации. Специалистам теперь станут очевидными альтернативные варианты и замены. Например, в предпочтительном варианте реализации изображен дифференциальный входной каскад, в котором используются n-p-n-транзисторы, включенные по схеме с общим коллектором (эмиттерный повторитель).

Однако специалистам известны схемы на МОП-структурах, КМОП-структурах и структурах на базе GaAs (арсенида галлия), использующие дифференциальный входной каскад на истоковом повторителе, где также могут быть реализованы преимущества настоящего изобретения.

При этом дифференциальный входной каскад включает первый и второй биполярные транзисторы, эмиттер каждого из которых подсоединен соответственно к одноименному выходу дифференциального входного каскада. Первый источник тока включает третий транзистор и программирующий резистор, соединяющий эмиттер третьего транзистора с землей.

В качестве резистивных элементов могут быть использованы резисторы, изготовленные из поликристаллического кремния или металла либо могут быть задействованы устройства для создания падения напряжения IR между их выводами.

Резистивные элементы в DRL могут также иметь различные значения сопротивлений для реализации нелинейного ADC. Соответственно не предполагается ограничивать изобретение, кроме как тем, что предложено в формуле изобретения.

Изобретение относится к области измерительной техники и может быть использовано в качестве параллельного АЦП. Техническим результатом является расширение динамического диапазона и полосы пропускания сигнала. Преобразователь содержит дифференциальный входной каскад, дифференциальную ступенчатую схему и матрицу компараторов. 3 з.п. ф-лы, 3 ил.

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ГНАТЕК Ю.Р | |||

| СПРАВОЧНИК ПО ЦИФРОАНАЛОГОВЫМ И АНАЛОГО-ЦИФРОВЫМ ПРЕОБРАЗОВАТЕЛЯМ | |||

| - М.: РАДИО И СВЯЗЬ, 1982, С.360-362 | |||

| Огнетушитель | 0 |

|

SU91A1 |

| Устройство для определения состояния обсадной колонны | 1972 |

|

SU446639A1 |

| Пожарный двухцилиндровый насос | 0 |

|

SU90A1 |

Авторы

Даты

2000-09-27—Публикация

1996-01-29—Подача