Изобретение относится к полупроводниковому запоминающему устройству и, в частности, к цепи усиления напряжения (употребляемый здесь термин "цепь усиления напряжения" имеет тот же смысл, что и "усилительная схема", "цепь выработки усиленного напряжения", "однокаскадная усилительная схема с компенсационной обратной связью" и т.д.) для усиления подаваемого от системы питающего напряжения до желательного уровня усиления напряжения.

В полупроводниковом запоминающем устройстве, таком как динамическое ОЗУ (оперативное запоминающее устройство или память со случайной выборкой) и т. п. , передача данных может вызывать сдвиг действующего потенциала. В динамическом ОЗУ, состоящем из КМОП-транзисторов, происходит падение напряжения МОП-транзистора во время передачи потенциала через канальную область МОП-транзистора. Это нежелательное падение напряжения становится препятствием для точного считывания и записи данных, а также приводит к потере данных. Чтобы решить эту проблему, приходится использовать цепь усиления напряжения для повышения уровня напряжения. Известно аппаратное средство (см. патент Кореи N 91-19740, выданный на патентную заявку, которая была подана 07 ноября 1991 года под названием "Цепь усиления напряжения" и принадлежащая настоящему заявителю: документ, озаглавленный "A 35ns 64 Mb DRAM Using - Onship Boosted Power Supply" 1992 Symposium on ULSI Circuits Digest of Technical Paper, pp. 64 - 65; патент США N 4704706, выданный инофирме Japan Fudjitsu Co. и подобные.)

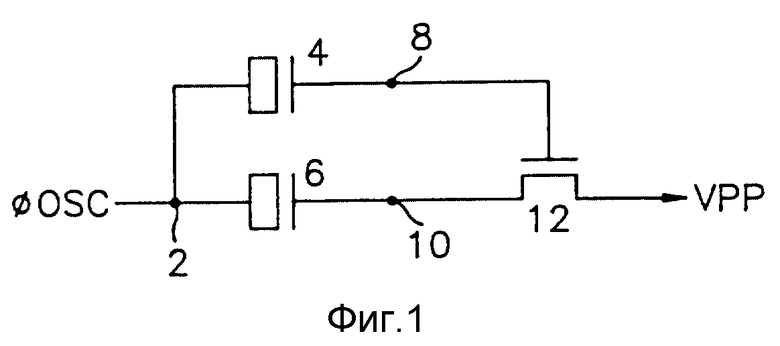

Фиг. 1 схематически показывает типичную часть цепи усиления напряжения, хорошо известной из уровня техники и описанной в вышеуказанных документах. Входная узловая точка электрической схемы 2 принимает осциллирующий сигнал ⊘ OSC, вырабатываемый в генераторе (не показан). Подкачивающий конденсатор 4 одним своим выводом соединен со входной узловой точкой 2, а другим выводом - с подкачивающей узловой точкой 8. Подкачивающий конденсатор одним своим выводом соединен со входной узловой точкой 2, а другим выводом - с подкачивающей узловой точкой 10. Передающий транзистор 12, соединенный затвором и стоком с подкачивающими узловыми точками 8 и 10 соответственно, вырабатывает усиливающее напряжение VPP. Дополнительно предусмотрена не показанная на фиг. 1 цепь предзаряда для предзаряда подкачивающих узловых точек 8 и 10 до уровня питающего напряжения VCC. Конструкция по фиг. 1 известна из уровня техники как цепь подачи заряда. Генератор действует, когда усиливающее напряжение VPP понижено до уровня ниже нормального внутренней цепью в процессе запитки микросхемы и ее активного цикла. Если осциллирующий сигнал ⊘ OSC подается на входную узловую точку 2, подкачивающие конденсаторы 4 и 6 доводят подкачивающие узловые точки 8 и 10 до напряжения, приблизительно равного удвоенному питающему напряжению VCC. Напряжение, поданное на подкачивающую узловую точку 10, передается через канал передающего транзистора 12 в виде усиливающего напряжения VPP. Цепь по фиг. 1 приводится в действие генератором, использующим питающее напряжение VCC как напряжение истока, так что можно достичь уровня усиливающего напряжение VPP, равного 2 VCC-VT (где VT - предельное напряжение передающего транзистора 12). Подкачивающие узловые точки 8 и 10 в начальном состоянии предзаряжены до уровня питающего напряжения VCC.

Цепь усиления напряжения по фиг. 1 формируется при помощи типичного процесса производства КМОП. Цепь по фиг. 1 имеет недостатки, связанные с эффективностью подкачки, состоящие в том, что передающий транзистор 12 является КМОП-транзистором, формируемым в процессе производства КМОП. Как хорошо известно специалистам, МОП-транзистор имеет такие конструктивные характеристики, что эффект подложки увеличивается с увеличением уровня напряжения между его истоком и стоком. Очевидно, что эффект подложки еще более возрастает в случае, если размеры каждого устройства уменьшаются и промежутки между ними становятся более узкими при все возрастающей интеграции полупроводникового запоминающего устройства. Цепь усиления напряжения по фиг. 1 имеет основополагающий недостаток в том, что эффективность подкачки снижается конструктивными характеристикам МОП-транзистора, т.е. передающего транзистора, а не структурой цепи.

Краткое описание изобретения

Объектом изобретения являются цепи усиления напряжения для улучшения эффективности подкачки.

Другим объектом изобретения являются цепи устройства напряжения для выработки усиливающего напряжения с высокой скоростью.

Еще одним объектом изобретения являются цепи усиления напряжения для улучшения эффективности подкачки независимо от появления эффекта подложки, даже если уровень усиливающего напряжения растет.

Дополнительным объектом изобретения являются цепи усиления напряжения для повышения эффективности подкачки при помощи конструктивных характеристик передающего транзистора.

В соответствии с одним из аспектов настоящего изобретения обеспечивается цепь усиления напряжения для выработки усиливающего напряжения посредством передающего транзистора с характеристиками биполярного транзистора. Цепь усиления напряжения содержит передающий транзистор, образованный "трехкарманным" процессом обычного процесса производства КМОП. Передающий транзистор действует как биполярный диод, содержащий парный карман второго типа проводимости, сформированный на подложке первого типа проводимости, второй карман первого типа проводимости, сформированный внутри первого кармана, первый диффузионный слой второго типа проводимости, сформированный внутри первого кармана, но не внутри упомянутого второго кармана, первый диффузионный слой соединен с линией, подключенной к подкачивающему конденсатору; первый диффузионный слой первого типа проводимости, сформированный внутри упомянутого второго кармана и подключенный к упомянутой линии, и второй диффузионный слой второго типа проводимости, сформированный внутри упомянутого второго кармана и подключенный к усиливающему узлу.

Краткое описание чертежей

Для лучшего понимания изобретения и указания того, как оно может быть применено, дается ссылка, - только в качестве примера, - на приложенные схемные чертежи, на которых:

Фиг. 1 является принципиальной схемой, показывающей типичную часть общепринятой цепи усиления напряжения;

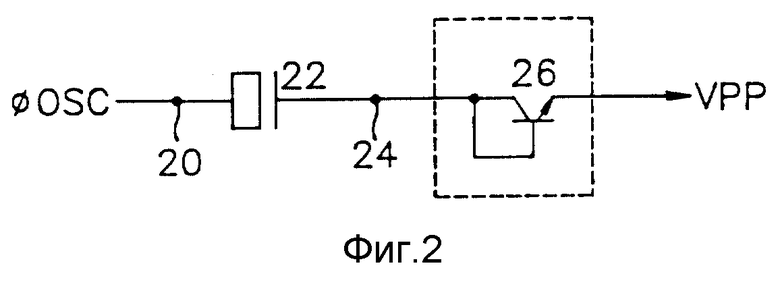

Фиг. 2 является эквивалентной схемой, показывающей схематическое построение цепи усиления напряжения в соответствии с настоящим изобретением;

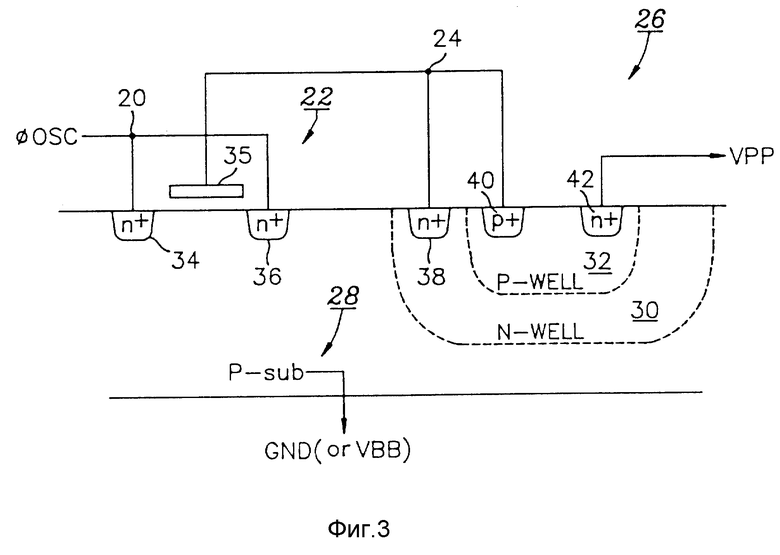

Фиг. 3 - вид в разрезе структурной реализации цепи по фиг. 2;

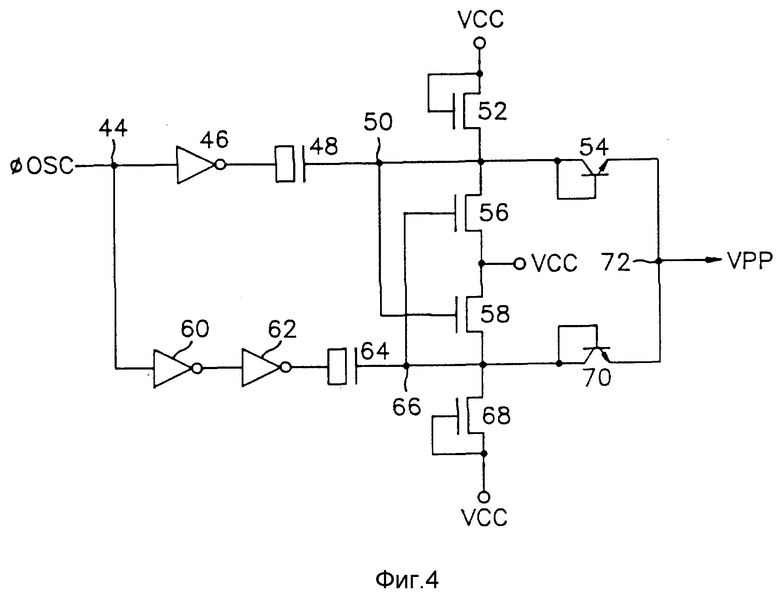

Фиг. 4 является принципиальной схемой, показывающей один из вариантов выполнения цепи усиления напряжения, выполненной в соответствии с фиг. 2 и 3;

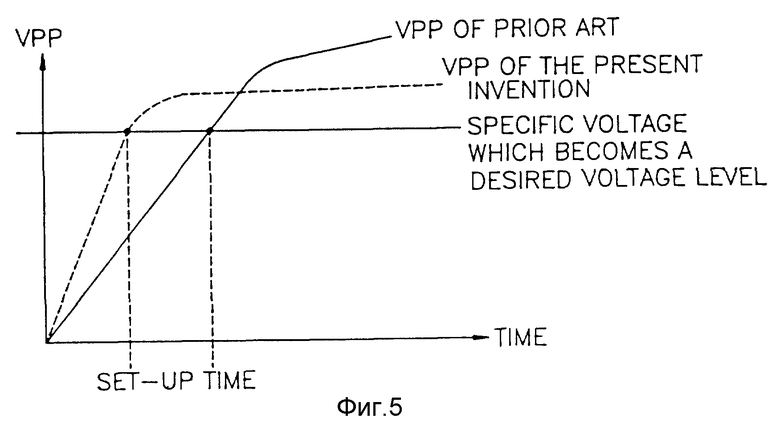

Фиг. 5 является графиком, показывающим кривые возрастания результирующего усиливающего напряжения VPP в цепи по фиг. 4.

Подробное описание предпочтительного варианта выполнения

По фиг. 2 цепь усиления напряжения согласно настоящему изобретению использует биполярный транзистор 26 в качестве передающего транзистора для выработки усиливающего напряжения VPP. Следует отметить, что термин "биполярный транзистор" означает то же самое, что и "биполярный диод" и "биполярный передающий транзистор", применяемые ниже. Как хорошо известно специалистам, биполярный транзистор является устройством, управляемым током, в то время, как МОП-транзистор является устройством, управляемым напряжением. Биполярный транзистор имеет преимущества в том, что увеличивается скорость переключения и возрастает сила возбуждения. Передающий транзистор 26, созданный из биполярного транзистора, в качестве цепи усиления напряжения имеет сложные конструктивные характеристик, и обладает такими преимуществами, как улучшенная эффективность подкачки, высокая скорость усиления до желательного уровня усиления и предотвращение эффекта подложки.

Фиг. 3 является видом в разрезе структурной реализации цепи по фиг. 2. Биполярный транзистор 26 образован трехкарманным процессом обычного процесса производства КМОП. Вкратце процесс изготовления биполярного транзистора 26 в качестве передающего транзистора происходит следующим образом. N-карман 30 формируется на подложке 28 P-типа проводимости. P-карман 32 формируется в средней части N-кармана 30. Внутри N-кармана 30, но вне P-кармана 32 сформирован n+ слой 38 путем внесения n+ примеси, p+ слой 40 и n+ слой 42 сформированы внутри P-кармана 32 путем внесения p+ и n+ примесей соответственно. Таким образом выполняется структура биполярного транзистора 26, показанного на фиг. 2. n+ слои 34 и 36, сформированные путем внесения n+ примеси на подложку 28 P-типа, а также затвор 35 образуют подкачивающий конденсатор 22 фиг. 2. Так как структура по фиг. 3 легко достижима при использовании обычного процесса производства, такие операции, как маскирование, диффузионный процесс и т.д., опущены. n+ слои 34 и 36 соединены со входной узловой точкой 20 и подкачивают сформированный на них затвор 35 в ответ на напряжение на входной узловой 20, тем самым подкачивая подкачивающую узловую точку 24, соединенную с затвором 35. Следует отметить, что подкачивающая узловая точка 24 обычно соединена с n+ слоем 38 внутри N-кармана 30 и с p+ слоем 40 внутри P-кармана 32, подробности чего еще будут обсуждены позже. Линия, к которой приложено усиливающее напряжение VPP, соединена с n+ слоем 42 внутри P-кармана 32. Легко понять, что биполярный транзистор 26 действует через P-карман 32 между подкачивающей узловой точкой 24 и линией усиливающего напряжения VPP. Для подкачки усиливающего напряжения VPP через биполярный транзистор 26 подкачивающая узловая точка 24 должна быть изолирована от подложки 28 P-типа. В противном случае напряжение подкачки, которым заряжена подкачивающая узловая точка 24, разряжается через подложку 28. Специалист поймет необходимость формирования биполярного транзистора внутри N-кармана 30 для предотвращения разрядки подкачивающего напряжения.

Опишем теперь причины, по которым подкачивающая узловая точка 24 обычно соединяется с n+ слоем 28 внутри N-кармана 30 и с p+ слоем 40 внутри P-кармана 32.

Если подкачивающая узловая точка 24 не может подать подкачивающее напряжение на N-карман 30 через n+ слой 38, то есть, если подкачивающая узловая точка 24 подает подкачивающее напряжение только на n+ слой 40 внутри Р-кармана 32, формируется Р-N прямое смещение. Соответственно, высокое напряжение, поданное на P-карман 32, стекает к N-карману 30. Тогда n+ слой 42 P-кармана 32 не подкачивается до желательного уровня. Следовательно, высокое напряжение должно подаваться от N-кармана 30. Для преодоления этой ситуации желательно, чтобы подкачивающая узловая точка 24 была соединена с n+ слоем 38 внутри N-кармана 30. Тем временем, желательно, чтобы подложка 28 P-типа была соединена с напряжением заземления GND или напряжением подложки VBB для предотвращения P-N прямого смещения. Если образован биполярный транзистор 26 с вышеописанной трехкарманной структурой, то изменения тока отсутствуют даже при повышении усиливающего напряжения VPP, тем самым минимизируется время подкачки для подкачивания усиливающего напряжения VPP до желательного высокого напряжения. Из-за этого увеличивается эффективность подкачки и гарантируются рабочие характеристики цепи усиления напряжения.

Фиг. 4 показывает один из вариантов выполнения цепи усиления напряжения, созданной в соответствии с фиг. 2 и 3. Цепь усиления напряжения по фиг. 4 показывает конструкцию цепи подкачки заряда. Цепь усиления напряжения выполняет двойную операцию подачки в ответ на изменение логического уровня запущенного осциллирующего сигнала ⊘ OSC от генератора. Входная узловая точка 44 принимает осциллирующий сигнал ⊘ OSC, выработанный генератором (не показан). Первый инвертор 46 имеет выходной вывод, соединенный со входной узловой точкой 44. Первый подкачивающий конденсатор 48, включенный обоими выводами между первым инвертором 46 и первой подкачивающей узловой точкой 50, подкачивает первую подкачивающую узловую точку 50 в ответ на уровень напряжения выходного сигнала первого инвертора 46. Первый транзистор 52 предзаряда предзаряжает первую подкачивающую узловую точку 50 до уровня напряжения VCC-Vth. Первый биполярный транзистор 54 NPN-транзистора своими базой и коллектором обычно подключен к первой подкачивающей узловой точке 50, а эмиттеры - к усиливающей узловой точке 72 для выработки усиливающего напряжения VPP. Второй инвертор 60 своим входом подключен ко входной узловой точке 44, а третий инвертор 62 входом подключен к выходу второго инвертора 60. Второй подкачивающий конденсатор 64, обоими выводами подключенный между третьим инвертором 62 и второй подкачивающей узловой точкой 66, подкачивает вторую подкачивающую узловую точку 66 в ответ на уровень напряжения выходного сигнала третьего инвертора 62. Второй транзистор 68 подзаряда предзаряжает вторую подкачивающую узловую точку 66 до уровня напряжения VCC-Vtn. Второй биполярный транзистор 70 NPN-транзистора своими базой и коллектором обычно подключен ко второй подкачивающей узловой точке 66, а эмиттером - к усиливающей узловой точке 72. Третий транзистор 56 предзаряда с каналом, подключенным между выводом питающего напряжения VCC и первой подкачивающей узловой точкой 50, и с затвором, подключенным ко второй подкачивающей узловой точке 66, предзаряжает первую подкачивающую узловую точку 50 до уровня питающего напряжения VCC. Четвертый транзистор 58 предзаряда с каналом, подключенным между второй подкачивающей узловой точкой 66 и выводом питающего напряжения VCC, и с затвором, подключенным к первой подкачивающей узловой точке 50, предзаряжает вторую подкачивающую узловую точку 66 до уровня питающего напряжения VCC. Структура по фиг. 4 имеет ту особенность, что цепь подкачки заряда использует биполярный транзистор в качестве передающего транзистора.

Далее обсуждается работа цепи по фиг. 4. После запитки микросхемы, когда цепь усиления напряжения по фиг. 4 находится в запертом состоянии посредством поддержания усиливающего напряжения VPP на желательном уровне или перед тем, как включена микросхема, подкачивающие узловые точки 50 и 66 предзаряжены до уровня напряжения VCC-Vtn при помощи операции предзаряда первого и второго транзисторов 52, 68 предзаряда, где Vtn - предельное напряжение транзисторов 52, 68 предзаряда NМОП-транзистора. Затем, если включена микросхема либо усиливающее напряжение VPP снижено до уровня ниже желательного, включается цепь усиления напряжения по фиг. 4. Тогда осциллирующий сигнал ⊘ OSC прикладывается ко входной узловой точке 44 в виде сигнала прямоугольной формы с постоянным периодом. Далее следует подробное описание.

Сначала, если осциллирующий сигнал ⊘ OSC, подаваемый на входную узловую точку 44, повышается от логически "низкого" до логически "высокого" уровня, первый инвертор 46 вырабатывает логически "низкий" уровень. Через первый подкачивающий конденсатор 48 не идет никакой подкачки и первая подкачивающая узловая точка 50 сохраняет свой уровень предзаряда. Второй и третий инверторы 60 и 62 вырабатывают логически "низкий" и "высокий" уровни соответственно. Второй подкачивающий конденсатор 64 усиливает вторую подкачивающую узловую точку 66 до уровня напряжения, вдвое большего, чем VCC - Vtn. Усиленный уровень напряжения второй подкачивающей узловой точки 66 передается через второй биполярный транзистор 70 к усиливающей узловой точке 72 для увеличения усиливающего напряжения VPP. Второй биполярный транзистор 70 является устройством со структурой по фиг. 3. В процессе операции разделения заряда второй подкачивающей узловой точки 66 и усиливающей узловой точки 72 через второй биполярный транзистор 70, второй биполярный транзистор 70 имеет конструктивные характеристики, указанные в описании к фиг. 3. Таким образом, высокое напряжение, заряженное в подкачивающую узловую точку 66, передается усиливающей узловой точке 72 на высокой скорости, и эффект подложки не имеет места, даже хотя усиливающая узловая точка 72 переходит на высокий уровень напряжения. Эмиттер первого или второго биполярного транзистора 54 или 70 на фиг. 4 соответствует n+ слою 42 внутри P-кармана 32 фиг. 3, базой которого является p+ слой 40 внутри P-кармана 32 фиг. 3, а коллектором - n+ слой 38 внутри N-кармана 30 фиг. 3. Следовательно, легко понять, что эффект подложки не обнаруживается, даже хотя усиливающая узловая точка 72 доходит до высокого напряжения. Уровень напряжения 2 (VCC-Vtn), подкачанный на второй подкачивающей узловой точке 66, полностью включает канал третьего транзистора 56 предзаряда для предзаряда первой подкачивающей узловой точки 50 до уровня питающего напряжения VCC.

Затем, если осциллирующий сигнал ⊘ OSC, приложенный ко входной узловой точке 44, понижается с логически "высокого" до логически "низкого" уровня, первый инвертор 46 вырабатывает логически "высокий" уровень. Первый подкачивающий конденсатор 48 подкачивает первую подкачивающую узловую точку 60 с предыдущего уровня предзаряда VCC (этот уровень достигается при помощи третьего транзистора 56 предзаряда посредством вышеописанного процесса) до уровня, вдвое большего, чем VCC. Уровень усиленного напряжения подкачивающей узловой точкой 50 передается усиливающей узловой точке 72 через первый биполярный транзистор 54 для увеличения усиливающего напряжения VPP до уровня более высокого, чем предыдущий уровень усиливающего напряжения. Первый биполярный транзистор 54 также сформирован в виде структуры по фиг. 3, а конструктивные характеристики, описанные со ссылкой на фиг. 3, поддерживаются в процессе операции разделения заряда второй подкачивающей узловой точки 50 и усиливающей узловой точки 72 через первый биполярный транзистор 54. Поэтому высокое напряжение, заряженное в подкачивающую узловую точку 30, передается в усиливающую узловую точку 72 на высокой скорости, и предотвращается эффект подложки, вызванный повышенным напряжением усиливающей узловой точки 72. С другой стороны, второй и третий инверторы 60 и 62 вырабатывают логически "высокий" и "низкий" уровни соответственно. Через второй подкачивающий конденсатор 64 не проходит никаких подкачивающих операций второй подкачивающей узловой точки 66. Уровень напряжения 2 VCC, подкачанный в первую подкачивающую узловую точку 50, полностью включает канал четвертого транзистора 58 предзаряда для предзаряда второй подкачивающей узловой точки 66 до уровня питающего напряжения VCC. Следовательно, эффективность следующей операции подкачки повышается.

Если осциллирующий сигнал ⊘ OSC опять переходит с логически "низкого" уровня на "высокий", вышеописанный первый процесс повторяется. Уровнем предзаряда первой подкачивающей узловой точки 50 становится уровень питающего напряжения VCC, и затем происходит операция подкачки. Процессы повторяются, пока усиливающее напряжение VPP не будет поднято до желательного уровня усиливающего напряжения, и при помощи этих процессов усиливающее напряжение VPP поднимается до заданного уровня.

Фиг. 5 показывает кривую нарастания усиливающего напряжения VPP, вытекающую из рабочих характеристик фиг. 4. Как показано, предложенная в изобретении цепь усиления напряжения имеет более короткое время установки для возрастания усиливающего напряжения VPP до желательного уровня усиливающего напряжения (порядка двойного питающего напряжения VCC), чем общепринятая цепь. Очевидно, что эти характеристики могут быть достигнуты при помощи первого и второго биполярных транзисторов 54 и 70 по фиг. 4, построенных в соответствии со структурой по фиг. 3.

Как описано выше, предложенная в настоящем изобретении цепь усиления напряжения поднимает усиливающее напряжения VPP до желательного уровня усиливающего напряжения при помощи цепи подкачки заряда, содержащей биполярный транзистор. Даже если усиливающее напряжение VPP на усиливающей узловой точке повышается, эффективность усиления увеличивается, так как не изменяется ток, текущий в усиливающую узловую точку. Кроме того, предотвращается эффект подложки, который увеличивается пропорционально поднятому усиливающему напряжению в обычной цепи усиления напряжения.

Предыдущее описание показывает лишь предпочтительный вариант выполнения настоящего изобретения. Различные модификации очевидны для специалистов без выхода за объем настоящего изобретения.

Цепь усиления напряжения для усиления питающего напряжения VСС, подаваемого из системы, до желательного уровня усиливающего напряжения VРР. Цепь усиления напряжения содержит передающий транзистор, сформированный путем трехкарманного процесса изготовления. Передающий транзистор имеет биполярные характеристики и действует как биполярный диод. Технический результат: увеличивается эффективность усиления, т.к. не изменяется ток, текущий в усиливающую узловую точку, даже если усиливающее напряжение в этой точке повышается. 3 з.п.ф-лы, 5 ил.

| US 4691304 A, 01.09.87 | |||

| US 4704706 A, 03.11.87 | |||

| US 4697252 A, 29.09.87 | |||

| Букреев И.Н | |||

| и др | |||

| Микроэлектронные схемы цифровых устройств | |||

| - М.: Радио и связь, 1990, с.57 - 62. |

Авторы

Даты

1999-09-20—Публикация

1994-11-16—Подача