Изобретение относится к электросвязи и может быть использовано для кадровой синхронизации приемников в системах передачи цифровой информации.

Последние годы характеризуются переводом значительной части спутниковых линий связи на цифровые методы передачи информации с временным уплотнением каналов и повышением тактовой частоты информационных потоков.

В настоящее время вновь вводимые линии связи упомянутого типа имеют скорость обработки информации более 120 мбит/с.

Поскольку устройства выделения маркера кадровой синхронизации работают на частоте входного информационного потока, то это обусловило включение требований к их быстродействию в число основных параметров этого класса устройств.

Создание же устройств выделения маркера кадровой синхронизации, удовлетворяющих современным требованиям по быстродействию при использовании известных способов их построения, - задача довольно трудоемкая.

Известен способ выделения маркера кадровой синхронизации, заключающийся в том, что входной сигнал с кодово-импульсной модуляцией, представляющий последовательность двоичных символов, преобразуют из последовательного кода в параллельный и сравнивают его с эталонной комбинацией маркера, определяют текущий код совпадения, соответствующий числу символов входного сигнала, совпавших с символами эталонной комбинации маркера, после чего определяют временное положение максимального кода совпадения.

Недостатком этого способа является то, что он предлагает использование суммирующего и анализирующего устройств, различающих все возможные состояния результатов сравнения анализируемого фрагмента входной последовательности и эталона маркера, количество которых равно количеству двоичных символов в маркере кадровой синхронизации, что накладывает существенные ограничения на быстродействие устройств, реализующих этот способ.

Наиболее близким к предлагаемому является известный способ выделения маркера кадровой синхронизации, который взят за прототип.

Этот способ заключается в том, что входной сигнал, представляющий собой последовательную комбинацию двоичных символов, преобразуют из последовательного кода в параллельный, сравнивают его с эталонной комбинацией маркера, формируют текущий код числа символов входного сигнала, совпавших с символами эталонной комбинации маркера. На протяжении первого временного интервала анализа определяют максимальный код совпадения, соответствующий максимальному числу символов входного сигнала, совпавших с символами эталонной комбинации маркера и запоминают временную позицию максимального кода совпадения. На протяжении последующих временных интервалов анализа производят сравнение максимального кода совпадения с текущим кодом числа символов, совпавших с символами маркера. При превышении текущего кода числа символов входного сигнала, совпавших с символами эталонной комбинации маркера, ранее определенного максимального кода совпадения, в качестве нового максимального кода совпадения запоминают текущий код числа символов, совпавших с символами маркера, а также запоминают его временную позицию, производят сравнение временных позиций максимального кода совпадения и при совпадении этих временных позиций подряд для заданного числа тактов формируют кадровый синхроимпульс.

Недостатком прототипа является наличие таких операций, как вычисление кодов совпадения, сравнение их с ранее вычисленными кодами совпадения, их запись и перезапись в памяти с тактовой частотой входной информации. Необходимость реализации этих операций существенно снижает потенциальные возможности по быстродействию устройств, реализующих этот способ. Вообще реализация этого способа предполагает использование широкой номенклатуры функционально разнородных элементов, добиться от которых высокого совокупного быстродействия задача сама по себе достаточно сложная. Способ, взятый за прототип, основывается на определении количества символов анализируемого фрагмента входной информационной последовательности, совпадающих с соответствующими символами эталона маркера. Количество совпавших символов может находиться в пределах 0 - F, где F - количество символов эталона маркера. Следовательно, реализующее этот способ устройство предполагает использование суммирующего и анализирующего устройств различающих (F + 1) возможных состояний результатов сравнения фрагмента входной информационной последовательности и эталона маркера. Как правило, F находится в пределах 20 - 50, поэтому суммирующие и анализирующие устройства накладывают дополнительные ограничения на скоростные качества устройств, реализующих способ, взятый за прототип.

Целью изобретения было повышение быстродействия выделения маркера кадровой синхронизации путем создания такого способа выделения маркера кадровой синхронизации, который в самой своей сущности содержал бы предпосылки модульности и регулярности структуры построения устройств, реализующих этот способ, при относительной простоте и номенклатурной ограниченности модулей, реализующих операции этого способа.

Для достижения указанной цели предлагается способ, заключающийся в том, что входной сигнал, представляющий собой последовательную комбинацию двоичных символов, преобразуют из последовательного кода в параллельный и сравнивают его с эталонной комбинацией маркера.

Согласно изобретению на основании вышеупомянутого сравнения формируют текущий код количества символов фрагмента входной информационной последовательности, не совпадающих с символами эталонной комбинации маркера, причем при любой длине и конфигурации маркера на первой ступени анализа маркер рассматривают как совокупность примыкающих друг к другу кодовых групп из K двоичных символов, где K - максимально допустимое количество пораженных символов маркера. Внутри каждой их выделенных групп, независимо от других групп, определяют количество символов фрагмента анализируемой входной последовательности, отличающихся от соответствующих символов эталона маркера, причем результат операции представляют в виде кодового слова длиной в (K + 1) бит, за каждой позицией которого закрепляется функция регистрации своего, отличного от других, количества символов из множества { 0, 1, 2, ..., K}, не совпадающих с соответствующими символами эталона маркера, поэтому в любой момент времени в K позициях этого кодового слова значения логических переменных равны между собой и противоположны значению логической переменной в одной из (K + 1) позиции. На второй ступени анализа кодовые слова, полученные по первой ступени анализа, разбивают на смежные пары. По информации, содержащейся в каждой паре этих слов, для каждого анализируемого фрагмента входного потока длиной в 2K бит определяют суммарное количество символов, отличающихся от соответствующих символов эталона маркера, при этом форма представления результата операции над отдельной смежной парой кодовых слов на второй ступени анализа в точности совпадает с формой представления результатов операции над отдельной кодовой группой на первой ступени анализа. Если количество символов в анализируемом фрагменте входного потока, не совпадающих с соответствующими символами эталона маркера, превышает допустимое - K, то во всех (K + 1) позициях кодового слова, полученного в результате второй ступени анализа, значения логических переменных равны между собой и совпадают со значениями K логических переменных любого из кодовых слов, полученных в результате первой ступени анализа. На третьей ступени анализа кодовые слова, полученные на второй ступени анализа, разбивают на смежные пары и повторяют последовательность операций, описанную для второй ступени анализа. Каждая последующая ступень анализа по сравнению с предыдущей содержит вдвое меньшее количество кодовых слов результата операции, поэтому через несколько однотипных ступеней анализа результаты операции всей последней ступени анализа будут сосредоточены в одном кодовом слове, причем равенство значений логических переменных во всех (K + 1) разрядах этого кодового слова указывает на отсутствие маркера, а равенство логических переменных в K разрядах и наличие в одном из (K + 1) разрядов этого слова логической переменной противоположного значения указывает на наличие маркера кадровой синхронизации в текущий момент времени.

В качестве одного из возможных вариантов осуществления рассматриваемого способа выделения маркера кадровой синхронизации предлагается устройство, содержащее регистр сдвига.

Согласно изобретению этот регистр сдвига выполнен в виде последовательно соединенных пар Д-триггеров, входящих в N элементов первой ступени анализа, причем вход регистровой пары триггеров первого элемента является информационным входом устройства, а выход этой регистровой пары триггеров соединен со входом регистровой пары триггеров второго элемента, выход же регистровой пары триггеров N-го элемента является информационным выходом устройства. Каждый из N элементов первой ступени анализа имеет по два входа установки кодовой комбинации эталона маркера, по два входа настройки на длину маркера и по три одноразрядных выхода результатов сравнения символов фрагментов анализируемой входной информационной последовательности и соответствующих символов эталона маркера. Выходы первого и второго элементов первой ступени анализа подключены к входам первого элемента второй ступени анализа, а выходы третьего и четвертого элементов первой ступени анализа подключены к входам элемента второй ступени анализа, выходы же (N-1)-го и N-го элементов первой ступени анализа подключены к входам M-го элемента второй ступени анализа. Каждый из M элементов второй ступени анализа имеет по три одноразрядных выхода, причем выходы первого и второго элементов второй ступени анализа подключены к входам первого элемента третьей ступени анализа, а выходы (M-1)-го и M-го элементов второй ступени анализа подключены к р-му элементу третьей ступени анализа. Каждый из двух элементов (K-1)-й ступени анализа имеет по шесть одноразрядных входов, подключенных к выходам (K-2)-й ступени анализа и по три одноразрядных выхода, которые подключены к входам единственного элемента K-й ступени анализа. Три одноразрядных выхода элемента K-й ступени анализа присоединены к первым входам оконечного анализирующего элемента, вторые входы которого являются входами установки допустимого количества ошибок в сигнале кадровой синхронизации, а выход служит выходом регистрации маркера кадровой синхронизации - выходом кадрового синхроимпульса.

Все элементы первой ступени анализа выполнены по одной и той же электрической функциональной схеме и содержат четыре триггера, три элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и два элемента И. Д-вход первого триггера является информационным входом элемента первой ступени анализа, а выход первого триггера соединен с Д-входом второго триггера и с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Выход второго триггера является информационным выходом элемента первой ступени анализа и соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Вторые входы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ являются входами установки эталонной кодовой комбинации - фрагмента маркера кадровой синхронизации. Выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с Д-входом третьего триггера, прямой выход которого подключен к первым входам первого элемента И и третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с Д-входом четвертого триггера, прямой выход которого подключен ко вторым входам первого элемента И и третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. R-входы третьего и четвертого триггеров являются входами настройки на длину маркера, а инверсные выходы этих триггеров присоединены к входам второго элемента И, выход которого является выходом регистрации совпадения двухбитного фрагмента анализируемой информационной последовательности с соответствующими символами эталона маркера - "Выход 0". Выход первого элемента И является выходом регистрации несовпадения обоих бит двухбитового фрагмента анализируемой информационной последовательности с соответствующими символами эталона маркера - "Выход 2". Выход третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является выходом регистрации несовпадения одного из двух бит анализируемого фрагмента информационной последовательности с соответствующими символами эталона маркера - "Выход 1".

Все элементы со второй по K-ю ступень анализа выполнены по одной и той же электрической функциональной схеме и содержат шесть элементов И, шесть триггеров и три элемента ИЛИ. "Вход 0", подключенный к первому элементу анализа, соединен с первыми входами первого, второго и третьего элементов И. Выход первого элемента И подключен к Д-входу первого триггера, выход которого присоединен к входу первого элемента ИЛИ, выход которого является "Выходом 0" рассматриваемого элемента анализа. "Вход 1", подключенный к первому элементу анализа, соединен с первыми входами четвертого и пятого элементов И. Выход пятого элемента И подключен к Д-входу второго триггера, выход которого присоединен к первому входу второго элемента ИЛИ. "Вход 2", подключенный к первому элементу анализа, соединен с первым входом шестого элемента И, выход которого подключен к Д-входу третьего триггера, выход которого присоединен ко второму входу второго элемента ИЛИ. "Вход 0", подключенный ко второму элементу анализа, соединен со вторыми входами первого, четвертого и шестого элементов И. Выход четвертого элемента И подключен к Д-входу четвертого триггера, выход которого присоединен к первому входу третьего элемента ИЛИ. "Вход 1", подключенный ко второму элементу анализа, соединен со вторыми входами второго и пятого элементов И. Выход второго элемента И подключен к Д-входу пятого триггера, выход которого присоединен ко второму входу третьего элемента ИЛИ, выход которого является "Выходом 1" рассматриваемого элемента анализа. "Вход 2", подключенный ко второму элементу анализа, соединен со вторым входом третьего элемента И, выход которого подключен к Д-входу шестого триггера, выход которого присоединен к третьему входу второго элемента ИЛИ, выход которого является "Выходом 2" рассматриваемого элемента анализа.

Элемент (K + 1)-й ступени анализа содержит три элемента И, три триггера и один элемент ИЛИ. Первые входы элементов И являются входами установки допустимого количества ошибок в сигнале кадровой сигнализации. "Вход 0" подключен ко второму входу первого элемента И, выход которого соединен с Д-входом первого триггера, выход которого присоединен к первому входу элемента ИЛИ. "Вход 1" подключен ко второму входу второго элемента И, выход которого соединен с Д-входом второго триггера, выход которого присоединен ко второму входу элемента ИЛИ. "Выход 4" подключен ко второму входу третьего элемента И, выход которого соединен с Д-входом третьего триггера, выход которого присоединен к третьему входу элемента ИЛИ, выход которого является выходом регистрации маркера кадровой синхронизации - выходом кадрового синхроимпульса.

Предлагаемый способ выделения маркера кадровой синхронизации предопределяет модульность и регулярность структуры построения реализующего его устройства. Простота операций на всех ступенях анализа в данном способе позволяет создавать чрезвычайно простые высокоскоростные структурные модули устройства выделения маркера кадровой синхронизации. Упрощение и повышение скоростных качеств суммирующих и анализирующих устройств, входящих в устройства, реализующие предлагаемый способ, по сравнению с прототипом предопределены самой сущностью предлагаемого способа. Действительно, суммирующие и анализирующие устройства способа-прототипа должны различать (F + 1) возможных состояний результатов сравнения фрагмента входной информационной последовательности и эталона маркера (F - количество символов эталона маркера), а суммирующие и анализирующие устройства предлагаемого способа должны различать K + 2 возможных состояний результатов сравнения фрагмента входной информационной последовательности и эталона маркера (K - допустимое количество ошибок в сигнале кадровой сигнализации). Поскольку во всех представляющих практический интерес случаях K существенно меньше F, то это и предопределяет возможное упрощение и увеличение быстродействия суммирующих и анализирующих устройств предлагаемого способа по сравнению с прототипом. Отличительной чертой предлагаемого устройства, реализующего рассматриваемый способ, является то, что увеличение числа символов маркера кадровой синхронизации приводит к увеличению потребного числа модулей устройства, но не влияет на его быстродействие. Особенностью этого устройства является возможность его оперативной перенастройки на различные конфигурации маркера и возможность оперативного изменения допустимого количества ошибок в сигнале кадровой синхронизации при его опознавании.

Сочетание отличительных признаков, а также свойства предлагаемого способа выделения маркера кадровой синхронизации и устройства для его осуществления в литературе не описаны, поэтому они соответствуют критериям "новизнa" и "изобретательский уровень".

На фиг. 1 приведенa функциональная схема предлагаемого устройства выделения маркера кадровой синхронизации.

На фиг. 2 приведена функциональная схема элемента первой ступени анализа предлагаемого устройства.

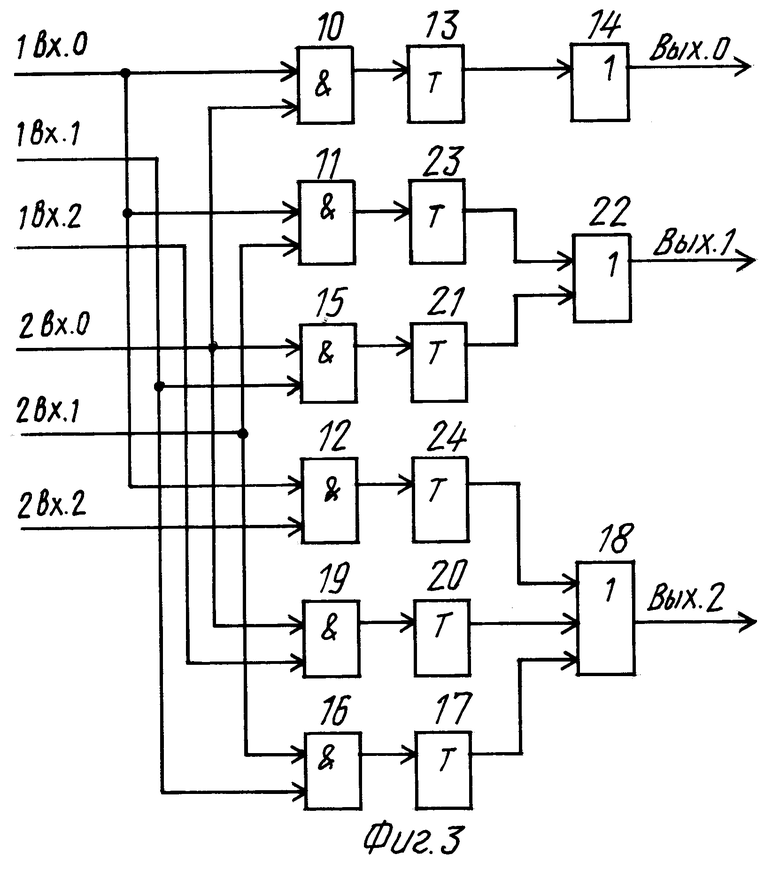

На фиг. 3 приведена функциональная схема элемента второй ступени анализа предлагаемого устройства.

На фиг. 4 приведена функциональная схема элемента оконечной ступени анализа предлагаемого устройства.

По предлагаемому способу осуществляют следующие операции.

1. Входной сигнал с кодово-импульсной модуляцией, представляющий собой последовательную комбинацию двоичных символов, преобразуют из последовательного кода в параллельный.

2. Aнализируемый фрагмент входного сигнала разбивают на K-символьные группы, где K - максимально допустимое количество пораженных символов маркера.

3. Для каждой из выделенных K-элементных групп, независимо от других групп, определяют количество символов фрагмента анализируемой входной последовательности, отличающихся от соответствующих символов эталона маркера, причем результат операции представляют в виде кодового слова длиной в (K + 1) бит, за каждой позицией которого закрепляется функция регистрации своего, отличного от других, количества несовпадающих символов из множества {0, 1, 2,..., K}.

4. Полученные в результате операции 3 кодовые слова разбивают на смежные пары и по информации, содержащейся в каждой паре этих слов, для каждого анализируемого фрагмента входного сигнала длиной в 2 K бит определяют суммарное количество символов, отличающихся от соответствующих символов эталона маркера, при этом форма представления результата операции над отдельной смежной парой кодовых слов в точности совпадает с формой представления результата операции 3, причем, если количество символов в анализируемом фрагменте входного сигнала, не совпадающих с соответствующими символами эталона маркера, превышает допустимое K, то во всех (K + 1) позициях кодового слова, полученного в результате операции 4, устанавливают равные между собой значения логических переменных.

5. Полученные в результате операции 4 кодовые слова разбивают на смежные пары и повторяют все действия, описанные в операции 4.

6. Oперацию 5 повторяют до тех пор, пока весь результат операции не окажется сосредоточенным в одном кодовом слове длиной в (K+1) бит.

7. По полученному в результате операции 6 кодовому слову производят опознавание маркера кадровой синхронизации, причем в случае равенства логических переменных в K разрядах и наличии в одном из (K + 1) разрядов этого слова логической переменной противоположного значения формируется кадровый синхроимпульс, а в случае равенства значений логических переменных во всех (K + 1) разрядах этого слова кадровый синхроимпульс не формируется.

Устройство для реализации предлагаемого способа содержит (фиг. 1) N элементов первой ступени анализа 1.1, 1.2, ... 1.N, каждый из которых содержит последовательно соединенную пару Д-триггеров, причем вход регистров пары триггеров элемента 1.1 является информационным входом устройства, а выход этой регистровой пары триггеров соединен с входом регистровой пары триггеров элемента 1.2, при этом вход регистровой пары триггеров элемента 1. (N-1) соединен с входом регистровой пары триггеров элемента 1.N, выход же регистровой пары триггеров элемента 1. N является информационным выходом устройства. Каждый из N элементов первой ступени анализа имеет по два входа установки кодовой комбинации эталона маркера, по два входа настройки на длину маркера и по три одноразрядных выхода результатов сравнения символов фрагментов анализируемой входной информационной последовательности и соответствующих символов эталона маркера. Одноразрядные выходы первой ступени анализа подключены к входам элементов 2.1, 2.2, ..., 2М второй ступени анализа, причем выходы элементов 1.1 и 1.2 подключены к входам элемента 2.1, а выходы элементов 1.3 и 1.4 подключены к входам элементов 2.2, выходы же элементов 1. (N-1) и 1. N подключены к входам элемента 2.М. Одноразрядные выходы второй ступени анализа подключены к входам элементов 3.1, 3.2,..., 3. P третьей ступени анализа, причем выходы элементов 2.1 и 2.2 подключены к входам элемента 3.1, а выходы элементов 2.(M-1) и 2.M подключены к входам элемента 3. P. (K-1)-я ступень анализа состоит из двух элементов: (K-1).1 и (K-1). 2, одноразрядные выходы которых подключены к входам единственного элемента K-й ступени анализа. Три одноразрядных выхода элемента K-й ступени анализа присоединены к первым входам оконечного анализирующего элемента (K + 1), вторые входы которого являются входами установки допустимого количества ошибок в сигнал кадровой синхронизации, а выход служит выходом регистрации маркера кадровой синхронизации - выходом кадрового синхроимпульса.

Все элементы первой ступени анализа выполнены по одной и той же электрической функциональной схеме и содержат (фиг. 2) четыре триггера, три элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и два элемента И. Д-вход триггера 1 является информационным входом элемента первой ступени анализа, а выход триггера 1 соединен с Д-входом триггера 2 и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3. Выход триггера 2 является информационным выходом элемента первой ступени анализа и соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4. Вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3 и 4 являются входами установки эталонной кодовой комбинации - фрагмента маркера кадровой синхронизации. Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 соединен с Д-входом триггера 5, прямой выход которого подключен к первым входам элемента И 6 и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7. Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 соединен с Д-входом триггера 8, прямой выход которого подключен ко вторым входам элемента И 6 и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7. P-входы триггеров 5 и 8 являются входами настройки на длину маркера, а инверсные выходы этих триггеров присоединены к входам элемента И 9, выход которого является выходом регистрации совпадения двухбитового фрагмента анализируемой информационной последовательности с соответствующими символами эталона маркера - "Выход 0". Выход элемента И 6 является выходом регистрации несовпадения обоих бит двухбитового фрагмента анализируемой информационной последовательности с соответствующими символами эталона маркера - "Выход 2". Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 является выходом регистрации несовпадения одного из двух бит анализируемого фрагмента информационной последовательности с соответствующими символами эталона маркера - "Выход 1".

Все элементы со второй по K-ю ступень анализа выполнены по одной и той же электрической функциональной схеме и содержат (фиг. 3) шесть элементов И, шесть триггеров и три элемента ИЛИ. "Вход 0", подключенный к первому элементу анализа, соединен с первыми входами трех элементов И: 10, 11, 12. Выход элемента И 10 подключен к Д-входу триггера 13, выход которого присоединен к входу элемента ИЛИ 14, выход которого является "Выходом 0" рассматриваемого элемента анализа, "Выход 1", подключенный к первому элементу анализа, соединен с первыми входами элементов И 15, 16. Выход элемента И 16 подключен к Д-входу триггера 17, выход которого присоединен к первому входу элемента ИЛИ 18. "Вход 2", подключенный к первому элементу анализа, соединен с первым входом элемента И 19, выход которого подключен к Д-входу триггера 20, выход которого присоединен ко второму входу элемента ИЛИ 18. "Вход 0", подключенный ко второму элементу анализа, соединен со вторыми входами трех элементов И: 10, 15, 19. Выход элемента И 15 подключен к Д-входу триггера 21, выход которого присоединен к первому входу элемента ИЛИ 22. "Вход 1", подключенный ко второму элементу анализа, соединен со вторыми входами элементов И 11, 16. Выход элемента И 11 подключен к Д-входу триггера 23, выход которого присоединен ко второму входу элемента ИЛИ 22, выход которого является "Выходом 1" рассматриваемого элемента анализа. "Вход 2", подключенный ко второму элементу анализа, соединен со вторым входом элемента И 12, выход которого подключен к Д-входу триггера 24, выход которого присоединен к третьему входу элемента ИЛИ 18, выход которого является "Выходом 2" рассматриваемого элемента анализа.

Элемент (K + 1)-й ступени анализа (фиг. 4) содержит три элемента И, три триггера и один элемент ИЛИ. Первые входы элементов И являются входами установки допустимого количества ошибок в сигнале кадровой синхронизации. "Вход 0" подключен ко второму входу элемента И 25, выход которого соединен с Д-входом триггера 26, выход которого присоединен к первому входу элемента ИЛИ 27. "Вход 1" подключен ко второму входу элемента И 28, выход которого соединен с Д-входом триггера 29, выход которого присоединен ко второму входу элемента ИЛИ 27. "Вход 2" подключен ко второму входу элемента И 30, выход которого соединен с Д-входом триггера 31, выход которого присоединен к третьему входу элемента ИЛИ 27, выход которого является выходом регистрации маркера кадровой синхронизации - выходом кадрового синхроимпульса.

Рассмотрение работы устройства выделения маркера кадровой синхронизации проведем в следующей последовательности:

- работа элемента первой ступени анализа;

- работа элемента второй ступени анализа;

- работа элемента (K + 1)-й ступени анализа;

- взаимодействие элементов анализа устройства выделения маркера кадровой синхронизации.

Для рассмотрения работы элемента первой ступени анализа воспользуемся фиг. 2.

На Д-вход триггера 1 подается информационная последовательность, в результате чего в течение каждого такта на первых входах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3, 4 фиксируется очередной фрагмент входной последовательности из двух бит. На вторых входах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3, 4 постоянно присутствуют потенциалы, соответствующие двухбитовому фрагменту эталонной кодовой комбинации маркера. При одновременном совпадении потенциалов на первых и вторых входах обоих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3, 4 на инверсных выходах триггеров 5 и 8 будут зафиксированы логические единицы и на выходе элемента И 9 - "Выход 0" в течение такта будет удерживаться логическая единица, одновременно с которой на выходах элементов 6, 7 ("Выход 1", "Выход 2") будут логические нули. При одновременном несовпадении потенциалов на первых и вторых входах обоих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3, 4 на прямых выходах триггеров 5 и 8 будут зафиксированы логические единицы и на выходе элемента И 6 - "Выход 2" в течение такта будет удерживаться логическая единица, одновременно с которой на входах элементов 7, 9 ("Выход 0", "Выход 1") будут логические нули. При совпадении потенциалов на первых и вторых входах одного из элементов и несовпадении потенциалов на входах другого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3, 4 на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 - "Выход 1" в течение такта будет удерживаться логическая единица, одновременно с которой на выходах элементов И 6, 9 ("Выход 0", "Выход 2") будут логические нули. Если на R-вход триггера 5 подан запирающий потенциал, то на выходе элемента И 6 - "Выход 2" будет зафиксирован логический нуль, и рассматриваемый элемент первой ступени анализа окажется переведенным в режим анализа однобитового фрагмента входной информационной последовательности. Если запирающие потенциалы поданы на R-входы обоих триггеров 5, 8, то на выходах элементов 6, 7 ("Выход 1", "Выход 2) будут зафиксированы логические нули, а на выходе элемента И 9 ("Выход 0") будет зафиксирована логическая единица, и рассматриваемый элемент первой ступени анализа будет исключен из процесса анализа входной информационной последовательности. То есть независимо от режима работы элемента первой ступени анализа в любой момент времени на одном из выходов ("Вых 0", "Вых 1", "Вых 2") будет присутствовать логическая единица, а на двух других выходах логический нуль.

Для рассмотрения работы элемента второй ступени анализа воспользуемся фиг. 3.

На входы "1 Вх 0", "1 Вх 1", "1 Вх 2" поступают сигналы от соответствующих выходов первого элемента первой ступени анализа, на входы "2 Вх 0", "2 Вх 1", "2 Вх 2" поступают сигналы от соответствующих выходов второго элемента первой ступени анализа. При одновременном появлении на входах "1 Вх 0" и "2 Вх 0" логической единицы, на выходе элемента И 10 установится логическая единица, которая и поступит на Д-вход триггера 13. При этом на выходе элемента ИЛИ 14 ("Вых 0") в течение такта будет удерживаться логическая единица, что будет свидетельствовать об отсутствии отличий двух смежных фрагментов анализируемой последовательности и соответствующих фрагментов эталона маркера. При одновременном появлении на входах "1 Вх 0" и "2 Вх 1" логической единицы, на выходе элемента И 11 установится логическая единица, которая и поступит на Д-вход триггера 23. При этом на выходе элемента ИЛИ 22 ("Вых 1") в течение такта будет удерживаться логическая единица. Точно к такому же результату приведет одновременное появление логической единицы на входах "1 Вх 1" и "2 Вх 0". Последнее будет свидетельствовать об отличии в одном бите двух смежных фрагментов анализируемой последовательности и соответствующих фрагментов эталона маркера. При одновременном появлении на входах "1 Вх 0" и "2 Вх 2" логической единицы на выходе элемента И 12 установится логическая единица, которая и поступит на Д-вход триггера 24. При этом на выходе элемента ИЛИ 18 ("Вых 2") в течение такта будет удерживаться логическая единица. Точно к такому же результату приведет одновременное появление логической единицы на входах "1 Вх 2" и "2 Вх 0" или на входах "1 Вх 1" и "2 Вх 1". Последнее будет свидетельствовать об отличии в двух битах двух смежных фрагментов анализируемой последовательности и соответствующих фрагментов эталона маркера. При одновременном появлении на входах "1 Вх 1" и "2 Вх 2" логической единицы на выходах элементов ИЛИ 14, ИЛИ 22 и ИЛИ 18 ("Вых 0", "Вых 1", "Вых 2") в течение такта будут удерживаться логические нули. Точно к такому же результату приведет одновременное появление логической единицы на входах "1 Вх 2" и "2 Вх 2" или на входах "1 Вх 2" и "2 Вх 2". Последнее будет свидетельствовать о том, что отличия двух смежных фрагментов анализируемой последовательности и соответствующих фрагментов эталона маркера превышают допустимые два бита. Если рассматриваемый элемент анализа используется на третьей, ..., К-й ступени анализа, то возможна ситуация, при которой одновременно на все три входа "1 Вx 0", "1 Вx 1", "1 Вx 2" или одновременно на другие три входа "2 Вx 0", "2 Вx 1", "2 Вx 2" поступит логический нуль, в этом случае на выходах элементов ИЛИ 14, ИЛИ 22 и ИЛИ 18 ("Вых 0", "Вых 1", "Вых 2") в течение такта будут удерживаться логические нули. Последнее будет свидетельствовать о том, что отличия двух смежных фрагментов анализируемой последовательности и соответствующих фрагментов эталона маркера превышают допустимые два бита. То есть если отличия двух смежных фрагментов анализируемой последовательности и соответствующих фрагментов эталона маркера меньше или равны двум битам, то на одном из выходов рассматриваемого элемента ("Вых 0", "Вых 1", "Вых 2") будет присутствовать логическая единица, а на двух других выходах логический нуль, если же упомянутые отличия превышают два бита, то на всех трех выходах ("Вых 0", "Вых 1", "Вых 2") будет присутствовать логический нуль.

Для рассмотрения работы элемента "(K + 1)-й ступени анализа воспользуемся фиг.4.

Предположим, что допустимое количество ошибок в сигнале кадровой синхронизации равно двум, в этом случае на первые входы элементов И 25, 28, 30 подаются потенциалы, соответствующие логической единице, а на вторые входы элементов И 25, 28, 30 ("Вх 0", "Вх 1", "Вх 2") поступают сигналы от соответствующих выходов элемента K-й ступени анализа, которые через триггеры 26, 29, 31 попадают на входы элемента ИЛИ 27. При этом, если на одном из входов ("Вх 0", "Вх 1", "Вх 2") появится единица, то на выходе элемента ИЛИ 27 в течение такта будет удерживаться логическая единица, которая и будет служить кадровым синхроимпульсом. Если же одновременно на всех трех входах ("Вх 0", "Вх 1", "Вх 2") будут логические нули, то и на выходе элемента ИЛИ 27 будет логический нуль, что интерпретируется как отсутствие маркера кадровой синхронизации. Предположим, что допустимое количество ошибок в сигнале кадровой синхронизации равно единице, в этом случае на первые входы элементов И 25, 28 подаются потенциалы, соответствующие логической единице, а на первый вход элемента И 30 подается логический нуль. При этом "Вх 2" оказывается заблокированным элементом И 30, и кадровый синхроимпульс на выходе элемента ИЛИ 27 появляется только в случае появления логической единицы на одном из входов "Вx 0" или "Вx 1". Если мы хотим формировать кадровый синхроимпульс лишь в случае обнаружения безошибочной комбинации маркера кадровой синхронизации, то на первые входы элементов И 28, 30, необходимо подать потенциалы, соответствующие логическому нулю, а на первый вход элемента И 25 - логическую единицу. При этом элементы И 28, 30 заблокируют входы "Вx 1", "Вx 2", и кадровый синхроимпульс на выходе элемента ИЛИ 27 будет регистрироваться лишь при появлении логической единицы на входе "Вx 0".

Для рассмотрения взаимодействия элементов анализа устройства выделения маркера кадровой синхронизации воспользуемся фиг. 1.

Предположим, что анализируемый фрагмент информационного потока, находящийся в регистре, входящем в элементы первой ступени анализа 1.1, ... 1.N, отличается от эталона маркера лишь в последнем и третьем от конца фрагмента битах. В этом случае у элементов 1.1, 1.2 логическая единица будет присутствовать на выходах "Вых 1", а у элементов 1.3,... 1.N логические единицы появятся на выходах "Вых 0", все остальные выходы элементов первой ступени анализа будут содержать логические нули. Такому состоянию выходов элементов первой ступени анализа будет соответствовать появление логической единицы на выходе "Вых 2" элемента 2.1 и логических единиц на выходах "Вых 0" элементов 2.2, ... 2.M при логических нулях на всех остальных выходах элементов второй ступени анализа. При этом на выходе "Вых 2" элемента 3.1 появится логическая единица, у элементов 3.3,... 3P логические единицы будут на выходах "Вых 0", а на всех остальных выходах третьей ступени анализа будут присутствовать логические нули. Такое состояние выходов третьей ступени анализа приведет к тому, что у элемента (K-1).1 логическая единица появится на выходе "Вых 2", а у элемента (K-1).2 логическая единица будет на выходе "Вых 0", при логических нулях на всех остальных выходах (K-1)-й ступени анализа. При этом у элемента K-й ступени анализа логическая единица появится на выходе "Вых 2" и логические нули на выходах "Вых 0", "Вых 1". Если задаваемое входами установки допустимое количество ошибок в сигнале кадровой синхронизации равно двум, то при описанном состоянии выходов устройства на выходе (K + 1)-го элемента появится кадровый синхроимпульс, если же допустимое количество ошибок в сигнале кадровой синхронизации равно нулю или единице, то кадровый синхроимпульс на выходе (K + 1)-го элемента не появится.

Предположим, что анализируемый фрагмент информационного потока, находящийся в регистре сдвига, входящем в элементы первой ступени анализа 1.1, . . ., 1.N, отличается от эталона маркера в последнем, предпоследнем и третьем от конца фрагмента битах. В этом случае у элемента 1.1 логическая единица будет присутствовать на выходе "Вых 2", у элемента 1.2 логическая единица будет на выходе "Вых 1", у элементов 1.3,... 1.N логические единицы появятся на выходах "Вых 0", а все остальные выходы элементов первой ступени анализа будут содержать логические нули. Такому состоянию выходов элементов первой ступени анализа будет соответствовать отсутствие единиц на всех трех выходах ("Вых 0", "Вых 1", "Вых 2") элемента 2.1, что приведет к появлению логических нулей на всех выходах элементов 3.1,..., (K-1).1, K и как следствие этого к логическому нулю на выходе (K + 1)-го элемента, т.е. кадровый синхроимпульс в этом случае будет отсутствовать.

Для повышения быстродействия устройства в каждый элемент анализа включены Д-триггеры, которые осуществляют привязку к тактовой частоте сигнала. При таком построении устройства его совокупное быстродействие не зависит от количества входящих в него элементов анализа. Однако при этом следует иметь в виду, что момент фиксации анализируемого фрагмента информационной последовательности в регистре сдвига первой ступени анализа отделен от момента завершения анализа этого фрагмента (K + 1) тактами.

На дату подачи заявки в Ростовском НИИ радиосвязи разработан, изготовлен и испытан макет предлагаемого устройства выделения маркера кадровой синхронизации.

Макет предлагаемого устройства был выполнен на микросхемах ТТЛ серии 530.

Макет предлагаемого устройства обеспечил следующие возможности:

- выделение маркера кадровой синхронизации при отсутствии в нем пораженных символов;

- выделение маркера кадровой синхронизации при количестве пораженных символов в нем, меньшем или равном единице;

- выделение маркера кадровой синхронизации при количестве пораженных символов в нем, меньшем или равном двум.

Работоспособность макета предлагаемого устройства проверялась и обеспечивалась при следующем виде и параметрах входных сигналов:

- входные сигналы в уровнях ТТЛ логики на нагрузке 50 Ом;

- тактовые импульсы - меандр;

- длина маркера кадровой синхронизации восемь бит;

- символьная скорость входного потока информации до 32 мбит/с.

Макет предлагаемого устройства прошел испытания и подтвердил достижение поставленной цели.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ВЫДЕЛЕНИЯ МАРКЕРА ДЛЯ СИСТЕМЫ КАДРОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2297103C2 |

| СТАНЦИЯ ТЕХНИЧЕСКОГО КОНТРОЛЯ СИГНАЛОВ СПУТНИКОВЫХ ЛИНИЙ СВЯЗИ | 1996 |

|

RU2176130C2 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ И ДЕМУЛЬТИПЛЕКСИРОВАНИЯ КОМПОНЕНТНЫХ СИГНАЛОВ В ЦИФРОВЫХ ПОТОКАХ | 2012 |

|

RU2514092C2 |

| СПОСОБ ОБРАБОТКИ ЦИФРОВЫХ ПОТОКОВ | 1995 |

|

RU2122291C1 |

| СПОСОБ КОНТРОЛЯ КАЧЕСТВА СИГНАЛА ГЕТЕРОДИНА МНОГОКАНАЛЬНОГО СУПЕРГЕТЕРОДИННОГО РАДИОПРИЕМНИКА | 1995 |

|

RU2109404C1 |

| ПРИЕМНИК СИГНАЛОВ КВАДРАТУРНОЙ АМПЛИТУДНОЙ МАНИПУЛЯЦИИ | 1990 |

|

RU2019053C1 |

| УСТРОЙСТВО ВЫДЕЛЕНИЯ МАРКЕРА ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2001 |

|

RU2210869C2 |

| ПРИЕМНИК СИНХРОСИГНАЛА | 2002 |

|

RU2242093C2 |

| УСТРОЙСТВО ВЫДЕЛЕНИЯ МАРКЕРА ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2271611C1 |

| Устройство кадровой синхронизации | 1990 |

|

SU1737745A1 |

Изобретение относится к электросвязи и может быть использовано для кадровой синхронизации приемников в системах передачи цифровой информации. Технический результат - повышение быстродействия выделения маркера кадровой синхронизации. Сущность способа заключается в том, что входной сигнал, представляющий собой последовательную комбинацию двоичных символов, преобразуют из последовательного кода в параллельный и сравнивают его с эталонной комбинацией маркера. Устройство, осуществляющее способ, обеспечивает возможность соединения маркера кадровой синхронизации при отсутствии в нем пораженных символов, выделение маркера кадровой синхронизации при количестве пораженных символов в нем меньше или равном единице, выделение маркера кадровой синхронизации при количестве пораженных сигналов в нем меньше или равном двум. 2 c. и 3 з.п. ф-лы, 4 ил.

| SU 1821932 A1, 15.06.1993 | |||

| SU 1821931 A1, 15.06.1993 | |||

| Устройство для выделения маркера кадровой синхронизации | 1987 |

|

SU1518903A2 |

| Устройство для выделения маркера кадровой синхронизации | 1983 |

|

SU1095434A1 |

| US 3760355 A, 18.09.1973. | |||

Авторы

Даты

2000-10-27—Публикация

1996-05-21—Подача