Изобретение относится к электросвязи и может быть использовано для цикловой синхронизации сообщений в системах передачи дискретной информации.

Устройство выделения маркера цикловой синхронизации, описанное в настоящей заявке, применимо для стартстопной и кодовой цикловой синхронизации сообщений. Его можно использовать как в системах синхронной связи для установки и поддержания постоянного фазового соотношения между сообщениями, так и в асинхронных системах сеансной связи для поиска и выделения отдельных сообщений.

В предлагаемом устройстве под маркером цикловой синхронизации будем понимать двоичную последовательность символов, однозначно определяющую начало или конец сообщения.

В настоящее время цифровые каналы связи ультракоротковолновых и дециметровых диапазонов, в частности спутниковые каналы, характеризуются большими массивами передаваемой информации. Причем скорость обработки информации во вновь вводимых линиях связи достигает 120 Мбит/с и более.

В связи с этим актуальной является задача создания устройства выделения маркера цикловой синхронизации, требующего небольшого количества операций при установлении синхронизации и, следовательно, обладающего высоким быстродействием.

Известно устройство выделения маркера цикловой синхронизации, содержащее регистр сдвига, элемент сравнения с эталонной комбинацией маркера и блок анализа кода совпадения, причем информационный вход устройства выделения маркера цикловой синхронизации связан с входом регистра сдвига, выходы разрядов которого соединены со входами элемента сравнения с эталонной комбинацией маркера, выходы элемента сравнения связаны с входами блока анализа кода совпадения, выход которого является выходом устройства выделения маркера цикловой синхронизации [1].

Однако это устройство имеет недостаточное быстродействие, обусловленное тем, что поиск комбинации маркера осуществляют при каждом сдвиге входного сигнала на один символ и количество попыток поиска маркера на длине входной последовательности равно количеству символов в этой последовательности.

Наиболее близким к предлагаемому устройству является устройство (прототип), содержащее регистр сдвига, элементы сравнения с эталонной комбинацией маркера и блоки анализа кода совпадения, при этом вход регистра сдвига является информационным входом устройства выделения маркера цикловой синхронизации, регистр сдвига состоит из совокупности последовательно соединенных групп элементов памяти, в свою очередь состоящих из последовательно соединенных K элементов памяти в каждой группе, выходы которых соединены со входами соответствующих элементов сравнения с эталонной комбинацией маркера, выход блока анализа кода совпадения последней ступени является выходом устройства выделения маркера цикловой синхронизации [2].

Недостатком этого устройства является недостаточное быстродействие, поскольку выделение комбинации маркера осуществляют при вводе входной последовательности в последовательном коде, т.е. при каждом сдвиге входной последовательности на один символ, что требует значительных затрат времени.

Цель изобретения - повышение быстродействия выделения маркера цикловой синхронизации за счет того, что решение о наличии маркера цикловой синхронизации во входной последовательности принимают при поступлении входной последовательности в последовательно параллельном коде, группами по K (K>1) символов, т.е. при сдвиге входной последовательности на K двоичных символов.

Для достижения цели предложено устройство выделения маркера цикловой синхронизации, содержащее регистр сдвига, элементы сравнения с эталонной комбинацией маркера и блоки анализа кода совпадения, при этом вход регистра сдвига является информационным входом устройства выделения маркера цикловой синхронизации, регистр сдвига состоит из совокупности последовательно соединенных групп элементов памяти, в свою очередь состоящих из последовательно соединенных K элементов памяти в каждой группе, выходы которых соединены со входами соответствующих элементов сравнения с эталонной комбинацией маркера, выход блока анализа кода совпадения последней ступени является выходом устройства выделения маркера цикловой синхронизации. Новым является то, что выходы элементов памяти каждой предыдущей группы элементов памяти соединены с входами элементов памяти следующей группы элементов памяти, причем выходы элементов сравнения с эталонной комбинацией маркера, начиная со второго элемента сравнения и заканчивая предпоследним, связаны с входами блока анализа кода совпадения первой ступени, а выход блока анализа кода совпадения первой ступени соединен со вторыми входами первого и последнего элементов сравнения с эталонной комбинацией маркера, а также связан с входом блока анализа кода совпадения второй ступени, выходы первого и последнего элементов сравнения соединены с входами блока анализа кода совпадения второй ступени.

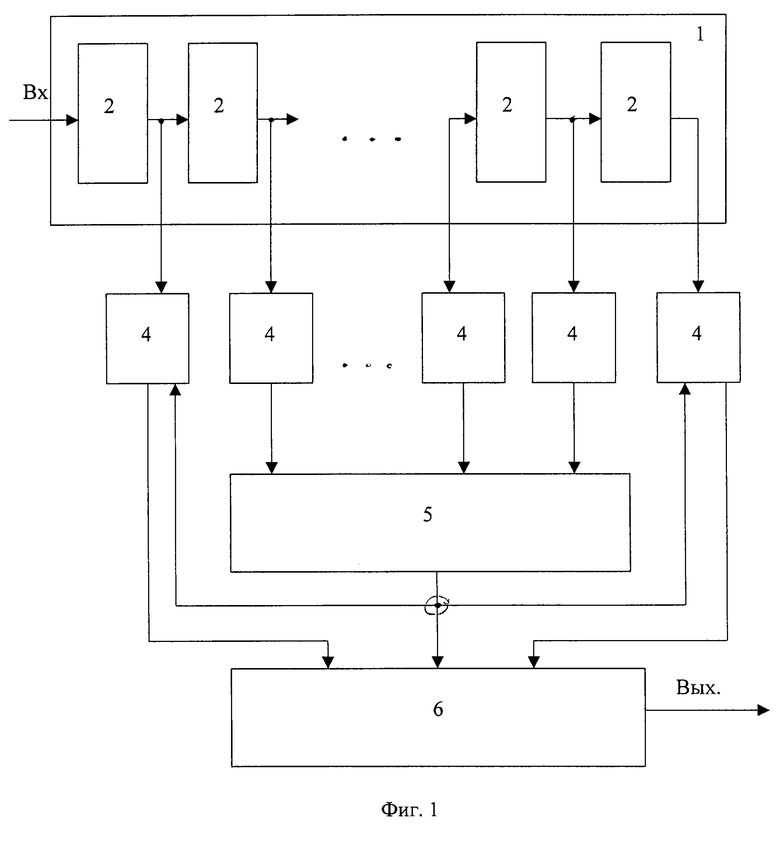

Заявляемое устройство иллюстрируется чертежами, представленными на фиг.1 - 3.

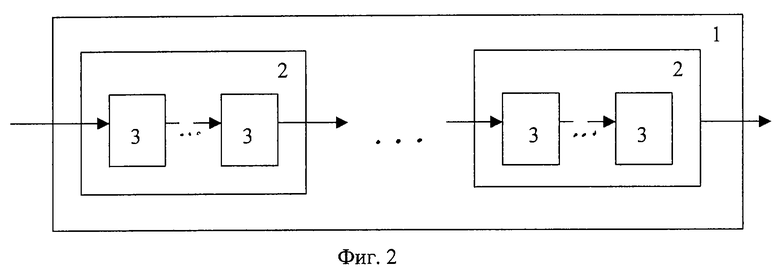

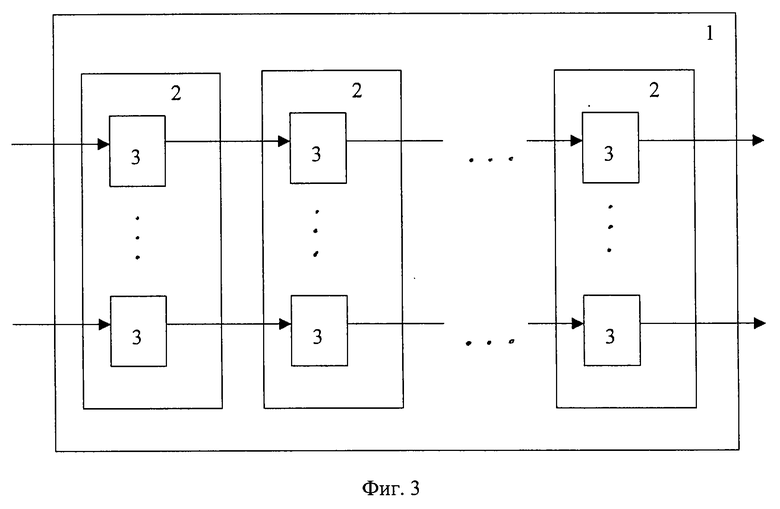

На фиг.1 приведена структурная электрическая схема предлагаемого устройства. На фиг.2 и на фиг.3 приведены схемы соединения элементов памяти регистра сдвига для прототипа и заявляемого устройства соответственно.

Устройство выделения маркера цикловой синхронизации содержит регистр сдвига 1, выполненный из последовательно соединенных групп элементов памяти 2 по K элементов памяти 3 в каждой группе, элементы сравнения 4 с эталонной комбинацией маркера, блок анализа кода совпадения первой ступени 5 и блок анализа кода совпадения второй ступени 6.

Предлагаемое устройство выделения маркера цикловой синхронизации работает следующим образом.

На передающей стороне формируют входную последовательность. Например, при стартстопной цикловой синхронизации к исходному сообщению объемом m двоичных символов добавляют комбинацию маркера, состоящую из F двоичных символов. В качестве комбинации маркера выбирается последовательность подходящей длины с хорошими синхронизирующими свойствами, например, последовательность максимальной длины (код Рида - Маллера 1-го порядка). Как правило, длина F комбинации маркера, для осуществления надежной синхронизации, находится в пределах 20-50 символов.

Далее последовательность, сформированная в виде следующих друг за другом комбинации маркера и сообщения, преобразованная в сигнал, имеющий аналоговую форму, поступает в канал связи. В канале связи возможно искажение передаваемого сигнала. Это может привести к тому, что входная последовательность будет принята с ошибками.

На приемной стороне осуществляется прием входной последовательности.

Далее входная последовательность в параллельном коде, состоящем из K символов, поступает на вход регистра сдвига 1. Регистр сдвига 1 состоит из N групп элементов памяти 2 по K элементов памяти 3 в каждой группе. Входная последовательность записывается в первую группу элементов памяти 2 регистра сдвига 1 в соответствии с порядком поступления символов. При этом символы с выхода предыдущей группы элементов памяти 2 регистра сдвига 1 в параллельном коде переписываются в элементы памяти 3 следующей группы элементов памяти 2. Длину регистра сдвига 1 или длину отрезка входной последовательности, которую используют для выделения комбинации маркера, определяют как сумму числа символов F в комбинации маркера и числа символов K в группе элементов памяти 2 (обычно K<<F). Поэтому при любом сдвиге комбинации маркера в пределах группы символов, состоящей из K символов, маркер полностью помещается в регистр сдвига 1.

Далее элементы сравнения 4 с эталонной комбинацией маркера осуществляют формирование кода совпадения для каждой группы символов входной последовательности, находящейся в соответствующей группе элементов памяти 2 регистра сдвига 1, с соответствующей группой символов эталонной комбинации маркера. Кодом совпадения является величина фазы сдвига входной последовательности относительно эталонной комбинации маркера, т.е. код совпадения определяет, на сколько символов входная последовательность смещена относительно эталонной комбинации маркера.

Элементы сравнения 4 представляют собой запоминающие устройства, например постоянные запоминающие устройства (ПЗУ), и формирование кода совпадения для каждой группы символов входной последовательности с соответствующей группой символов эталонной комбинации маркера осуществляется по таблицам, записанным в ПЗУ. Входом каждой такой таблицы или ее адресом являются данные, составляющие входную последовательность символов, из рассматриваемой группы символов с учетом ошибок, наложенных на входную последовательность в канале. Выходом таблицы - величина сдвига группы символов (фаза) входной последовательности относительно эталонной комбинации маркера.

Таблицы фаз формируются заранее на приемной стороне в следующем порядке. Рассмотрим сначала вторую группу символов. Вторая группа символов входной последовательности полностью состоит из символов маркера. Во второй группе символов могут быть первые K символов маркера. В этом случае будем считать, что маркер принят с фазой, равной 0. Если во второй группе символов символы маркера начинаются со второго символа маркера, тогда маркер принят с фазой, равной 1 и т.д. Всего существует K фаз положения маркера в пределах одной группы.

Составим следующую таблицу ϕ1 = T1(A1). Входом этой таблицы являются комбинации А1 из K символов маркера, принятые с различными сдвигами, начиная с 0 и до K-1, а выходом - указанные сдвиги от 0 до K-1 или фазы ϕ1 принятой группы символов длины K из комбинации маркера.

Поскольку комбинации маркера выбраны из числа последовательностей с хорошими синхронизирующими свойствами, сдвиги рассматриваемой группы символов маркера на K-1 символов и менее будут попарно отличаться друг от друга на некоторое число символов. Пусть минимальное расстояние между рассматриваемыми комбинациями составляет величину dmin, тогда при наличии ошибок в группе символов маркера, кратность которых не превышает (dmin-1)/2, комбинация маркера будет определяться однозначно.

Внесем в рассматриваемую таблицу фаз ϕ = T1(A1) также комбинации маркера, отличающиеся от ранее записанных сдвигов маркера на вектор ошибок, вес которого не превышает величины (dmin-1)/2.

Входом таблицы являются K двоичных символов, и объем таблицы будет составлять 2К значений. Из них ровно K значений будут соответствовать возможным сдвигам маркера, а CK 1, CK 2, ..., CK T значений для каждого из K сдвигов будут соответствовать сдвигам маркера с ошибками, где t=(dmin-1)/2 - количество ошибок в группе символов, которые исправляет комбинация маркера. Оставшееся количество значений в таблице, которым не будет соответствовать определенная фаза маркера, будет равно

Эти значения в таблице заполняются запрещенными комбинациями, например числом K. Поэтому разрядность выхода таблицы будет не менее log2(K+1).

Немаловажное значение при реализации предлагаемого устройства имеет выбор подходящего значения длины K группы символов. При увеличении длины K синхронизирующие свойства входной последовательности улучшаются, с другой стороны, при этом экспоненциально растет объем таблицы фаз и требуемый объем памяти ПЗУ, что приводит к необходимости ограничивать величину K.

Аналогичным образом вычисляют таблицу фаз ϕ2 = T2(A2) для следующей, третьей группы символов во входной последовательности и т. д.

Отличия в формировании таблиц фаз возникают для первой и последней групп символов входной последовательности. Это связано с тем, что не все символы этих групп могут принадлежать символам маркера, поскольку начало и конец комбинации маркера может не совпадать с границами групп символов. В этом случае формирование таблиц фаз выполняют следующим образом.

На основании сравнения фаз, вычисленных по таблицам для групп символов, начиная со второй группы и заканчивая предпоследней, и их совпадения, можно принять предварительное решение о суммарной фазе маркера. В зависимости от ее величины выбираются те разряды первой и последней групп входной последовательности, которые соответствуют символам маркера. Далее для этих символов таблицы фаз ϕ0 = T0(A0) и ϕn-1 = Tn-1(An-1) строят в том же порядке, что и ранее сформированные таблицы для других групп символов.

Решение о наличии комбинации маркера во входной последовательности символов и величине его фазы принимают в случае совпадения фаз для всех групп символов входной последовательности. При наличии хотя бы одной запрещенной комбинации на выходе таблиц фаз решение о наличии маркера не принимается.

Анализ наличия комбинации маркера во входной последовательности осуществляется в блоке анализа кода совпадения первой ступени 5 и блоке анализа кода совпадения второй ступени 6. В блоке анализа кода совпадений первой ступени 5 выполняют сравнение фаз групп символов входной последовательности, получаемых с выходов элементов сравнения 4, начиная со второго элемента сравнения и заканчивая предпоследним. В случае совпадения всех сравниваемых фаз код фазы с выхода блока анализа кода совпадений первой ступени 5 поступает на вторую группу входов первого и последнего элементов сравнения 4 с эталонной комбинацией маркера. В зависимости от величины этой фазы указанные элементы сравнения 4 по таблицам учитывают необходимые разряды входной последовательности и определяют фазы сдвига первой и последней группы символов входной последовательности.

Далее фазы с выхода первого и последнего элемента сравнения 4 и блока анализа кода совпадений первой ступени 5 поступают на вход блока анализа кода совпадений второй ступени 6. В случае совпадения всех перечисленных фаз код фазы принятой комбинации маркера с выхода блока анализа кода совпадения второй ступени 6 поступает на выход устройства выделения маркера цикловой синхронизации.

Блоки анализа кода совпадений 5 и 6 осуществляют сравнение поступающих на вход кодов фаз между собой и в случае их совпадения выдают этот код фазы на выход, в случае их несовпадения на выходе возникает запрещенная комбинация. Логическая функция fi, выражающая один из выходных разрядов блока анализа совпадения, в зависимости от значения разрядов входных фаз запишется в виде

где ϕ1i, ϕ2i, Кi - i - разряд соответственно первой, второй фазы и запрещенной комбинации.

Блоки анализа кода совпадений 4 и 5 могут быть реализованы согласно логической функции с помощью комбинационной схемы на логических элементах, например, как это описано в [3].

В предлагаемом изобретении, в отличие от известного устройства, поиск маркера во входной последовательности осуществляют после приема очередной группы символов из K символов входной последовательности, поступающей на вход устройства выделения маркера цикловой синхронизации в параллельном коде. Такой поиск осуществляют только один раз для всей вновь принятой группы из K символов. В известном устройстве поиск комбинации маркера осуществляют с приемом каждого вновь поступившего символа входной последовательности. Поэтому предложенное устройство обладает примерно в K раз большим быстродействием, чем известное.

Достигаемым техническим результатом предлагаемого устройства выделения маркера цикловой синхронизации является повышение быстродействия.

Источники информации

1. Лосев В.В., Бродская Е.Б., Коржик В.И. Поиск и декодирование сложных дискретных сигналов./ Под ред. В.И. Коржика. - М.: Радио и связь, 1988, стр. 21.

2. Патент Российской Федерации N 2158483, кл. Н 04 L 7/04, G 06 F 1/04, опубл. 27.10.2000.

3. Основы импульсной и цифровой техники. М., "Сов. радио", 1975, стр. 341.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ВЫДЕЛЕНИЯ МАРКЕРА ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2271611C1 |

| СПОСОБ ВЫДЕЛЕНИЯ МАРКЕРА ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2001 |

|

RU2183911C1 |

| СПОСОБ ВЫДЕЛЕНИЯ МАРКЕРА ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2002 |

|

RU2231929C2 |

| СПОСОБ ВЫДЕЛЕНИЯ МАРКЕРА ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2341027C1 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2001 |

|

RU2214689C2 |

| СПОСОБ АДАПТИВНОЙ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2001 |

|

RU2210870C2 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2342796C1 |

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2251210C1 |

| КОДЕК ЦИКЛИЧЕСКОГО ПОМЕХОУСТОЙЧИВОГО КОДА | 2002 |

|

RU2212101C1 |

| УСТРОЙСТВО АДАПТИВНОЙ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2259638C1 |

Устройство выделения маркера цикловой синхронизации относится к электросвязи и может быть использовано для цикловой синхронизации сообщений в системах передачи дискретной информации. Технический результат - повышение быстродействия выделения маркера цикловой синхронизации за счет того, что решение о наличии маркера цикловой синхронизации во входной последовательности принимают при поступлении входной последовательности в последовательно-параллельном коде группами по К (К>1) символов, т.е. при сдвиге входной последовательности на К двоичных символов. Технический результат достигается тем, что выходы элементов памяти каждой предыдущей группы элементов памяти соединены с входами элементов памяти следующей группы элементов памяти, причем выходы элементов сравнения с эталонной комбинацией маркера, начиная со второго элемента сравнения и заканчивая предпоследним, связаны с входами блока анализа кода совпадения первой ступени, а выход блока анализа кода совпадения первой ступени соединен со вторыми входами первого и последнего элементов сравнения с эталонной комбинацией маркера, а также связан с входом блока анализа кода совпадения второй ступени, выходы первого и последнего элементов сравнения соединены с входами блока анализа кода совпадения второй ступени. 3 ил.

Устройство выделения маркера цикловой синхронизации, содержащее регистр сдвига, элементы сравнения с эталонной комбинацией маркера и блоки анализа кода совпадения, при этом вход регистра сдвига является информационным входом устройства выделения маркера цикловой синхронизации, регистр сдвига состоит из совокупности последовательно соединенных групп элементов памяти, в свою очередь, состоящих из К элементов памяти в каждой группе, выходы которых соединены со входами соответствующих элементов сравнения с эталонной комбинацией маркера, выход блока анализа кода совпадения последней ступени является выходом устройства выделения маркера цикловой синхронизации, отличающееся тем, что выходы элементов памяти каждой предыдущей группы элементов памяти соединены с входами элементов памяти следующей группы элементов памяти, причем выходы элементов сравнения с эталонной комбинацией маркера, начиная со второго элемента сравнения и заканчивая предпоследним, связаны с входами блока анализа кода совпадения первой ступени, а выход блока анализа кода совпадения первой ступени соединен со вторыми входами первого и последнего элементов сравнения с эталонной комбинацией маркера, а также связан с входом блока анализа кода совпадения второй ступени, выходы первого и последнего элементов сравнения соединены с входами блока анализа кода совпадения второй ступени.

| СПОСОБ ВЫДЕЛЕНИЯ МАРКЕРА КАДРОВОЙ СИНХРОНИЗАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2158483C2 |

| СХЕМА И СПОСОБ ОПРЕДЕЛЕНИЯ СИНХРОНИЗАЦИИ И ЗАЩИТЫ (ВАРИАНТЫ) | 1996 |

|

RU2159510C2 |

| DE 4107640 A1, 10.09.1991 | |||

| US 4641327, 03.02.1987. | |||

Авторы

Даты

2003-08-20—Публикация

2001-08-24—Подача