Изобретение относится к области электросвязи и может быть использовано для цикловой синхронизации сообщений в системах передачи дискретной информации.

Предлагаемое устройство выделения маркера цикловой синхронизации может применяться для стартстопной и кодовой цикловой синхронизации сообщений. Его можно использовать как в системах синхронной связи для установки и поддержания постоянного фазового соотношения между сообщениями, так и в асинхронных системах сеансной связи для поиска и выделения отдельных сообщений.

В настоящей заявке под маркером цикловой синхронизации будем понимать двоичную последовательность символов, местоположение которой однозначно определяет начало или конец сообщения.

В настоящее время цифровые каналы связи ультракоротковолновых и дециметровых диапазонов, в частности спутниковые каналы, характеризуются большими массивами передаваемой информации. При этом скорость обработки информации во вновь вводимых линиях связи достигает 120 Мбит/с и более.

В связи с этим актуальной является задача создания устройства выделения маркера цикловой синхронизации, обладающего высоким быстродействием, повышенной помехоустойчивостью и при этом имеющего простую аппаратную и программную реализацию.

Известно устройство выделения маркера цикловой синхронизации, содержащее регистр сдвига, элементы сравнения с эталонной комбинацией маркера и блоки анализа кода совпадения, при этом вход регистра сдвига является информационным входом устройства выделения маркера цикловой синхронизации, регистр сдвига состоит из совокупности последовательно соединенных групп элементов памяти, в свою очередь состоящих из последовательно соединенных К элементов памяти в каждой группе, выходы которых соединены с входами соответствующих элементов сравнения с эталонной комбинацией маркера, выход блока анализа кода совпадения последней ступени является выходом устройства выделения маркера цикловой синхронизации (патент РФ №2158483, кл. Н 04 L 7/04, G 06 F 1/04, опубл. 27.10.2000).

Однако это устройство имеет низкое быстродействие, обусловленное тем, что поиск комбинации маркера осуществляют при сдвиге входной последовательности на один символ и количество попыток поиска маркера на длине входной последовательности равно количеству символов в этой последовательности.

Наиболее близким к предлагаемому устройству является устройство выделения маркера цикловой синхронизации (прототип), содержащее регистр сдвига, элемент сравнения с эталонной комбинацией маркера и блок анализа кода совпадения, при этом вход регистра сдвига является информационным входом устройства выделения маркера цикловой синхронизации, регистр сдвига состоит из совокупности последовательно соединенных групп элементов памяти, и выход второй группы элементов памяти соединен с входом элемента сравнения с эталонной комбинацией маркера (патент РФ №2210869, кл. Н 04 L 7/04, G 06 F 1/12, опубл. 20.08.2003).

Недостатком этого устройства является высокая сложность из-за большого объема памяти запоминающего устройства (ЗУ) для реализации элементов сравнения с эталонной комбинацией маркера, а также низкая помехоустойчивость устройства выделения маркера цикловой синхронизации.

Цель изобретения - упрощение устройства выделения маркера цикловой синхронизации за счет сокращения числа элементов сравнения с эталонной комбинацией маркера и, следовательно, уменьшения объема памяти ЗУ для реализации этих элементов. Также целью является повышение помехоустойчивости устройства выделения маркера цикловой синхронизации.

Для достижения цели предложено устройство выделения маркера цикловой синхронизации, содержащее регистр сдвига, элемент сравнения с эталонной комбинацией маркера и блок анализа кода совпадения, при этом вход регистра сдвига является информационным входом устройства выделения маркера цикловой синхронизации, регистр сдвига состоит из совокупности последовательно соединенных групп элементов памяти, и выход второй группы элементов памяти соединен с входом элемента сравнения с эталонной комбинацией маркера. Новым является то, что в устройство введены первая схема И, первый генератор маскирующей последовательности, генератор символов маркера, блок вычисления кода совпадения, вторая схема И, второй генератор маскирующей последовательности и пороговый блок, при этом выход первой группы элементов памяти соединен с входом первой схемы И, другой вход которой подключен к выходу первого генератора маскирующей последовательности, выход первой схемы И соединен с входом блока вычисления кода совпадения, выход элемента сравнения с эталонной комбинацией маркера подключен к входу первого и второго генератора маскирующей последовательности, выходу синхронизации устройства, а также к входу генератора символов маркера, выход второго генератора маскирующей последовательности соединен с входом второй схемы И, другие входы которой подключены к выходам групп элементов памяти, начиная с третьей группы элементов памяти и заканчивая последней группой элементов памяти, выход второй схемы И соединен с входом блока вычисления кода совпадения, другой вход которого подключен к выходу генератора символов маркера, выход блока вычисления кода совпадения соединен с входом блока анализа кода совпадения, выход которого подключен к входу порогового блока, выход которого является информационным выходом устройства выделения маркера цикловой синхронизации.

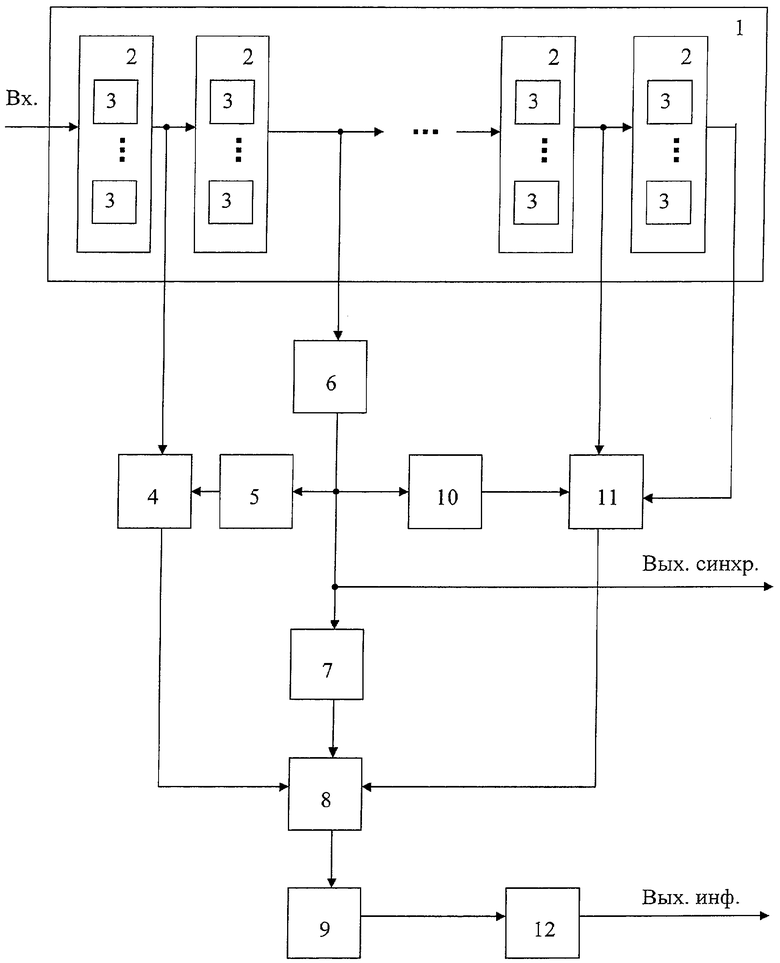

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Устройство выделения маркера цикловой синхронизации содержит регистр сдвига 1, выполненный из последовательно соединенных групп 2 элементов памяти 3, первую схему И 4, первый генератор маскирующей последовательности 5, элемент сравнения с эталонной комбинацией маркера 6, генератор символов маркера 7, блок вычисления кода совпадения 8, блок анализа кода совпадения 9, второй генератор маскирующей последовательности 10, вторую схему И 11 и пороговый блок 12.

Предлагаемое устройство выделения маркера цикловой синхронизации работает следующим образом.

Устройство выделения маркера цикловой синхронизации находится на приемной стороне системы передачи дискретной информации. Входную информационную последовательность устройства выделения маркера цикловой синхронизации формируют на передающей стороне системы передачи дискретной информации. Например, при стартстопной цикловой синхронизации к исходному сообщению объемом m двоичных символов добавляют комбинацию маркера, состоящую из F двоичных символов. В качестве комбинации маркера выбирают последовательность подходящей длины с хорошими синхронизирующими свойствами, например, последовательность максимальной длины (код Рида-Маллера 1-го порядка). Как правило, длина F комбинации маркера для осуществления надежной синхронизации находится в пределах 20...50 символов.

Далее входная последовательность, сформированная в виде следующих друг за другом комбинаций маркера и сообщения, преобразованная в сигнал, имеющий аналоговую форму, поступает в канал связи. В канале связи возможно искажение передаваемого сигнала. Это может привести к тому, что входная последовательность будет принята с ошибками.

На приемной стороне входная последовательность поступает на вход устройства выделения маркера цикловой синхронизации. На вход устройства выделения маркера цикловой синхронизации входная последовательность поступает в параллельном коде, состоящем из К символов.

Эти символы поступают сначала на вход регистра сдвига 1. Регистр сдвига 1 состоит из N групп 2 элементов памяти 3 по К элементов памяти в каждой группе. Входную последовательность записывают в первую группу 2 элементов памяти 3 регистра сдвига 1. При этом символы с выхода предыдущей группы 2 элементов памяти 3 регистра сдвига 1 в параллельном коде переписывают в следующую группу 2 элементов памяти 3. Длину регистра сдвига 1 или длину отрезка входной последовательности, которую используют для выделения комбинации маркера, определяют как сумму числа символов F в комбинации маркера и числа символов К в группе 2 элементов памяти (обычно К≪F). Поэтому при любом сдвиге комбинации маркера в пределах группы символов, состоящей из К символов, маркер полностью помещается в регистр сдвига 1.

С выхода второй группы 2 элементов памяти 3 регистра сдвига 1 символы входной последовательности поступают на вход элемента сравнения с эталонной комбинацией маркера 6. Элемент сравнения с эталонной комбинацией маркера 6 определяет величину фазы сдвига входной последовательности относительно несмещенного положения комбинации маркера, то есть определяет на сколько символов входная последовательность смещена относительно несмещенного (нулевого) положения комбинации маркера. При этом под несмещенным положением комбинации маркера понимается такое ее положение, при котором начало комбинации маркера совпадает с началом второй группы 2 элементов памяти регистра сдвига 1, а конец комбинации маркера совпадает с концом регистра сдвига 1. Элемент сравнения с эталонной комбинацией маркера 6 может быть реализован, например, с помощью запоминающего устройства. Таким запоминающим устройством может быть, в частности, постоянное запоминающее устройство (ПЗУ), и формирование величины фазы сдвига входной последовательности осуществляют с помощью функциональной зависимости, записанной в ПЗУ. Входом каждой такой функциональной зависимости, или ее аргументом (адресом ПЗУ), являются данные с выхода второй группы 2 элементов памяти 3 регистра сдвига 1, составляющие входную последовательность символов с учетом ошибок, наложенных на входную последовательность в канале связи. Выходом функциональной зависимости, или содержимым ПЗУ, является величина сдвига (фаза) символов комбинации маркера относительно несмещенного положения комбинации маркера.

Функциональную зависимость ϕ=T1(A) между символами А комбинации маркера и величиной фазы ϕ этой комбинации маркера формируют заранее на приемной стороне в виде таблицы, записанной в ПЗУ. Формирование этой функциональной зависимости осуществляют в следующем порядке. При любом сдвиге комбинации маркера в пределах регистра сдвига 1 символы А, находящиеся во второй группе 2 элементов памяти, являются К символами комбинации маркера. Во второй группе 2 элементов памяти могут быть первые К символов комбинации маркера. В этом случае будем считать, что комбинация маркера принята с фазой, равной 0. Если во второй группе 2 элементов памяти символы комбинации маркера начинаются со второго символа комбинации маркера, тогда комбинация маркера принята с фазой, равной 1, и так далее. Всего существует К фаз положения комбинации маркера в пределах одной группы. Аргументом функциональной зависимости являются символы А, состоящие из К символов комбинации маркера, принятые с различными сдвигами, начиная с 0 и до К-1, а выходом функциональной зависимости - указанные сдвиги от 0 до К-1 или фазы ϕ К символов комбинации маркера, находящихся во второй группе 2 элементов памяти.

Поскольку комбинации маркера выбраны из числа последовательностей с хорошими синхронизирующими свойствами, сдвиги рассматриваемой группы символов комбинации маркера на К-1 символов и менее будут попарно отличаться друг от друга на некоторое число символов. Пусть минимальное расстояние между рассматриваемыми комбинациями составляет величину dmin, тогда при наличии ошибок в группе символов комбинации маркера, кратность которых не превышает (dmin-1)/2, комбинация маркера будет определяться однозначно.

Внесем в рассматриваемую функциональную зависимость фаз ϕ=Т1 (А) также символы А комбинации маркера, отличающиеся от ранее записанных символов А комбинации маркера на комбинацию ошибок, вес которой не превышает величины (dmin-1)/2.

Аргументом функциональной зависимости являются К двоичных символов, и количество значений этой функциональной зависимости (объем памяти ПЗУ для ее задания) будет составлять 2K значений. Из них ровно К значений будет соответствовать возможным сдвигам комбинации маркера без ошибок, а С1 K,С2 K,...,С1 K значений для каждого из К сдвигов будут соответствовать сдвигам комбинации маркера с ошибками, где t=(dmin-1)/2 - количество ошибок в группе из К символов, которые исправляет комбинация маркера. Оставшееся количество значений г функциональной зависимости, которым не будет соответствовать определенная фаза комбинации маркера, будет равно

Эти значения в ПЗУ заполняются запрещенными комбинациями, которые не соответствуют возможным значениям фазы. В качестве запрещенной комбинации может быть выбрано, например, число К. Поэтому разрядность выхода функциональной зависимости будет не менее log2(K+l). Объем памяти VПЗУ для хранения функциональной зависимости ϕ=Т1 (А) равен

V=2klog2(K+l).

Немаловажное значение при реализации предлагаемого устройства имеет выбор подходящего числа К элементов памяти в каждой группе 2 элементов памяти. При возрастании величины К синхронизирующие свойства группы символов входной последовательности улучшаются, с другой стороны, при этом экспоненциально растет объем памяти ПЗУ для хранения функциональной зависимости фазы, что приводит к необходимости ограничивать величину К.

На основании величины фазы, определенной для второй группы символов комбинации маркера, получают остальные (эталонные) символы комбинации маркера, не входящие во вторую группу символов. Эталонные символы комбинации маркера получают в генераторе символов маркера 7. На вход генератора символов маркера 7 с выхода элемента сравнения с эталонной комбинацией маркера 6 поступает фаза комбинации маркера. Генератор символов маркера 7 осуществляет преобразование кода фазы комбинации маркера в код эталонных символов маркера. Такое преобразование кода может выполняться, например, с помощью ПЗУ, в которое записана функциональная зависимость В=Т2(ϕ) между величиной фазы ϕ комбинации маркера и эталонными символами маркера В. Адресное пространство памяти ПЗУ для хранения функциональной зависимости В=Т2(ϕ) будет оцениваться величиной log2(K), a разрядность выхода таблицы будет равна F-К. Поэтому, объем памяти W ПЗУ, необходимый для хранения функциональной зависимости В=Т2(ϕ), будет равен

W=(F-K)log2(K).

Отсюда следует, что объем памяти ПЗУ, необходимый для хранения функциональной зависимости В=Т2(ϕ), как правило, существенно меньше объема памяти для хранения функциональной зависимости ϕ=Т1(А) (W≪V для F=20...50 и К=8...16), и сложность устройства выделения маркера цикловой синхронизации определяется сложностью реализации функциональной зависимости ϕ=T1(А).

Далее фаза комбинации маркера поступает на входы первого и второго генератора маскирующей последовательности 5 и 10. Первый и второй генераторы маскирующей последовательности 5 и 10 осуществляют преобразование кода фазы комбинации маркера в код маскирующей последовательности. Код маскирующей последовательности первого генератора 5 представляет собой серию нулевых двоичных символов, за которой следует серия единичных двоичных символов: 00...011...1. Положение единичных символов в маскирующей последовательности соответствует положению символов комбинации маркера в первой группе 2 элементов памяти и полностью определяется фазой комбинации маркера. Код маскирующей последовательности второго генератора 10 представляет собой серию единичных двоичных символов, за которой следует серия нулевых двоичных символов: 11...100...0. Положение единичных символов в маскирующей последовательности соответствует положению символов комбинации маркера в третьей и последующих группах 2 элементов памяти и также определяется фазой комбинации маркера. Первый и второй генераторы маскирующей последовательности 5 и 10 представляют собой преобразователи кода и могут быть реализованы, например, с помощью ПЗУ. В эти ПЗУ записаны функциональные зависимости между фазой комбинации маркера и маскирующими последовательностями. Объем памяти этих ПЗУ, реализующих первый и второй генераторы маскирующей последовательности 5 и 10, соизмерим с объемом памяти ПЗУ, реализующего генератор символов маркера 7, и существенно меньше объема памяти ПЗУ для реализации элемента сравнения с эталонной комбинацией маркера 6.

Маскирующие последовательности с выходов генераторов маскирующей последовательности 5 и 10 поступают на входы первой и второй схем И 4 и 11. В первой схеме И 4 осуществляют операцию поразрядного логического И символов комбинации маркера с выхода первой группы 2 элементов памяти 3 регистра сдвига 1 и соответствующими символами маскирующей последовательности. Аналогично во второй схеме И 11 осуществляют операцию поразрядного логического И символов комбинации маркера с выхода третьей и последующей групп 2 элементов памяти 3 регистра сдвига 1 и символов маскирующей последовательности. На выходе первой и второй схем И 4 и 11 получают серии нулевых символов вместе с символами комбинации маркера, которые были приняты из канала связи.

Далее эти символы комбинации маркера, принятые из канала связи, вместе с эталонными символами маркера с выхода генератора символов маркера 7 поступают на вход блока вычисления кода совпадения 8. Блок вычисления кода совпадения 8 поразрядно сравнивает (суммирует по модулю два) символы комбинации маркера, принятые из канала связи с эталонными символами маркера, полученными с генератора символов маркера 7.

Последовательность символов с выхода блока вычисления кода совпадения 8 затем поступает на вход блока анализа кода совпадения 9. Блок анализа кода совпадения 9 подсчитывает количество единиц в этой последовательности символов, то есть вес Хемминга последовательности символов. Блок анализа кода совпадения 9 может быть реализован, например, с помощью многовходового полного сумматора, входы которого соединены с выходами блока вычисления кода совпадения 8. Число на выходе блока анализа кода совпадения 9 будет характеризовать соответствие принятых символов маркера эталонным символам маркера.

Решение о наличии комбинации маркера во входной последовательности символов принимают в случае, если число несовпадений принятых символов маркера и эталонных символов маркера, то есть количество ошибок во входной последовательности символов, не превышает некоторого порогового значения d0, определяемого синхронизирующими свойствами маркера. Такое решение принимает пороговый блок 12, который анализирует число ошибок во входной последовательности, и в случае, если оно не превышает порогового значения, выдает сигнал о наличии маркера во входной последовательности символов. Одновременно с элемента сравнения с эталонной комбинацией маркера 6 на выход устройства, поступает код фазы входной последовательности символов.

В качестве примера рассмотрим цикловую синхронизацию с помощью 32-х разрядного маркера вида

00001001011001111100011011101010.

Эта последовательность символов является последовательностью максимальной длины и имеет хорошие синхронизирующие свойства. Циклические сдвиги этой последовательности символов отличаются друг от друга не менее чем в 16 позициях. При количестве элементов памяти 3 в каждой группе 2 элементов памяти регистра сдвига 1, равном 9 (K=8), регистр сдвига 1 будет состоять в рассматриваемом примере из 5 групп 2 элементов памяти. При приеме символов маркера из канала связи с фазой сдвига, равной 2, и ошибками на 15 и 29 месте маркера в регистре сдвига 1 будет находиться последовательность символов

*******00 00100101 10011011 00011011 100010**,

где символом * обозначены двоичные символы, не являющиеся символами маркера. Во второй группе 2 элементов памяти будет находиться последовательность символов 00100101, которая поступает на вход элемента сравнения с эталонной комбинацией маркера 6. Элемент сравнения с эталонной комбинацией маркера 6 преобразует двоичный код 00100101 в код фазы сдвига символов маркера в канале связи, который равен 2. Для этой фазы сдвига символов маркера первый генератор маскирующей последовательности 5 выдает код, равный 00000011, второй генератор маскирующей последовательности 10 аналогичным образом выдает код, равный 11111111 11111111 11111100.

На выходе первой схемы И 4 будет последовательность символов 00000000, на выходе второй схемы И 11 - последовательность символов 10011011 00011011 10001000. Генератор символов маркера 7 преобразует код фазы сдвига символов маркера, равный 2, в эталонные символы маркера 00000000100111110001101110101000.

Блок вычисления кода совпадения 8 осуществляет поразрядное сложение по модулю два принятых символов маркера, которые поступают с выходов первой и второй схем И 4 и 11, и эталонных символов маркера. На выходе блока вычисления кода совпадения 8 будет последовательность символов 000000000000100000000000100000.

Блок анализа кода совпадения 9 вычисляет вес Хемминга этой последовательности, то есть количество единиц в последовательности символов. В результате будет получено число d=2. Пороговый блок 12 сравнивает это число с пороговым значением d0=3 и, поскольку d<d0, выдает сигнал наличия маркера цикловой синхронизации.

Отметим также, что предлагаемое устройство может быть реализовано как аппаратным, так и программно-аппаратным путем. В последнем случае включение уже существующих отдельных элементов ЭВМ (сумматоров, запоминающих устройств, регистров) в предлагаемое устройство дает выигрыш в объеме оборудования. Наибольшее сокращение аппаратных затрат дает использование запоминающих устройств ЭВМ для реализации элемента сравнения с эталонной комбинацией маркера 6, первого и второго генераторов маскирующей последовательности 5 и 10, генератора символов маркера 7. Содержимое этих запоминающих устройств ЭВМ может загружаться с внешних носителей информации, например, с гибких или жестких магнитных дисков. Программная реализация с использованием алгоритмических языков программирования высокого уровня (Pascal, С и т.д.) позволяет достаточно просто выполнять поразрядные вычисления логического И и суммирования по модулю два, необходимые для реализации первой и второй схемы И 4 и 11, а также блока вычисления кода совпадения 8.

В предлагаемом изобретении, в отличие от известного устройства, фазу входной последовательности определяют только для второй группы символов, что требует меньшего объема памяти ЗУ для реализации устройства, то есть упрощает устройство выделения маркера цикловой синхронизации. Код совпадения для символов, не входящих во вторую группу символов входной последовательности, определяют для всех остальных групп символов в целом, а не по группам, как в прототипе, что повышает помехоустойчивость устройства выделения маркера цикловой синхронизации по сравнению с известным устройством.

Достигаемым техническим результатом предлагаемого устройства выделения маркера цикловой синхронизации является упрощение устройства и повышение его помехоустойчивости.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ВЫДЕЛЕНИЯ МАРКЕРА ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2001 |

|

RU2210869C2 |

| СПОСОБ ВЫДЕЛЕНИЯ МАРКЕРА ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2341027C1 |

| СПОСОБ ВЫДЕЛЕНИЯ МАРКЕРА ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2002 |

|

RU2231929C2 |

| СПОСОБ ВЫДЕЛЕНИЯ МАРКЕРА ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2001 |

|

RU2183911C1 |

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2251210C1 |

| Декодирующее устройство | 1990 |

|

SU1783626A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА РАДИОСТАНЦИЙ | 1994 |

|

RU2099868C1 |

| Устройство для цикловой синхронизации | 1979 |

|

SU866772A1 |

| Устройство для выделения маркера кадровой синхронизации | 1989 |

|

SU1663775A1 |

Устройство выделения маркера цикловой синхронизации относится к области электросвязи и может быть использовано для цикловой синхронизации сообщений в системах передачи дискретной информации. Технический результат - повышение помехоустойчивости. Устройство выделения маркера цикловой синхронизации содержит регистр сдвига, элемент сравнения с эталонной комбинацией маркера и блок анализа кода совпадения, первую схему И, первый генератор маскирующей последовательности, генератор символов маркера, блок вычисления кода совпадения, вторую схему И, второй генератор маскирующей последовательности и пороговый блок. При этом вход регистра сдвига является информационным входом устройства выделения маркера цикловой синхронизации, регистр сдвига состоит из совокупности последовательно соединенных групп элементов памяти и выход второй группы элементов памяти соединен со входом элемента сравнения с эталонной комбинацией маркера. Выход элемента сравнения с эталонной комбинацией маркера подключен к входу первого и второго генератора маскирующей последовательности, к входу генераторов символов маркера и выходу синхронизации устройства, выход генератора символов маркера подключен к входу блока вычисления кода совпадения, выход блока вычисления кода совпадения соединен с входом блока анализа кода совпадения, выход которого подключен к входу порогового блока, выход которого является информационным выходом устройства выделения маркера цикловой синхронизации. 1 ил.

Устройство выделения маркера цикловой синхронизации, содержащее регистр сдвига, элемент сравнения с эталонной комбинацией маркера и блок анализа кода совпадения, при этом вход регистра сдвига является информационным входом устройства выделения маркера цикловой синхронизации, регистр сдвига состоит из совокупности последовательно соединенных групп элементов памяти и выход второй группы элементов памяти соединен со входом элемента сравнения с эталонной комбинацией маркера, отличающееся тем, что в устройство введены первая схема И, первый генератор маскирующей последовательности, генератор символов маркера, блок вычисления кода совпадения, вторая схема И, второй генератор маскирующей последовательности и пороговый блок, при этом выход первой группы элементов памяти соединен с входом первой схемы И, другой вход которой подключен к выходу первого генератора маскирующей последовательности, выход первой схемы И соединен с входом блока вычисления кода совпадения, выход элемента сравнения с эталонной комбинацией маркера подключен к входам первого и второго генератора маскирующей последовательности, выходу синхронизации устройства, а также к входу генератора символов маркера, выход второго генератора маскирующей последовательности соединен с входом второй схемы И, другие входы которой подключены к выходам групп элементов памяти, начиная с третьей группы элементов памяти и заканчивая последней группой элементов памяти, выход второй схемы И соединен с входом блока вычисления кода совпадения, другой вход которого подключен к выходу генератора символов маркера, выход блока вычисления кода совпадения соединен с входом блока анализа кода совпадения, выход которого подключен к входу порогового блока, выход которого является информационным выходом устройства выделения маркера цикловой синхронизации.

| УСТРОЙСТВО ВЫДЕЛЕНИЯ МАРКЕРА ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2001 |

|

RU2210869C2 |

| СПОСОБ ВЫДЕЛЕНИЯ МАРКЕРА ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2002 |

|

RU2231929C2 |

| СПОСОБ ВЫДЕЛЕНИЯ МАРКЕРА ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2001 |

|

RU2183911C1 |

| US 4641327 А, 03.02.1987 | |||

| DE 4107640, А1, 10.09.1992 | |||

| US 4376309 А, 08.03.1983 | |||

| DE 3611959 A1, 22.10.1987. | |||

Авторы

Даты

2006-03-10—Публикация

2004-09-13—Подача