Изобретение относится к аналого-цифровому и цифроаналоговому преобразованию речевых сигналов. Более конкретно, настоящее изобретение относится к аналого-цифровым и цифроаналоговым преобразователям (АЦП и ЦАП) для телефонных передающих и коммутационных систем и радиотелефонных систем с импульсно-кодовой модуляцией (ИКМ), в которых речевые сигналы или радиосигналы обрабатываются, по меньшей мере частично, в цифровом виде в процессорах.

В результате аналого-цифрового преобразования цифровой обработки сигналов (ПЦОС) аналоговый сигнал речевого источника, получаемый например с микрофона, преобразуется в поток цифровых отсчетов, вводимый в ПЦОС. ЦАП принимает обработанные цифровые отсчеты из ПЦОС и преобразует их в аналоговые колебания для возбуждения, например, головного телефона.

Громкоговорящие устройства, такие как телефоны или сотовые радиотелефоны, из соображений экономичности используют специализированные интегральные схемы (ИС), в которых АЦП и ЦАП являются встроенными, в числе множества средств иного орального назначения, реализуемого в ИС. Эти ИС характеризуются низкой потребляемой мощностью, что предоставляет определенные преимущества, особенно когда используются ручные телефоны, запитываемые от батарей. Настоящее изобретение обеспечивает реализацию усовершенствованного способа цифрового преобразования речевых сигналов при низком потреблении мощности, пригодного для кремниевых ИС с высокой степенью интеграции.

Для преобразования в цифровую форму аналоговых речевых сигналов используются два основных способа: способ последовательного двоичного приближения и способ дельта-сигма-модуляции с избыточной дискретизацией.

В АЦП последовательного приближения отсчет аналогового входного сигнала сначала сравнивается с аналоговым напряжением, соответствующим "1" в позиции старшего двоичного разряда (СДР) требуемого цифрового представления с "0" в остальных позициях (100000...). Если входное напряжение больше, чем это аналоговое напряжение, то позиции СДР будет соответствовать "1". Однако, если напряжение входного сигнала меньше этого аналогового напряжения, то "1" для СДР слишком велика и требуется "0". В результате этого сравнения для СДР устанавливается в A и генерируется напряжение, соответствующее цифровому коду (A100000...). Если входное напряжение больше, чем этот цифровой код, то требуется "1" во втором разряде, в противном случае - "0". В соответствии с этим генерируется напряжение, соответствующее коду (AB10000...) и сравнивается со входным напряжением, и т.д.

Практическим недостатком метода последовательного приближения является то, что АЦП должен включать в себя ЦАП, который должен генерировать напряжения, соответствующие всем возможным кодам, при этом необходимая точность по напряжению для различения кодов 10000000...и 01111111... может быть чрезмерно высокой для обеспечения точности более чем 8-разрядного преобразования. Типовая точность преобразования, требуемая в случае преобразований речевых сигналов составляет 13 разрядов, что позволяет охватить полный динамический диапазон различных речевых сигналов при сохранении достаточного качества. Точность в 13 разрядов требует использования резисторов с чрезвычайно малым допуском (например, 0,01%). Такая технология может оказаться неприемлемой для таких же процессов обработки, необходимых для воспроизведения других характерных особенностей требуемой кремниевой ИС.

Второй из обычно используемых хорошо известных способов определяется как дельта-модуляция с избыточной дискретизацией или дельта-сигма-модуляция. Этот способ позволяет избежать необходимости в точных значениях компонент. Дельта-модуляция с избыточной дискретизацией включает в себя сравнение напряжения на выходе интегратора (например, заряд на конденсаторе) с напряжением входного сигнала и генерирование решения "на разряд выше" (1) или "на разряд ниже" (0). Интегратор (заряд на конденсаторе) затем получает приращение или уменьшение на определенную ступеньку, так что он отслеживает входной сигнал. Ступеньки с размером положительного или отрицательного приращения прикладываются к интегратору. Это "аналоговый" сигнал (хотя он может рассматриваться также и как двоичный цифровой сигнал), хотя и не сглаженный. Как аналого-цифровое, так и цифроаналоговое дельта-сигма преобразование осуществляются указанным способом. Путем передачи ступенек вверх/вниз и приложения их к удаленному интегратору может быть воспроизведена та же самая форма напряжения, индицирующая информацию, содержащуюся в потоке разрядов.

Шумы квантования, присущие дискретизации за счет дельта-модуляции с высокой скоростью следования разрядов, уменьшаются на 9 дБ при каждом удвоении скорости разрядов (скорости ступенек вверх/вниз). Если ступеньки прикладываются к интегратору в два раза чаще, они будут лишь половинного размера, чтобы отслеживать ту же самую скорость изменения сигнала. Таким образом, ступенчатый сигнал отслеживает входной сигнал вдвое ближе, что проявляется в выигрыше в 6 дБ. Кроме того, отклонения ступенчатого сигнала от входного сигнала происходит с удвоенной частотой, растягивая шумы квантования по двойному частотному диапазону, так что только половина их перекрывает область спектра сигнала. Шумы вне этой области будут режектированы фильтром нижних частот, который пропускает только спектр желательного сигнала, а не более высокочастотные компоненты шумов квантования. Этот дополнительный фактор обеспечивает дополнительный выигрыш 3 дБ, так что общий выигрыш по качеству от удвоения разрядной скорости составляет 9 дБ.

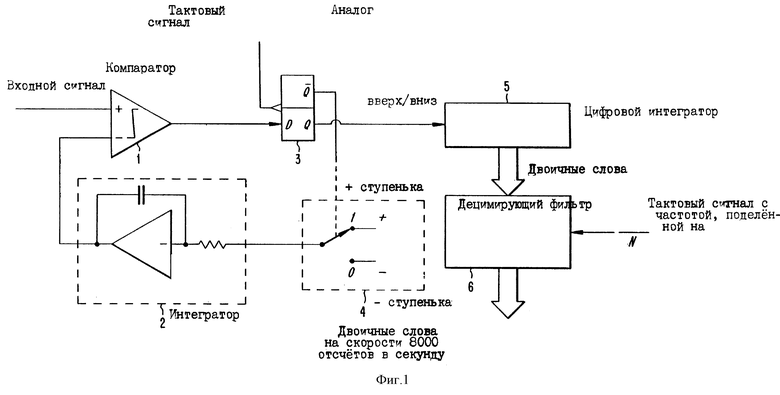

Блок-схема устройства дискретизации, основанного на использовании дельта-модуляции с избыточной диксретизацией, представлена на фиг. 1. Входной речевой сигнал прикладывается к одному входу компаратора 1, а к его другому входу прикладывается выходной сигнал интегратора 2. Выходной сигнал компаратора представляет собой двоичное решение высокого/низкого уровня, и тактируется в триггер 3 тактовым сигналом дельта-модуляции с высокой разрядной скоростью. Частота этого тактового сигнала в N раз выше желательной конечной частоты отсчетов. Выходные сигналы высокого/низкого уровня управляют переключателем 4, обеспечивая выбор положительного или отрицательного напряжения для приложения его к интегратору 2 так, чтобы оно следовало за входным сигналом в ступенчатом виде. Одновременно те же выходные сигналы высокого/низкого уровня прикладываются к цифровому интегратору 5, так что его выходной сигнал отслеживает тот же образец, но уже в качестве цифрового представления сигнала. Мгновенное значение на выходе цифрового интегратора 5 изменяется на каждый такт, что в N раз превышает желательную выходную скорость дискретизации. Эти значения прикладываются к цифровому фильтру 6 нижних частот (или децимации, прореживания), который удаляет быстрые флюктуации значений в каждом периоде из N следующих друг за другом тактов, обеспечивая в то же время изменения этого значения с медленными частотами, лежащими в диапазоне основных речевых частот, до 3,4 кГц. После цифровой низкочастотной фильтрации значение может быть дискретизировано с желательной выходной скоростью дискретизации в 8000 отсчетов в секунду с учетом выполнения критерия Найквиста для исключения потерь информации, т.е. частота дискретизации должна быть по меньшей мере вдвое больше наивысшей частотной компоненты сигнала (теперь составляющей 3400 Гц).

Одним из преимуществ известного способа дельта-модуляции с избыточной дискретизацией является то, что не требуется никакого аналогового фильтра для исключения ступенчатости с частотой отсечки на 3,4 кГц, т.к. эта функция выполняется в цифровом виде. Кроме того, не требуется никаких прецизионных аналоговых компонентов и фактически все используемые компоненты являются элементами цифровой логики, пригодными для интеграции на кремниевом кристалле.

Недостатком этого метода для некоторых применений является то, что для обеспечения требуемого 13-разрядного динамического диапазона необходим высокий коэффициент N избыточной дискретизации, равный в этом случае 256. Таким образом, фильтры децимации должны выполнять большое количество вычислительных операций в секунду, увеличивая потребление мощности в цифровой части. В различных публикациях, например Naus et al., "A.CMOS Stereo 16-bit D/A Converter For Digital Audio; IEEE Yournal of Solid State Circuits, т. SC22 N 3, June 1987, рассмотрены способы достижения высокого качества при использовании низких коэффициентов избыточной дискретизации. Такие способы основаны на применении фильтра обратной связи более сложного, чем простой интегратор, для придания спектру шумов квантования такой формы, чтобы в пределы речевого диапазона 3,4 кГц попадала меньшая часть шумов.

В патенте США N 4783644, выданном Кильхспергеру (Kilchsperger) описан дельта-модулятор с использованием цифрового вектора для непрерывного изменения крутизны. В патенте США N 4151517, выданном Келли (Kelley), описано устройство дельта-модуляции с непрерывно изменяемой крутизной для кодирования и декодирования входных сигналов.

Настоящее изобретение предусматривает новый способ для преобразования аналогового речевого сигнала в цифровую форму, который основан не на формировании шумового спектра, а на компандировании (сжатии сигнала в одной точке и восстановлении его путем расширения в другой точке), таком как компандированная дельта-модуляция. Наиболее известный принцип компандированной дельта-модуляции определяется как дельта-модуляции с непрерывно изменяемым наклоном (ДМНИН) и используется в случаях, когда дельта-модуляция с низкой разрядной скоростью является конечной формой кодирования, в которой желательно передавать или хранить речевой сигнал. ДМНИН широко используется в системах радиосвязи военного назначения со скоростями 16 кбит/с, 19,2 кбит/с и 32 кбит/с. На последней из упомянутых разрядных скоростей качество в общем случае рассматривалось как сравнимое с хорошим качеством телефонного сигнала.

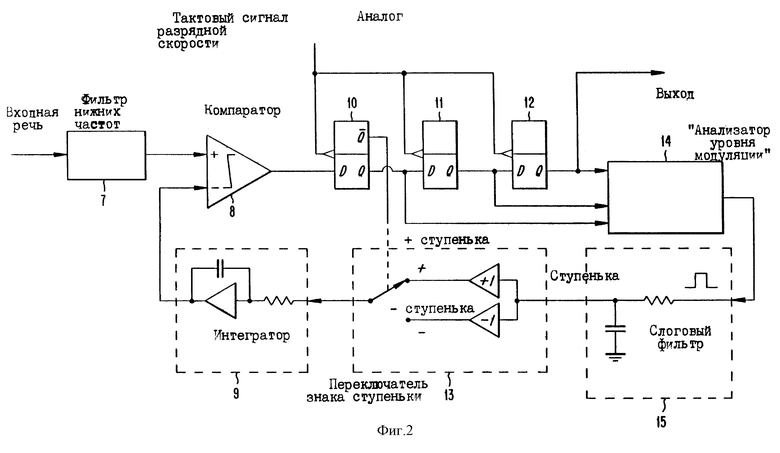

Блок-схема известного речевого кодера ДМНИН показана на фиг. 2. Выходной речевой сигнал сначала ограничивается в полосе частот до диапазона 0-3,4 кГц фильтром 7 нижних частот, защищающим от наложения спектров. Отфильтрованная речь затем прикладывается к одному из входов компаратора 8, к другому входу которого приложен выходной сигнал основного интегратора 9.

Выходные сигналы высокого/низкого уровня компаратора 8 подаются в триггер 10 на каждый такт генератора тактового сигнала разрядной скорости (не показан). Сигналы высокого/низкого уровня, регистрируемые триггером 10, управляют выбором либо напряжения отрицательной ступеньки, либо напряжения положительной ступеньки, приложенного к основному интегратору 9 через знаковый переключатель 13 ступенек. Сигналы высокого/низкого уровня кроме того задерживаются в триггерах 11 и 12, так что каждые три следующих друг за другом таких сигнала доступны анализатору 14 модуляции. Анализатор 14 модуляции обнаруживает случай, когда все три следующих друг за другом сигнала одинаковы (высокий, высокий и высокий или низкий, низкий и низкий) и определяет, когда в интеграторе 9 возникают затруднения в отслеживании скорости изменения входного сигнала с текущим размером ступеньки. Тогда анализатор 14 модуляции направляет импульс в слоговый фильтр 15 для приращения размера ступеньки. Если импульсов нет, слоговый фильтр 15 позволяет размеру ступеньки уменьшаться по экспоненте до тех пор, пока не наступит естественное равновесие со входным сигналом, так что интегратор 9 сможет отслеживать входной сигнал с минимальным размером ступеньки. Размер ступеньки таким образом подстраивается к уровню входного сигнала. Более того, размер ступеньки быстро подстраивается к изменениям уровня между разными словами и слогами слов (отсюда название фильтра - "слоговый фильтр"). Поэтому воспринимаемое качество речи поддерживается несмотря на разрядные скорости, намного превышающие те, что требуются в отсутствие компандирования.

Уровень техники для ЦАП аналогичен уровню техники для АЦП, включая два основных способа.

Обычные ЦАП основаны на точной резисторной цепи (например, лестничной R-2R), либо на дельта-модуляции с излишней дискретизацией или дельта-сигма-модуляции. Третий известный способ использует широтно-импульсную модуляцию. Когда требуется 13-разрядная или более высокая точность, метод, требующий точной резисторной цепи, может быть непригоден для интегрирования в большие кремниевые кристаллы из-за конфликтующих производственных требований. Метод некомпадированной дельта-модуляции с избыточной диксретизацией имеет тот недостаток, что фильтры децимации должны работать с высокой скоростью вычислений, потребляя более высокую мощность. Настоящее изобретение использует компандированную дельта-модуляцию, позволяющую существенно снизить разрядную скорость при поддержании данного качества речи.

Использование ДМНИН в качестве основы для двоичного АЦП с избыточной дискретизацией, требующей децимации и снижения частоты дискретизации, раньше считалось весьма сложным из-за свойственной компандированию нелинейности. Так, невозможно просто фильтровать поток разрядов как в некомпадированной дельта-модуляции. В патенте США 3949299 описан способ оцифровки речи, использующий ограниченную форму компандирования, что в некоторой степени решает вышеотмеченную проблему фильтрования потока разрядов, при этом использовались семь или восемь относительно грубых ступенек компандирования в логарифмических/экспоненциальных амплитудных последовательностях 1, 2, 4, 8, 16 и т.д.

С другой стороны, относительно грубые ступеньки усиления 6 дБ, обеспечиваемые в вышеуказанном патенте степенями двух размеров ступенек, нежелательны, когда требуется высокое качество речи, потому что соответствующее устройство не гарантирует согласования декомпандированного сигнала с компандированным и потому не сохраняет абсолютное канальное усиление.

Настоящее изобретение позволяет исключить вышеотмеченные ограничения аналога, такого как устройство по патенту США N 3949299 в частности, связанных с малым числом размеров ступенек, и другие недостатки аналога. Эта задача решается в настоящем изобретении путем использования линейного цифрового слогового фильтра и формируемого им полного цифрового значения в процессе децимации.

В настоящем изобретении предусматривается средство преобразования речевого сигнала в одну или две желательных формы: (1) 13-разрядную линейную эквивалентную ИКМ (импульсно-кодовую модуляцию) со скоростью 8000 отсчетов в секунду, либо (2) компандированную дельта-модуляцию с низкой разрядной скоростью.

Это осуществляется с помощью промежуточной операции преобразования в дельта-модуляцию со средней разрядной скоростью, компандируемой с использованием линейного цифрового слогового фильтра. Результат преобразования компандированной дельта-модуляцией со средней разрядной скоростью на цифровой интегратор с утечкой, и на аналоговый интегратор, так что цифровое значение увеличивается и уменьшается так же, как на аналоговом интеграторе, чтобы вырабатывать цифровое значение, которое отслеживает речевой сигнал так же, как значение на аналоговом интеграторе отслеживает речевой сигнал. Затем цифровое представление фильтруется в цифровом фильтре для удаления высокочастотных шумов квантования и дискретизируется с требуемой выходной частотой. Эта комбинация цифровой низкочастотной фильтрации и уменьшения частоты диксретизации характеризует собой вышеназванные "снижение частоты дискретизации" или "децимацию".

Схема для преобразования аналогового сигнала в цифровую форму согласно настоящему изобретению включает в себя средство интегрирования для выработки проинтегрированного сигнала и средство для сравнения сигнала аналогового сида с проинтегрированным сигналом и регистрации последовательности результатов сравнения по одному результату на очередной интервал. Схема содержит также средство для установки знака ступеньки проинтегрированного сигнала на основании самого последнего зарегистрированного результата, средство фильтрации слогов для выбора величины ступеньки на основании зарегистрированных результатов и фильтр децимации для обработки знака ступеньки и величины ступеньки и выработки последовательности двоично-кодированных цифровых сигналов, представляющих сигнал аналогового сида. В одном из вариантов выполнения средство интегрирования включает в себя по меньшей мере программируемый источник тока, соединенный с конденсатором, который может программироваться согласно желательной величине ступеньки или длительности импульса тока.

Средство фильтрации слогов может включать в себя средство для последовательного запоминания записанных результатов обработки в виде разрядной последовательности и логическое средство для выполнения логических операций над разрядной последовательностью и выработки накопленного значения, индуцирующего величину ступеньки в соответствии с выполняемыми логическими операциями. Фильтр децимации может включать в себя интегратор с утечкой для интегрирования разрядной последовательности и получения числового значения и для вычитания части числового значения из числового значения в регулярно выбранные интервалы.

Величина ступеньки согласно предпочтительному выполнению определяется 12-разрядным двоично-кодированным значением. Двоично-кодированное значение управляет первым программируемым источником тока согласно числу наименьших значащих разрядов и вторым программируемым источником тока согласно числу наибольших значащих разрядов.

Другая схема аналого-цифрового преобразования согласно настоящему изобретению включает в себя средство для сравнения аналогового входного сигнала с напряжением на конденсаторе и регистрации последовательности решений по одному решению на очередной интервал и по меньшей мере один источник тока с широтно-импульсной модуляцией для управления конденсатором в соответствии с последовательностью результатов. Эта схема может также содержать накопитель, накопленное значение которого изменяется ступенчато, с управлением конденсатором путем изменения длительности импульсов. Схема может также содержать средство для сложения N следующих друг за другом значений накопителя с выработкой ряда двоично-кодированных выходных значений, по одному двоично-кодированному выходному значению на N периодов изменения значения накопителя, и двоично-кодированные значения представляют аналоговый входной сигнал. Последовательности результатов в этом варианте выполнения могут выводиться как поток разрядов с компандированной дельта-модуляцией, представляющий аналоговый входной сигнал.

Схема для преобразования множества двоично-кодированных числовых отсчетов сигнала в аналоговый сигнал согласно настоящему изобретению включает в себя средство для интерполяции между последовательными двоично-кодированными числовыми отсчетами сигнала для выработки N интерполированных отсчетов для каждого двоично-кодированного числового отсчета сигнала, средство для сравнения интерполированных отсчетов со значениями в цифровом интеграторе и регистрации последовательности результатов обработки и средство для изменения значений цифрового интегратора в соответствии с результатами с использованием знака ступеньки. Кроме того, в схему включены средство фильтрации слогов для выработки величины ступеньки и изменения значений цифрового интегратора в зависимости от числа последовательных результатов обработки, аналоговое интегрирующее средство с утечкой для получения знака ступеньки и величины ступеньки и выработки аналогового сигнала, описываемого в числовом виде значениями цифрового интегратора, и средство для фильтрации аналогового сигнала и выработки аналогового колебания, соответствующего двично кодированным числовым отсчетам сигнала.

Средство фильтрации слогов может быть выполнено так же, как аналогичное вышеописанное средство. Аналоговое интегрирующее средство может включать в себя по меньшей мере один программируемый источник тока, соединенный с конденсатором. По меньшей мере один программируемый источник тока может программироваться, как указано выше.

В другом варианте выполнения настоящего изобретения схема ЦАП содержит средство для приема потока разрядов компандированной дельта-модуляции и слоговое фильтрующее средство для выработки множества переменных величин ступенек, основанных на числе последовательных разрядов в разрядном потоке. В схему также включены интегрирующее средство, изменяемое переменными величинами ступенек согласно знаку разрядов в разрядном потоке, для выработки аналогового выходного сигнала и средство для фильтрации аналогового выходного сигнала получения аналогового колебания, соответствующего разрядному потоку.

Способ преобразования сигнала аналогового вида в сигнал цифрового вида согласно настоящему изобретению включает операции выработки проинтегрированного сигнала, сравнения сигнала аналогового вида с проинтегрированным сигналом и записи ряда решений по одному решению на очередной интервал, и установки знака ступенек проинтегрированного сигнала, основанного на самом последнем из записанных решений. Способ дополнительно включает в себя операции выбора величины ступенек, основанного на записанных решениях, и обработки знака ступенек и величины ступенек для выработки последовательности двоично-кодированных цифровых сигналов, представляющих сигнал аналогового вида.

Способ преобразования множества двоично-кодированных числовых отсчетов сигнала в аналоговый сигнал согласно настоящему изобретению включает операции интерполяции между последовательными двоично-кодированными числовыми отсчетами сигнала и получение N интерполированных отсчетов для каждого двоично-кодированного числового отсчета сигнала, сравнения интерполированных отсчетов со значениями в цифровом интеграторе и регистрации ряда результатов сравнения. Кроме того, в способ включены следующие операции: изменение значений цифрового интегратора в соответствии с результатами сравнения с помощью знака ступенек, выработка величины ступенек для изменения значений цифрового интегратора в зависимости от числа последовательных результатов, прием знака ступеньки и величины ступеньки и выработка аналогового сигнала, описываемого в числовом виде значениями цифрового интегратора, и фильтрация аналогового сигнала для получения аналогового колебания, соответствующего двоично-кодированным числовым отсчетам сигнала.

Настоящее изобретение будет описано более подробно со ссылками на предпочтительные варианты выполнения, приведенные в качестве примеров, иллюстрируемых чертежами, на которых представлено следующее.

Фиг. 1 - пример обычного АЦП с дельта-модуляцией с избыточной дискретизацией.

Фиг. 2 - пример обычного речевого кодера с ДМНИН.

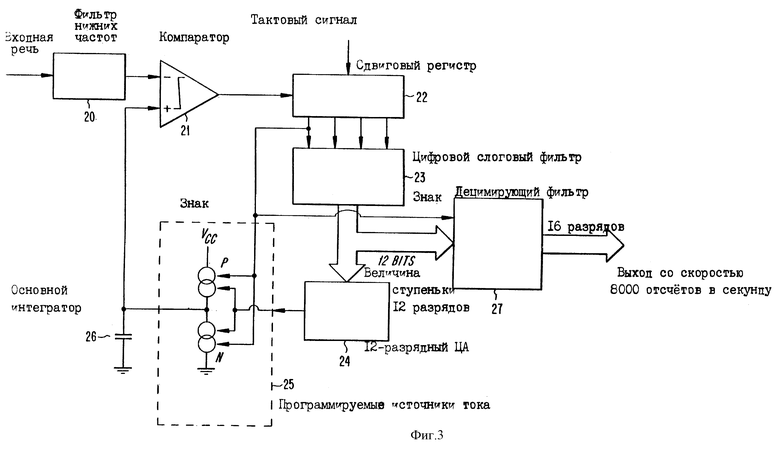

Фиг. 3 - пример речевого кодера согласно настоящему изобретению.

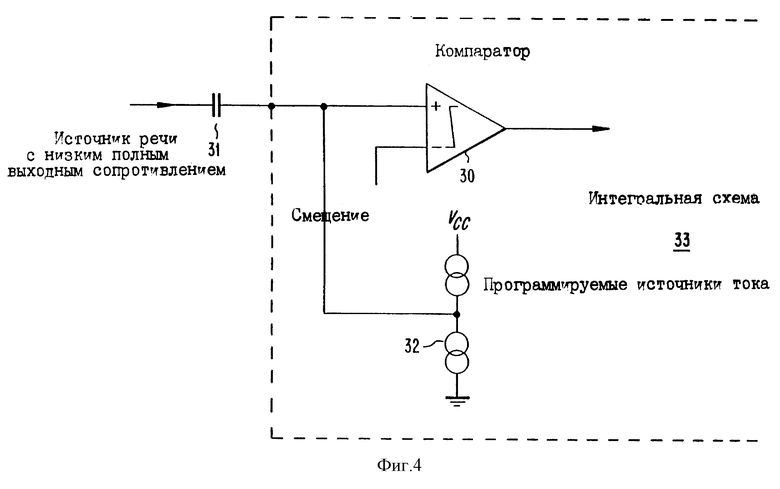

Фиг. 4 - пример конфигурации компаратора и основного интегратора для речевого кодера согласно настоящему изобретению.

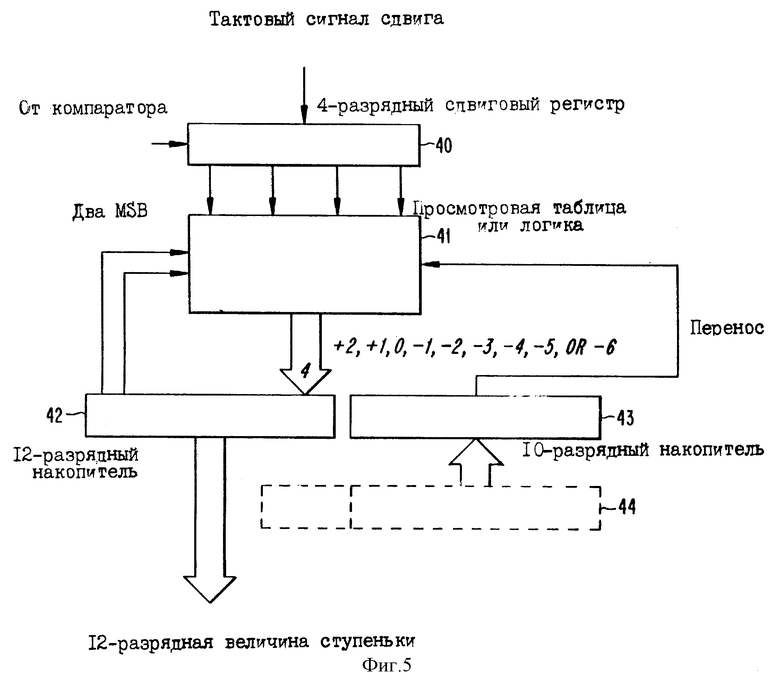

Фиг. 5 - пример конфигурации слогового фильтра согласно настоящему изобретению.

Фиг. 6 - пример фильтра децимации согласно настоящему изобретению.

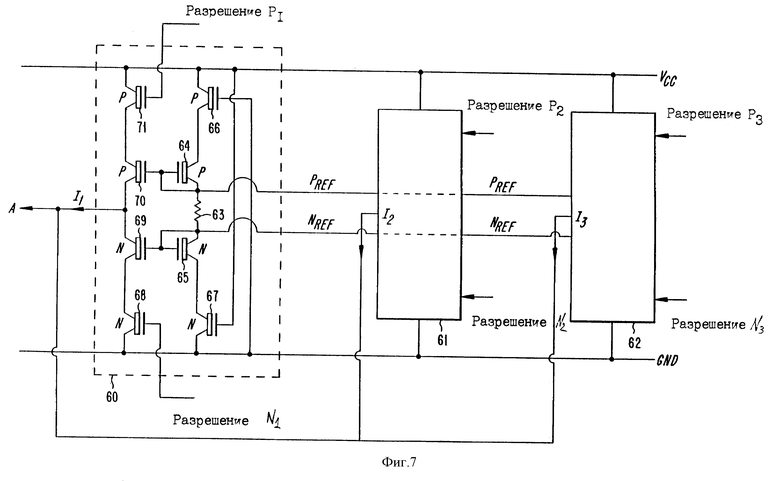

Фиг. 7 - пример конфигурации программируемого источника тока и 12-разрядного ЦА преобразователя согласно настоящему изобретению.

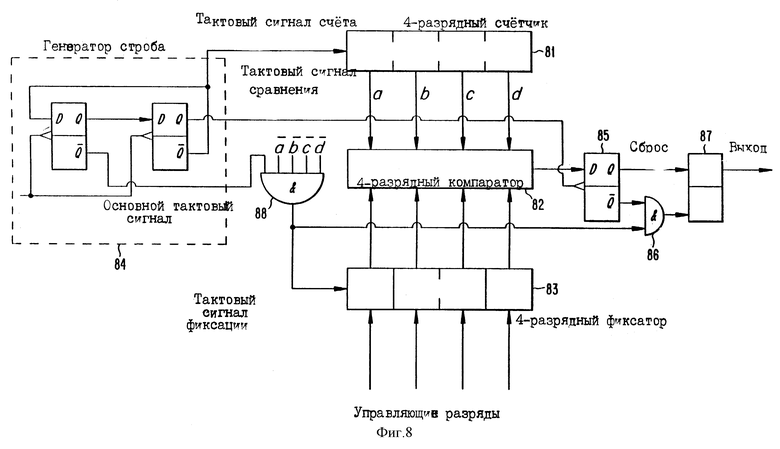

Фиг. 8 - пример широтно-импульсного контроллера тока согласно настоящему изобретению.

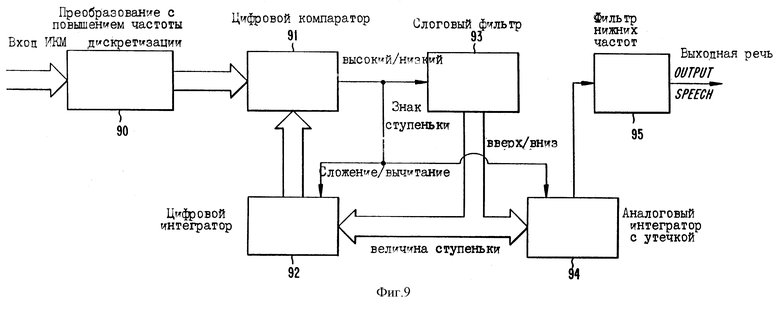

Фиг. 9 - пример ЦАП согласно настоящему изобретению.

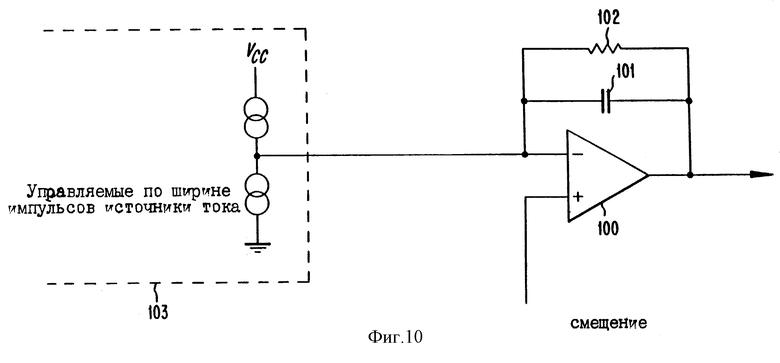

Фиг. 10 - примерная конфигурация аналогового интегратора с утечкой согласно настоящему изобретению.

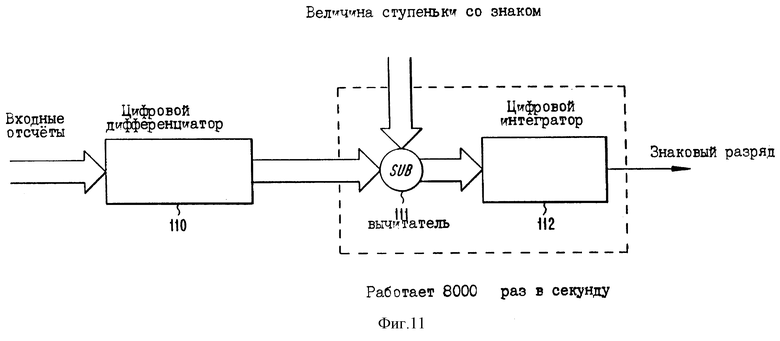

Фиг. 11 - примерная конфигурация для выполнения линейной интерполяции, интегрирования и сравнения согласно одному из вариантов выполнения настоящего изобретения.

Описание предпочтительных вариантов выполнения изобретения.

Согласно настоящему изобретению, показанному на фиг. 3, входная речь подвергается низкочастотной фильтрации в фильтре 20. Полоса пропускания фильтра определяется частотами от 0 до 3,4 кГц, с ослаблением на частотах 4 кГц и выше, что помогает иметь простой цифровой децимирующий фильтр. Разрядная скорость дельта-модуляции либо 200 кбит/с; либо 240 кбит/с с соответствующим коэффициентом N избыточной дискретизации 25 или 30.

Отфильтрованный речевой сигнал прикладывается к одному из входов средства для сравнения 21, ко второму входу которого приложен выходной сигнал основного интегратора 26. Основной интегратор 26 образован конденсатором, включенным между выходом программируемого источника 25 тока и землей. Программируемый источник 25 тока вырабатывает ток нарастания от интегрального источника тока, выполненного на транзисторах P-типа, или ток убывания от интегрального источника тока, выполненного на транзисторах N-типа, так что напряжение на конденсаторе может увеличиваться или уменьшаться, чтобы отслеживать речевой сигнал. Смена знака вверх или вниз определяется результатом сравнения высокий/низкий уровень в средстве для сравнения 21, регистрируемым на каждый такт в первом триггерном каскаде средства 22 для определения знака ступеньки. Это зависит от того, какой источник - P- или N-типа - использован в программируемом источнике тока 25. Основной интегратор 26 и программируемые источники тока 25 составляют первое интеграторное средство.

Средство 22 для определения знака ступеньки, кроме того, задерживает результат сравнения высокий/низкий уровень в трех последующих каскадах так, что четыре последовательных результата сравнения доступны цифровому слоговому фильтру 23. В зависимости от комбинации четырех результатов слоговый фильтр 23 либо увеличивает 12-разрядное значение на один или два, либо уменьшает его на один или два, либо не делает ничего. Результирующее 12-разрядное значение представляет величину ступеньки, которая будет использоваться для увеличения или уменьшения значения основного интегратора 26. Это 12-разрядное представление величины ступеньки и используется для программирования уровня тока программируемого источника 25 тока с помощью 12-разрядного ЦАП 24.

12-разрядный ЦАП 24 образован разделением 12-разрядного слова на три 4-разрядных отрезка, которые управляют током в трех параллельных источниках 60, 61 и 62 тока, как показано на фиг. 7, с отношением токов 1:16:256. Ток от каждого источника управляется с помощью относящегося к нему 4-разрядного отрезка для управления длительностью его токового импульса, устанавливаемой на одно из 16 значений. Основной интегратор 26 таким образом отслеживает речевой сигнал в виде последовательностей не обязательно равных ступенек вверх или вниз. Величина ступенек задана 12-разрядным выходным сигналом со слогового фильтра 23, тогда как знак ступеньки определяется результатом сравнения в компараторе. 13-разрядная комбинация является, следовательно, представлением последовательностей ступенек с учетом знака и величины ступенек. Если такое представление с учетом знака и величины ступенек интегрируется в цифровом виде в демпфирующем фильтре 27, образуется числовая копия аналогового напряжения на конденсаторе основного интегратора 26.

Децимирующий фильтр 27 накапливает представления знака и величины ступенек в цифровом накопителе, который является частью децимирующего фильтра 27. Накопитель вычитает часть, 1/512, от своего накопленного значения на каждой итерации, чтобы получить интегратор 50 с утечкой, как представлено на фиг. 6. Это обеспечивает то, что накопленное значение не будет дрейфовать к одному крайнему значению или к другому. Доля, определяемая как 1/512, соответствует фильтру верхних частот с частотой сопряжения примерно 64 Гц.

Первую операцию децимирующего фильтра можно выразить математически как

I(i) = (1-1/512)•I(i-1) + D(i),

где D(i) является размером ступеньки, включая знак. Приравнивание коэффициента 1-1/512 коэффициенту экспоненциального затухания за тактовый период Т,

e-ωT = 1-1/512,

приводит к ω Т = 1/512, так что для Т = 1/200000 частота ω немного меньше, чем 400 радиан/с, что соответствует 64 Гц.

Вторая ступень децимирующего фильтра 27 вычисляет сумму проинтегрированных значений по N значениям. Сумма затем выводится на каждый период частоты 8000 Гц.

Частотный отклик вышерассмотренного децимирующего фильтра 27 соответствует квадрату функции sin x/x, где

x = π • f/8000 = ω/16000,

f - частота в Гц, ω - частота, радиан/с.

Это приводит к ослаблению на 2,75 дБ на наивысшей частоте 3,4 кГц речевого сигнала. Чтобы скомпенсировать это ослабление, накопитель на конечной ступени сбрасывается не в нуль перед следующим суммированием N значений, а устанавливается на 1/8 от предыдущего результата. Это приводит к подчеркиванию верхних речевых частот и компенсации смещения sin x/x. Это - отличие от децимирующего фильтра аналога по патенту США N 3949299, в котором смещения высокой частоты можно было избежать накоплением не всех отсчетов, из-за чего, однако, возникал дополнительный недостаток, заключающийся в недостаточном снижении шумов.

Иное выполнение для компаратора и основного интегратора показано на фиг. 4. Компаратор 30 и программируемый источник 32 тока встроены в большую интегральную схему 33. Источник 32 тока соединен с одним входом компаратора и с одним выводом конденсатора 31 основного интегратора. Речевой сигнал, подлежащий кодированию, прикладывается к другому выводу конденсатора 31 интегратора. Напряжение, получаемое интегрированием тока от источника 32 тока, протекающего через конденсатор 31, вычитается из входного речевого сигнала. Остаток от этого вычитания сравнивается в компараторе 30 с фиксированным напряжением смещения в половину напряжения питания (Vcc/2). Компаратор 30 формует результаты сравнения высокого/низкого уровня, который управляет источником 32 тока аналогично тому, как рассмотрено со ссылкой на выполнение по фиг. 3, при равных входных напряжениях компаратора. Преимущество этого устройства в том, что уменьшается число выводов, требуемых для ИС, а компаратор упрощается, потому что его входы должны только работать вблизи фиксированной точки смещения.

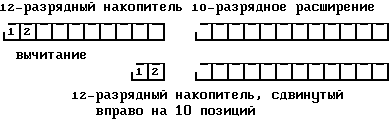

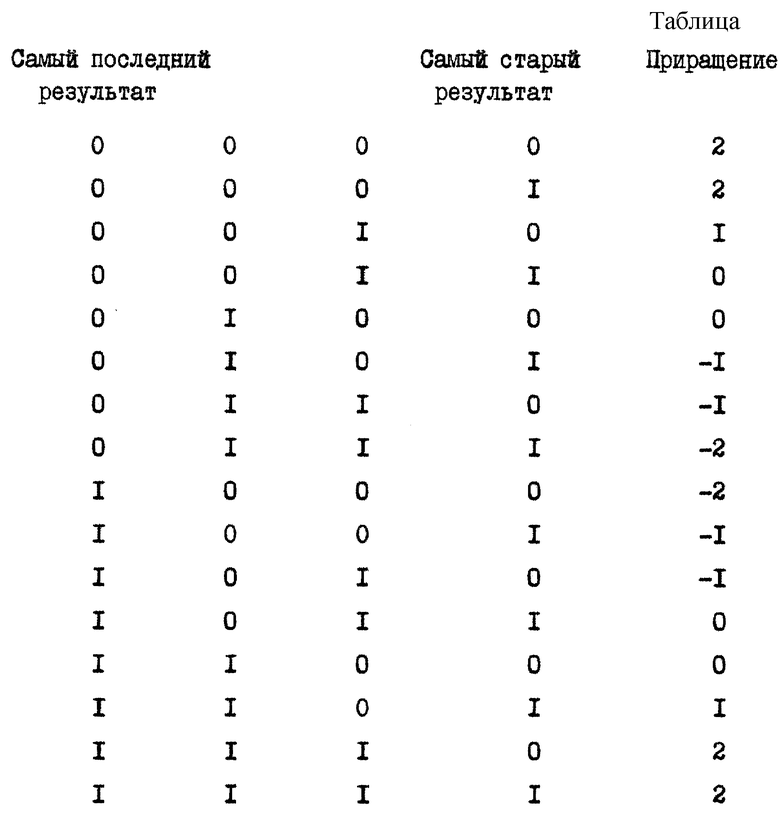

Работа слогового фильтра согласно настоящему изобретению иллюстрируется схемой на фиг. 5. Четыре последовательных результата обработки в компараторе предоставляются сдвиговому регистру 40. Эти результаты определяют, увеличить ли значение 12-разрядного накопителя 42 на 2 или на 1, или уменьшить его на 2 или 1, либо оставить без изменений. Эти варианты выбираются согласно просмотровой таблице или логике 41, показанной в таблице.

Кроме того, 12-разрядный накопитель 42 становится интегратором с утечкой путем вычитания 1/1024-й части накопленного значения из его накопительного значения при каждой итерации. Это гарантирует, что накопленное значение не будет дрейфовать ни к одному из крайних значений и что воздействие любого произвольного начального значения убывает во времени экспоненциально.

Положение разрядов 12-разрядного накопителя 42 показано в блоке 44 после сдвига назад (направо) на 10 позиций, что соответствует делению на 1024. Два его старших двоичных разряда перекрывают два его младших двоичных разряда и должны вычитаться. Это достигается изменением приращения, формируемого согласно таблице.

Коротко говоря, основой компандированного дельта-модулятора со средней разрядной скоростью является интегратор, который вынуждается отслеживать речевой сигнал путем ступенчатого увеличения или уменьшения его значения. Размер ступеньки также увеличивается или уменьшается соответственно на 2, 1, 0, -1 или -2 для обеспечения возможности более эффективного отслеживания. Размер ступеньки содержится в виде цифрового числа в 12-разрядном накопителе, который может получать приращения или уменьшать свое значение на вышеуказанные величины. Кроме того, этот интегратор имеет "утечку", означающую, что 1/1024-я часть его текущего значения вычитается на каждом такте. Это делается для того, чтобы старые значения имели экспоненциально убывающее остаточное влияние на текущие значения и, в частности, чтобы воздействие произвольного начального значения после включения не продолжалось более нескольких миллисекунд.

Чтобы вычесть 1/1024-ю часть 12-разрядного значения из самого этого значения, его необходимо сдвинуть назад на 10 двоичных позиций, а затем вычесть из самого себя, как представлено ниже:

Можно видеть, что только два наиболее значимых разряда 1 и 2 перекрывают тогда исходное 12-разрядное значение, и потому никакого эффекта утечки не может быть для значений, имеющих два нулевых старших разряда. Чтобы убедиться, что желательный эффект накопителя с утечкой достигается для всех значений, накопитель снабжен 10-разрядным расширением, которое накапливает десять младших значащих разрядов вычитаемого, которые не перекрывают 12-разрядный накопитель. Когда 10-разрядное расширение переполняется, это означает, что пропущенные 10-разрядные части накопились в целом до одного младшего значащего разряда 12-разрядного накопителя, так что в дополнение к двум перекрывающим разрядам 1 и 2 должна быть вычтена дополнительная "1".

Таким образом, общий диапазон чисел, которые могут вычитаться из 12-разрядного накопителя, составляет:

Увеличение/уменьшение основного размера ступеньки: 2, 1, 0, -1, -2.

Разряды 1 и 2 10-разрядного сдвига: 0, -1, -2 или -3.

Переполнение из 10-разрядного расширения: 0 или 1.

Итог вышеприведенных комбинаций: 2, 1, 0, -1, -2, -3, -4, -5, -6.

Какое из этих девяти значений следует добавить или вычесть из значения 12-разрядного накопителя, является функцией приращения размера ступеньки, определенного четырьмя последовательными результатами обработки в компараторе, двух текущих старших разрядов накопителя и состоянием переполнения из 10-разрядного расширения накопителя. Таким образом, все семь этих разрядов подаются в качестве входных сигналов на просмотровую таблицу 41, которая заранее запрограммирована одним правильным из вышеуказанных девяти значений для каждого из 128 возможных комбинаций семи адресных разрядов, которые могут возникнуть.

Чтобы обеспечить 10-разрядное расширение, 10 младших значащих разрядов накапливаются в 10-разрядном накопителе 43 и проявляются только тогда, когда происходит перенос через границу 10 и 12 разрядов. Этот перенос может также быть учтен изменением вышерассмотренной таблицы путем внесения в нее 0 или -1 для случая, когда перенос имеет место или отсутствует. Таким образом, просмотровая таблица 41 имеет лишние входы от двух младших значащих разрядов накопителя 42 и от выхода переноса 10-разрядного накопителя 43 и содержит все приемлемые вводимые данные между +2 и -6 для каждого возможного состояния входных линий. Четырехразрядное число достаточно для представления этих девяти возможных значений с учетом знака и величины. Знак управляет накопителем 42 для задания сложения или вычитания трехразрядной величины. 12-разрядная величина является выходом в качестве размера ступеньки для использования при увеличении или уменьшении значения основного интегратора 26 или 31, показанных на фиг. 3 и 4 соответственно. В предпочтительном выполнении может использоваться последовательная арифметика для сложений и вычитаний в накопителе, чтобы минимизировать количество вентилей в интегральной схеме.

Содержимое просмотровой таблицы определено эмпирически для получения наилучших результатов на типичном речевом сигнале. Однако и другое содержимое таблицы может обеспечить в равной степени хорошие или лучшие результаты. Подобным же образом не является основополагающим и число результатов обработки в компараторе, используемое для воздействия на выбор размера ступеньки. Например, могут иметь место малые усиления для использования большого числа результатов обработки в компараторе для воздействия на размер ступеньки. Точная настройка размера ступеньки согласно последним результатам была предметом рассмотрения многочисленных публикаций. Любая такая эмпирически оптимизированная стратегия адаптации размера ступеньки может быть включена в настоящее изобретение. Однако адаптация размера ступеньки все же должна зависеть от текущего размера ступеньки для получения слогового интегратора с утечкой согласно изобретению.

Примерный децимирующий фильтр согласно настоящему изобретению показан на фиг. 6. Знак ступеньки и 12-разрядная величина ступеньки сначала интегрируется в интеграторе 50 с утечкой. Утечка обеспечивается вычитанием 1/512-й (0,000000001) части значения, накопленного интегратором, из накопленного значения на каждой итерации. Это обеспечивает интегратор с потенциальным "усилением" в 512, если на интеграторе 50 присутствует постоянное значение, тем самым расширяя длину слова с 12 разрядов плюс знаковый разряд до 22 разрядов двойного полного представления. Значение интегратора с утечкой составляет 12 разрядов и знак, что идентично 13 разрядам двойного полного представления. При наличии постоянного входного значения для интегрирования значение интегратора будет нарастать до тех пор, пока величина "утечки" не станет постоянной, так что она прекратит нарастать. Поскольку утечка составляет 1/512-ю от значения интегратора, значение в этой точке должно быть в 512 раз больше постоянного значения, т.е. на 9 разрядов длиннее. Таким образом, длина интегратора с утечкой составляет 13 + 9 = 22 разряда.

22-разрядный результат суммируется по N посдедовательным значениям в сумматоре 51, чтобы снизить частоту дискретизации сигнала до требуемой скорости в 8000 отсчетов в секунду.

Поскольку в предпочтительном выполнении N равно 25 или 30, происходит дальнейшее потенциальное расширение длины слова до 27 разрядов. Если два 22-разрядных значения складываются, максимально возможный результат составляет двойное значение, дающее еще один старший разряд, т.е. расширение с 22 до 23 разрядов. Если складываются 4 старших разряда это дает 24 разряда. Если складывается 8 старших разрядов, результат будет 25 разрядов. Если складывается 16 старших разрядов, то получится 26 разрядов. Если складываются 32 старших разряда, то получится 27 разрядов. Последняя длина в 27 разрядов желательна потому, что число складываемых значений (25 или 30) больше чем 16, но меньше чем 32. При нормальной речи на номинальном уровне полный 27-разрядный динамический диапазон может никогда не использоваться. Поэтому может быть выгодно выбрать 16 разрядов из менее значимого сдвига вместо более значимых 16 разрядов для выхода.

Поскольку не всегда возможно заранее принять решение о наилучшем сдвиге для всех применений, можно обеспечить выбор 16-разрядного сдвига, который будет выводиться посредством управляющего входа "выбор сдвига".

После формирования отсчета сумматор 51 не сбрасывается до нуля перед следующим периодом суммирования, но уменьшается до -1/8-й от значения непосредственно перед выходом, чтобы обеспечить коррекцию частотного отклика sin (x)/x. Для сохранения площади ИС может использоваться последовательная арифметика. Сброс накопителя до -1/8-й от его предыдущего значения достигается просто путем рециркуляции содержимого 27-разрядного сдвигового регистра с помощью трехразрядной задержки, инвертирования и знакового расширения.

Программируемые источники тока требуются для выработки токовых импульсов в направлении, индицируемом знаком ступеньки, и величиной, заданной размером ступеньки. В противовес обычным требованиям ЦАП и АЦП речевой сигнал полностью представлен последовательностью знаков, и тогда его амплитуда регулируется величиной ступеньки. Поэтому нелинейности или ошибки в преобразовании 12-разрядной величины в ток не вызывают искажений речевого сигнала, но проявляются в изменениях усиления через систему. Поэтому достаточно, если 12-разрядный ЦАП имеет 8-разрядную точность в своем 12-разрядном динамическом диапазоне.

Примерное устройство программируемого источника тока согласно настоящему изобретению показано на фиг. 7. Первый источник 60 тока составлен из токовых зеркал 69, 65 N-типа, которые могут включаться или выключаться последовательным ключевым транзистором 68 для выработки тока I1 уменьшения. Транзистор 67 компенсирует сопротивление ключевого транзистора 68, так что получается точное токовое отражение тока в резисторе 63. Такой же источник тока увеличения образован транзисторами 70, 71, 66 и 64 P-типа. Может быть включен либо ток уменьшения по сигналу "Включение N1", либо ток увеличения по сигналу "Включение P1", либо не включен ни одни из них. Вместо этих источников тока может использоваться "каскадная" схема токового зеркала. Каскадная схема токового зеркала обеспечивает улучшенную точность при наличии изменений напряжения на выходе. Когда используется наиболее эффективное устройство компаратора 30 и интегратора 32 по фиг. 4, источники тока работают при постоянном выходном напряжении и каскадные токовые зеркала не требуются. Если используется устройство компаратора по фиг. 1, то рекомендуются каскадные источники тока.

Источник 6 тока при включении вырабатывает ток I1 уменьшения. Второй источник 61 тока вырабатывает ток I2, а третий источник 62 тока вырабатывает ток I3. Как показано на фиг. 7, выходы источника тока 60, источника 61 и источника тока 62 соединены в общую выходную линию, вследствие чего ток I1, I2 и ток I3 складываются. Отношение токов I1:I2:I3 выбрано равным 1:16:256, что обеспечено соответствующим выбором отношения площадей транзисторов в токовых зеркалах. Чтобы получить точные отношения, общие опорные линии, обозначенные Pref и Nref, подают одни и те же опорные напряжения на все три источника тока.

Шесть управляющих линий (разрешения) на три токовых зеркала управляются тремя цифровыми логическими схемами, как показано на фиг. 8, которые включают три источника тока p- и n-типа переменной длительности импульсов, определенной соответственно тремя 4-разрядными отрезками 12-разярдной величины ступеньки. Разряд знака ступеньки определяет, включен ли источник p-типа или n-типа, тогда как четыре выбранных разряда величины определяют длительность импульса в пределах от 0 до 15 единиц. Четыре младших разряда управляют длительностью импульса источника тока наименьшей силы. Средние четыре разряда управляют длительностью импульса источника тока средней силы, которая в 16 раз больше первой. Старшие разряды управляют длительностью импульса наиболее сильного источника тока, в 256 раз больше первого.

Обычная схема для выработки управляющего сигнала длительности импульса от 4-разрядного управляющего входа показана на фиг. 8. Имеется три таких схемы, по одной для каждого 4-разрядного отрезка. Схема 84 деления на четыре вырабатывает управляющие стробы для логической операции. Цикл начинается, когда 4-разрядный счетчик 81 находится в состоянии a=b=c=d=0 (счет = 0). Это разрешает генерирование тактового импульса фиксации через 5-входовой вентиль 88, который вводит новое 4-разрядное управляющее значение в фиксатор 83. Генерируемый строб является тактовым сигналом сравнения, который посылается на триггер 85. Этот тактовый сигнал регистрирует, обнаружено ли 4-разрядным компаратором 82 равенство 4-разрядного значения счетчика и 4-разрядного значения фиксатора. Если обнаружено, что значение счетчика и значение фиксатора не равны, пока тактовый импульс фиксации еще высокий, то вентиль 86 И вырабатывает выходной сигнал, который устанавливает триггер 87. Если обнаружено, что эти значения равны, выходной сигнал триггера 85 сбрасывает триггер 87. Таким образом, если управляющие разряды равны 0 в начале цикла, когда счетчик 81 также имеет нулевое значение, триггер 87 остается сброшенным, в противном случае происходит его установка.

Далее генератором 84 стробов генерируется строб счета, дающий приращение счетчика 81. Поскольку условие для выполнения функции вентиля 88 И пропадает, никакие дальнейшие тактовые импульсы фиксации не будут генерироваться до тех пор, пока счетчик 81 не вернется к нулевому значению. Следующий строб сравнения регистрируется в триггере 85, равно или нет увеличенное значение счета 4-разрядному значению в фиксаторе 83. Если они равны, триггер 87 сбрасывается. Триггер 87 находится в установленном состоянии до тех пор, пока счетчик 81 не достигнет счета, равного 4 управляющим разрядам, введенным в фиксатор 83 из цифрового слогового фильтра 23, тем самым на выходе генерируется испульс длиной от 0 до 15 тактовых периодов счета. Импульс повторяется каждые 16 тактовых периодов счета. Таким образом, выходной коэффициент заполнения импульсов изменяется от 0 до 15/16 ступенями по 1/16-ой в зависимости от управляющего входа.

Период повторения равен разрядной скорости дельта-модуляции, которая составляет 8000 кГц, где N является коэффициентом избыточной дискретизации (например, 25). Тактовый сигнал счета должен быть по меньшей мере в 16 раз больше разрядной скорости дельта-модуляции, тогда как основной тактовый сигнал в 4 раза выше, т.е. 64•8000 N. В одном выполнении основной тактовый сигнал, равный 65•8000 N, доступен, но он передает лишь блок из 64 от каждых 65 тактовых импульсов на входную линию основного тактового сигнала генератора 84 стробов. Коэффициент заполнения импульсов изменяется тогда от 0 до 60/65 ступенями по 4/65 в зависимости от управляющего разрядного входа.

Следует иметь в виду, что специалистами в цифровой технике может быть создано много других логических конструкций без отхода от объема и духа изобретения, как оно дано в формуле изобретения.

В предпочтительном выполнении кодер может управляться, чтобы работать только в качестве кодера компандированной дельта-модуляции с различными разрядными скоростями. Путем отказа от процесса децимирующей фильтрации и изменения частоты синхронизации на схему дельта-модуляции могут быть получены следующие альтернативные режимы оцифровки:

1) компандированная дельта-модуляция на 8 кбит/с,

2) компандированная дельта-модуляция на 16 кбит/с,

3) компандированная дельта-модуляция на 32 кбит/с,

4) компандированная дельта-модуляция на 200 кбит/с с преобразованием в линейную эквивалентную ИКМ на 8000 отсчетов/с.

Речевой декодер является противоположностью речевого кодера. Декодер принимает поток двоично-кодированных речевых отсчетов, например, на стандартной скорости 8000 отсчетов за секунду и преобразует эти отсчеты в соответствующее аналоговое речевое колебание. В соответствии с альтернативными режимами работы, обеспечиваемыми кодером, декодер настоящего изобретения работает в соответствующих альтернативных режимах.

ЦАП согласно настоящему изобретению показан на фиг. 9. Входные двоично-кодированные речевые отсчеты (в виде ИКМ) на стандартной скорости 8000 отсчетов/с сначала преобразуются с повышением частоты дискретизации в N раз по отношению к желательной скорости дельта-модуляции. Средство для интерполяции 90 использует линейную интерполяцию между последовательными входными отсчетами.

Существует компромисс между сложностью метода интерполяции, используемого для преобразования с увеличением частоты дискретизации, и сложностью средства 95 для фильтрации, необходимого для подавления частотных компонентов, больших, чем половина первоначальной скорости отсчетов 8000 Гц. Более высокий порядок преобразования с повышением частоты дискретизации позволяет смягчить требования к средству 95 для фильтрации, но в выполнении, где выходное речевое колебание предназначено для возбуждения наушников, соответствующие характеристики получаются при использовании линейной интерполяции.

Преобразованные с повышением частоты дискретизации значения сравниваются в средстве для сравнения 91 со значением в средстве 92 для изменения значений цифрового интегратора, что приводит к решению "больше чем" и "меньше чем". Эти значения подаются в средство 93 фильтрации слогов такой же конструкции, как и ранее описанный со ссылкой на фиг. 5. Средство 93 фильтрации слогов вырабатывает величину ступеньки, с которой средство 92 для изменения значений цифрового интегратора будет увеличивать свое значение и уменьшать его в соответствии со знаком операции сравнения. Таким образом, значение цифрового интегратора отслеживает последовательность преобразованных с повышением частоты дискретизации входных значений в последовательности ступенек вверх/вниз.

Такие же величины ступеньки и знак ступеньки подаются также в аналоговое интеграторное средство 94 утечкой. Аналоговое интеграторное средство 94 с утечкой воспроизводит в аналоговом виде то же самое колебание, которое описано в числовом виде последовательностью значений цифрового интегратора. После фильтрации нижних частот в средстве 95 для фильтрации для удаления компонент цифрового шума больших, чем максимальная частота речи 3,4 кГц, аналоговое речевое колебание подается, например, для возбуждения миниатюрного вставляемого в ухо телефона.

В кодере (фиг. 3) по изобретению аналоговый интегратор находится в цепи обратной связи с компаратором, препятствуя дрейфу, тогда как цифровой интегратор 50 (фиг. 6) действует в незамкнутой цепи, требуя использования компонента утечки для предотвращения дрейфа. В декодере средство 92 для изменения значений цифрового интегратора работает в петле и не требует использования утечки. Аналоговое интегральное средство 94 с утечкой работает в незамкнутой цепи, требуя использования утечки для управления дрейфом. Аналоговое интегральное средство 94 с утечкой использует те же конфигурации программируемых источников 60, 61 и 62 тока и широтно-импульсный контроллер, описанные ранее со ссылками на фиг. 7 и 8. Однако для введения утечки интегральный конденсатор 101 обратной связи шунтируется резистором 102, как показано на фиг. 10. Это вызывает уменьшение в усилении на низких частотах относительно интегратора без утечки. Если частота сопряжения PC выбрана ниже минимальной речевой частоты 300 Гц, например 60 Гц, то проблем не возникает.

Как и в кодере, источники тока аналогового интегрального средства в с утечкой 94 могут быть упрощенной конструкции, если они работают с виртуальным заземлением, т.е. с постоянным выходным напряжением.

Предпочтительное выполнение декодера показано на фиг. 10. Источники 103 тока выдают токовые импульсы для инвертирующего входа операционного усилителя 100. Его неинвертирующий вход поддерживается под постоянным напряжением смещения, равным, например, половине напряжения питания. Основная функция интегратора обеспечивается конденсатором 101 обратной связи, тогда как утечка обеспечивается резистором 102 обратной связи. Когда операционный усилитель 100 имеет больший коэффициент усиления разомкнутой схемы, инвертирующий вход никогда не будет значительно отличаться по напряжению от (смещения) неинвертирующего входа, обеспечивая тем самым источники тока нагрузкой с постоянным напряжением.

Если используется альтернативное выполнение непосредственного подключения источников тока к конденсатору, соединенному с землей, изменяющийся заряд на конденсаторе не обеспечивает источникам тока постоянной по напряжению нагрузки. В таком выполнении следует использовать источники тока из различных "каскадных" токовых зеркал для уменьшения зависимости точности их тока от напряжения нагрузки.

На фиг. 11 показано устройство, которое выполняет линейную интерполяцию операции преобразования с повышением частоты дискретизации, интегрирование и сравнение, при уменьшении сложности схемы. Входной поток отсчетов подается сначала на цифровой дифференциатор 110, который вычисляет разность между следующими друг за другом отсчетами. Это дает наклон, необходимый для линейной интерполяции. Линейная интерполяция достигается просто путем интегрирования значения наклона для выдачи отсчетов на желаемой выходной скорости. Это достигается в том же самом цифровом интеграторе 112, который используется для интегрирования величины/знака ступеньки, путем вычитания размера ступеньки со знаком из значения наклона в вычитателе 111 перед интегрированием результата в интеграторе 112. Это основано на принципе линейности: разность между интегралом от A и интегралом от B равна интегралу от разности A и B. К тому же компаратор 91 исключен, потому что больше или меньше интеграл A, чем интеграл B, теперь задается знаковым разрядом интегратора 112. В то время, как только цифровой дифференциатор 110 выдает новое выходное значение 8000 раз в секунду, вычитатель 111 и интегратор 112 работают на скорости с повышенной частотой дискретизации 8000 N раз в секунду, где отношение N избыточной дискретизации обычно равно 25 в предпочтительном выполнении. Каждое значение наклона с цифрового дифференциатора 110 добавляется N раз в цифровом интеграторе 112, обеспечивая в схеме "усиление" в N раз, которое должно учитываться при определении полного выигрыша обработки посредством декодера.

Можно доказать, что цифровой дифференциатор 110 при его аппроксимации простым вычитанием двух последовательных значений с использованием задержки одного отсчета вносит в частотный отклик функцию sin (x)/x в четвертой степени. Это дает ослабление на 5,5 дБ на наивысшей речевой частоте 3,4 кГц, которое компенсируется изменением значения дифференциатора 110 для выполнения операции, записываемой математическим выражением:

D(i) = X(i) - X(i-1) - D(i-1)/4,

где X(i) представляет последовательность входных значений, а D(i) представляет выходные значения. За счет вычитания 1/4 от предыдущего выходного значения при вычитании следующего получается ослабление на 2 дБ на низких частотах, поднимающееся до усиления на 2 дБ на высоких частотах, с общим наклоном вверх на 4 дБ, компенсирующим все, кроме 1,5 дБ, в 5,5 дБ, внесенных функциями sin (x)/x.

Типичным воплощением настоящего изобретения является объединение кодера и декодера в составе большой ИС (БИС) для использования в телефоне, сотовом радиотелефоне или телефоне с батарейным питанием. Другие функции, которые могут быть интегрированы в той же самой БИС, могут включать в себя универсальные АЦП или ЦАП, специализированные АЦП, используемые для оцифровки радиосигналов промежуточной частоты, усилители промежуточной частоты, микрофонные предусилители, оконечные усилители головных телефонов, либо цифровую логику, связанную с клавиатурным набором номера или с памятью номеров электронного телефона.

Интерфейс для цифровых речевых сигналов, передаваемых вовне и принимаемых извне, является четырехпроводным последовательным интерфейсом, содержащим последовательные 16-разрядные слова входной ИКМ речи, последовательные 16-разрядные слова выходной ИКМ речи, последовательный тактовый сигнал частоты следования бит и строб синхронизации слоев, индицирующий положение блока разрядов, образующих каждое двоично-кодированное выходное значение. Этот же интерфейс может использоваться при работе ИС в одном из своих альтернативных режимов дельта-модуляции.

Хотя были описаны и проиллюстрированы конкретные примеры выполнения настоящего изобретения, должно быть ясно, что изобретение не ограничивается ими, т. к. специалисты могут внести в него самые различные изменения. Настоящее изобретение включает в себя любые и всевозможные изменения, которые входят в объем изобретения, раскрытого в описании и охарактеризованного в пунктах формулы изобретения.

Изобретение относится к аналого-цифровым и цифроаналоговым преобразователям для телефонных передающих и коммутационных систем и радиотелефонных систем с импульсно-кодовой модуляцией. Техническим результатом является повышение качества передаваемой по этим системам речи за счет формирования полного цифрового значения в процессе децимации. Для этого устройство для преобразования аналогового сигнала в цифровой сигнал в одном варианте содержит средство для определения знака ступеньки, интеграторные средства, средство для сравнения, средство фильтрации слогов, децимирующее фильтрующее средство, а в другом варианте - компаратор, конденсатор, источник опорного напряжения, источник тока с широтно-импульсной модуляцией. Устройство для преобразования множества двоично-кодированных числовых отсчетов сигнала в аналоговый сигнал содержит в одном варианте средство для сравнения, средство для интерполяции, цифровой интегратор, средство фильтрации слогов, аналоговый интегратор, средство для фильтрации аналогового сигнала. Способ преобразования аналогового сигнала в цифровой сигнал включает операции сравнения аналогового сигнала с проинтегрированным сигналом и определения знака и величины ступеньки для выработки цифрового сигнала. Способ преобразования множества двоично-кодированных числовых отсчетов сигнала в аналоговый сигнал включает операции сравнения интерполированных отсчетов со значениями цифрового интегратора для определения знака ступеньки, выработки величины ступеньки, выработки аналогового сигнала и его фильтрацию. 7 с. и 25 з.п. ф-лы, 11 ил., 2 табл.

| US 3949299 A, 06.04.1976 | |||

| US 4783644 A, 08.11.1988 | |||

| US 4151517 A, 24.04.1979 | |||

| Дельта-кодер | 1984 |

|

SU1197087A1 |

| Цифро-аналоговый преобразователь | 1981 |

|

SU1019622A1 |

| PETER J.A | |||

| et al | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| B: "IEEE Journal of Solid - State Circuts" | |||

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| Поливное приспособление для паровозов | 1922 |

|

SU390A1 |

Авторы

Даты

2000-11-20—Публикация

1994-09-13—Подача