Изобретение относится к радиотехнике и предназначено для преобразования в цифровую форму аналоговых узкополосных сигналов.

Известно устройство аналого-цифрового преобразования узкополосных сигналов, содержащее блок выборки и запоминания аналого-цифровой преобразователь (АЦП), сумматор, регистры, счетчик, логические элементы [1] Данное устройство позволяет формировать цифровые значения отсчетов квадратурных составляющих узкополосного сигнала из отсчетов его мгновенных значений.

Недостатком известного устройства является невозможность достижения большого динамического диапазона аналого-цифрового преобразования. Сверху динамический диапазон ограничивают нелинейные искажения, возникающие в блоке выборки и запоминания и АЦП, а снизу шум квантования и шум апертурной неопределенности моментов стробирования сигнала в блоке выборки и хранения. Дифференциальная нелинейность многоразрядного АЦП принципиально не может быть полностью скомпенсирована при изменении температуры в широких пределах. Снижение уровней шумов требует уменьшения шага квантования и временной нестабильности моментов стробирования, что практически недостижимо из-за неточности изготовления АЦП, фазовой нестабильности опорного генератора и действия дестабилизирующих факторов. Кроме того, многоразрядный АЦП имеет, как правило, низкое быстродействие, которое не позволяет повысить частоту дискретизации и уменьшить уровень помех наложения при дискретизации узкополосного сигнала.

Наиболее близким по технической сущности к заявляемому является устройство аналого-цифрового преобразования, содержащее вычитательинтегратор, выход которого соединен через компаратор с входами цифрового фильтра и одноразрядного цифроаналогового преобразователя (ЦАП), выход которого подключен к выходу вычитателя [2] В данном устройстве путем дельта-сигма-модуляции с высокой частотой дискретизации формируется последовательность бинарных отсчетов, из которых затем с помощью цифрового фильтра нижних частот получается последовательность многоразрядных отсчетов с низкой частотой дискретизации. Устройство обеспечивает большое отношение сигнал/шум квантования для сигналов, спектр которых прилегает к нулевой частоте, благодаря подавлению низкочастотного шума квантования в спектре последовательности одноразрядных отсчетов.

Однако известное устройство не позволяет достичь большого динамического диапазона преобразования при узкополосном входном сигнале, спектр которого сосредоточен вокруг относительно высокой центральной частоты, значительно превышающей ширину спектра. Действительно для полезного сигнала данное устройство эквивалентно фильтру нижних частот, а для шума квантования на выходе компаратора фильтру верхних частот (см.например Агнелло А. 16-разрядные преобразователи ключ к построению высококачественных аудиосредств для персональных компьютеров./Электроника, 1990, N 15, с.61-62). Спектральная плотность шума квантования на выходе компаратора монотонно возрастает с увеличением частоты, поэтому отношение сигнал/шум для узкополосных входных сигналов значительно меньше, чем для низкочастотных. Это отношение снижается с ростом центральной частоты узкополосного сигнала. В результате динамический диапазон преобразования узкополосных сигналов оказывается недостаточным.

Цель изобретения расширение динамического диапазона аналого-цифрового преобразования узкополосных сигналов.

Цель достигается тем, что в устройство аналого-цифрового преобразования, содержащее первый вычитатель, первый вход которого является входной шиной, первый интегратор, выход которого соединен с первым входом компаратора, второй вход которого является шиной нулевого потенциала, а выход соединен с информационным входом цифрового фильтра и через ЦАП с вторым входом первого вычитателя, причем выход цифрового фильтра является выходной шиной, введены второй вычитатель, второй интегратор и блок опорных частот, а компаратор выполнен стробируемым, при этом первый вход второго вычитателя соединен с выходом первого вычитателя, а выход с входом первого интегратора, выход которого подключен через второй интегратор к второму входу второго вычитателя, первый выход блока опорных частот соединен с входом стробирования компаратора и с первым входом синхронизации цифрового фильтра, а второй его выход с вторым входом синхронизации цифрового фильтра. Цифровой фильтр выполнен на одноразрядном регистре сдвига, первом, втором и третьем регистрах памяти, постоянном запоминающем блоке, сумматоре комплексных чисел, многоразрядном регистре сдвига, первом и втором вычитающих счетчиках, ключевом элементе и формирователе импульсов, при этом информационным входом цифрового фильтра является информационный вход одноразрядного регистра сдвига, выход которого через последовательно включенные первый регистр памяти, постоянный запоминающий блок, сумматор комплексных чисел, многоразрядный регистр сдвига и второй регистр памяти соединен с другим входом сумматора комплексных чисел, выход которого подключен к входу третьего регистра памяти, выход которого является выходом цифрового фильтра, первым входом синхронизации цифрового фильтра является вход синхронизации одноразрядного регистра сдвига, а вторым входом информационный вход ключевого элемента и счетный вход первого вычитающего счетчика, выход заема которого соединен с входом синхронизации первого регистра памяти и счетным входом второго вычитающего счетчика, выходы разрядов первого и второго вычитающих счетчиков подключены к соответствующим старшим разрядам адресных входов постоянного запоминающего блока, выход заема второго вычитающего счетчика соединен с управляющим входом ключевого элемента и через формирователь импульсов с входом синхронизации третьего регистра памяти и с входом сброса второго регистра памяти, вход синхронизации которого объединен с входом синхронизации многоразрядного регистра сдвига и подключен к выходу ключевого элемента.

Такая структура устройства аналого-цифрового преобразования позволяет значительно расширить динамический диапазон преобразования узкополосных сигналов благодаря подавлению шумов квантования и апертурной неопределенности в полосе частот сигнала при формировании последовательности бинарных отсчетов с высокой частотой дискретизации. Подавление шумов обеспечивается аналоговым резонатором, образованным вторым интегратором и вторым вычитателем совместно с первым интегратором. Сосредоточенные за пределами полосы частот сигнала шумы и другие помехи в спектре последовательности бинарных отсчетов устраняются комплексным полосовым цифровым фильтром, на выходе которого с пониженной частотой дискретизации формируются многоразрядные отсчеты квадратурных составляющих преобразуемого сигнала. Дополнительное увеличение динамического диапазона достигается благодаря отсутствию операций умножений в цифровом фильтре, что позволяет повысить его порядок и обеспечить высокие степень подавления шумов и точность формирования квадратурных составляющих.

Совокупность узлов и связей, введенных в устройство, не было обнаружена в известных технических решениях в ходе исследования проведенного по источникам патентной и другой научно-технической информации.

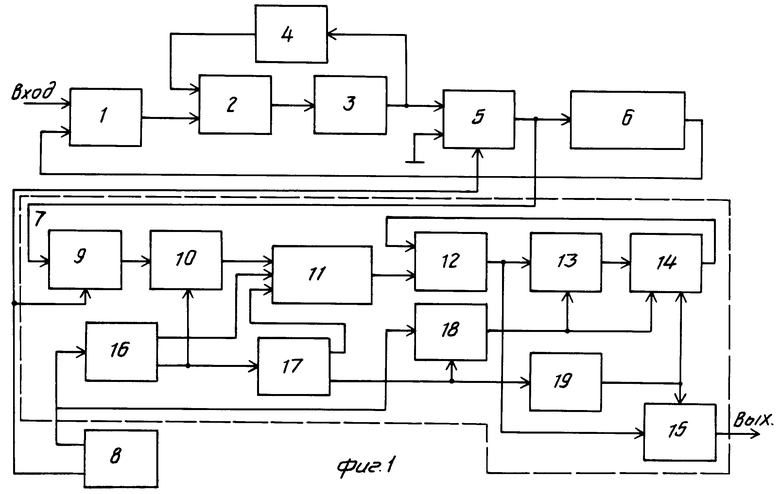

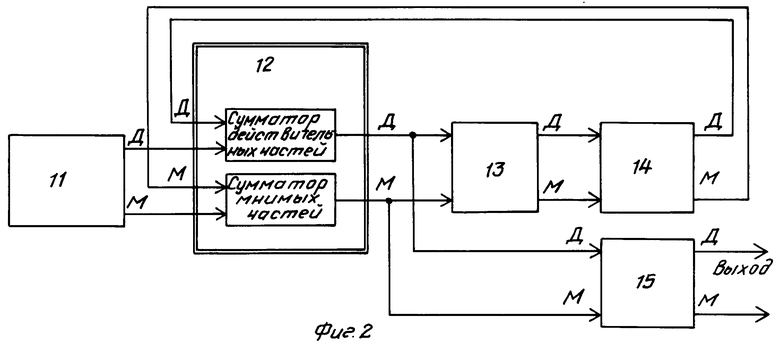

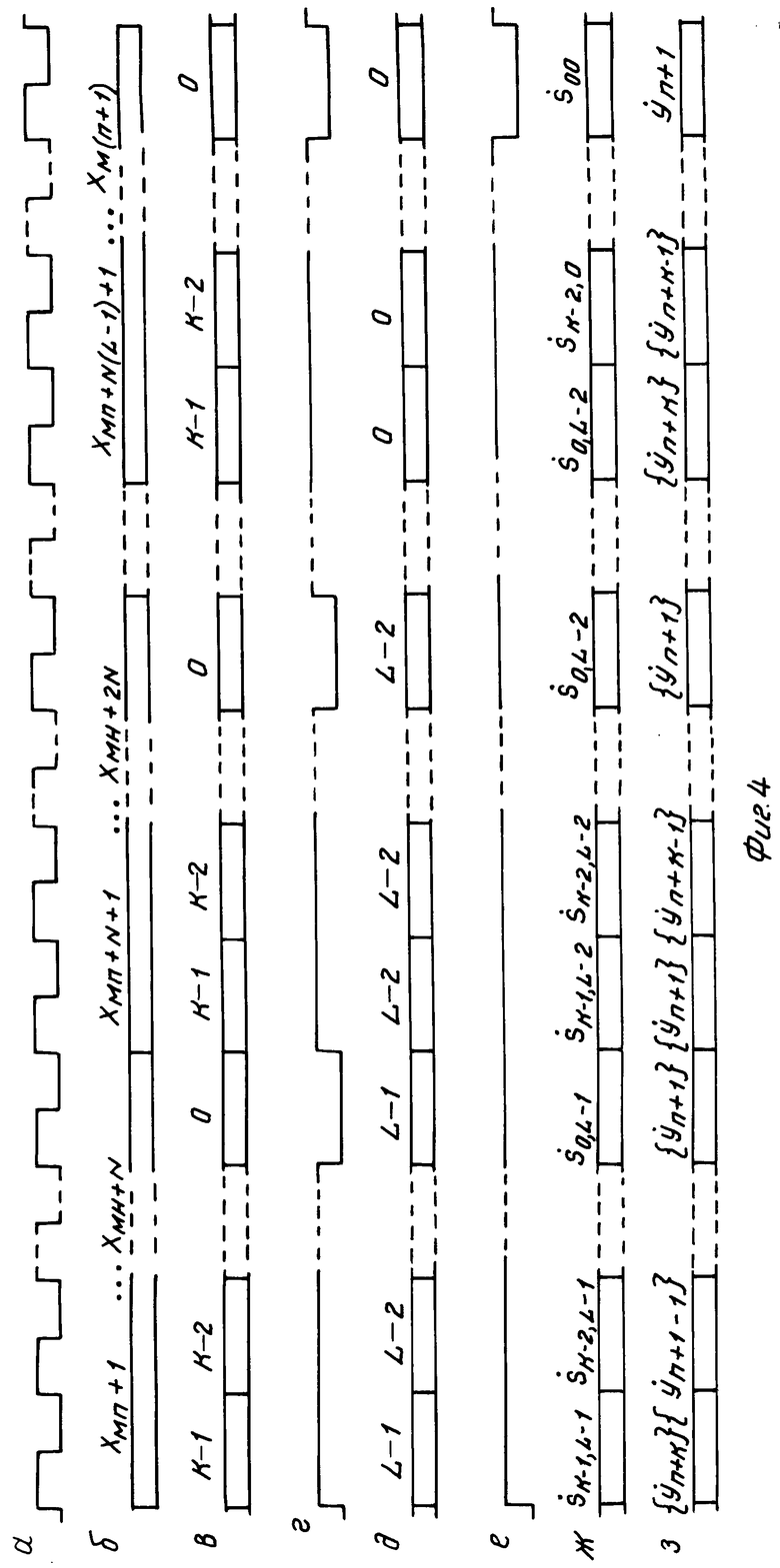

На фиг. 1 приведена структурная схема устройства аналого-цифрового преобразования; на фиг.2 схема включения сумматора комплексных чисел; на фиг.3 показаны спектральные диаграммы основных сигналов; на фиг.4 временные диаграммы напряжений в устройстве.

Устройство содержит первый вычитатель 1, первый вход которого (вход уменьшаемого) является входной шиной, а выход соединен с первым входом (входом уменьшаемого) второго вычитателя 2, выход которого через первый и второй интеграторы 3 и 4 подключен к второму входу (входу вычитаемого) второго вычитателя 2. Выход первого интегратора 3 соединен через стробируемый компаратор 5, второй вход которого является шиной нулевого потенциала, с входом одноразрядного ЦАП 6 и с информационным входом цифрового фильтра 7, выход которого является выходной шиной. Выход ЦАП 6 подключен к второму входу (входу вычитаемого первого вычитателя 1. Первый выход блока 8 опорных частот соединен c входом стробирования компаратора 5 и с первым входом синхронизации цифрового фильтра 7, а второй его выход с вторым входом синхронизации цифрового фильтра. Информационным входом цифрового фильтра 7 является информационный вход одноразрядного регистра 9 сдвига, параллельный выход которого через первый регистр 10 памяти соединен с входом младших адресных разрядов постоянного запоминающего блока 11, выход которого подключен к первому входу сумматора 12 комплексных чисел. Выход сумматора 12 соединен через последовательно включенные многоразрядный регистр 13 сдвига и второй регистр 14 памяти с вторым входом сумматора 12, а также подключен к входу третьего регистра 15 памяти, выход которого является выходом цифрового фильтра 7. Сумматор 12 комплексных чисел (фиг.2) состоит из сумматоров действительных (д) и мнимых (м) частей слагаемых. Информационные шины между блоком 11, сумматором 12, регистрами 13 сдвига и 14, 15 памяти и выходная шина устройства состоят из двух частей, предназначенных для передачи соответственно действительных и мнимых компонентов обрабатываемых чисел. Первым входом синхронизации цифрового фильтра 7 является вход синхронизации одноразрядного регистра 9 сдвига, а вторым входом счетный вход первого вычитающего счетчика 16, выход заема которого соединен с входом синхронизации первого регистра 10 памяти и счетным входом второго вычитающего счетчика 17, и информационный вход ключевого элемента 18, второй вход которого объединен с входом формирователя 19 импульсов и подключен к выходу заема второго вычитающего счетчика 17. Выходы разрядов первого и второго вычитающих счетчиков 15 и 17 подключены к соответствующим старшим разрядам адресных входов постоянного запоминающего блока 11. Выход ключевого элемента 18 подключен к входам синхронизации многоразрядного регистра 13 сдвига и второго регистра 14 памяти, а выход формирователя 19 импульсов к входу сброса второго регистра 14 памяти и к входу синхронизации третьего регистра 15 памяти.

Вычитатели 1 и 2 и интеграторы 3 и 4 могут быть выполнены, например, по схемам, приведенным на рис.1.17, с.43 и рис.3.4, с.94 в кн. Гутников В.С. Интегральная электроника в измерительных устройствах. Л. Энергоатомиздат, 1988. В качестве компаратора 5 со стробированием можно использовать, например, интегральные микросхемы типа К597СА1 или К597СА2. Блок 8 опорных частот состоит из опорного генератора и двух делителей частоты, формирующих последовательности импульсов с необходимыми частотами. Постоянный запоминающий блок 11 может быть выполнен на микросхемах постоянных запоминающих устройств, например, типов 556РТ6, 556РТ7, 573РФ4, 573РФ6А и др. Многоразрядный регистр 13 сдвига состоит из включенных параллельно одноразрядных регистров сдвига с объединенными входами синхронизации. В качестве ключевого элемента 18 можно использовать элемент И. Формирователь 19 импульсов может быть выполнен по схемам, приведенным на рис.5.10, с.159 указанной выше книги. В качестве остальных блоков можно использовать цифровые и аналоговые микросхемы.

Устройство аналого-цифрового преобразования работает следующим образом.

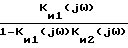

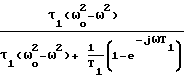

Узкополосный сигнал поступает через первый вычитатель 1 на вход второго вычитателя 2 (на фиг.3а схематически показан спектр сигнала). Вычитатель 2, первый и второй интеграторы 3 и 4 образуют аналоговый резонатор, передаточная функция которого от входа вычитателя 2 до выхода интегратора 3 определяется формулой

Kp(jω)

где j

где j  ; Kи1(jω)

; Kи1(jω)  передаточная функция интегратора 3;

передаточная функция интегратора 3;

Kи2(jω)  общая передаточная функция вычитателя 2 и интегратора 4;

общая передаточная функция вычитателя 2 и интегратора 4;

ωp= 1/  резонансная частота; τ1 и τ2 постоянные времени интегрирования интеграторов 3 и 4, которые должны быть выбраны такими, чтобы ωp ωo где ωo 2 π fо центральная частота узкополосного сигнала.

резонансная частота; τ1 и τ2 постоянные времени интегрирования интеграторов 3 и 4, которые должны быть выбраны такими, чтобы ωp ωo где ωo 2 π fо центральная частота узкополосного сигнала.

Напряжение на выходе интегратора 3 дискретизируется по времени с входной частотой дискретизации fд1 и квантуется по уровню компаратором 5, который стробируется тактовыми импульсами, поступающими с частотой fд1 с первого выхода блока 8 опорных частот. На выходе компаратора 5 формируется последовательность бинарных отсчетов хm, равных единице при положительном напряжении на первом входе компаратора 5 в момент стробирования и минус единица при отрицательном, где m0,1.2, Положительному отсчету соответствует логическая "1" на выходе компаратора 5, а отрицательному логический "0".

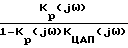

Выходное напряжение компаратора 5 с помощью одноразрядного ЦАП 6 преобразуется в биполярное напряжение обратной связи, которое подается на второй вход вычитателя 1. Полный размах этого напряжения определяет амплитудный диапазон аналого-цифрового преобразования. Благодаря наличию отрицательной обратной связи между выходом компаратора 5 и входом вычитателя 1 через ЦАП 6 передаточная функция части устройства от первого входа вычитателя 1 до выхода компаратора 5 для сигнала определяется формулой

Kc(jω)

где KЦАП(jω)

где KЦАП(jω)

1-e

1-e общая передаточная функция ЦАП 6 и вычитателя 1; Т1 1/fд1 входной период дискретизации.

общая передаточная функция ЦАП 6 и вычитателя 1; Т1 1/fд1 входной период дискретизации.

Так как входная частота дискретизации в устройстве выбирается значительно (в 5 и более раз) выше центральной частоты сигнала, передаточная функция для сигнала близка к передаточной функции полосового фильтра второго порядка (фиг.3б).

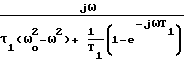

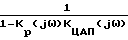

Бинарное квантование сигнала компаратором 5 приводит к появлению шума квантования, а дрожание моментов стробирования компаратора 5 шума апертурной неопределенности. Оба шума добавляются к полезному сигналу. Если в устройстве отсутствует отрицательная обратная связь, то общий шум на выходе компаратора 5 имеет спектральную плотность, практически равномерную на всех частотах. Однако благодаря обратной связи форма спектральной плотности шума повторяет форму передаточной функции устройства для шума, определяемой выражением

Kш(jω)

Данная передаточная функция (фиг.3в) соответствует передаточной функции режекторного фильтра второго порядка, что обеспечивает подавление шума в окрестности центральной частоты сигнала.

Таким образом, спектральная плотность последовательности бинарных отсчетов на выходе компаратора 5 (фиг.3г) состоит из двух компонентов: спектра полезного сигнала, прошедшего через полосовой фильтр, и спектра шумов квантования и апертурной неопределенности, прошедших через режекторный фильтр. Выбирая достаточно большое отношение входной частоты дискретизации к ширине спектра сигнала ΔF, можно обеспечить практически сколь угодно малую мощность шумов в полосе частот сигнала.

Однако за пределами полосы частот сигнала мощность шумов в спектре последовательности бинарных отсчетов на выходе компаратора 5 быстро возрастает. Подавление внеполосных шумов обеспечивает цифровой фильтр 7, на вход которого подается последовательность бинарных отсчетов. Комплексный полосовой цифровой фильтр 7 имеет комплексные коэффициенты и несимметричную относительно нулевой частоты амплитудно-частотную характеристику, которая схематически показана на фиг. 3д. Полоса пропускания цифрового фильтра 7, заключающаяся в пределах от fo 0,5 ΔF до fо + 0,5 ΔF, совпадает с полосой частот полезного сигнала. На остальных частотах цифровой фильтр 7 обеспечивает максимально возможное затухание. Для расчета передаточной функции такого фильтра необходимо синтезировать передаточную функцию действительного цифрового фильтра нижних частот такого же порядка с полосой пропускания от -0,5 ΔF до 0,5 ΔF, а затем повернуть координаты нулей и полюсов передаточной функции на Z-плоскости, умножив их на фазовый множитель ljωo T1.

В цифровом фильтре 7 подавляются внеполосные шумы, а также зеркальное отображение спектра полезного сигнала, сосредоточенное в полосе частот от -fo 0,5 ΔF до -fo + 0,5 ΔF, и производится снижение входной частоты дискретизации в М раз (децимация отсчетов). На выходе цифрового фильтра 7 формируется последовательность многоразрядных отсчетов с выходной частотой дискретизации fд2 fд1/М, спектр которых (фиг.3е) состоит из прямого отображения спектра полезного сигнала и остатков спектральных составляющих шумов. Значения входной частоты дискретизации и коэффициента децимации М выбираются такими, чтобы центральная частота узкополосного сигнала была кратна выходной частоте дискретизации. При этом прямое отображение спектра сигнала на выходе цифрового фильтра 7 после децимации имеет нулевую центральную частоту (фиг. 3е) и полностью совпадает со спектром комплексной огибающей входного узкополосного сигнала. Так как спектральные и временные характеристики сигнала взаимно-однозначно определяют друг друга, действительная часть каждого комплексного отсчета на выходе цифрового фильтра 7 является отсчетом действительной части комплексной огибающей сигнала (косинусной квадратурной составляющей), а мнимая мнимой части комплексной огибающей (синусной квадратурной составляющей). С выхода цифрового фильтра 7 многоразрядные отсчеты квадратурных составляющих поступают на выходную шину устройства.

Цифровой фильтр 7 является нерекурсивным. Каждый комплексный отсчет уn на его выходе вычисляется путем попарного перемножения последовательностей входных отсчетов и коэффициентов фильтра и сложения полученных произведений по формуле =

=  XMn-i (1) где n 0,1,2, Nф К.М длина импульсной характеристики фильтра, выбираемая в целое число раз К большей коэффициента децимации;

XMn-i (1) где n 0,1,2, Nф К.М длина импульсной характеристики фильтра, выбираемая в целое число раз К большей коэффициента децимации;  комплексные коэффициенты фильтра. Для вычисления следующего выходного отсчета производятся сдвиг последовательности коэффициентов относительно последовательности входных отсчетов на М позиций и повторение указанных операций.

комплексные коэффициенты фильтра. Для вычисления следующего выходного отсчета производятся сдвиг последовательности коэффициентов относительно последовательности входных отсчетов на М позиций и повторение указанных операций.

В предлагаемом устройстве при вычислениях используется комбинация табличных и арифметических операций в соответствии со следующей из (1) формулой: =

=

(2) где

(2) где =

=

XMn-i (3) комплексные частичные суммы произведений N бинарных входных отсчетов и N комплексных коэффициентов фильтра 7, причем N целое число, выбираемое в целое число раз L меньшим коэффициента децимации М.

XMn-i (3) комплексные частичные суммы произведений N бинарных входных отсчетов и N комплексных коэффициентов фильтра 7, причем N целое число, выбираемое в целое число раз L меньшим коэффициента децимации М.

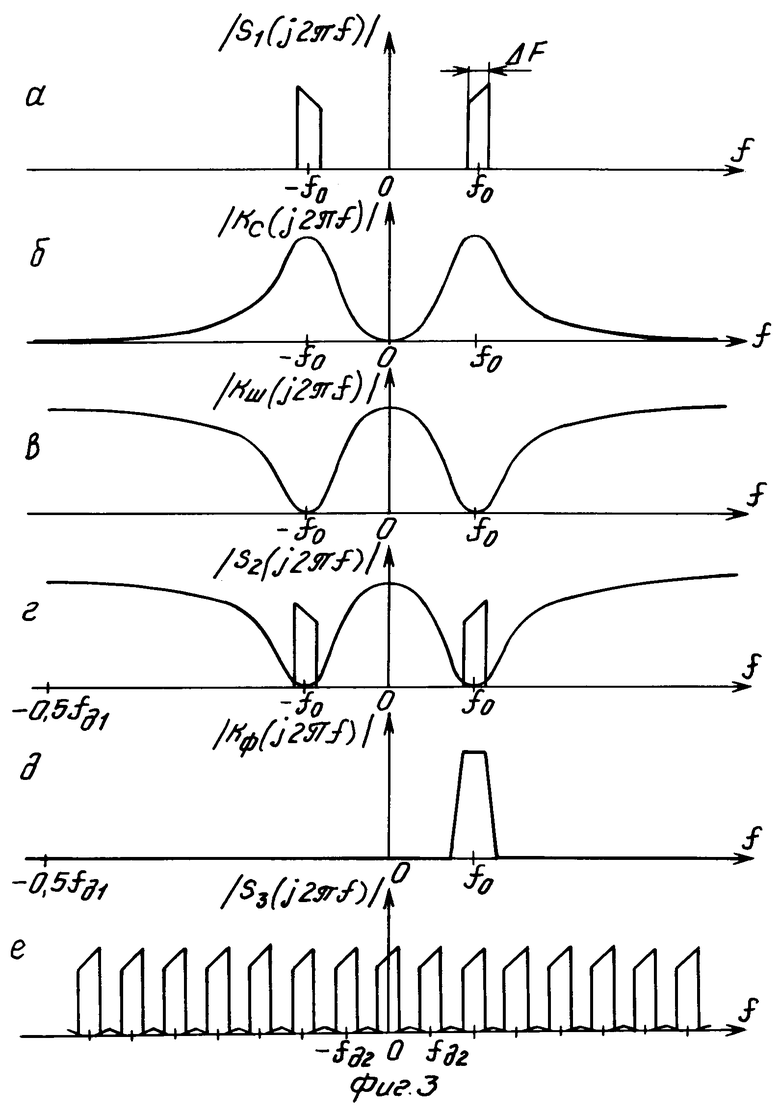

Последовательность входных бинарных отсчетов с помощью регистра 9 сдвига и регистра 10 памяти разбивается на группы по N отсчетов. В регистре 9 бинарные отсчеты продвигаются с периодом Т1, задаваемым тактовыми импульсами на входе синхронизации регистра 9, а в регистр 10 каждая очередная группа отсчетов (фиг.4б) переписывается из регистра 9 через интервалы времени NT1, задаваемые тактовыми импульсами (фиг.4г) на входе синхронизации регистра 10.

Затем по таблице, записанной в постоянном запоминающем блоке 11, определяются частичные комплексные суммы  произведений группы отсчетов и группы из N соседних коэффициентов фильтра. Младшие разряды входов постоянного запоминающего блока 11 в количестве N подключены к выходам регистра 10 памяти, часть старших разрядов в количестве log2K к выходам вычитающего счетчика 16, а остальные старшие разряды в количестве log2L к выходам вычитающего счетчика 17. В ячейках блока 11, общее число которых равно 2NKL, записана (путем предварительного программирования) таблица комплексных частичных сумм, вычисленных по формуле (3) при всех возможных комбинациях N входных бинарных отсчетов и индексов k и l. При записи в каждую конкретную ячейку комбинация входных бинарных отсчетов берется равной двоичному коду в N младших разрядах адреса данной ячейки, а индексы k и l двоичным кодам в старших разрядах адреса, подключаемых соответственно к выходам счетчиков 16 и 17. В одну половину информационных разрядов ячейки записывается действительная, а в другую мнимая части комплексной частичной суммы. При работе устройства двоичный код в младших входных разрядах блока 11, поступающий с выхода регистра 10, соответствует конкретной группе входных отсчетов, а код в старших разрядах, поступающий с выходов счетчиков 16 и 17, набору коэффициентов для данной частичной суммы. Счетчики 16 и 17 являются вычитающими и имеют модули счета К и L. За время хранения одной группы отсчетов в регистре 10 (фиг.4б) число k на выходе счетчика 16 уменьшается с К-1 до нуля с шагом единица (фиг.4в). В конце этого интервала времени по импульсу с выхода заема счетчика 16 (фиг. 4г) уменьшается на единицу и число l в счетчике 17, диапазон значений которого от L-1 до нуля (фиг.4д). Таким образом, за период счета счетчика 17, равный выходному периоду дискретизации 1/fд2, происходит перебор всех возможных комбинаций индексов k и l, т.е. всех групп коэффициентов фильтра.

произведений группы отсчетов и группы из N соседних коэффициентов фильтра. Младшие разряды входов постоянного запоминающего блока 11 в количестве N подключены к выходам регистра 10 памяти, часть старших разрядов в количестве log2K к выходам вычитающего счетчика 16, а остальные старшие разряды в количестве log2L к выходам вычитающего счетчика 17. В ячейках блока 11, общее число которых равно 2NKL, записана (путем предварительного программирования) таблица комплексных частичных сумм, вычисленных по формуле (3) при всех возможных комбинациях N входных бинарных отсчетов и индексов k и l. При записи в каждую конкретную ячейку комбинация входных бинарных отсчетов берется равной двоичному коду в N младших разрядах адреса данной ячейки, а индексы k и l двоичным кодам в старших разрядах адреса, подключаемых соответственно к выходам счетчиков 16 и 17. В одну половину информационных разрядов ячейки записывается действительная, а в другую мнимая части комплексной частичной суммы. При работе устройства двоичный код в младших входных разрядах блока 11, поступающий с выхода регистра 10, соответствует конкретной группе входных отсчетов, а код в старших разрядах, поступающий с выходов счетчиков 16 и 17, набору коэффициентов для данной частичной суммы. Счетчики 16 и 17 являются вычитающими и имеют модули счета К и L. За время хранения одной группы отсчетов в регистре 10 (фиг.4б) число k на выходе счетчика 16 уменьшается с К-1 до нуля с шагом единица (фиг.4в). В конце этого интервала времени по импульсу с выхода заема счетчика 16 (фиг. 4г) уменьшается на единицу и число l в счетчике 17, диапазон значений которого от L-1 до нуля (фиг.4д). Таким образом, за период счета счетчика 17, равный выходному периоду дискретизации 1/fд2, происходит перебор всех возможных комбинаций индексов k и l, т.е. всех групп коэффициентов фильтра.

Каждая группа входных отсчетов используется с несколькими группами коэффициентов при вычислении К выходных отсчетов. Вычисление выходных отсчетов происходит параллельно путем накопления соответствующих им промежуточных неполных) сумм произведений, которые хранятся в регистре 13 сдвига, состоящем из К-1 многоразрядных ячеек, и регистре 14 памяти. Продвижение информации в регистрах 13 и 14 происходит при поступлении на их входы синхронизации через замкнутый ключевой элемент 18 тактовых импульсов с периодом NT1/K (фиг.4а). При накоплении к каждой из К промежуточных сумм, последовательно поступающих с выхода регистра 14 (на фиг.4з в фигурных скобках показаны обозначения отсчетов, которым соответствует присутствующая в данный момент времени на выходе регистра 14 промежуточная сумма), в сумматоре 12 прибавляется частичная сумма (фиг. 4ж) с выхода постоянного запоминающего блока 11. За время хранения очередной группы входных отсчетов в регистре 10 памяти на выходе блока 11 формируется К частичных сумм для разных групп коэффициентов (фиг. 4ж), которые поочередно суммируются с промежуточными суммами, соответствующими им согласно выражению (2). Для каждой группы отсчетов последовательно используются группы коэффициентов со смещением на М, 2М, 3М и т.д. позиций, а для следующей группы со смещением относительно предыдущей на N позиций. Количество частичных сумм, входящих в ту или иную промежуточную сумму, т.е. степень приближения ее к конечному результату, тем больше, чем раньше началось формирование данной промежуточной суммы.

В конце каждого выходного периода дискретизации завершается накопление наиболее ранней промежуточной суммы (она является результатом сложения KL частичных сумм и равна выходному отсчету). При этом на выходе заема счетчика 17 появляется импульс (фиг.4е), который запирает ключевой элемент 18, запрещая тем самым прохождение на входы синхронизации регистров 13 и 14 последнего в данном периоде тактового импульса. Число на выходе регистра 14 в этот момент времени (согласно выражению (2)) равно выходному отсчету. По окончании импульса на выходе заема счетчика 17 формирователь 19 импульсов вырабатывает короткий импульс, которым выходной отсчет записывается в третий регистр 15 памяти и обнуляется регистр 14 памяти. Благодаря обнулению регистра 14 в начале следующего выходного периода дискретизации начинает формироваться промежуточная сумма, соответствующая новому выходному отсчету. Кроме того, в начале нового периода в ячейках регистра 13 сдвига записаны К-1 промежуточных сумм, формирование которых началось в предыдущие периоды, в очередности, которая совпадает с порядком следования соответствующих этим суммам выходным отсчетам.

Требуемые для работы устройства тактовые частоты 1/Т1 и К/NТ1вырабатываются соответственно на первом и втором выходах блока 8 опорных частот путем деления опорной частоты К/Т1 на К и на N.

Таким образом, предлагаемое устройство аналого-цифрового преобразования позволяет значительно расширить динамический диапазон преобразования узкополосных сигналов благодаря подавлению внутриполосных шумов квантования и апертурной неопределенности аналоговой частью устройства и подавлению внеполосных шумов и других помех путем цифровой фильтрации с одновременным формированием многоразрядных отсчетов квадратурных составляющих сигнала. Кроме того, благодаря отсутствию операций умножения в цифровом фильтре можно повысить его порядок и обеспечить высокие степень подавления шумов и точность формирования квадратурных составляющих, Исключая свойственную всем многоразрядным квантователям дифференциальную нелинейность и снижая помехи наложения, структура устройства в отличие от известных аналогов с использованием дельта-сигма-модуляции одновременно позволяет избежать снижения динамического диапазона при увеличении центральной частоты сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ УЗКОПОЛОСНЫХ СИГНАЛОВ | 1992 |

|

RU2036558C1 |

| Цифровой нерекурсивный фильтр | 1986 |

|

SU1332519A1 |

| Устройство аналого-цифрового преобразования узкополосных сигналов | 1986 |

|

SU1336234A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| ЦИФРОВОЙ КОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР ЧЕТЫРЕХПОЗИЦИОННОГО СИГНАЛА С ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2017 |

|

RU2656577C1 |

| Цифровой согласованный фильтр | 1988 |

|

SU1653174A1 |

| Цифровое устройство измерения частоты | 1988 |

|

SU1677653A1 |

| Цифровой измеритель отношения сигнал/шум сигналов с фазовой манипуляцией | 2024 |

|

RU2827313C1 |

Изобретение относится к радиотехнике и предназначено для преобразования в цифровую форму аналоговых узкополосных сигналов. Устройство позволяет расширить динамический диапазон преобразования и состоит из двух вычитателей, двух интеграторов, компаратора, одноразрядного цифроаналогового преобразователя, блока опорных частот и цифрового фильтра, который содержит одноразрядный и многоразрядный регистры сдвига, три регистра памяти, постоянный запоминающий блок, сумматор комплексных чисел, два вычитающих счетчика, ключевой элемент и формирователь импульсов. В устройстве с высокой частотой дискретизации формируется последовательность бинарных отсчетов, представляющих собой сумму отсчетов полезного сигнала и шумов квантования и апертурной неопределенности, причем шумы подавлены в полосе частот сигнала. В цифровом фильтре с комплексными коэффициентами на низкой частоте дискретизации вычисляются многоразрядные отсчеты квадратурных составляющих сигнала путем накопления комплексных частичных сумм произведений групп бинарных отсчетов и групп комплексных коэффициентов. В ходе фильтрации устраняются внеполосные шумы и помехи и подавляется зеркальное отображение спектра сигнала. 1 з.п. ф-лы, 4 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Электроника, т.61, N 1, 1988, с.69, рис.3. | |||

Авторы

Даты

1995-08-20—Публикация

1992-06-08—Подача