Настоящее изобретение относится к схемам определения синхронизации и защиты и способу, а более точно к схемам определения синхронизации и защиты и способу для точного определения данных в раннеустановленном положении в цифровых VCR путем точного определения синхронизации и генерирования псевдосинхронизирующего сигнала управления, когда найдена ошибка в синхронизации.

Был разработан стандартный SD видеомагнитофон (VCR), в котором стандартные NTSC и PAL сигналы записываются/воспроизводятся с использованием пленки с цифровой видеозаписью, и был установлен формат записи SD сигнала. Под разработкой понимается разработка усовершенствованного телевидения (ATV) и цифрового видео вещания (DVB)VCR для ATV и DVB сигналов записи/воспроизведения с использованием пленки с цифровой видеозаписью. В ATV-VCR и в DVB-VCR сигналы записаны на пленке с цифровой видеозаписью в SD формате записи.

Дорожка и структура сектора данных пленки с цифровой видеозаписью SD формата, используемой в цифровом видеомагнитофоне, будут описаны ниже.

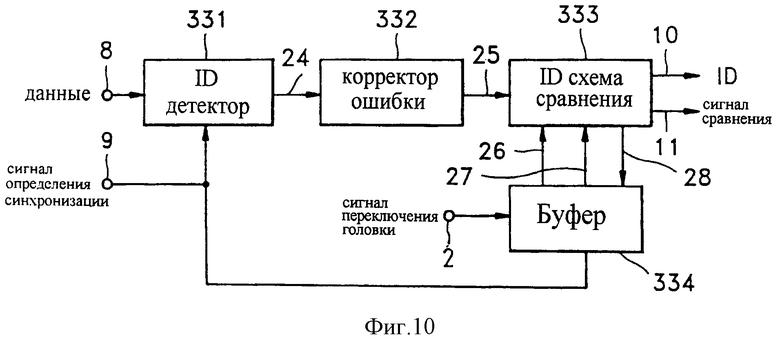

На Фиг. 1 показан вариант выполнения секторов на винтовой дорожке пленки с цифровой видеозаписью, имеющей SD формат записи.

На дорожке сектор информации дорожки ITI и ввода, аудио сектор, видео сектор и сектор подкода выполнены надлежащим образом от начала дорожки, где головка начинает сканирование. Расположение данных на дорожке следующее.

ITI сектор состоит из предварительной области ввода ITI с 1,400 битами (PRE1), 1,830-битовой области блока начала синхронизации (SSA), 90-битовой области информации дорожки (TIА) и 280-битовой ITI завершающей области (POS1).

Аудио сектор состоит из предварительной аудио области ввода (PRE2), имеющей 400-битовое обновление данных и 2 блока предварительной синхронизации, области аудио данных (AUDIO), включающей 14 блоков синхронизации данных, и 550-битовой завершающей аудио области (POS2), имеющей блок постсинхронизации и 500-битовую область защиты.

Видео сектор состоит из предварительной видео области ввода (PRE3), имеющей 400-битовое обновление данных и 2 блока предварительной синхронизации, области видео данных (VIDEO), имеющей 149 блоков синхронизации данных, и 975-битовой завершающей видео области (POS3), имеющей блок постсинхронизации и 925-битовую область защиты.

Сектор подкода состоит из 1,200-битовой предварительной области подкода (PRE4), 1,200-битовой области подкода (SUBCODE), и завершающей области подкода (POS4), имеющей 1,200 битов для системы с 625 строками/50 полями, но 1,325 битов для системы с 525 строками/60 полями, 1,250-битовая область предела перезаписи следует после POS4 сектора подкода.

Блок синхронизации данных для аудио и видео секторов имеет 750 битов. Каждый из промежутков для редакции G1, G2 и G3 между секторами G1, G2 и G3 имеет 625 битов, 700 битов и 1,500 битов соответственно.

Структура видео сектора дорожки, показанной на Фиг. 1, будет описана более подробно.

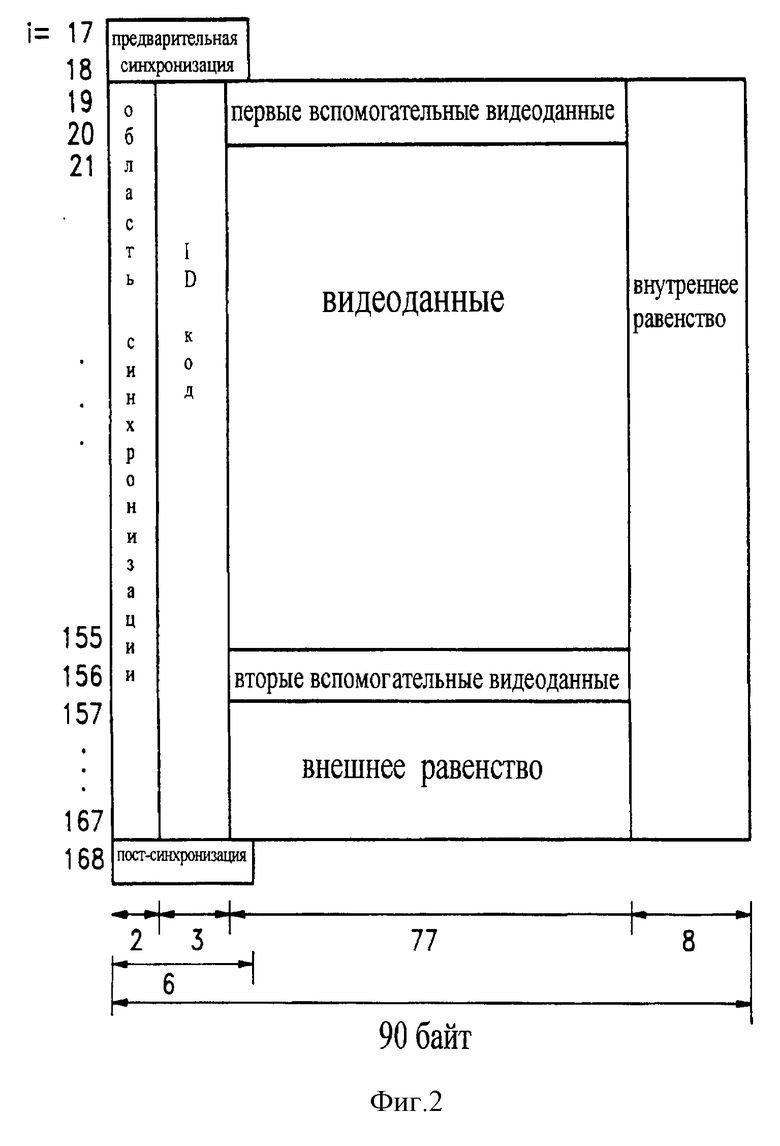

На Фиг. 2 изображены блок предварительной синхронизации, область видеоданных и блок постсинхронизации видеосектора.

Согласно Фиг. 2 область видеоданных состоит из блоков синхронизации 19 и 20 для первых вспомогательных видеоданных, блоков синхронизации 21-155 для видеоданных, блока синхронизации 156 для вторых вспомогательных видеоданных и блоков синхронизации 157-167 для внешнего равенства. Каждый блок синхронизации имеет 2-байтовую синхронизацию, 3-байтовый код идентификации (ID), 77-байтовые данные и 8-байтовое внутреннее равенство.

Блоки синхронизации 17 и 18 являются блоками предварительной синхронизации области PRE3 и блок синхронизации 168 является блоком постсинхронизации области POS3.

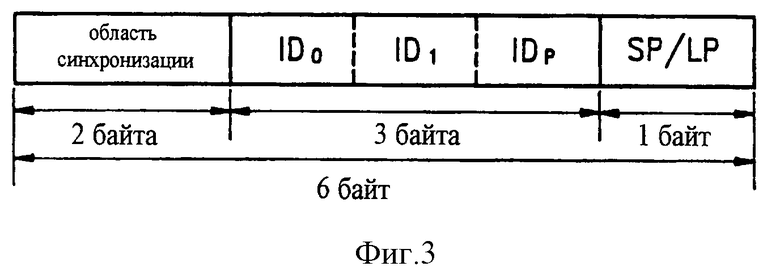

На Фиг. 3 изображена структура блока предварительной синхронизации, показанного на Фиг. 2.

Согласно Фиг. 3 каждый из двух блоков предварительной синхронизации, показанных на Фиг. 2, имеет 2-байтовую синхронизацию, 3-байтовый ID код, 1-байтовый SP/LP код, SP/LP =FFh присвоены SP режиму и SP/LP = OOh присвоены LP режиму. ID0 кода ID (ID0, ID1 и IDp) показывают информацию пары дорожек и информацию применения. ID1 показывает номер блока синхронизации, и IDp является 1-байтовым ID равенством исправления ошибки для ID0 и ID1.

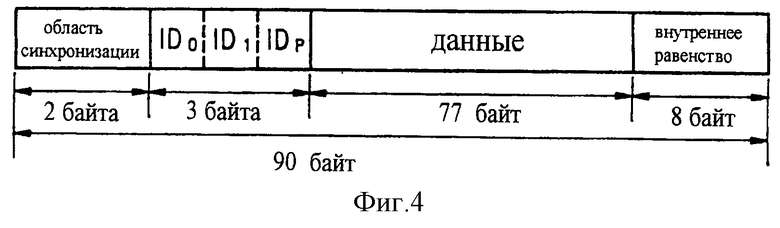

На Фиг. 4 изображена структура блока синхронизации данных, показанного на Фиг. 2.

Согласно Фиг. 4 блок синхронизации данных состоит из 2-байтовой синхронизации, 3-байтового ID кода, 77-байтовых данных и 8-байтового внутреннего равенства исправления внутрикодовой ошибки. ID0 3-байтового ID кода (ID0, ID1 и IDp) показывает порядковый номер и информацию пары дорожек для блоков синхронизации 19-156 и информацию пары дорожек и информацию применения для блоков синхронизации 157-168, ID1 показывает номер блока синхронизации, и IDp является ID равенством исправления ошибки для ID0 и ID1.

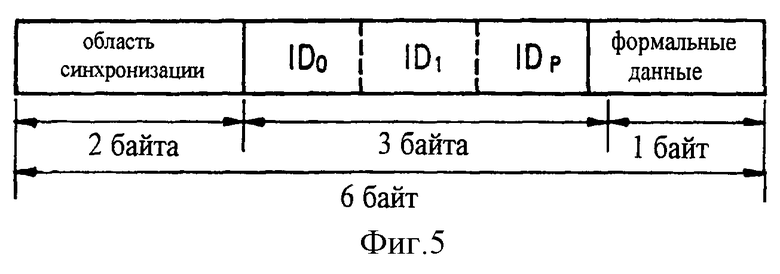

На Фиг. 5 изображена структура блока постсинхронизации, показанного на Фиг. 2.

Согласно Фиг. 5 блок постсинхронизации состоит из 2-байтовой синхронизации, 3-байтового ID кода и 1-байтовых формальных данных. Формальными данными всегда являются FFn•ID0 кода (ID0, ID1 и IDp) показывает информацию пары дорожек и информацию применения, ID1 показывает номер блока синхронизации, и IDp показывает ID равенство исправления ошибки для ID0 и ID1.

Блок предварительной синхронизации и блок постсинхронизации, показанные на Фиг. 3 и 5, имеют общую форму для аудио и видео секторов.

В цифровом VCR, имеющем описанный выше формат записи, синхронизация должна быть точно определена во время воспроизведения для того, чтобы точно определить данные каждой области, которая была записана в ранее определенном положении.

Каждый из интервалов синхронизации SYNC-D и SYNC-E, как описано ниже, записан в областях синхронизации блока предварительной синхронизации области PRE2, блоке синхронизации данных области AUDIO, и блоке постсинхронизации области POS2 в аудио секторе, и в областях синхронизации блока предварительной синхронизации области PRE3, блоке синхронизации данных области VIDEO и блоке предварительной синхронизации области POS3 в видео секторе, показанном на Фиг. 1.

SYNC-D: 00011111111110001

SYNC-E: 11100000000001110

Каждый из интервалов синхронизации SYNC-F и SYNC-G, как описано ниже, записан в областях синхронизации блока синхронизации подкода сектора подкода, показанного на Фиг. 1.

SYNC-F: 00000111111111101

SYNC-G: 11111000000000010

Каждый из интервалов обновления RVN-A и RVN-B, как описано ниже, записан в промежутке для редакции G1 между ITI сектором и аудио сектором, промежутке для редакции G2 между аудио сектором и видео сектором, промежутке для редакции G3 между видео сектором и сектором подкода, области обновления вводной части в каждом секторе и области защиты заключительной части каждого сектора.

RVN-A: 0001110001110000011100011

RVN-B: 1110001110001111100011100

В устройстве воспроизведения известного цифрового VCR создана схема защиты синхронизации, так как точное определение данных затруднено, когда в синхронизации есть ошибка.

Между тем, в схеме определения синхронизации (патент США N 4747116) сигнал показания синхронизации определяется сравнением ранее определенного интервала синхронизации с интервалом синхронизации входного цифрового сигнала, определяются ошибки входной цифровой синхронизации, определенный сигнал индикации синхронизации выводится, если номера ошибок равны ранее заданному значению или ниже, и выход определенного сигнала индикации синхронизации предотвращается, если номер превышает ранее заданное значение.

В схеме определения синхронизации для цифрового аудиомагнитофона с вращающейся головкой (патент США N 5228041) синхронизация последовательных цифровых данных, имеющих код определения ошибки, генерируемый ранее определенным вычислением, сравнивается с заранее определенным интервалом синхронизации в течение продолжительности каждого блока путем использования вспомогательного кода и адресного кода, показывающего адресное значение периода блока. Сигнал определения синхронизации генерируется, если синхронизация идентична интервалу синхронизации, и сигнал определения ошибки определен ранее определенным вычислением путем использования вспомогательного кода, адресного кода и кода определения ошибки. Сигнал определения синхронизации является выходным сигналом, если только не найдена ошибка в сигнале определения ошибки.

Однако описанные выше схемы определения синхронизации не могут применяться в цифровом VCR, имеющем SD формат записи сигнала и не имеют функции генерирования псевдосинхронизирующего сигнала управления, который предлагается в настоящем изобретении, когда в синхронизации есть ошибка.

Существо изобретения

Целью настоящего изобретения является создание схемы определения синхронизации и защиты для точного определения данных, записанных в ранее определенной области каждой дорожки, путем определения синхронизации и генерирования псевдосинхронизирующего сигнала управления, когда в синхронизации найдена ошибка.

Другой целью настоящего изобретения является создание способа определения синхронизации и защиты для точного определения данных, записанных в ранее определенной области каждой дорожки путем определения синхронизации и генерирования псевдосинхронизирующего сигнала управления, когда найдена ошибка в синхронизации.

Для достижения вышеописанных целей создана схема определения синхронизации и защиты для использования в воспроизводящих устройствах для воспроизведения цифровых данных из записывающей среды, где заранее определенное множество областей для записи цифровых данных выполнены в каждой дорожке, каждая область состоит из множества блоков синхронизации, и ранее определенный предварительный интервал записан в начале каждой области, схема определения синхронизации и защиты содержит: первое детекторное (определяющее) средство для определения предварительного интервала цифровых данных, полученных из записывающей среды, и вывода соответствующего сигнала области; второе детекторное (определяющее) средство для определения синхронизации полученных цифровых данных, сравнения определенной синхронизации и заранее определенного интервала синхронизации и вывода сигнала определения синхронизации; и средство генерирования для генерирования синхронизирующего сигнала управления на основе сигнала определения синхронизации и генерирования псевдосинхронизирующего сигнала управления, если определенная синхронизация имеет ошибку.

Для достижения другой цели создан способ определения синхронизации и защиты для использования в воспроизводящих устройствах для воспроизведения цифровых данных из записывающей среды, в которой заранее определенное множество областей для записи цифровых данных размещены в каждой дорожке, каждая область состоит из множества блоков синхронизации, заранее определенный предварительный интервал записан в начале каждой области, способ определения синхронизации и защиты содержит следующие шаги: (a) определение заранее заданного интервала цифровых данных, полученных из записывающей среды, и генерирование соответствующего сигнала области; (b) определение синхронизации полученных цифровых данных, сравнение определенной синхронизации с заранее определенным интервалом синхронизации и генерирование сигнала определения синхронизации; и (с) генерирование синхронизирующего сигнала управления на основе сигнала определения синхронизации и генерирование псевдосинхронизирующего сигнала управления, если найдена ошибка в определенной синхронизации.

Краткое описание чертежей

Описанные выше цели и преимущества настоящего изобретения будут более очевидны из подробного описания предпочтительного варианта выполнения со ссылками на прилагаемые чертежи, в которых:

На Фиг. 1 изображен вариант выполнения секторов на винтовой дорожке пленки в цифровом VCR;

на Фиг. 2 изображена структура видео сектора, показанного на Фиг. 1;

на Фиг. 3 изображена структура блока предварительной синхронизации, показанного на Фиг. 2;

на Фиг. 4 изображена структура блока данных синхронизации, показанного на Фиг. 2;

на Фиг. 5 изображена структура блока постсинхронизации, показанного на Фиг. 2;

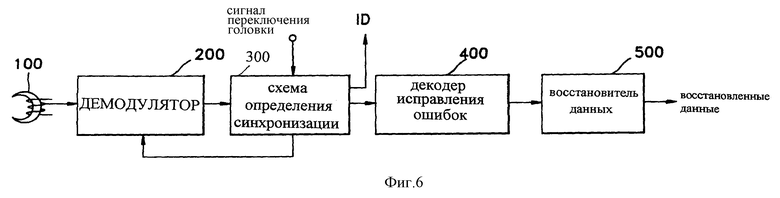

на Фиг. 6 изображена блок-схема воспроизводящего устройства цифрового VCR, в котором применяется настоящее изобретение;

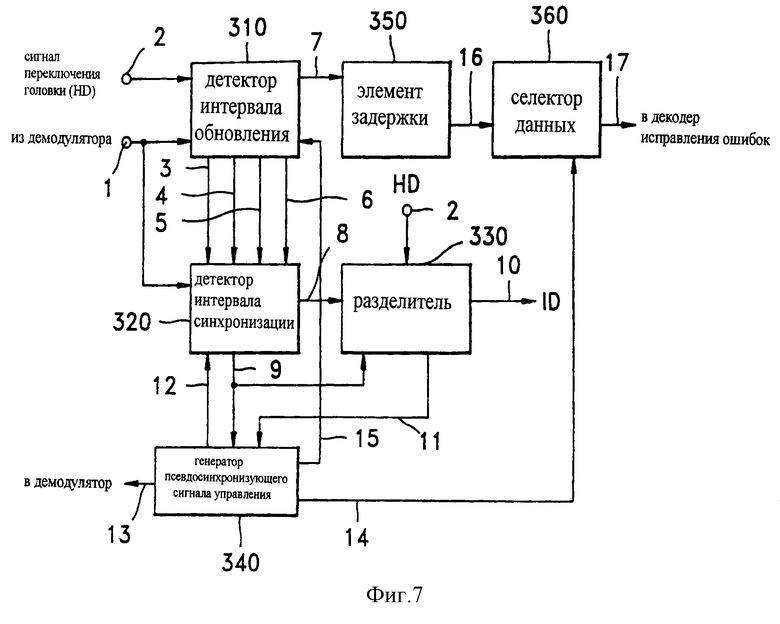

на Фиг. 7 изображена блок-схема определения синхронизации и защиты согласно настоящему изобретению;

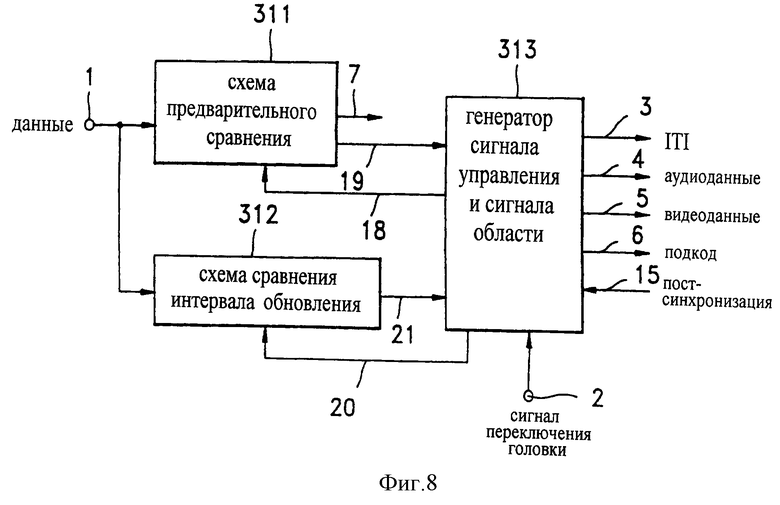

на Фиг. 8 изображена блок-схема детектора интервала обновления, показанного на Фиг. 7;

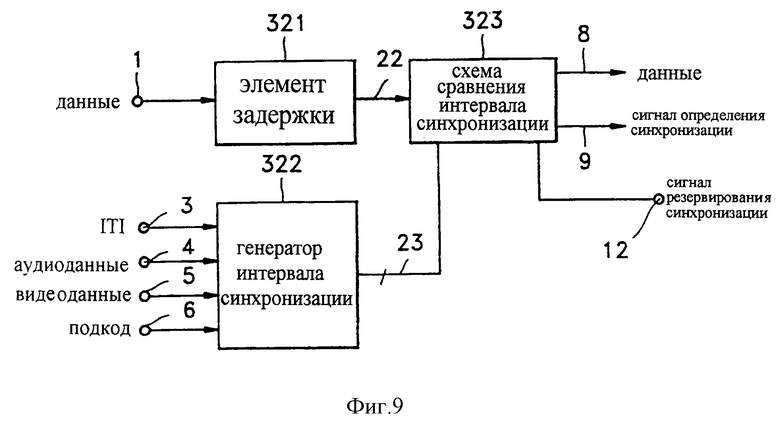

на Фиг. 9 изображена блок-схема детектора интервала синхронизации, показанного на Фиг. 8; и

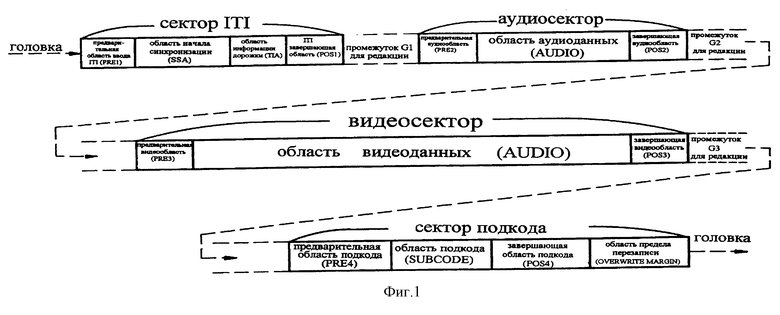

на Фиг. 10 изображена блок-схема ID разделителя, показанного на Фиг. 7.

Подробное описание изобретения

На Фиг. 6 изображена блок-схема воспроизводящего устройства цифрового VCR, в котором применяется настоящее изобретение.

Согласно Фиг. 6 сигнал, воспроизводимый головкой 100, вводится в демодулятор 200. В демодуляторе 200 воспроизводимые 25-битовые данные демодулируются в 24-битовые данные. Здесь модуляция 24-в-25 осуществляется во время записи. Модуляция 24-в-25 показывает, что 0 битов или 1 бит предшествует 24-битовым данным, достигая таким образом 25-битового слова канала предназначенного спектра частоты.

Как показано в структуре дорожки на Фиг. 1, головка 100 считывает данные, записанные на дорожке из PRE1 в POS4. Для точного считывания данных в каждой области синхронизация должна быть определена точно.

Поэтому схема определения синхронизации и защиты 300 определяет синхронизацию из данных, демодулирозанных в демодуляторе 200, сравнивает интервал определенной синхронизации с заранее определенным интервалом синхронизации, выводит синхронизирующий сигнал управления в демодулятор 200, если они одинаковы, генерирует псевдосинхронизирующий сигнал управления, если найдена ошибка в определенном интервале синхронизации, и выводит псевдосинхронизирующий сигнал управления в демодулятор 200.

Декодер исправления ошибки 400 декодирует данные, закодированные в форме кода продукта, т.е. кода Рида-Соломона, который выходит из схемы определения синхронизации и защиты 300, путем использования внутреннего равенства и внешнего равенства.

Восстановитель данных 500 декодирует с изменением длины декодированные данные исправления ошибки, производит инверсивное квантование декодированных данных переменной длины, и восстанавливает инверсивно-квантуемые данные в первичные данные при операции преобразования инверсивного дискретного косинуса путем использования размера шага квантования, используемого во время кодирования.

На Фиг. 7 изображена блок-схема определения синхронизации и защиты согласно варианту выполнения настоящего изобретения.

Согласно Фиг. 7 выход демодулированных данных из выходного порта 1 демодулятора 200, показанного на Фиг.6, является входом в детектор интервала обновления 310 и детектор интервала синхронизации 320.

Детектор интервала обновления 310 определяет интервал обновления (который именуется предварительным интервалом), каждой предварительной области полученных данных и выводит сигнал области, соответствующей ITI области, аудио области, видео области и области подхода через выходные порты 3, 4, 5 и 6 соответственно.

Детектор интервала синхронизации 320 сравнивает заранее определенный интервал синхронизации с интервалом синхронизации демодулированных данных, полученных через входной порт 1 демодулятора 200, в соответствии с выходом сигнала каждой области из выходных портов 3, 4, 5 и 6, генерирует сигнал определения синхронизации, выводит сигнал определения синхронизации в ID разделитель 330 и генератор псевдосинхронизирующего сигнала управления 340 и вводит демодулированные данные в ID разделитель 330.

ID разделитель 330 отделяет ID от вывода данных из выходного порта 8 детектора интервала синхронизации 320 в соответствии с сигналом переключения головки HD, полученным из входного порта 2, и выходом сигнала определения синхронизации из выходного порта 9 детектора интервала синхронизации 320, выводит ID через выходной порт 10, сравнивает записанный ID с текущим ID и выводит ID сигнал сравнения через выходной порт 11 в генератор псевдосинхронизирующего сигнала управления 340.

Генератор псевдосинхронизирующего сигнала управления 340 выводит сигнал резервирования синхронизации через выходной порт 12 в детектор интервала синхронизации 320, если сигнал определения синхронизации получен через выходной порт 9 детектора интервала синхронизации 320, и выводит синхронизирующий сигнал управления в демодулятор 200 через выходной порт 13, если получен сигнал определения синхронизации, генерируемый во время периода резервирования синхронизации, и ID выход сигнала сравнения из выходного порта 11. Даже если ID сигнал сравнения определен без сигнала определения синхронизации, синхронизирующий сигнал управления выводится через выходной порт 13 в демодулятор 200. Здесь синхронизирующий сигнал управления выступает в качестве псевдосинхронизирующего сигнала управления. Более того, синхронизирующий сигнал управления выводится в демодулятор 200, когда сигнал определения синхронизации для блока синхронизации данных определяется после определения сигнала определения синхронизации для блока предварительной синхронизации.

Между тем, генератор псевдосинхронизирующего сигнала управления 340 генерирует синхронизацию и ID сигнал области, когда синхронизирующий сигнал управления выходит в демодулятор 200, выводит синхронизацию и сигнал ID области через выходной порт 14 в селектор данных 360 и выводит сигнал определения постсинхронизации через выходной порт 15 в детектор интервала обновления 310, если сигнал определения синхронизации, определенный во время периода резервирования синхронизации, является сигналом для постсинхронизации каждого сектора для управления детектором интервала обновления 310 при генерировании следующего сигнала области.

Элемент задержки 350 задерживает данные, демодулированные в демодуляторе 200, который является выходом выходного порта 7 детектора интервала обновления 310 во время обработки сигнала пока генерируется синхронизация и сигнал ID области, и выводит задержанные данные через выходной порт 16 в селектор данных 360.

Селектор данных 360 выводит вывод данных через выходной порт 16 как данные, из которых удаляются синхронизация и в соответствии с синхронизацией и выходом сигнала ID области через выходной порт 14 генератора псевдосинхронизирующего сигнала управления 340, в декодер исправления ошибки 400. Здесь детектор 310 интервала обновления именуется детекторным средством, детектор 320 интервала синхронизации именуется вторым детекторным средством, ID разделитель 330 именуется ID разделяющим средством, а генератор 340 псевдосинхронизирующего сигнала управления именуется средством генерирования сигнала управления.

Работа схемы, показанной на Фиг. 7, будет описана подробно в связи с Фиг. 8-10.

На Фиг. 8 изображена подробная блок-схема детектора интервала обновления 310, показанного на Фиг. 7.

Согласно Фиг. 8 выход демодулированных данных из выходного порта 1 является входом в ITI схему предварительного сравнения 311 и в схему сравнения интервала обновления 312.

Когда генератор 313 сигнала управления и сигнала области получает из входного порта 2 HD сигнал переключения головки, показывающий начало воспроизведения каждой дорожки, первый разрешающий сигнал выводится через первый разрешающий порт 18 в ITI предварительную схему 311, включая ITI схему предварительного сравнения 311.

ITI схема предварительного сравнения 311, имеющая предварительные встроенные интервалы, сравнивает встроенный предварительный интервал с предварительным интервалом данных, полученных через входной порт 1, и выводит первый сравнивающий сигнал как "высокий" сигнал через выходной порт 19 в генератор 313 сигнала управления и сигнала области. Генератор 313 сигнала управления и сигнала области выводит ITI сигнал области, показывающий область ITI, через выходной порт 3.

Когда ITI схема предварительного сравнения 311 определяет завершающую часть ITI, первый сравнивающий сигнал выводится как "низкий" сигнал в генератор 313 сигнала управления и сигнала области. Затем генератор 313 сигнала управления и сигнала области выводит второй разрешающий сигнал через второй разрешающий порт 20 в схему сравнения интервала обновления 312 для включения схемы сравнения интервала обновления 312.

Схема сравнения интервала обновления 312, имеющая встроенные интервалы обновления RVN-A и RVN-B, сравнивает встроенный интервал обновления демодулированных данных, полученных из входного порта 1, выводит второй сравнивающий сигнал как "высокий" сигнал через выходной порт 21 в генератор 313 сигнала управления и сигнала области, если они одинаковы, выводит второй сравнивающий сигнал как "низкий" сигнал в генератор 313 сигнала управления и сигнала области, если сигнал определения постсинхронизации аудио сектора вводится через выходной порт 15 в генератор псевдосинхронизирующего сигнала управления, показанный на Фиг. 7, спустя определенное время.

При повторении процедуры второй сравнивающий сигнал на дорожке периодически меняется между "высоким" и "низким" три раза".

Таким образом, в генераторе 313 сигнала управления и сигнала области, если второй сравнивающий сигнал на первом логическом высоком уровне получен через выходной порт 21 схемы сравнения интервала обновления 312, AUDIO сигнал области, показывающий аудио область, вводится через выходной порт 4, если второй сравнивающий сигнал на втором логическом высоком уровне получен, VIDEO сигнал области, показывающий видео область, вводится через выходной порт 5, и, если второй сравнивающий сигнал на третьем логическом высоком уровне получен, SUBCODE сигнал области, показывающий область подкода, выводится через выходной порт 6. Выходные порты 3, 4, 5 и 6 соединены с генератором интервала синхронизации 322 детектора интервала синхронизации 320, показанного на Фиг. 9.

Здесь выходные данные III схемы предварительного сравнения 311 являются выходом к элементу задержки 350 Фиг.7 через выходной порт 7.

На Фиг. 9 изображена подробная блок-схема детектора интервала синхронизации 320, показанного на фиг. 7.

Согласно Фиг. 9 генератор интервала синхронизации 322 имеет встроенный интервал синхронизации каждой области и выводит соответствующий интервал синхронизации в соответствии с выходом сигнала каждой области из выходных портов 3, 4, 5 и 6 и генератора 313 сигнала управления и сигнала области, через выходной порт 23 в схему сравнения интервала синхронизации 323.

Как описано выше, генератор интервала синхронизации 322 генерирует интервалы синхронизации SYNC-D и SYNC-E, если сигналы области, полученные из выходных портов 3, 4, 5 и 6, показывают аудио и видео области, и генерирует интервалы синхронизации SYNC-F и SYNC-G, если сигнал области, полученный из выходных портов 3, 4, 5 и 6, показывает область подкода.

Элемент задержки 321 задерживает демодулированные данные, полученные из входного порта 1, в течение заранее заданного времени для компенсации времени для генерирования сигнала области в детекторе интервала обновления 310 и выводит задержанные данные через выходной порт 22 в схему сравнения интервала синхронизации 323.

Соответственно, в схеме сравнения интервала синхронизации 323, данные, полученные из элемента задержки 321, выводятся через выходной порт 8, интервал синхронизации входных данных сравнивается с интервалом синхронизации, генерируемым генератором интервала синхронизации 322 во время разрешающего периода выхода сигнала резервирования синхронизации через выходной порт 12 генератора псевдосинхронизирующего сигнала управления 340 и, если они одинаковы, сигнал определения синхронизации выводится через выходной порт 9 в генератор псевдосинхронизирующего сигнала управления 340, показанный на Фиг. 7, и ID детектор 331 и буфер 334 ID разделителя 330, показанного на Фиг. 10.

Здесь выход данных из выходного порта 8 схемы сравнения интервала синхронизации 323 задержан за счет времени для генерирования сигнала определения синхронизации в элементе задержки (не показан) схемы сравнения интервала синхронизации 323 и затем вывод в ID детектор 331, показанный на Фиг. 10.

На Фиг. 10 изображена подробная блок-схема ID разделителя 330, показанного на Фиг. 7.

Согласно Фиг. 10 ID детектор определяет 3-байтовый код ID из выхода данных из выходного порта 8 схемы сравнения интервала синхронизации 323, показанной на фиг. 9.

ID корректор ошибки 332 исправляет ошибки 2-байтового кода ID (ID0 и ID1) 3-байтового кода ID с равенством другого 1-байтового кода ID (IDp)i и выводит 2-байтовый код ID (ID0 и ID1) с исправленными ошибками через выходной порт 25 в ID схему сравнения 333.

ID схема сравнения 333 выводит исправленный 2-байтовый код ID (ID0 и ID1) через выходной порт 10, используемый для управления системы. Кроме того, ID схема сравнения 333 определяет непрерывность и конгруэнтность между текущими ID0 и ID1 выходами из ID корректора ошибки 332 и ID0 и ID1 выходами из буфера 334, где ID0 и ID1 предыдущей дорожки или предыдущего блока синхронизации записаны в памяти.

Таким образом, если сигнал переключения головки HD получен из входного порта 2, буфер 334 выводит биты информации пары дорожек предыдущей дорожки ID0 через выходной порт 26 в ID схему сравнения 333 и, когда сигнал определения синхронизации получен из выходного порта 9 схемы сравнения интервала синхронизации 323, показанной на Фиг. 9, выводит ID1 предыдущего блока синхронизации через выходной порт 27 в ID схему сравнения 333.

Здесь ID0 имеет одинаковую информацию пары дорожек, записанную на каждых двух дорожках. ID1 показывает номер блока синхронизации, и таким образом он должен быть увеличен на "1", когда определен сигнал определения синхронизации.

ID схема сравнения 333 сравнивает информацию пары дорожек ID1 кода, записанного в буфере 334, с информацией пары дорожек текущего ID0 путем получения ID, исправленного в ID корректоре ошибки 332, и выхода ID0 из буфера 334. То есть определяется, являются ли одинаковыми текущий ID0 и ID0 предыдущей дорожки и их приращение равно "1". Затем текущий ID1 сравнивается с ID1 предыдущего блока синхронизации для определения, равно ли приращение "1", т. е. для определения, существует ли непрерывность между обоими ID. Когда существует конгруэнтность и непрерывность между ними, сравнивающий сигнал выводится как "высокий" сигнал в генератор псевдосинхронизирующего сигнала управления 340 через выходной порт 11 и текущий ID записан в буфере 334 через выходной порт 28.

В случае, когда информация пары дорожек текущего ID0 и предыдущего ID0 отличается или отсутствует непрерывность между текущим ID0 и предшествующим ID0, ID сравнивающий сигнал выходит как "высокий" сигнал из ID схемы сравнения 333 и ID текущего блока синхронизации считается одинаковым с ID предшествующего блока синхронизации. Однако в случае, когда информация пары дорожек текущего ID0 и предшествующего ID0 также отличается в следующем блоке синхронизации или отсутствует непрерывность между текущим ID1 и предшествующим ID1, ID сравнивающий сигнал выходит как "низкий" сигнал и ID текущего блока синхронизации считается рассогласованным с ID предшествующего блока синхронизации.

Между тем, необходимо проверять, генерируется ли в 6-байтовом цикле 2-байтовая синхронизация для предварительной синхронизации и постсинхронизации и генерируется ли в 90-байтовом цикле 2-байтовая синхронизация для синхронизации данных. Причина в том, что синхронизация должна быть определена в правильном положении для предотвращения генерирования таких же данных, как интервал синхронизации в области данных.

Следовательно, когда первый сигнал определения синхронизации для каждой области получен через выходной порт 9 схемы сравнения интервала синхронизации 323, показанной на Фиг. 9, генератор псевдосинхронизирующего сигнала управления 340, изображенный на Фиг. 7, генерирует сигнал резервирования синхронизации для области следующей приходящей синхронизации и выводит сигнал резервирования синхронизации через выходной порт 12 в схему сравнения интервала синхронизации 323 детектора интервала синхронизации, показанного на Фиг. 9.

Сигнал резервирования синхронизации принимает различные формы, зависящие от аудио, видео- или области подкода. Например, в случае видео области, если сигнал определения синхронизации определен для первого из двух блоков предварительной синхронизации, логический "высокий" сигнал резервирования синхронизации генерируется только во время периода области синхронизации второго блока предварительной синхронизации. Соответственно, логический "высокий" сигнал резервирования синхронизации генерируется только во время периода области синхронизации 149 блоков синхронизации данных в 90-байтовом цикле, и затем логический "высокий" сигнал резервирования синхронизации генерируется только во время периода области синхронизации блока постсинхронизации.

Когда сигнал определения синхронизации для блока синхронизации данных определен из детектора интервала синхронизации 320 во время периода резервирования синхронизации и ID выход сравнивающего сигнала из выходного порта 11 ID схемы сравнения 333, показанной на Фиг. 10, является "высоким", генератор псевдосинхронизирующего сигнала управления 340 выводит синхронизирующий сигнал управления через выходной порт 13 в демодулятор 200, показанный на Фиг. 6, т.о. разрешая правильное определение данных. Демодулятор 200 задерживает данные, воспроизводимые головкой 100, в течение времени генерирования выхода синхронизирующего сигнала управления через выходной порт 13 генератора псевдосинхронизирующего сигнала управления 340.

С другой стороны, если даже сигнал определения синхронизации не определен в течение периода резервирования синхронизации, если ID сравнивающий сигнал является "высоким", генератор псевдосинхронизирующего сигнала управления 340 выводит синхронизирующий сигнал управления через выходной порт 13 в демодулятор 200. Здесь синхронизирующий сигнал управления функционирует как псевдосинхронизирующий сигнал управления. Даже, если ID сравнивающий сигнал является "низким", если сигнал определения синхронизации определен, синхронизирующий сигнал управления обычно выходит через выходной порт 13. Однако, если не определен сигнал определения синхронизации и ID сравнивающий сигнал является "низким", предотвращается вывод синхронизирующего сигнала управления из демодулятора 200 и не разрешается вывод сигнала резервирования синхронизации в детектор интервала синхронизации 320.

Т. е. если не определен интервал синхронизации вследствие ошибки синхронизации, генерируется синхронизирующий сигнал управления (псевдосинхронизирующий сигнал управления), и если последовательно не определен интервал синхронизации, все интервалы синхронизации данных на соответствующей дорожке определяются для определения данных.

Кроме того, во время завершающей синхронизации, определяется постсинхронизация для соответствующей области, генератор псевдосинхронизирующего сигнала управления 340 выводит сигнал определения постсинхронизации через выходной порт 15 в генераторе 313 сигнала управления и сигнала области детектора интервала обновления 310, показанного на Фиг. 8, как описано выше.

Когда сигнал определения синхронизации для блока синхронизации данных генерируется после сигнала определения синхронизации для блока предварительной синхронизации, то есть когда синхронизирующий сигнал управления выходит в демодулятор 200, сигнал синхронизации и ID области выходит через выходной порт 14 в селектор данных 360. Селектор данных 360 разделяет синхронизацию и ID от вывода данных из выходного порта 16 элемента задержки 350 в соответствии с синхронизацией и ID сигналом области, выделяет только действительные данные и равенство и выводит выделенные данные и равенство через выходной порт 17 в декодер исправления ошибки 400.

Даже если настоящее изобретение не обеспечено ID разделителем 330, использующим определенный ID сигнал для правильного определения синхронизации, проблем, связанных с работой, не существует.

Как описано выше, в схеме настоящего изобретения, синхронизация, используемая для определяющих данных в ранее определенном положении, точно определена и даже, если в синхронизации найдена ошибка, псевдосинхронизирующий сигнал управления генерируется, разрешая правильное определение данных в ранее определенном положении.

Создана схема определения синхронизации и защиты для использования в воспроизводящих устройствах. Схема определения синхронизации и защиты содержит первый детектор для определения предварительного интервала цифровых данных, полученных из записывающей среды, и вывод сигнала соответствующей области, второй детектор для определения синхронизации полученных цифровых данных, сравнения определенной синхронизации и заранее определенного интервала синхронизации и вывода сигнала определения синхронизации, 1D разделитель для разделения 1D кода, следующего за определенной синхронизацией, сравнения разделенного 1D с предшествующей дорожкой и блоком синхронизации и вывода 1D сигнала сравнения и генератор сигнала управления для генерирования синхронизирующего сигнала управления на основе сигнала определения синхронизации и 1D сигнала сравнения и генерирования псевдосинхронизирующего сигнала управления, если в определенной синхронизации есть ошибка. Следовательно, синхронизация, используемая для определения данных в заранее определенном положении, определена точно и псевдосинхронизирующий сигнал управления генерируется, даже если в синхронизации найдена ошибка, таким образом разрешая правильное определение данных в заранее определенном положении, в чем и состоит технический результат, достигаемый при осуществлении предлагаемой группы изобретений. 3 с. и 13 з.п.ф-лы, 10 ил.

| US 4747116 A, 13.07.1988 | |||

| Устройство кадровой синхронизации | 1990 |

|

SU1737745A1 |

| US 5228041 A, 13.07.1993 | |||

| US 5216667 A, 01.06.1992. | |||

Авторы

Даты

2000-11-20—Публикация

1996-05-30—Подача