Изобретение относится к устройству для записи цифровых сигналов, использующему при записи I-NRZI-модуляцию (перемежающаяся, без возвращения к нулю, с инвертированием на единицы), которая включает пилот-сигналы, используемые для слежения головки во время воспроизведения. В устройствах магнитной записи/воспроизведения, например, в видеомагнитофонах, из-за того, что во время воспроизведения головка отклоняется от дорожки на магнитном носителе записи, выходной сигнал головки ослабевает и увеличиваются сигналы ошибки. Это препятствует нормальному воспроизведению изображения, следовательно, необходимо, чтобы головка точно следовала по заданной дорожке. Другими словами, необходимо поддерживать трекинг головки. Для того чтобы удлинить время записи, в цифровых видеомагнитофонах для домашнего пользования дорожки выполняются специально узкими, что повышает требования к точности слежения головки, необходимой для удовлетворительного воспроизведения изображения. Среди способов обнаружения ошибки слежения или отклонения от идеального слежения имеются способы, которые используют соответствующие пилот-сигналы различного типа для следующих друг за другом дорожек, что облегчает сравнение перекрестных помех пилот-сигналов от предшествующих дорожек и последующей дорожки, ближайшей в данный момент к головке, и дает возможность определить, к какой из дорожек, предыдущей или последующей, отклоняется головка. Пилот-сигналы имеют пики и провалы в частотном спектре цифровых сигналов, записываемых на дорожках посредством выбора одного из двух типов I-NRZI-модуляции. Одна и та же информация кодируется в виде двух параллельных во времени наборов из последовательно поступающих на дорожку слов (канальных слов); и канальные слова, которые выбираются из одного либо другого набора для управления I-NRZI-модуляцией во время записи, отбираются так, чтобы I-NRZI-модуляция имела бы минимальные отклонения по пилот-сигналу для каждой дорожки записи. Когда выбор канального слова завершен, предварительно закодированная информация, хранящаяся в устройстве предварительного кодирования (прекодере), который не генерирует выбранное канальное слово, изменяется для приведения ее в соответствие с предварительно закодированной информацией, хранящейся в прекодере, который сгенерировал выбранное канальное слово. Это делается для обеспечения непрерывности процедур предварительного кодирования и процедур декодирования, выполняемых вслед за I-NRZI-модуляцией, которая восстанавливается из носителя записи при воспроизведении и демодулируется. Когда выбор канального слова совершен, интеграторы в схемах определения, какое канальное слово должно быть выбрано, должны изменить свое содержимое для отражения того, какой канал был в действительности выбран для записи. Подобные способы описаны в патенте США N 5142421, выданном 25 августа 1992 года Kahlman и др. под заголовком "Device for recording a digital informational signal on a record carrier" (Устройство для записи цифровых информационных сигналов на носитель записи) и включенном в эту заявку по ссылке.

Согласно Kahlman и др. формирование I-NRZI-модуляции выполняется на последовательной битовой основе. Это не поддается конвейерной обработке, при которой канальные слова, отбираемые от последовательных битовых прекодеров, записываются на магнитный носитель записи после некоторой фиксированной задержки, необходимой для восстановления схем выбора. Требуется некоторое время после того, как сгенерирована пара соответствующих канальных слов, для процедуры принятия решения, которая определяет, какое из этих двух слов будет записано. После выполнения процедуры принятия решения требуется дополнительное время для изменения информации, хранящейся в прекодерах. Эти процедуры принятия решения и обновления информации должны завершиться, прежде чем будет возможно следующее предварительное кодирование, так что задержки, вызванные этими процедурами принятия решения и обновления информации, вызывают пропуски в непрерывном потоке бит, регулярно синхронизируемом согласно известным способам синхронизации. Процедуры принятия решения характеризуются значительными временными задержками, связанными с выполнением процедур цифрового умножения, сложения, интегрирования и возведения в квадрат, хотя время выполнения операции возведения в квадрат может быть уменьшено путем использования справочных таблиц, хранящихся в памяти, предназначенной только для считывания. Соответственно перед последовательными битовыми прекодерами должна быть предусмотрена буферная память F1F0 (первым поступил - первым выводится), которая может периодически считываться; а для канальных слов, генерируемых последовательными битовыми прекодерами, должна быть предусмотрена F1F0 буферная память, в которую могут периодически записываться и из которой могут последовательно непрерывно считываться выбранные канальные слова. Генерирование синхронизирующих сигналов для буферной памяти - достаточно сложная проблема, так что желательно избежать необходимости иметь буферную память для периодической записи или периодического считывания информации.

Благодаря данному изобретению в устройстве для записи цифровых сигналов, использующем I-NRZI-модуляцию, исключается связанная с этим необходимость в периодическом считывании и периодической записи буферной памяти. Предварительно кодирование, используемое для генерирования кодов, которые управляют формированием I-NRZI-модуляции, выполняется по принципу: слова - последовательно, биты в слове - параллельно. Прекодеры модифицируются для выполнения предварительного кодирования на ускоренной основе с использованием сквозного интегрирования следующих друг за другом бит, используемых для формирования каждого канального слова. Два прекодера генерируют затем канальные слова с (n+1) параллельными битами с частотой канальных слов в (n+1) меньшей, чем частота системного тактового генератора. Это оставляет дополнительное время в течение каждого интервала канального слова для выполнения процедуры принятия решения, в результате которой определяется, какое из канальных слов должно быть выбрано для записи. Имеется также достаточно дополнительного времени для завершения процедуры последовательного обновления, при которой предварительно закодированная информация, хранящаяся в прекодере, который не генерировал выбранное канальное слово, изменяется, чтобы прийти в соответствие с предварительно закодированной информацией, хранящейся в прекодере, который действительно сгенерировал выбранное канальное слово. Канальные слова в формате "слова - последовательно, биты - параллельно" из прекодеров, которые выбраны для записи на магнитный носитель, преобразуются в последовательный битовый формат с битовой частотой, равной частоте системного тактового генератора для I-NRZI-модуляции, использованной при записи. Закодированные потоки данных в формате "слова - последовательно, биты в слове - параллельно", поступающие от прекодеров, преобразуются в последовательный битовый формат с эффективной битовой частотой, существенно более высокой, чем частота системного тактового генератора, что обеспечивает своевременное выполнение процедур принятия решения и обновления информации.

В некоторых предпочтительных вариантах реализации изобретения канальные слова, поступающие от прекодеров, разделяются каждый на два подслова или разделенных канальных слова, при преобразовании к последовательному битовому формату для получения двух параллельных битовых потоков, каждый из которых имеет такую же битовую частоту, как системный тактовый генератор, используемый для управления I-NRZI-модуляцией, применяемой при записи. Два параллельных битовых потока обеспечивают входные данные для расчетов, выполняемых для определения того, какое из канальных слов должно быть записано, причем входные данные имеют эффективную битовую частоту, в два раза большую, чем системный тактовый генератор.

В альтернативных вариантах реализации изобретения, для того чтобы генерировать сигналы, на основе которых выполняются расчеты для определения, какое из канальных слов должно быть записано, канальные слова, поступающие от прекодеров, преобразуются в последовательный битовый формат, имеющий битовую частоту, в два раза превышающую частоту системного тактового генератора, используемую для управления I-NRZI-модуляцией при записи. Последовательные битовые канальные слова, имеющие битовую частоту, в два раза превышающую частоту системного тактового генератора, обеспечивают входные данные для расчетов, которые выполняются для определения того, какое из канальных слов должно быть записано.

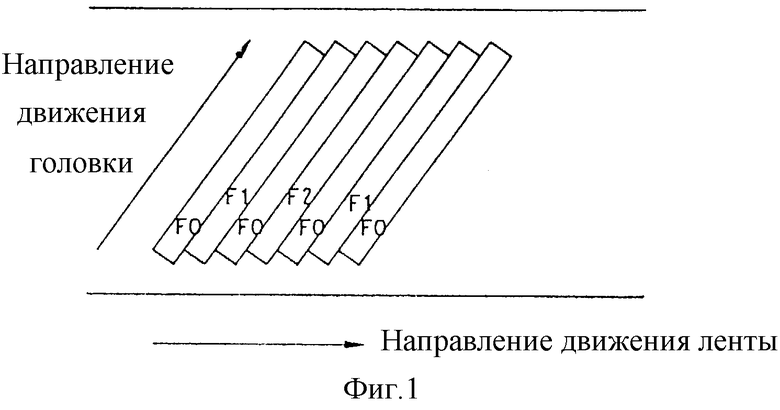

Фиг. 1 иллюстрирует запись последовательного потока канальных слов на смежные параллельные дорожки, расположенные на поверхности магнитного носителя записи.

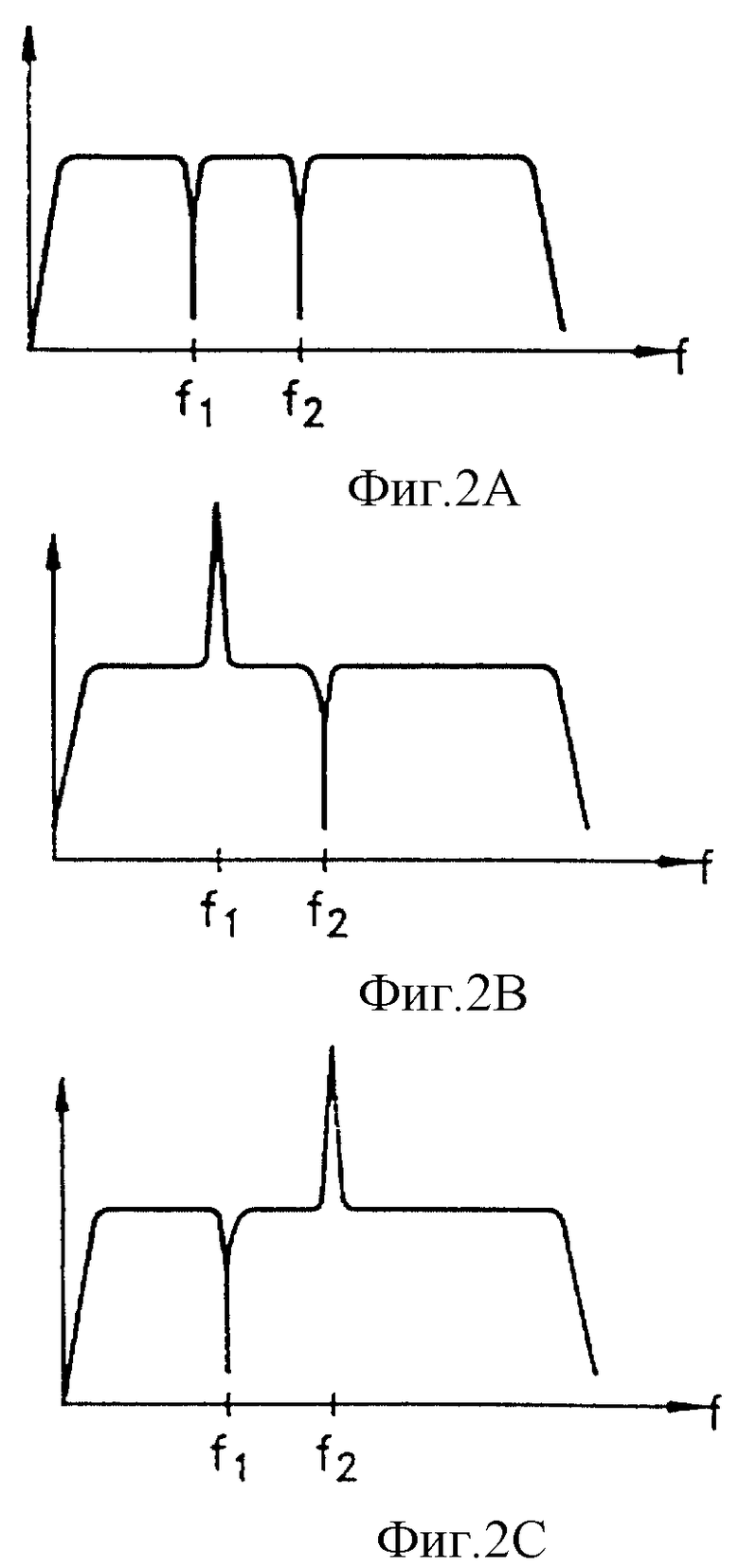

На фиг. 2A, 2B и 2C показаны частотные спектры, относящиеся к изображению, показанному на фиг. 1.

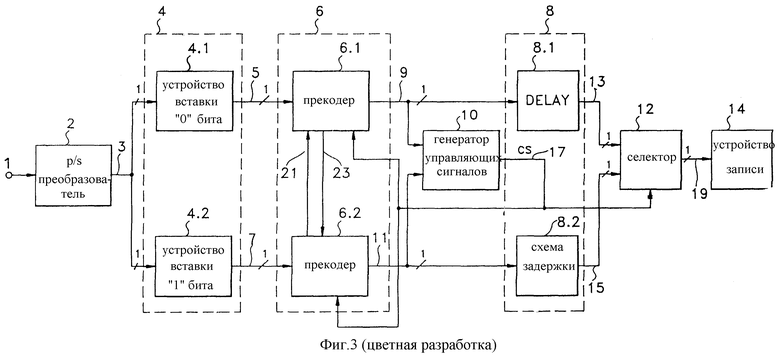

На фиг. 3 представлена блок-схема известного устройства для записи цифровых сигналов, описанного в патенте США N 5142421.

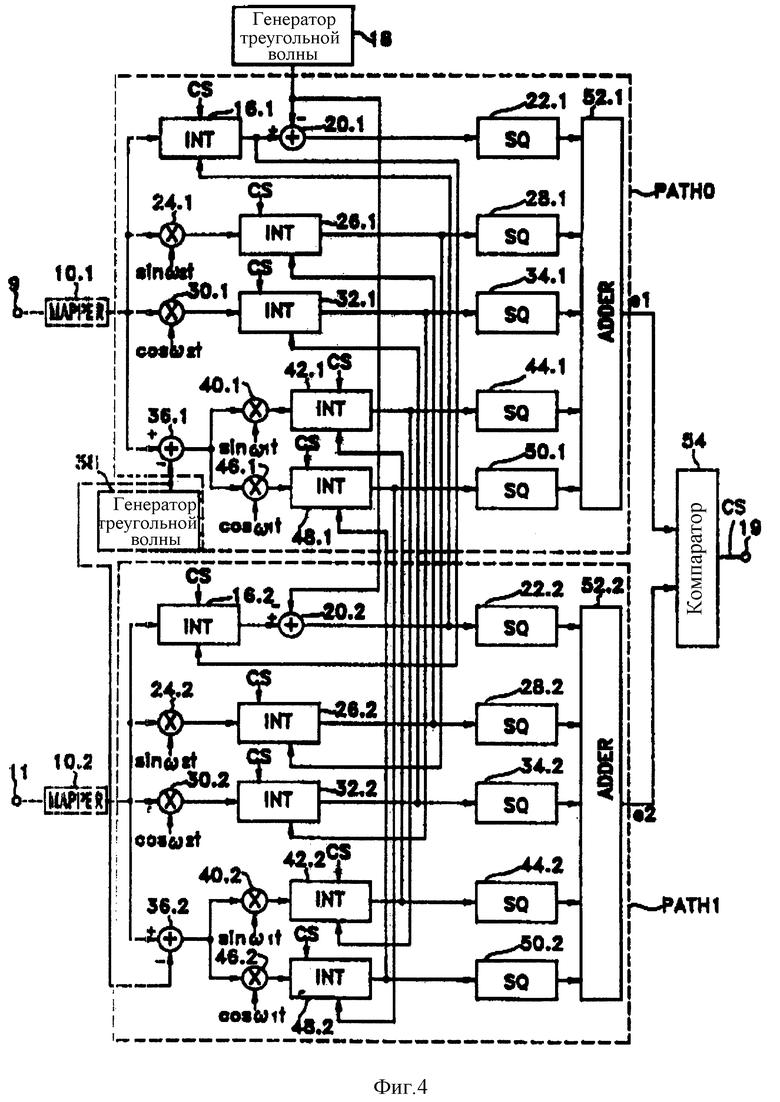

На фиг. 4 показана подробная схема одной из частей усовершенствованного генератора контрольного (управляющего) сигнала для устройства записи цифровых сигналов, показанного на фиг. 3.

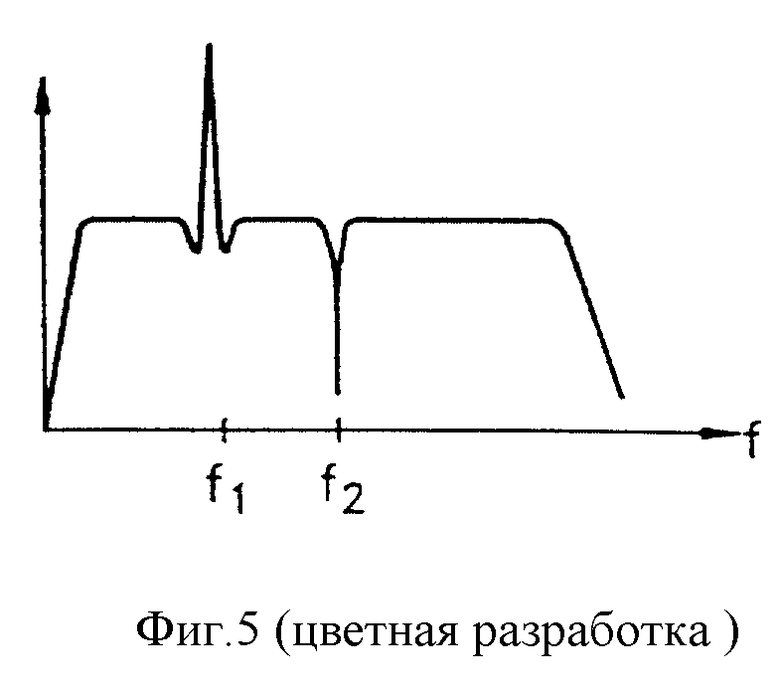

На фиг. 5 показан один из вариантов частотного спектра последовательного потока канальных слов, выбираемых посредством контрольного сигнала, который генерируется генератором контрольного (управляющего) сигнала, показанным на фиг. 4.

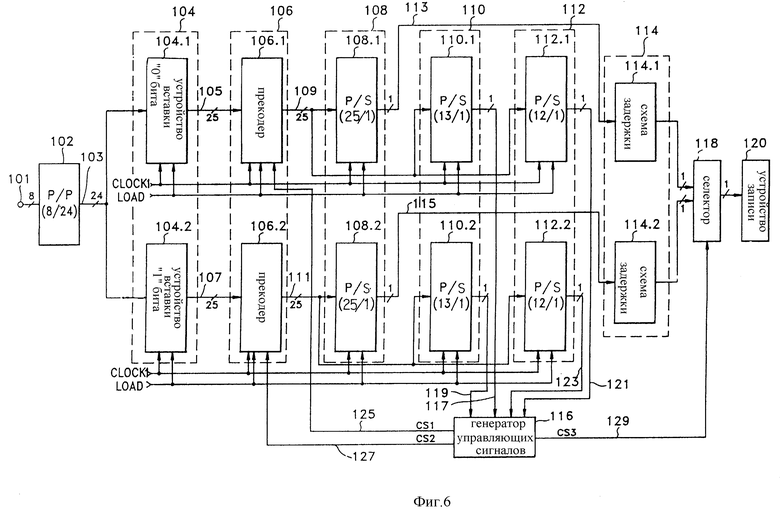

На фиг. 6 представлена блок-схема устройства для записи цифровых сигналов согласно изобретению.

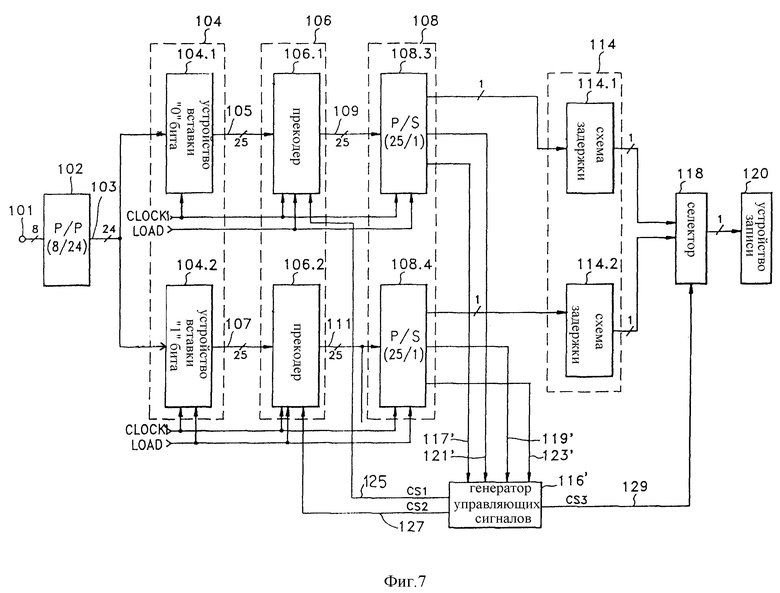

На фиг. 7 показана блок-схема другого устройства для записи цифровых сигналов согласно изобретению.

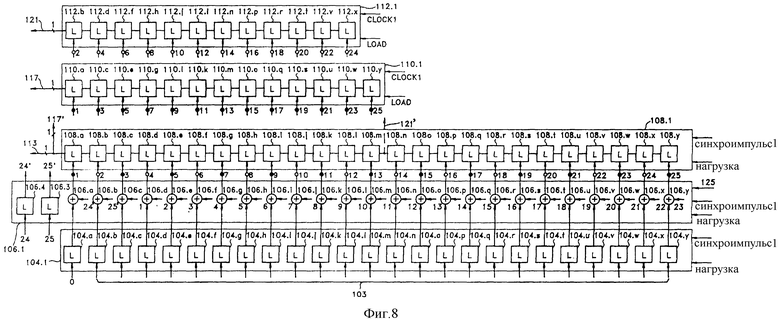

На фиг. 8 показана подробная схема одной из частей устройства для записи цифровых сигналов на фиг. 6.

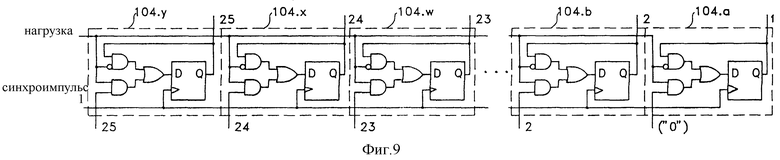

На фиг. 9 показана схема устройства вставки "0" бита, показанного на фиг. 8.

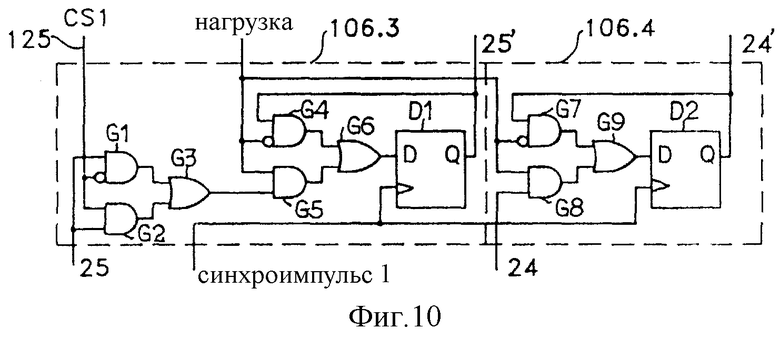

На фиг. 10 представлена схема 2Т-прекодера, показанного на фиг. 8.

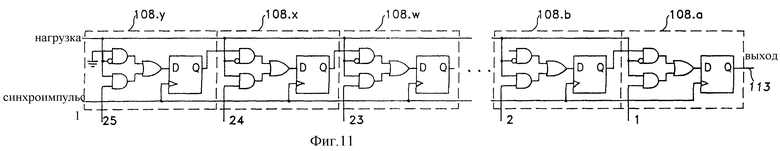

На фиг. 11 изображена подробная схема параллельно-последовательного преобразователя, показанного на фиг. 8.

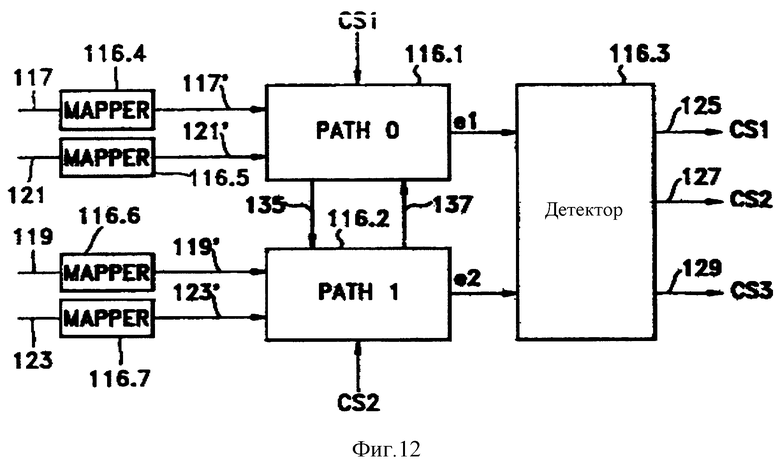

На фиг. 12 представлена блок-схема генератора управляющего сигнала, который используется в устройстве для записи цифровых сигналов на фиг. 6.

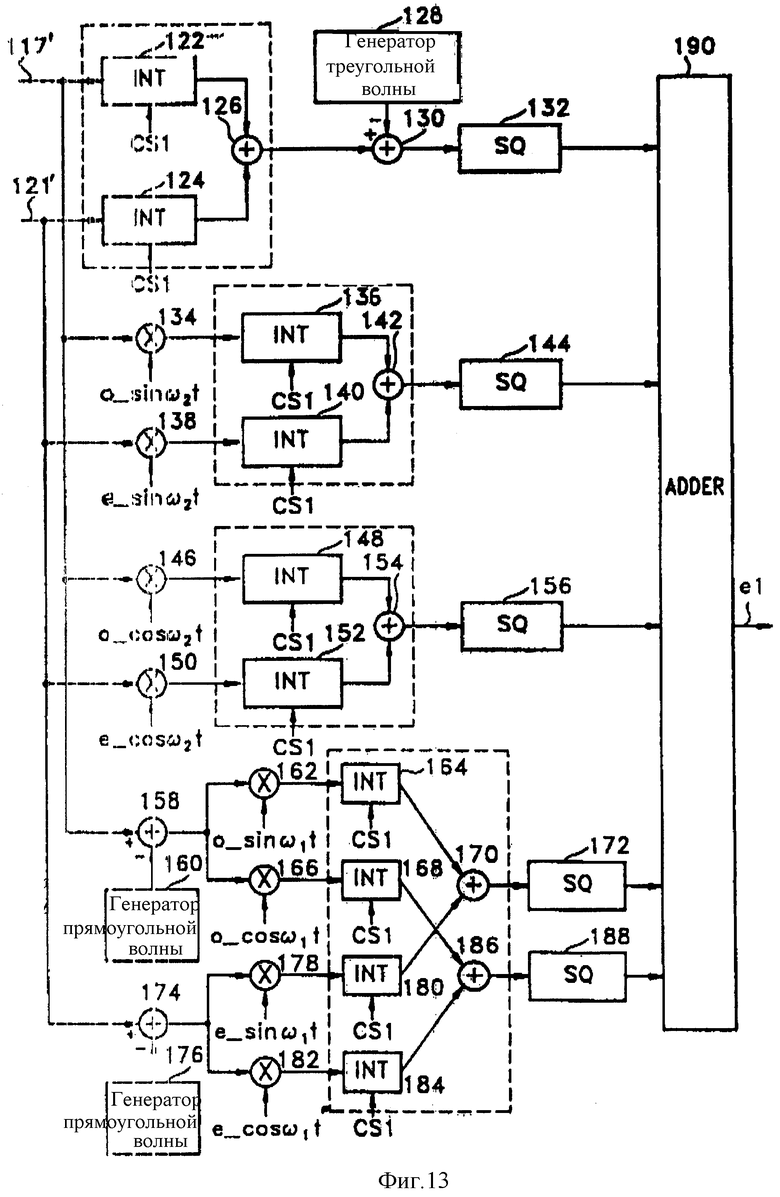

На фиг. 13 изображена подробная схема РАТН0 в одной из частей генератора управляющего сигнала, показанного на фиг. 12.

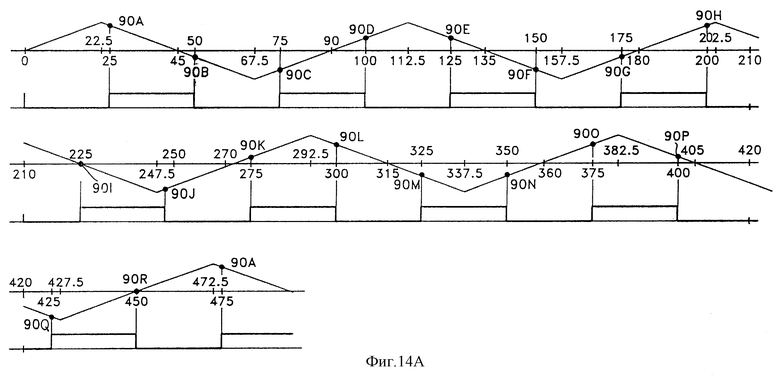

Фиг. 14A иллюстрирует форму сигнала, генерируемого генератором треугольной волны, показанным на фиг. 13.

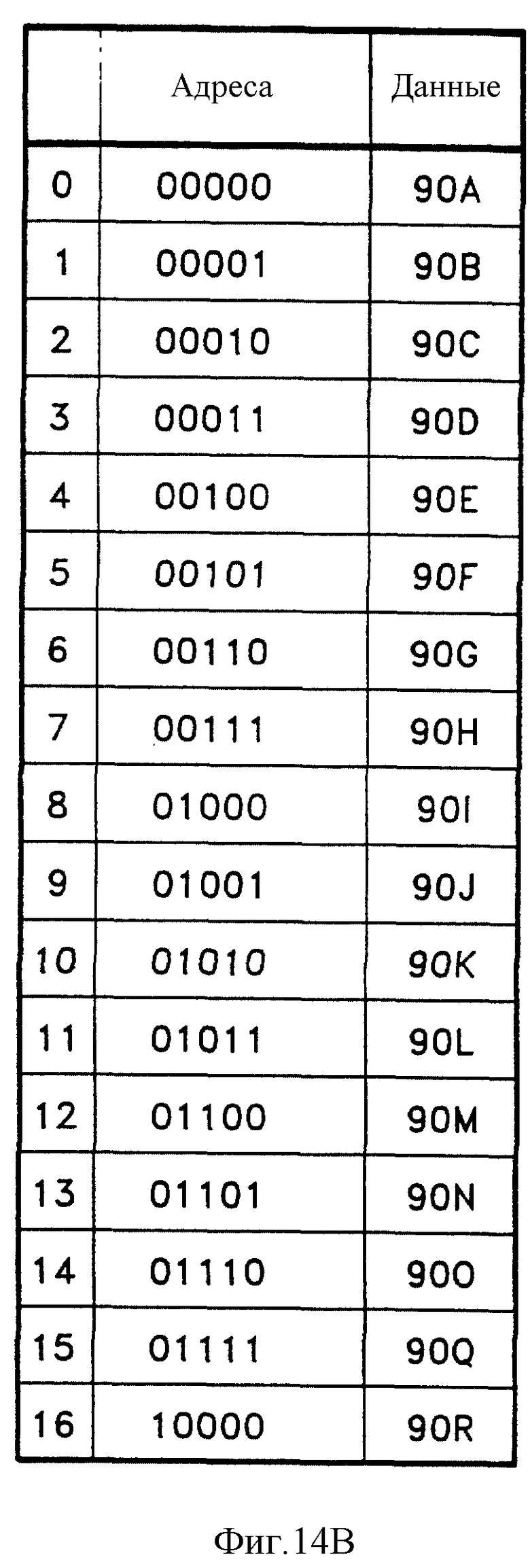

На фиг. 14B представлена таблица данных, хранящихся в ROM (ПЗУ) памяти, используемая в работе генератора треугольной волны.

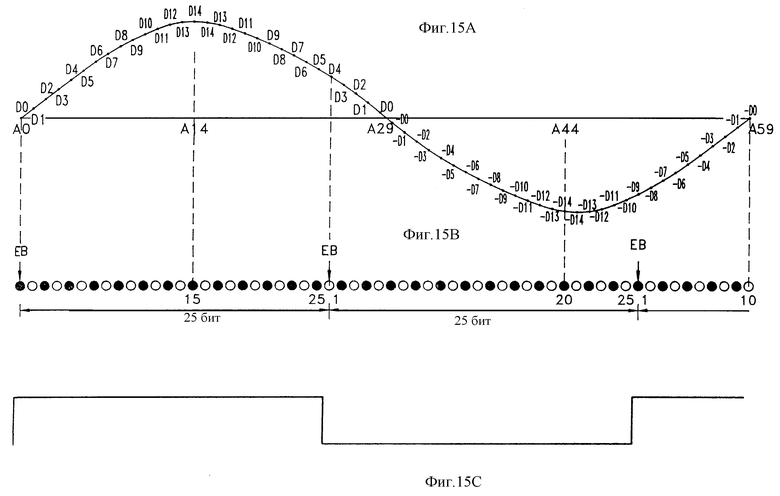

На фиг. 15A, 15B и 15C показаны синусоидальные и косинусоидальные сигналы, используемые в фиг. 13.

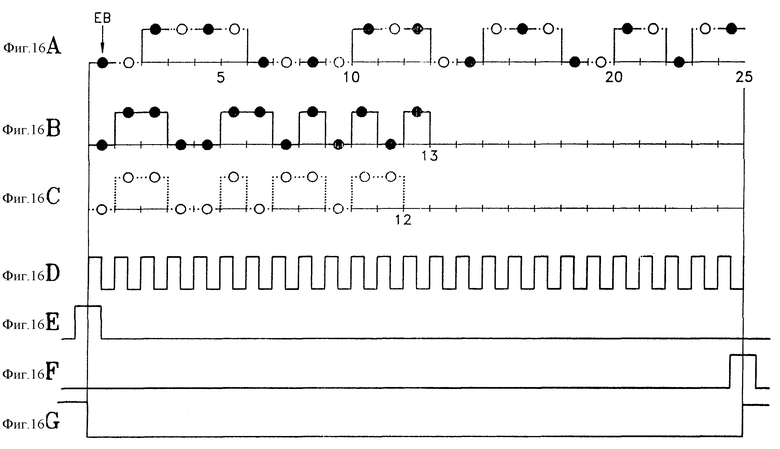

Фиг. 16A-16G иллюстрируют формы рабочих сигналов в блок-схеме, показанной на фиг. 6.

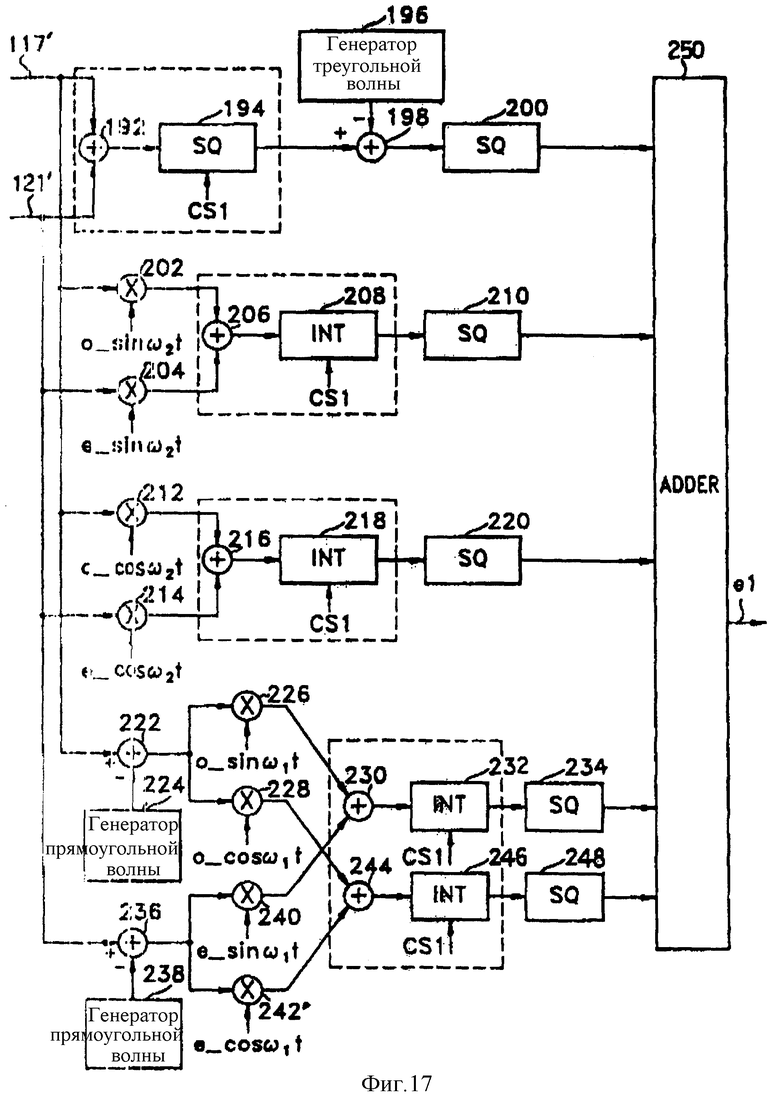

На фиг. 17 представлена подробная схема РАТН0 в одной из частей генератора управляющего сигнала, показанного на фиг. 6, который построен по другому варианту по сравнению с фиг. 13.

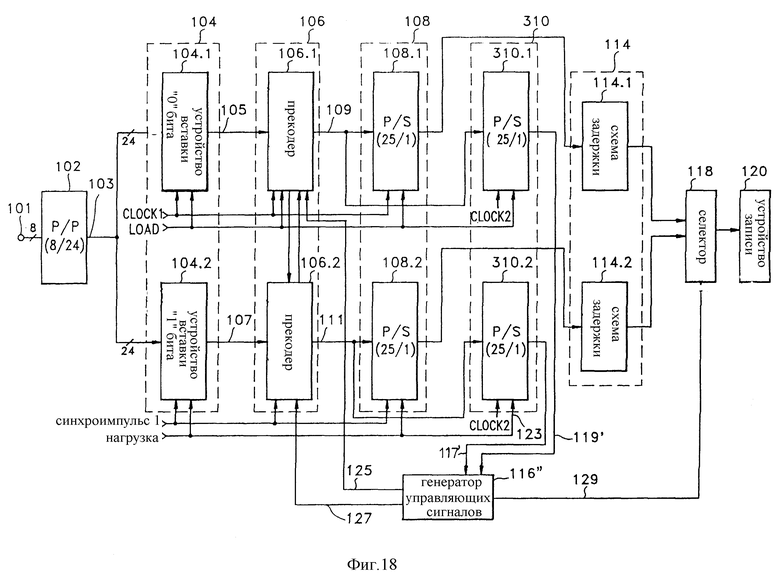

На фиг. 18 представлена блок-схема еще одного устройства для записи цифровых сигналов согласно изобретению.

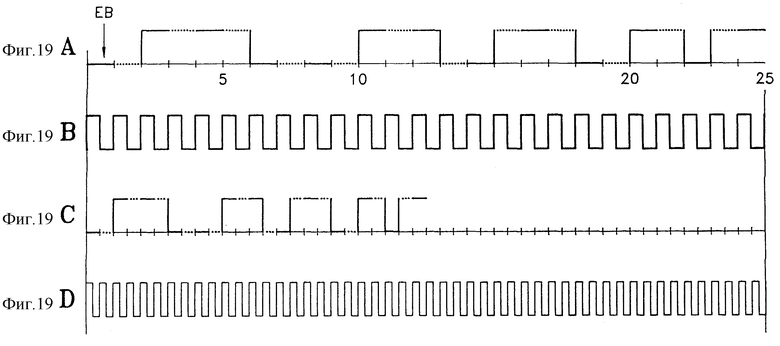

На фиг. 19A-19D показаны формы рабочих сигналов блоков схемы, показанной на фиг. 18.

В блок-схемах блоки с обозначением P/P являются параллельно-параллельными преобразователями для преобразования каждой следующей друг за другом группы данных в параллельном битовом формате в слова в параллельном битовом формате; блоки с обозначением P/S - это параллельно-последовательные преобразователи для преобразования данных в параллельном битовом формате в данные в последовательном битовом формате; блоки, обозначенные INT - цифровые интеграторы; блоки, обозначенные SQ - устройства цифрового квадратирования и блоки, обозначенные L - битовые защелки.

На фиг. 1 показано, каким образом с целью повышения удобства слежения головкой дорожки, устройство для записи цифровых сигналов с винтовым сканированием записывает последовательный поток канальных слов по трем образцам спектральных характеристик F0, F1 и F2 на следующих друг за другом параллельных дорожках на магнитном носителе записи. Условно дорожки здесь показаны более короткими и сильнее скошенными относительно направления движения ленты, чем в действительности. Пилот-сигналы появляются в спектре цифровых сигналов, записанных в последовательности F0, F1 и F2 на соответствующих дорожках магнитного носителя записи. Пилот-сигналы имеют провалы или пики на заданных частотах, которые вводятся в спектральную энергетическую характеристику (преобразование Фурье) сигналов, записанных на дорожках. При воспроизведении с любой из этих дорожек конкретного образца выясняются некоторые отклонения спектральной энергетической характеристики от ожидаемых значений. Такие отклонения приписываются перекрестным наводкам пилот-сигналов от предыдущей и последующей дорожек, на основании чего оценивается относительное приближение головки к предыдущей и последующей дорожке, из которого можно определить ошибку слежения головки. Показанная последовательность F0, F1 и F2 лишь пример; на практике количество образцов и последовательность записи могут отличаться от данного примера. В патенте США N 5142421 описаны некоторые из таких вариантов.

На фиг. 2A, 2B и 2C показаны частотные спектры последовательных битовых потоков канальных слов, характеризующие соответственно образцы F0, F1 и F2, показанные на фиг. 1. В частотном спектре образца F0 имеются провалы на частотах f1 и f2, где спектральная энергия относительно мала. В частотном спектре образца F1 имеется пилот-сигнал (пик) на частоте f1 = ω1/2π, где спектральная энергия относительно велика и провал на частоте f2 = ω2/2π, где спектральная энергия относительно мала. В частотном спектре образца F2 имеется провал на частоте f1, где спектральная энергия относительно мала, и пилот-сигнал (пик) на частоте f2, где спектральная энергия относительно велика.

Во время воспроизведения образца F0 эффект перекрестных помех между пилот-сигналами (пики f1 и f2) образцов F1> и F2 соседних дорожек используется для определения ошибки слежения. С одной стороны, если головка отклоняется от центра образца F0 к образцу F1, перекрестная помеха контрольного сигнала от образца F1 станет больше, чем от образца F2. В результате частотная компонента f1 сигнала воспроизведения станет больше, а частотная компонента сигнала f2 меньше. С другой стороны, если головка отклоняется от центра образца F0 к образцу F2, перекрестная помеха контрольного сигнала от образца F2 станет больше, чем помеха от образца F1. В результате в среднем частотная компонента f2 сигнала воспроизведения станет больше, а частотная компонента f2 меньше. Затем при воспроизведении образца F0 сравнение усредненной спектральной энергии сигнала воспроизведения на частотах f1 и f2 даст возможность определить отклонение слежения головки. Используя этот способ, можно обеспечить точное слежение посредством регулирования высоты элемента головки с помощью напряжения, подводимого к пьезоэлектрическому элементу, смонтированному на головке, либо путем регулирования скорости протяжки магнитного носителя записи (ленты).

На фиг. 3 представлена блок-схема устройства для записи цифровых сигналов, раскрытого в патенте США N 5142421, выданного 25 августа 1992 года "Device for recording a digital informational signal on a record carrier" и включенного в это описание в качестве ссылки. Структура и функционирование схемы будут описаны в соответствии с известным способом записи образцов F0, F1 и F2.

Как показано на фиг. 3, цифровые слова (8 бит параллельно) подаются на параллельно-последовательный преобразователь (P/S) 2 через входной порт 1. P/S преобразователь 2 преобразует, например, каждую следующую друг за другом группу из трех 8-битовых цифровых слов и одно 24-битовое последовательное информационное слово, выдаваемое через выходной порт 3 P/S преобразователя 2. Блок вставки 4 включает устройство вставки бита "0" 4.1 и устройство вставки бита "1" 4.2, каждое из которых в качестве входного сигнала имеет поток 24-битовых последовательных информационных слов, появляющихся на выходе 3 P/S преобразователя 2. Устройство вставки бита "0" 4.1 вставляет однобитовый цифровой префикс, состоящий из "0", перед старшим значащим разрядом (MSB) каждого 24-битового последовательного информационного слова для генерирования соответствующего 25-битового последовательного "положительного" информационного слова, выдаваемого на выходном порте 5 устройства вставки бита "0" 4.1. Устройство вставки бита "1" 4.2 вставляет однобитовый цифровой префикс, содержащий "1", перед старшим значащим битом (MSB) каждого 24-битового последовательного информационного слова для генерирования 25-битового последовательного "отрицательного" информационного слова, которое выдается на выходном порте 7 устройства вставки бита "1" 4.2.

Кодер 6 включает прекодер 6.1, преобразующий "положительные" информационные слова в соответствующие 25-битовые последовательные канальные слова, выдаваемые на шину 9. Кодер 6, кроме того, включает прекодер 6.2, преобразующий "отрицательные" информационные слова в соответствующие 25-битовые канальные слова, выдаваемые на шину 11. В остальной части этого описания и в формуле изобретения, приложенной к нему, для того чтобы различать канальные слова, выдаваемые прекодером 6.1, и канальные слова, выдаваемые прекодером 6.2, канальные слова на выходе прекодера 6.1 называются "положительными" информационными канальными словами, а канальные слова на выходе прекодера 6.2 называются "отрицательными" информационными канальными словами. Если прекодеры 6.1 и 6.2 являются 2Т-прекодерами, однобитовый код префикса заставляет их генерировать два 25-битовых последовательных канальных слова, в которых соответствующие четные биты одинаковы, а соответствующие нечетные биты являются двоичным дополнением. 2Т-прекодер включает двухвходовый логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и двухступенчатый сдвиговый регистр, обеспечивающий интегрирующую обратную связь с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ к первому входному соединению. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ получает входной сигнал прекодера на свой второй вход, выдает выходной сигнал прекодера на свою выходную шину и обычно принимает на своем первом входе выходной сигнал прекодера, с задержкой 2Т, которая обеспечивается прохождением через двухступенчатый сдвиговый регистр. Интервал Т - это интервал дискретизации входного сигнала прекодера и интервал между тактовыми сдвигами битов в двухступенчатом сдвиговом регистре. Обратная связь элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, обеспечиваемая двухступенчатым сдвиговым регистром, называется "интегрирующей обратной связью" или просто "интегрирующей связью".

Прекодер 6.1 выдает 25-битовые последовательные "положительные" информационные канальные слова на шину 9 в качестве своего выходного сигнала, а прекодер 6.2 выдает 25-битовые последовательные "отрицательные" информационные канальные слова на шину 11 в качестве своего выходного сигнала. На основе этих 25-битовых последовательных канальных слов, подаваемых параллельно от прекодеров 6.1 и 6.2, генератор контрольных сигналов 10 сравнивает соответствующие спектральные энергетические характеристики каждого слова с заданными спектральными энергетическими характеристиками для дорожки, которая должна быть записана цифровым видеомагнитофоном 14, чтобы определить, какое канальное слово меньше всего отклоняется от заданной спектральной характеристики. Генератор управляющих сигналов 10 генерирует управляющий сигнал CS, указывающий, какое из канальных слов, поступающих от прекодеров 6.1 и 6.2, меньше всего отклоняется от заданной спектральной характеристики и, следовательно, должно быть выбрано для записи. Управляющий сигнал CS подается через шину 17 к управляющему порту селектора 12, который отбирает выходной сигнал от одного из прекодеров 6.1 и 6.2 (с временной задержкой, обеспечиваемой временным компенсатором 8), который меньше всего отклоняется от заданной спектральной характеристики, для его использования в цифровом видеомагнитофоне 14. Схемы задержки 8.1 и 8.2 временного компенсатора 8 необходимы для компенсации времени, которое требуется генератору контрольных сигналов 10 для генерирования сигнала CS с целью его использования в селекторе 12. Управляющий сигнал CS подается также через шину 17 на соответствующие управляющие порты прекодеров 6.1 и 6.2 для управления передачей содержимого сдвигового регистра в одном из прекодеров 6.1 или 6.2, выход которого отбирается для записи в сдвиговый регистр в другом прекодере для обеспечения непрерывности кодирования.

Селектор 12 через шину 13 получает "положительный" информационный выходной сигнал прекодера 6.1, задержанный схемой задержки 8.1, а через шину 15 "отрицательный" информационный выходной сигнал прекодера 6.2, задержанный схемой задержки 8.2. В ответ на контрольный сигнал CS селектор 12 через шину 19 выдает выбранный выходной сигнал с задержкой от прекодера 6.1 или 6.2 на цифровой видеомагнитофон 14, в качестве входного сигнала для записи. Для того чтобы битовая модуляция могла бы записываться цифровым видеомагнитофоном 14 при постоянной битовой частоте, необходима частотная буферизация. Схемы задержки 8.1 и 8.2 могут обеспечивать фиксированные задержки с частотной буферизацией, обеспечиваемой после селектора 12, или, как вариант, схемы задержки 8.1 и 8.2 могут представлять собой буферные запоминающие устройства F1F0 ("первый поступил - первый выводится"), которые обеспечивают необходимую буферизацию в дополнение к всегда осуществляемой задержке, достаточной для завершения расчетов, необходимых для принятия решения о том, какой из выходных сигналов прекодеров 6.1 и 6.2 следует записать.

На фиг. 4 представлена подробная схема генератора управляющего сигнала для устройства записи цифровых сигналов (фиг. 3), который предназначен для генерирования последовательного потока канальных слов со спектральными характеристиками, показанными на фиг. 5. По сравнению со спектром образца F1, показанным на фиг. 2В, в спектре, показанном на фиг. 5, с каждой стороны f1 имеется спад. Эти спады указывают на то, что энергия шума спектра уменьшается при отклонении от частоты пилот-сигнала f1, что приводит к возрастанию отношения сигнал/шум, используемого для обнаружения пилот-сигнала на частоте f1.

Усовершенствованный генератор управляющего сигнала по фиг. 4 отличается от аналогичного генератора, описанного Kahlman и др., в том, что он содержит преобразователи кодов в арифметические выражения 10.1 и 10.2. Преобразователь код - арифметическое выражение 10.1 преобразует единицы и нули "положительного" информационного выходного сигнала прекодера 6.1 в арифметические выражения I-NRZI-модуляции, которые принимают то отрицательные, то положительные арифметические значения одной и той же амплитуды и не сопровождаются постоянной составляющей. Преобразователь "код - арифметическое выражение" 10.2 аналогичен по своей структуре преобразователю 10.1. Преобразователь "код - арифметическое выражение" 10.2 преобразует единицы и нули "отрицательного" информационного выходного сигнала прекодера 6.2 в арифметические выражения I-NRZI-модуляции, которые принимают то отрицательные, то положительные арифметические значения с одной и той же амплитудой и не сопровождаются постоянной составляющей. Например, каждый из преобразователей 10.1 и 10.2 может использовать подаваемые на него единицы и нули, как изменяющийся знаковый бит перед неизменяемой единицей, так что модуляция будет описываться арифметическими членами в двоичном дополнительном коде.

Таблица синусов/косинусов, хранящаяся в ROM (ПЗУ) памяти (не показана), генерирует комплексную несущую на частоте f1, с угловой частотой ω1, состоящую из sinω1t и cosω1t компонент. Другая таблица синусов/косинусов, хранящаяся в ROM (не показана), генерирует комплексную несущую на частоте f2, с угловой частотой ω2, состоящую из sinω2t и cosω2t компонент. Генератор треугольной волны 18 генерирует сигнал треугольной формы, соответствующий итоговому цифровому значению заданной частоты (f1) последовательного потока канальных слов, а генератор прямоугольных импульсов 38 генерирует прямоугольные импульсы с частотой f1. Генератор треугольных сигналов 18 и генератор прямоугольных сигналов 38 также могут быть обеспечены справочными таблицами, хранящимися в ROM. Генерирование всех системных функций в ROM упрощает обработку канальных слов при порядке следования бит, отличающемся от обычного.

Схема фильтрации РАТН0 определяет, на сколько спектральное распределение энергии I-NRZI-модуляции при ее генерировании на основе "положительного" информационного канального слова от прекодера 6.1, отклоняется от желаемого спектрального распределения энергии для дорожки, которая записывается с помощью F1 образца, имеющего пик на частоте f1, спад с каждой стороны от f1 и провал на частоте f2. Схема суммирования со взвешиванием 52.1 вычисляет в сочетании с соответствующим взвешиванием расчетное отклонение от желаемого провала на нулевой частоте и от желаемого пика на частоте f1, получаемое от схемы квадратирования 22.1, вместе с расчетными отклонениями от других желаемых характеристик. Расчетные отклонения от провала на частоте f2, полученные для ортогональных фаз частоты f2 с помощью схем квадратирования 28.1 и 34.1, взвешиваются подобным же образом друг по отношению к другу в схеме суммирования со взвешиванием 52.1. Расчетные отклонения от спада с любой стороны от частоты f1, получаемые для ортогональных фаз частоты f1 с помощью схем квадратирования 44.1 и 50.1, взвешиваются друг по отношению к другу подобным же образом в схеме суммирования со взвешиванием 52.1. Эффективное взвешивание входов к схеме суммирования со взвешиванием 52.1 от схем квадратирования 28.1 и 34.1 весьма сопоставимо со взвешиванием входа в схему суммирования со взвешиванием 52.1 от схемы квадратирования 22.1, поскольку отсутствие правильной частоты пилот-сигнала f1 скорее допустимо, чем наличие неправильной частоты пилот-сигнала f2 благодаря схеме коррекции слежения, используемой во время воспроизведения. Эффективное взвешивание входов в схему суммирования со взвешиванием 52.1 от схем квадратирования 44.1 и 50.1 слабо сопоставимо на взвешивание входа в схему суммирования со взвешиванием 52.1 от схемы квадратирования 22.1. Схема фильтрации РАТН0 выдает первый сигнал ошибки e1 в виде взвешенного суммарного выходного сигнала от схемы суммирования со взвешиванием 52.1

Расчет в РАТН0 системы величин, характеризующих, насколько спектральное распределение энергии I-NRZI-модуляции при ее генерировании на основе "положительного" информационного канального слова от прекодера 6.1 отклоняется от желаемого провала на нулевой частоте и желаемого пика на частоте f1, выполняется следующим образом. Схема интегрирования 16.1 получает текущее "положительное" информационное канальное слово от прекодера 6.1, преобразованное к арифметическому виду с помощью преобразователя код - арифметическое выражение 10.1, и суммирует его с ранее записанным значением. Вычитатель 20.1 вычитает выходной сигнал генератора треугольной волны 18 из выходного сигнала схемы интегрирования 16.1, а схема квадратирования 22.1 умножает результирующую разность саму на себя; а результирующий квадрат подается в схему суммирования со взвешиванием 52.1 для получения компоненты первого сигнала ошибки e1. Генератор треугольной волны 18 и вычитатель 20.1 образуют схему для обнаружения любого отклонения от заданной цифровой суммы, необходимого для поддержания желаемого пилот-сигнала, причем значение цифровой суммы выдает схема интегрирования 16.1. Схема квадратирования 22.1 рассчитывает энергию этого отклонения.

Расчет в РАТН0 системы величин, характеризующих, насколько спектральное распределение энергии I-NRZI-модуляции при ее генерировании на основе "положительного" информационного канального слова от прекодера 6.1 отклоняется от желаемого провала на частоте f2, выполняется следующим образом. Умножитель 24.1 умножает выходной сигнал прекодера 6.1 на синусоидальную системную функцию sinω2t частоты f2; схема интегрирования 26.1 интегрирует результат действия умножителя 24.1, а схема квадратирования 28.1 возводит в квадрат результат интегрирования, полученный от схемы интегрирования 26.1, для использования в схеме суммирования со взвешиванием 52.1. Умножитель 30.1 умножает выходной сигнал прекодера 6.1 на косинусоидальную системную функцию cosω2t частоты f2, схема интегрирования 32.1 интегрирует результат, полученный от умножителя 30.1, а схема квадратирования 34.1 возводит в квадрат результат интегрирования, полученный от схемы интегрирования 32.1, для использования в схеме суммирования со взвешиванием 52.1. (Выражение "системная функция" используется в цифровой электронике для обозначения аналоговой функции, которая описывается в дискретизированном виде с помощью цифровых выборочных значений).

Расчет в РАТН0 системы величин, характеризующих, насколько спектральное распределение энергии I-NRZI-модуляции при ее генерировании на основе "положительного" информационного канального слова от прекодера 6.1 отклоняется от желаемого спада с любой стороны пика на частоте f1, выполняется следующим образом. Вычитатель 36.1 вычитает выходной прямоугольный сигнал частоты f1, подаваемый генератором прямоугольных импульсов 38 из выходного сигнала прекодера 6. 1. Генератор прямоугольных импульсов 38 и вычитатель 36.1 образуют схему для обнаружения любого отклонения от заданной прямоугольной формы "положительного" информационного последовательного битового канального слова, которое выдает прекодер 6.1 в виде, преобразованном к арифметическому посредством преобразователя код - арифметическое выражение 10.1. Умножитель 40.1 умножает выходной сигнал разности вычитателя 36.1 на синусоидальную системную функцию sinω1t частоты f1; схема интегрирования 42.1 интегрирует произведение, полученное от умножителя 40.1, а схема квадратирования 44.1 возводит в квадрат результаты интегрирования от схемы интегрирования 42.1 для использования в схеме суммирования со взвешиванием 52.1. Умножитель 46.1 умножает выходной сигнал разности вычитателя 36.1 на косинусоидальную системную функцию cosω1t частоты f1, схема интегрирования 48.1 интегрирует результат, полученный от множителя 46.1, а схема квадратирования 50.1 возводит в квадрат результаты интегрирования от схемы интегрирования 48.1 для использования в схеме суммирования со взвешиванием 52.1.

Схема фильтрации РАТН1 определяет величину, характеризующую, насколько спектральное распределение энергии I-NRZI-модуляции при ее генерировании на основе "отрицательного" информационного канального слова от прекодера 6.2 отклоняется от желаемого спектрального распределения энергии для дорожки, записанной с помощью образца F1, имеющего пик на частоте f1, спад по обе стороны от частоты f1 и провал на частоте f2. Схема суммирования со взвешиванием 52.2 в схеме фильтрации РАТН1 комбинирует с соответствующим взвешиванием расчетные отклонения от желаемого провала на нулевой частоте и желаемого пика на частоте f1, поступающие от схемы квадратирования 22.2, вместе с расчетными отклонениями от других желаемых характеристик, поступающими от схем квадратирования 28.2, 34.2, 44.2 и 50.2. Схема суммирования со взвешиванием 52.2 выдает в качестве суммарного выходного сигнала второй сигнал ошибки e2. Компаратор 54 сравнивает сигналы ошибок e1 и e2 для генерирования контрольного сигнала CS, подаваемого на контрольный порт выбора селектора 12, который выбирает канальное слово, имеющее наименьшее значение сигнала ошибки.

Расчет в РАТН1 системы величин, характеризующих, насколько спектральное распределение энергии I-NRZI-модуляции при ее генерировании на основе "отрицательного" информационного канального слова от прекодера 6.2 отклоняется от желаемого провала на нулевой частоте и желаемого пика на частоте f1, выполняется следующим образом. Схема интегрирования 16.2 получает текущее "отрицательное" информационное канальное слово от прекодера 6.2, преобразованное к арифметическому виду посредством преобразователя код - арифметическое выражение 10.2 и складывает его с накопленным ранее значением. Вычитатель 20.2 вычитает выходной сигнал генератора треугольных импульсов 18 из выходного сигнала схемы интегрирования 16.2, схема квадратирования 22.2 умножает полученную разность саму на себя, а полученный квадрат подается на схему суммирования со взвешиванием 52.2 для получения компоненты второго сигнала ошибки e2. Генератор треугольных импульсов 18 и вычитатель 20.2 образуют схему для обнаружения любого отклонения от заданной суммы, необходимого для поддержания желаемого пилот-сигнала, причем цифровое значение суммы выдается схемой интегрирования 16.2. Схема квадратирования 22.2 рассчитывает энергию этого отклонения.

Расчет в РАТН1 системы величин, характеризующих, насколько спектральное распределение энергии I-NRZI-модуляции при ее генерировании на основе "отрицательного" информационного канального слова от прекодера 6.2 отклоняется от желаемого провала на частоте f2, выполняется следующим образом. Умножитель 24.2 умножает выходной сигнал прекодера 6.2 на синусоидальную системную функцию sinω2t частоты f2; схема интегрирования 26.2 интегрирует результат действия умножителя 24.1, а схема квадратирования 28.2 возводит в квадрат результат интегрирования, полученный от схемы интегрирования 26.2, для использования в схеме суммирования со взвешиванием 52.2. Умножитель 30.2 умножает выходной сигнал прекодера 6.2 на косинусоидальную системную функцию cosω2t частоты f2, схема интегрирования 32.2 интегрирует результат, полученный от умножителя 30.2, а схема квадратирования 34.2 возводит в квадрат результат интегрирования, полученный от схемы интегрирования 32.2, для использования в схеме суммирования со взвешиванием 52.1.

Расчет в РАТН1 системы величин, характеризующих, насколько спектральное распределение энергии I-NRZI-модуляции при ее генерировании на основе "отрицательного" информационного канального слова от прекодера 6.2 отклоняется от желаемого спада по любую сторону от пика на частоте f1, выполняется следующим образом. Вычитатель 36.2 вычитает прямоугольный сигнал с частотой f1, подаваемый генератором прямоугольных импульсов 38, из выходного сигнала прекодера 6.2. Генератор прямоугольных импульсов 38 и вычитатель 36.2 обеспечивают обнаружение любого отклонения от заданного прямоугольного сигнала "отрицательного" информационного последовательного битового канального слова, которое прекодер 6.2 выдает в виде, преобразованном к арифметическому, преобразователем код - арифметическое выражение 10.2. Умножитель 40.2 умножает выходной сигнал разности от вычитателя 36.2 на синусоидальную системную функцию sinω1t частоты f1, схема интегрирования 42.2 интегрирует результат, полученный от умножителя 40.2, а схема квадратирования 44.2 возводит в квадрат результаты интегрирования, получаемые от схемы интегрирования 42.2, для использования в схеме суммирования со взвешиванием 52.2. Умножитель 46.2 умножает выходной сигнал разности от вычитателя 36.2 на косинусоидальную системную функцию cosω1t частоты f1, схема интегрирования. 48.2 интегрирует результат от умножителя 46.2, а схема квадратирования 50.2 возводит в квадрат результаты интегрирования, полученные от схемы интегрирования 48.2, для использования в схеме суммирования со взвешиванием 52.2.

Здесь была описана работа генератора контрольных сигналов 10 при генерировании образца F1. При генерировании образца F2 работа генератора контрольных сигналов 10 модифицируется посредством перестановки f1 и f2, и тем самым перестановки 1 и 2. При генерировании образца F0 работа генератора контрольных сигналов 10 модифицируется посредством блокировки генератора треугольных импульсов 18 и генератора прямоугольных импульсов 38. Независимо от того, какой из образцов F0, F1 и F2 генерируется, должны быть выполнены некоторые процедуры повторной инициализации вслед за принятым решением, так чтобы выбрать "положительное" информационное слово, обеспечиваемое прекодером 6.1, либо выбрать "отрицательное" информационное слово, обеспечиваемое прекодером 6.2, для определения I-NRZI-модуляции, подлежащей записи. Эти процедуры повторной инициализации обеспечивают непрерывность кодирования и дают возможность генератору контрольных сигналов создать основу для принятия решения о том, какое из следующей пары канальных слов должно быть выбрано для записи.

В последнем случае, если канальное слово, подлежащее записи следующим, уже определено, содержимое схем интегрирования 16.1, 26.1, 32.1, 42.1 и 48.1 или содержимое схем интегрирования 16.2, 26.2, 32.2, 42.2 и 48.2 должно быть изменено. Если вновь выбранное канальное слово несет информацию "отрицательного" типа, содержимое схем интегрирования 16.1, 26.1, 32.1, 42.1 и 48.1 приводится в соответствие с содержимым схем интегрирования 16.2, 26.2, 32.2, 42.2 и 48.2 соответственно. Если вновь выбранное канальное слово несет информацию "положительного" типа, содержимое схем интегрирования 16.2, 26.2, 32.2, 42.2 и 48.2 приводится в соответствие с содержимым схем интегрирования 16.1, 26.1, 32.1, 42.1 и 48.1 соответственно.

Как было отмечено ранее, если канальное слово, которое должно быть записано следующим, уже определено, закодированная информация от цепи "интегрирующей обратной связи" одного из прекодеров 6.1 или 6.2, подающих канальное слово, выбранное для записи, должна быть передана в цепь "интегрирующей обратной связи" другого прекодера. Если канальное слово, выбранное для записи в качестве следующего, было получено от прекодера 6.1, содержимое сдвигового регистра в цепи интегрирующей обратной связи его элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подается на соответствующие позиции в сдвиговом регистре, находящемся в цепи интегрирующей обратной связи элемента ИСКЛЮЧАЮЩЕЕ ИЛИ в прекодере 6.2. С другой стороны, если канальное слово, выбранное для записи в качестве следующего, было получено от прекодера 6.2, содержимое сдвигового регистра в цепи интегрирующей обратной связи его элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подается на соответствующие позиции в сдвиговом регистре, находящемся в цепи интегрирующей обратной связи элемента ИСКЛЮЧАЮЩЕЕ ИЛИ в прекодере 6.1.

Однако на практике в известном устройстве для записи цифровых сигналов, описанном в патенте США N 5142421, получается существенная временная задержка, прежде чем такая передача может быть завершена, причем эта задержка возрастает в цифровых умножителях, схемах интегрирования и схемах квадратирования в генераторе контрольных сигналов 10. Эта задержка вызывает необходимость иметь периодически перезаписываемую буферную память после кодера 6, что может быть обеспечено временным компенсатором 8, и периодически считываемую буферную память перед кодером 6, что может быть обеспечено параллельно-последовательным преобразователем 2. Практическая реализация такой периодически считываемой и перезаписываемой буферной памяти затруднена в связи с проблемой синхронизации, но этого можно избежать, если согласно данному изобретению выполнять предварительное кодирование на основе слов с параллельными битами.

Как показано на фиг. 6, входной порт 101 для приема последовательно подаваемых 8-битовых параллельных слов подсоединен к входному порту параллельно-параллельного преобразователя P/P 102. P/P преобразователь 102 преобразует каждую поступающую друг за другом группу из трех последовательно идущих 8-битовых параллельных слов, подаваемых на его входной порт, в три идущих параллельно 8-битовых параллельных слова, то есть, 24-битовое информационное слово и выдает преобразованное слово в параллельном битовом формате с выходного порта 103.

Блок вставки сигнала 104 приставляет однобитовый цифровой префикс к каждому 24-битовому информационному слову, выдаваемому в параллельном битовом формате от выходного порта 103 P/P преобразователя 102. Блок вставки сигнала включает устройство вставки бита "0" 104.1 для прикрепления "0" бита в виде префикса к 24-битовому информационному слову и устройство вставки бита "1" 104.2 для прикрепления "1" бита в виде префикса к 24-битовому информационному слову.

Полученные таким образом 25-битовые информационные слова подаются от выходных портов 105 и 107 на прекодеры 106.1 и 106.2 соответственно блока кодирования 106. В качестве прекодеров 106.1 и 106.2 предпочтительно использовать 2Т-прекодеры для преобразования 25-битового информационного слова в 25-битовое канальное слово. Эти 2Т-прекодеры годятся для обработки слов в параллельном битовом формате и по своей структуре отличаются от прекодеров, описанных в патенте США N 5142421, которые годятся для обработки слов в последовательном битовом формате. Конструкция этих прекодеров 106.1 и 106.2, каждый из которых включает 25 логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, будет описана подробно далее со ссылками на фиг. 8 и 10, в которых блок вставки сигнала 104 включен в устройство кодирования 106. Предварительное кодирование кроме того требует, чтобы биты, которые были записаны позже, были определены после бит, которые были записаны ранее. Во время предварительного кодирования требуется также время для сквозного интегрирования бит инициализации и следующих друг за другом бит, используемых для формирования каждого канального слова. Однако время, необходимое во время предварительного кодирования для сквозного интегрирования этих бит, составляет лишь часть интервала канального слова.

Входные порты параллельно-последовательных (P/S) преобразователей 18.1 и 108.2 первого преобразователя сигналов 108 подсоединены соответственно к выходным портам 109 и 111 прекодеров 106.1 и 106.2, а выходные порты преобразователей 108.1 и 108.2 соединены соответственно с входными портами схем задержки 114.1 и 114.2 временного компенсатора 114. Каждый преобразователь 108.1 и 108.2 преобразует подаваемое на него каждое 25-битовое параллельное канальное слово в 25-битовое последовательное канальное слово, выдаваемое с битовой частотой, связанное с I-NRZI-модуляцией, используемой при записи на магнитный носитель.

P/S преобразователи 110.1 и 110.2 второго преобразователя сигналов 110 преобразуют к последовательному битовому формату битовые позиции с нечетными порядковыми номерами каждого канального слова (здесь и далее называемого "нечетным канальным" словом) из 25-битовых канальных слов, выдаваемых параллельно из прекодеров 106.1 и 106.2. P/S преобразователи 112.1 и 112.2 третьего преобразователя сигналов 112 преобразуют к последовательному битовому формату битовые позиции с четными порядковыми номерами каждого канального слова (здесь и далее называемого "четным" канальным словом) из 25-битовых канальных слов, выдаваемых параллельно из прекодеров 106.1 и 106.2 соответственно.

Фиксированные задержки, создаваемые схемами задержки 114.1 и 114.2 временного компенсатора 114, компенсируют время, которое требуется генератору контрольных сигналов 116 для генерирования контрольного сигнала, указывающего селектору 118, какое из канальных слов, генерируемых соответственно прекодерами 106.1 и 106.2 и задерживаемых схемами задержки 114.1 и 114.2, выбрать для записывающего устройства 120. Генератор контрольных сигналов 116 генерирует первый, второй и третий контрольные сигналы CS1, CS2 и CS3 на основе сигналов канальных слов, подаваемых соответственно с выходных портов 117, 119, 121 и 123 P/S преобразователей 110.1, 110.2, 112.1 и 112.2. Схема в генераторе контрольных сигналов 116, который решает, какое из канальных слов, генерированных прекодерами 106.1 и 106.2, должно быть записано, обрабатывает нечетное канальное слово, поступающее от P/S преобразователя 110.1, и четное канальное слово, поступающее от P/S преобразователя 112.1, параллельно, и эта схема также обрабатывает нечетное канальное слово, поступающее от P/S преобразователя 110.2, и четное канальное слово, поступающее параллельно от P/S преобразователя 112.1. Эти параллельные процедуры

обработки вдвое сокращают время, необходимое для завершения процедуры принятия решения, расчеты по которой синхронизируются при той же битовой частоте, что и I-NRZI-сигнал, который должен быть записан. Соответственно расчеты могут быть выполнены за время, чуть большее половины временного интервала между тактами последовательного канального слова, которые появляются с частотой, равной одной двадцать пятой от битовой частоты I-NRZI-сигнала, который должен быть записан. Время для этих расчетов вместе с временем для сквозного интегрирования в прекодерах 106.1 и 106.2 кодирующего блока 106 существенно меньше, чем временной интервал между тактами канальных слов, что дает избыток времени для повторной инициализации интеграторов в генераторе контрольных сигналов 116 и позволяет установить инициализацию для сквозного интегрирования, что должно иметь место, когда следующее последовательное слово синхронизируется в прекодерах 106.1 и 106.2. Первый и второй контрольные сигналы CS1 и CS2, выдаваемые генератором контрольных сигналов 116 через порты 125 и 127, подаются на соответствующие контрольные порты прекодеров 106.1 и 106.2. Третий контрольный сигнал CS3, выдаваемый генератором контрольных сигналов 116 через выходной порт 127, подается на управляющий порт селектора 118.

В соответствии с третьим контрольным сигналом CS3 селектор 118 выбирает величину, ближайшую к заданной частотной характеристике, между 25-битовым последовательным "положительным" информационным канальным словом, выдаваемым P/S преобразователем 108.1 и 25-битовым последовательным "нечетным" информационным канальным словом, выдаваемым P/S преобразователем 108.2, и передает выбранное слово в блок записи 120.

В устройстве для записи цифровых сигналов на фиг. 6 могут быть сделаны упрощения. Соответствующие битовые позиции четных канальных слов, выдаваемых параллельно прекодерами 106.1 и 106.2, идентичны, если это прекодеры типа 2Т и если используются однобитовые префиксы, так что можно обойтись одним P/S преобразователем 112.1, 112.2, а сигнал, выдаваемый из его выходного порта генератору контрольных сигналов 116, может подаваться от выходного порта оставшегося преобразователя 112.1 или 112.2. Если прекодеры 106.1 и 106.2 являются прекодерами типа 2Т и используются однобитовые префиксы, то соответствующие битовые позиции нечетных канальных слов, подающихся параллельно, комплементарны друг относительно другу, так что можно обойтись одним из двух P/S конвертеров 110.1 и 110.2, и сигнал, поступающий от его выходного порта к генератору контрольных сигналов 116, может вместо этого быть получен посредством битового дополнения сигнала от выходного порта оставшегося преобразователя 110.1 или 110.2.

На фиг. 7 представлена блок-схема другого варианта устройства для записи цифровых сигналов согласно настоящему изобретению. На фиг. 7 одни и те же номера обозначают одни и те же элементы, что и в устройстве на фиг. 6. Соответственно аналогичные структуры и принципы действия не будут снова описываться. На фиг. 7 показано, что входные порты 117', 119', 121' и 123' первого преобразователя сигналов 108 непосредственно подсоединены к входным портам модифицированного генератора контрольных сигналов 116', так что из схемы исключены второй и третий преобразователи сигналов 110 и 112 по фиг. 6.

При работе схемы на фиг. 7 в ответ на 25-битовое параллельное "положительное" информационное канальное слово, получаемое от прекодера 106.1, P/S преобразователь 108.3 в первом преобразователе сигналов 108 передает с первого по тринадцатый биты канального слова (здесь и далее называемые "начальная битовая группа") через выходной порт 117' в генератор контрольных сигналов 116'. В то же самое время, когда P/S преобразователь 108.3 выдает с первого по двенадцатый из этих бит, он выдает также с четырнадцатого по двадцать пятый биты канального слова (здесь и далее называемые "конечной битовой группой") через выходной порт 121' в генератор контрольных сигналов 116'.

В ответ на 25-битовое параллельное "отрицательное" информационное канальное слово, поступающее от прекодера 106.2, P/S преобразователь 108.4 в первом преобразователе сигналов 108 выдает с первого по тридцатый биты канального слова (здесь и далее называемые "начальная битовая группа") через выходной порт 119' в генератор контрольных сигналов 116'. В то же самое время P/S преобразователь 108.4 подает также с четырнадцатого по двадцать пятый биты канального слова (здесь и далее называемые "конечная битовая группа") через выходной порт 123' в генератор контрольных сигналов 116'.

Модифицированный генератор контрольных сигналов 116' выполняет те же самые общие расчеты, что и генератор контрольных сигналов 116, но в несколько другом порядке, для чего требуется модификация схемы фильтрации на фиг. 4 в отношении генератора треугольных импульсов 18, генератора прямоугольных импульсов 38 и генераторов синусоидального и косинусоидального сигналов. Эти модификации достаточно просто выполняются методами, известными специалистам по разработке цифровых систем. Это особенно просто сделать, если в генераторах используется память ROM, поскольку порядок последовательного считывания выборочных значений каждой системной функции легко изменить.

На фиг. 8 представлена подробная схема устройства вставки "0" бита 104.1, прекодера 106.1 и P/S преобразователей 108.1, 110.1 и 112.1, каждый из которых показан на фиг. 6. Обратимся к фиг. 8, где устройство вставки бита "0" 104.1 выполнено на 25 защелках с 104.a по 104.y. "0" бит подается на защелку 104.a, в которой хранится старший значащий бит, в соответствии с системным синхросигналом (CLOCK 1) и командным сигналом загрузки LOAD. Остальные защелки с 104.b по 104.y принимают 24-битовое информационное слово, подаваемое параллельно с выходного порта 103 P/P преобразователя 102.

На фиг. 9 представлена подробная схема устройства вставки "0" бита 104.1, каждая из 25 защелок выполнена из одного D-триггера, двух логических элементов И и одного элемента ИЛИ. При работе блока вставки 104.1, если командный сигнал LOAD имеет высокий уровень, "0" бит, подаваемый на информационный вход защелки 104.a и 24-битовое информационное слово, поступающее от P/P преобразователя 102, фиксируются и снимаются с Q выходов соответствующих D-триггеров. Если командный сигнал LOAD имеет низкий уровень, защелки сохраняют выходной сигнал каждого D-триггера.

Первые входные порты логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с 106.a по 106. y прекодера 106.1, показанные на фиг. 8, подсоединены к соответствующим выходным портам защелок с 104.a по 104.y устройства вставки "0" бита 104.1. Вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 106.a и 106.b соединены соответствующими выходами заделок 106.3 и 106.4. Соответствующие выходы логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с 106. a по 106.w соединены со вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с 106.e по 106.y. Выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 106.x и 106.y подсоединены к соответствующим входам защелок 106.3 и 106.4.

Работа прекодера 106 будет объяснена ниже.

Второй младший значащий бит из предшествующего канального слова и MSB (здесь вставленный "0" бит) текущего 25-битового канального слова подаются на логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 106.a. Младший значащий бит (LSB) из предшествующего канального слова и второй MSB бит (здесь первый бит входных данных) текущего 25-битового канального слова подаются на логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 106. b. Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 106.a и второй бит входных данных подаются на элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 106.c. Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 106.b и третий бит входных данных подаются на элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 106.d.

Логические элементы ИСКЛЮЧАЮЩЕЕ ИЛИ с 106.e по 106.y предварительно кодируют остальные данные 25-битового канального слова подобным же образом. Выходные сигналы логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с 106.a по 106.y являются 25-битовым канальным словом (предварительно закодированными данными), подаваемым параллельно от прекодера 106.1.

На фиг. 10 показана подробная схема защелок 106.3 и 106.4 прекодера 106.1. Если сигнал LOAD имеет высокий логический уровень, выходной сигнал 24 логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 106.x, подаваемый на информационный вход D-триггера D2 через логические элементы G8 и G9, подается в качестве второго LSB 24' предыдущего канального слова на второй вход логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 106.a по фиг. 8 в соответствии с системным синхроимпульсом (GLOCK 1). Одновременно выходной сигнал 25 логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 106.y, подаваемый на информационный вход D триггера D1 через логические элементы G2, G3, G5 и G6, подается как LSB 25' предшествующего канального слова на второй вход логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 106.b на фиг. 8 в соответствии с системным синхроимпульсом (GLOCK 1). Если командный сигнал LOAD имеет низкий логический уровень (и до тех пор, пока он не станет высоким), значения Q выходов D-триггеров D1 и D2 сохраняются. Поскольку выход D-триггера D1 подвержен влиянию первого контрольного сигнала CS1, подаваемого от выходного порта первого контрольного сигнала 125 генератора контрольных сигналов 116, показанного на фиг. 6, если первый контрольный сигнал CS1 имеет высокий уровень, выход 25 логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 106.y подается на элемент G2 без изменений. Если первый контрольный сигнал имеет низкий логический уровень, значение выхода логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 106.y меняется на противоположное.

Например, если выход 25 логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 106.y имеет высокий логический уровень, а первый контрольный сигнал CS1 - низкий уровень, выход D-триггера D1 будет иметь низкий уровень. Если первый контрольный сигнал CS1 и выход 25 оба имеют высокий уровень, выход D-триггера D1 будет иметь высокий уровень.

Если первый контрольный сигнал CS1 имеет высокий логический уровень, который указывает на то, что выбирается "положительное" информационное канальное слово, начальное состояние защелки 106.3 прекодера 106.1 остается без изменения. Если контрольный сигнал CS1 имеет низкий логический уровень, который указывает на то, что выбрано "отрицательное" канальное информационное слово, начальное состояние защелки 106.3 прекодера 106.1 меняется на противоположное.

P/S преобразователь 108.1 на фиг. 8 принимает соответствующие выходные сигналы логических элементов с 106.a по 106.y параллельно в соответствии с системным синхроимпульсом и командным сигналом LOAD, выдавая тем самым получаемые выходные сигналы в виде последовательного 25-битового канального слова. На фиг. 8 представлен P/S преобразователь 108.1, состоящий из 25 защелок с 108.a по 108.y, детально показанных на фиг. 11. На этой фиг. 11 показано, что каждая защелка выполнена на двух логических элементах И, логическом элементе ИЛИ и D-триггере. Если командный сигнал LOAD имеет высокий уровень, каждый D-триггер принимает выходной сигнал соответствующего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ прекодера 106.1 и выдает его в качестве входного сигнала первого логического элемента и заделки следующего более старшего бита. Если командный сигнал LOAD имеет низкий логический уровень, каждый D-триггер сохраняет свой Q выход до тех пор, пока командный сигнал LOAD не станет высокого уровня. Последовательное 25-битовое канальное слово выдается из выходного порта 113 в виде окончательного выходного сигнала.

P/S преобразователь 108.3 на фиг. 7 имеет ту же структуру, что и P/S преобразователь 108.1 на фиг. 11. Однако разница заключается в том, что выходной порт 117' защелки 108.a и выходной порт 121' защелки 108.n подсоединены к генератору контрольных сигналов 116.

P/S преобразователь 110.1 на фиг. 8 состоит из тринадцати защелок 10.a, 110.e..., и 110.y. Их структура такая же, как структура соответствующих защелок P/S преобразователя 108.1, показанного на фиг. 11. В ответ на командный сигнал LOAD и синхросигнал, появляющиеся одновременно из 25-битового канального слова (выдаваемого параллельно прекодером 106.1), отбираются нечетные канальные слова для параллельной загрузки в тринадцать защелок 110.a, 110.c, ..., и 110.y, так что с выходного порта 117 защелки 110.a выдается 13-битовое нечетное канальное слово.

P/S преобразователь 112.1 по фиг. 8 состоит из двенадцати защелок 112.b, 112.d..., и 112.x. Их структура такая же, как структура соответствующих защелок P/S преобразователя 108.1, показанного на фиг. 11. В ответ на командный сигнал LOAD и синхросигнал, появляющиеся одновременно из 25-битового канального слова (выдаваемого параллельно прекодером 106.1), отбираются четные канальные слова для параллельной загрузки в 12 защелок 112.a, 112.d,..., и 110. x, так что с выходного порта 121 защелки 112.a выдается 12-битовое четное канальное слово.

На фиг. 12 представлена блок-схема генератора контрольных сигналов 116, показанного на фиг. 6, который включает блок РАТН1 116.2, детектор 116.3 и преобразователи код - арифметическое выражение 116.4 -116.7. Преобразователь код - арифметическое выражение 116.4 преобразует единицы и нули, подаваемые от выходного порта 117 P/S преобразователя 110.1 на фиг. 6, в арифметические описания I-NRZI-модулированного сигнала, которые принимают то отрицательные, то положительные арифметические значения одной и той же амплитуды и в которых отсутствует постоянный член, причем арифметические выражения поступают с выходного порта 117' преобразователя код - арифметическое выражение 116.4. Преобразователь код - арифметическое выражение 116.5 преобразует единицы и нули, подаваемые от выходного порта 121 P/S преобразователя 110.1 по фиг. 6, в арифметические описания I-NRZI-модулированного сигнала, которые принимают то отрицательные, то положительные арифметические значения одной и той же амплитуды и в которых отсутствует постоянный член, причем арифметические выражения поступают с выходного порта 121' преобразователя код - арифметическое выражение 116.5. Преобразователь код - арифметическое выражение 116.6 преобразует единицы и нули, подаваемые от выходного порта 119 P/S преобразователя 110.2 по фиг. 6, в арифметические описания NRSZI модулированного сигнала, которые принимают то отрицательные, то положительные арифметические значения одной и той же амплитуды и в которых отсутствует постоянный член, причем арифметические выражения поступают с выходного порта 119' преобразователя код - арифметическое выражение 116.6. Преобразователь код - арифметическое выражение 116.7 преобразует единицы и нули, подаваемые от выходного порта 123 P/S преобразователя 110.2 по фиг. 6, в арифметические описания NRZI-модулированного сигнала, которые принимают то отрицательные, то положительные арифметические значения одной и той же амплитуды и в которых отсутствует постоянный член, причем арифметические выражения поступают с выходного порта 123' преобразователя код - арифметическое выражение 116.6.

Первый и второй входные порты блока РАТН0 116.1 соединены с соответствующими выходными портами 117' и 121' преобразователей код - арифметическое выражение 116.4 и 116.5. Выходной порт сигнала предустановки 137 блока РАТН1 116.2 соединен с входным портом предустановки блока РАТН0 116.1. Выходной порт блока РАТН0 116.1, выдающий сигнал ошибки e1, подсоединен к первому входному порту детектора 116.3. Первый и второй входные порты блока РАТН1 116.2 соединены с соответствующими выходными портами 119' и 123' преобразователей код - арифметическое выражение 116.6 и 116.7. Выходной порт сигнала предустановки 135 блока РАТН0 116.1 соединен с входом предустановки блока РАТН1 116.2. Выходной порт блока РАТН1 116.2, выдающего сигнал ошибки e2, подсоединен к второму входному порту детектора 116.3. Выходные порты первого и второго контрольного сигнала 125 и 127 детектора 116.3 соединены с соответствующими контрольными портами прекодеров 106.1 и 106.2 на фиг. 6 и с соответствующими контрольными портами блоков 116.1 и 116.2. Выходной порт третьего контрольного сигнала 129 подсоединен к контрольному порту выбора селектора 118.

На фиг. 13 представлена подробная схема блока РАТН0 116.1 генератора контрольных сигналов, показанного на фиг. 12. Первый и второй входные порты блока РАТН0 116.1 соединены с соответствующими выходными портами 117' и 121' преобразователей код - арифметическое выражение 116.4 и 116.5 по фиг. 12 для приема дополнительных двоичных кодов, описывающих INRZI-модуляцию, которая используется в качестве входного сигнала арифметическими элементами 122, 124, 134, 138, 146, 150, 158 и 174. Блок 116.1 состоит из схем интегрирования 122, 124, вплоть до схемы квадратирования 132 для формирования пилот-сигнала на заданной частоте (здесь f1) в частотном спектре 25-битового последовательного потока данных и одновременного формирования провала на нулевой частоте, умножителей 134, 138, вплоть до схемы квадратирования 156 для формирования провала на заданной частоте (здесь f2), вычитателей 158, 174, вплоть до схемы квадратирования 188 для формирования спадов на частотной характеристике пилот-сигнала (f1) и схемы суммирования со взвешиванием 190 для суммирования выходных сигналов схем квадратирования 132, 144, 156, 172 и 188, что позволяет генерировать сигнал ошибки e1.

Входное нечетное канальное слово от выходного порта 117' и входное четное канальное слово от выходного порта 121' суммируются со значением (значение цифровой суммы предыдущего 25-битового канального слова), хранящимся в соответствующих схемах интегрирования 122 и 124. Соответствующие выходные сигналы схем интегрирования 122 и 124 суммируются в сумматоре 126 и подаются затем на первый входной порт вычитателя 130.

Генератор треугольных импульсов 128 выполнен с ROM памятью и генерирует треугольный сигнал, соответствующий значению цифровой суммы (DSV) потока последовательных данных канальных слов, описывающему заданную частоту (здесь f1), соответствующую основной частотной составляющей треугольного сигнала. Если сигнал, генерируемый ROM, представляет собой треугольные импульсы с частотой f1 (например, 1/90 Т), как показано на фиг. 14A, 8-битовые данные (например, с 90A по 90L) записываются с использованием 5-битовых адресов, которые указывают значения от нуля до шестнадцати в таблице ROM, показанной на фиг. 14B. Вычитатель 130 вычитает выходной сигнал генератора треугольных импульсов 128 из выходного сигнала сумматора 126. Значение разности возводится в квадрат в схеме квадратирования 132 и подается в схему суммирования со взвешиванием 190. Генератор треугольных импульсов 128 и вычитатель 130 составляют схему, обеспечивающую обнаружение любого отклонения от заданной цифровой суммы, что необходимо для поддержания желаемого пилот-сигнала, причем значение цифровой суммы выдает сумматор 126; а схема квадратирования 132 рассчитывает энергию этого отклонения. Эти расчеты обеспечивают провал, формируемый на частоте f=0 Гц (другими словами, постоянная составляющая) и пилот-сигнал, который формируется на частоте f1.

Также выполняются расчеты для обеспечения провала на частоте f2 (ω2/2π) путем генерирования входных сигналов слагаемых для использования в схеме суммирования со взвешиванием 190 всякий раз, когда есть энергия на данной частоте спектра "положительного" информационного канального слова, подаваемого от прекодера 106.1. Это выполняется следующим образом.

Умножитель 134 умножает нечетные канальные слова на нечетный синусоидальный сигнал o_sinω2t,, а результат интегрируется в схеме интегрирования 136. Умножитель 138 умножает четные канальные слова на четный синусоидальный сигнал e_sinω2t,, а результат интегрируется в схеме интегрирования 140. Результаты интегрирования из схем интегрирования 136 и 140 складываются в сумматоре 142. Результирующая сумма возводится в квадрат в схеме квадратирования 144, а результирующий квадрат подается в схему суммирования со взвешиванием 190.

Умножитель 146 умножает нечетные канальные слова на нечетный косинусоидальный сигнал o_cosω2t,, а результат интегрируется в схеме интегрирования 48. Умножитель 150 умножает четные канальные слова на четный косинусоидальный сигнал e_cosω2t,, а результат интегрируется в схеме интегрирования 152. Результаты интегрирования из схем интегрирования 148 и 152 складываются в сумматоре 154. Результирующая сумма возводится в квадрат в схеме квадратирования 156, а результирующий квадрат в качестве слагаемого подается в схему суммирования со взвешиванием 190.

ROM (не показана) генерирует синусоидальный входной сигнал для использования в умножителях 134 и 138. Таблица синусов, хранящаяся в ROM, делится на таблицу нечетных выборочных значений синусов и таблицу четных выборочных значений синусов. Если колебание синусоидального сигнала представляет собой, например, 1/60 Т для частоты, f2, как показано на фиг. 15A, один период синусоидального сигнала делится на шестьдесят адресов, и данные, соответствующие величине выборочного синусоидального сигнала, хранятся по каждому адресу в таблице синусов. Данные, соответствующие нечетным адресам дискретизированного синусоидального сигнала, хранятся в таблице нечетных выборочных значений синусов. В таблице четных выборочных значений синусов хранятся данные, соответствующие четным адресам дискретизированного синусоидального сигнала. Как показано на фиг. 15B, точки, соответствующие битам (указаны тонкими кружками), имеют попеременно то нечетные, то четные адреса синусоидального сигнала, дискретизированного в периоде 25-битового канального слова. На чертеже символы ЕВ (дополнительный бит) указывают, куда вставляется "0" бит, то есть MSB. Подобным же образом ROM, имеющая таблицу нечетных выборочных значений косинусов, и таблицу четных выборочных значений косинусов, может генерировать косинусоидальный сигнал, который подается на умножители 146 и 150. Если установлено, что синусоидальный и косинусоидальный сигналы должны генерироваться посредством одной ROM, используется адрес, сдвинутый на 45o по отношению к синусоидальному сигналу, и считывается соответствующее значение (косинуса).

Также в зоны частотного спектра справа и слева от частоты f1= (ω1/2π) вводятся спады характеристики посредством генерирования входных сигналов слагаемых для использования в схеме суммирования со взвешиванием 190 всякий раз, когда есть энергия в этих зонах частотного спектра "положительного" информационного канального слова, выдаваемого прекодером 106.1. Это делается следующим образом.

Вычитатель 158 вычитает из нечетных канальных слов нечетные выборочные значения дискретизированного прямоугольного сигнала (фиг. 15C), генерируемого генератором прямоугольных импульсов 160. Генератор прямоугольных импульсов 160 и вычитатель 158 образуют схему детектирования для обнаружения любого отклонения от заданной прямоугольной формы "положительного" информационного последовательного битового нечетного канального слова, которое выдает P/S преобразователь 110.1 в виде, преобразованном к арифметическому преобразователем код - арифметическое выражение 116.4. Умножитель 162 умножает выходной сигнал вычитателя 158 на нечетный синусоидальный сигнал o_sinω1t, а результат интегрируется в схеме интегрирования 164. Умножитель 166 умножает выходной сигнал вычитателя 158 на нечетный косинусоидальный сигнал o_cosω1t, а результат интегрируется в схеме интегрирования 168.

Вычитатель 174 вычитает из четных канальных слов четные выборочные значения дискретизированного прямоугольного сигнала, генерируемого генератором прямоугольных импульсов 176. Генератор прямоугольных импульсов 176 и вычитатель 174 образуют схему детектирования для обнаружения любого отклонения от заданной прямоугольной формы "положительного" информационного последовательного битового нечетного канального слова, которое выдает P/S преобразователь 112.1 в виде, преобразованном к арифметическому преобразователем код - арифметическое выражение 116.5. Умножитель 178 умножает выходной сигнал вычитателя 174 на четный синусоидальный сигнал o_sinω1t, а результат интегрируется в схеме интегрирования 180. Умножитель 182 умножает выходной сигнал вычитателя 174 на четный косинусоидальный сигнал o_cosω1t, а результат интегрируется в схеме интегрирования 184.

Сумматор 170 суммирует соответствующие выходные сигналы схем интегрирования 164 и 180; результирующая сумма возводится в квадрат схемой квадратирования 172 и полученный квадрат подается в схему суммирования со взвешиванием 190. Сумматор 186 суммирует соответствующие выходные сигналы схем интегрирования 168 и 184; результирующая сумма возводится в квадрат схемой квадратирования 188 и полученный квадрат подается в схему суммирования со взвешиванием 190. Затем схема суммирования со взвешиванием 190 суммирует выходные сигналы схем квадратирования 132, 144, 156, 172 и 188, генерируя тем самым сигнал ошибки e1.

Функционирование схемы, показанной на фиг. 13, аналогично функционированию блока РАТН1 116.2 на фиг. 12. Отличие заключается в том, что контрольный сигнал, вводимый в соответствующие схемы интегрирования (не показаны) блока 116.2, является вторым контрольным сигналом CS2 и что схемой генерирования со взвешиванием (не показана) блока 116.2 генерируется сигнал ошибки e2. Если прекодеры 106.1 и 106.2 - 2Т-типа, ряд расчетов, выполняемых в РАТН0 и РАТН1 перед процедурами интегрирования, по существу одинаковы, что позволяет использовать одно и то же аппаратное обеспечение, если это необходимо. Сигнал ошибки e1 указывает, насколько DSV (значение цифровой суммы) в последовательном потоке данных, формируемом посредством ближайшего выбора "положительного" информационного слова, отклоняется от заданного DSV, а сигнал ошибки e2 указывает, насколько DSV в потоке последовательных данных, формируемом посредством ближайшего выбора "отрицательного" информационного слова, отклоняется от заданного DSV. Если сигнал ошибки e1 меньше сигнала ошибки e2, для записи будет выбрано "положительное" информационное слово от прекодера 106.1. Если сигнал ошибки e2 меньше сигнала ошибки e1, для записи будет выбрано "отрицательное" информационное слово от прекодера 106.2. Если сигналы ошибки e1 и e2 практически одинаковы, предпочтительно записывать "положительное" информационное слово от прекодера 106.1.

Детектор 116.3 по фиг. 12 включает компаратор, который выбирает меньший из сигналов ошибки e1 и e2 и выдает третий контрольный сигнал CS3. Компаратор обычно строится в виде вычитателя в дополнительном двоичном коде, принимающего сигналы ошибки e1 и e2 с дополнительными "0" битом знака, в виде уменьшаемого и вычитаемого, причем знаковый бит итоговой разности используется в качестве третьего контрольного сигнала CS3. Третий контрольный сигнал CS3 определяет, какой из контрольных сигналов, первый CS1 или второй CS2, будет генерироваться на заключительном отрезке интервала канального слова.

В соответствии с первым и вторым контрольными сигналами CS1 и CS2, генерируемыми из детектора 116.3 на фиг. 12, то есть, если первый контрольный сигнал CS1 имеет высокий уровень, а второй контрольный сигнал CS2 имеет низкий уровень, РАТН0, имеющий сигнал ошибки e1, селектируется так, что значения выходов соответствующих схем интегрирования РАТН1 заменяются на значения, хранящиеся в соответствующих схемах интегрирования 122, 124, 136, 149, 148, 152, 164, 168, 182 и 184, соответствующих РАТН0, показанному на фиг. 13, через порт предустановки 131.

На фиг. 16A - 16G представлены временные диаграммы сигналов в блоках, показанных на фиг. 6.

На фиг. 16A представлен выходной сигнал P/S преобразователя 108.1 первого преобразователя 108 для преобразования "положительного" информационного 25-битового параллельного канального слова, подаваемого из блока кодирования 106, в 25-битовое последовательное канальное слово в соответствии с системными синхроимпульсами (CLOCK1), показанными на фиг. 16D. Фиг. 16B иллюстрирует выходной сигнал P/S преобразователя 110.1 второго преобразователя 110 для приема "положительного" информационного 25-битового параллельного канального слова от блока кодирования 106 и последовательной выдачи только нечетных отобранных из него канальных слов в соответствии с системными синхроимпульсами (фиг. 16D). На фиг. 16C показан выходной сигнал P/S преобразователя 112.1 третьего преобразователя 112 для приема "положительного" информационного 25-битового параллельного канального слова от блока кодирования 106 и последовательной выдачи только четных отобранных из него канальных слов в соответствии с системными синхроимпульсами.

На фиг. 16E, 16F, 16G показаны первый, второй и третий контрольные сигналы CS1, CS2 и CS3, генерируемые генератором контрольных сигналов 116.

Первый и второй контрольные сигналы CS1 и CS2 попеременно принимают высокий уровень на концах циклов длиной 25 бит. Первый и второй сигналы CS1 и CS2 подаются соответственно на первый прекодер 106.1 и второй прекодер 16.2. Третий контрольный сигнал CS3 подается на селектор 118. Если третий контрольный сигнал CS3 имеет высокий уровень, селектор 118 выбирает выходной сигнал P/S преобразователя 108.1, задержанный посредством схемы задержки 114.1 вплоть до следующего цикла длиной 25 бит. Если третий контрольный сигнал CS3 имеет низкий уровень, селектор 118 выбирает выходной сигнал P/S преобразователя 108.2, задержанный посредством схемы задержки 114.2 вплоть до следующего цикла длиной 25 бит.

Следовательно, если данные в режиме разделения времени мультиплексируются в нечетные канальные слова и четные канальные слова, показанные на фиг. 16B и 16C, хотя и задерживаемые схемами интегрирования, умножителями и схемами квадратирования генератора контрольных сигналов, показанными на фиг. 13, то обеспечивается уменьшение по крайней мере на двенадцать синхроимпульсов, времени, необходимого для расчета контрольного сигнала, по сравнению с интервалом в 25 системных синхроимпульсов на канальное слово. Если данные мультиплексируются в режиме разделения времени в начальные и конечные битовые группы, возможно подобное же уменьшение времени, необходимого для расчета контрольного сигнала. Это дает возможность генерировать контрольный сигнал в реальном времени для выбора одного выходного сигнала, то есть, сигнала, имеющего заданные спектральные характеристики, из двух сигналов, подаваемых от P/S преобразователей 108.1 и 108.2.

На фиг. 17 показана другая подробная схема РАТН0, показанного на фиг. 12. Схема демонстрирует упрощение структуры, которое может быть достигнуто в схеме РАТН0 по фиг. 13. Две схемы интегрирования 122 и 124 и единый сумматор 126, обведенные пунктирной линией на фиг. 13, заменены на фиг. 17 более простой эквивалентной схемой, выполненной на едином сумматоре 192 и единой схеме интегрирования 194. Две схемы интегрирования 136 и 140 и единый сумматор 142, обведенные на фиг. 13 пунктирной линией, заменены на фиг. 17 более простой эквивалентной схемой, выполненной на едином сумматоре 206 и единой схеме интегрирования 208. Две схемы интегрирования 148 и 152 и единый сумматор 154, обведенные на фиг. 13 пунктирной линией, заменены на фиг. 17 более простой эквивалентной схемой, выполненной на едином сумматоре 216 и единой схеме интегрирования 218. Две схемы интегрирования 164 и 180 и единый сумматор 170, обведенные на фиг. 13 пунктирной линией, заменены на фиг. 17 более простой эквивалентной схемой, выполненной на едином сумматоре 230 и единой схеме интегрирования 232. И две схемы интегрирования 168 и 184 и единый сумматор 186, обведенные на фиг. 13 пунктирной линией, заменены на фиг. 17 более простой эквивалентной схемой, выполненной на едином сумматоре 244 и единой схеме интегрирования 246. Если прекодеры 106.1 и 106.2 являются прекодерами 2Т типа, конкретные расчеты, выполняемые в РАТН0 и РАТН1 перед процедурами интегрирования, в принципе одинаковы, что позволяет, если это необходимо, совместно использовать одну и ту же аппаратуру.

На фиг. 18 показано другое устройство для записи цифровых сигналов, воплощающее изобретение, в котором слова с параллельными битами, которые последовательно подаются прекодерами, преобразуются в последовательный битовый формат с битовой частотой, кратной битовой частоте, используемой при цифровой записи. Элементы, подобные тем, что использованы в фиг. 6, обозначены теми же номерами, и повторное описание их работы не производится.

Структура на фиг. 18 подобна схеме на фиг. 6, за исключением второго преобразователя 310 для преобразования 25-битового канального слова, подаваемого параллельно из кодирующего блока 106, в последовательное 25-битовое канальное слово в соответствии со вторым тактовым импульсом (CLOCK2) с частотой, в два раза большей, чем частота системных тактовых импульсов (CLOCK1). Второй преобразователь 310 заменяет второй преобразователь 110 для преобразования нечетных канальных слов из 25-битового, с параллельными битами, канального слова, подаваемого из блока кодирования 106 на фиг. 6, в последовательное битовое канальное слово и третий преобразователь 112 для преобразования четных канальных слов из 25-битового, с параллельными битами, канального слова, подаваемого из блока кодирования 106, в последовательное битовое канальное слово.

Функционирование схемы по фиг. 18 будет объяснено со ссылками на фиг. 19A - 19D.

На фиг. 18 конкретное устройство и принцип действия P/P преобразователя 102, блока вставки 104, блока кодирования 106 и первого преобразователя 108 - такие же, как и на фиг. 8-11.

На фиг. 19A показан выходной сигнал P/S преобразователя 108, который преобразует 25-битовое параллельное "положительное" информационное канальное слово (подаваемое от прекодера 106.1) в 25-битовое последовательное "положительное" информационное канальное слово.

На фиг. 19B показан первый синхросигнал (CLOCK1), согласно которому синхронизируются последовательные битовые сигналы от первого преобразователя 108.

На фиг. 19C показан выходной сигнал P/S преобразователя 310.1, второго преобразователя 310, который преобразует 25-битовое параллельное "положительное" информационное канальное слово (подаваемое от прекодера 106.1) в 25-битовое последовательное канальное слово, подаваемое с битовой частотой, в два раза большей, чем частота 25-битовых последовательных канальных слов, подаваемых от P/S преобразователя 108.1.

На фиг. L9D показан второй синхросигнал (CLOCK2), согласно которому синхронизируются последовательные битовые сигналы от второго преобразователя 310.

В устройстве для записи цифровых сигналов по фиг. 18 генератор контрольных сигналов 116' принимает выходной сигнал второго преобразователя 310 с двойным временным уплотнением в соответствии со вторым синхроимпульсом, что соответствует половине первоначального периода 25-битового параллельного канального слова. Сравнение соответствующих частотных компонент уплотненных во времени "положительных" информационных 25-битовых последовательных канальных слов и уплотненных во времени "отрицательных" информационных 25-битовых последовательных канальных слов, выдаваемых параллельно, успешно выполняется в рамках одного интервала 25-битового параллельного канального слова, несмотря на задержку, вводимую в расчеты схемами интегрирования, умножителями и схемами квадратирования генератора контрольных сигналов 116'', подобных тем, которые показаны на фиг. 13 или 17. Соответственно контрольный сигнал для выбора 25-битового параллельного канального слова для заданного канала может быть сгенерирован и без необходимости отказа от конвейерной обработки канальных слов. Двойное временное уплотнение обычно достаточно и является предпочтительным благодаря легкости, с которой могут быть сгенерированы синхросигналы с отношением частот 2:1, путем использования простой счетной схемы, и благодаря тому, что возможность удвоения тактовой частоты не приведет к необходимости иметь чрезмерно высокую тактовую частоту.