Изобретение относится к радиотехнике и может найти применение в приемниках широкополосных сигналов.

Известны устройства поиска широкополосных сигналов по задержке, описанные в а.с. N 1104677 H 04 L 7/04, патенте РФ N 2020762 H 04 B 1/10, недостатком которых является большая вероятность ложной синхронизации по помехе.

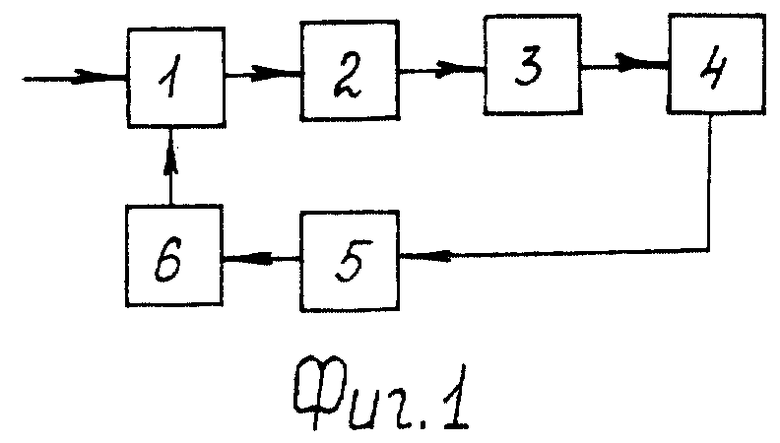

Наиболее близким по технической сущности к предлагаемому устройству является устройство поиска широкополосных сигналов по задержке, описанное в монографии Г.И. Тузова "Статистическая теория приема сложных сигналов", Москва, "Сов. радио", 1977 г., стр. 326, структурная схема которого приведена на фиг. 1, где использованы следующие обозначения:

1. перемножитель (фазовый ремодулятор);

2 - фильтр;

3 - амплитудный детектор;

4 - блок сравнения с порогом;

5 - блок управления поиском;

6 - генератор кода.

Устройство-прототип содержит последовательно соединенные перемножитель 1, вход которого является входом устройства, фильтр 2, амплитудный детектор 3, блок сравнения с порогом 4, блок управления поиском 5, генератор кода 6, выход которого соединен с опорным входом перемножителя 1.

Устройство-прототип работает следующим образом.

Входная смесь, содержащая полезный широкополосный сигнал и узкополосную помеху, поступает на блок 1, где перемножается с опорным сигналом блока 6. Опорная кодовая последовательность, формируемая блоком 6, сканирует по задержке, управление сканированием осуществляет блок 5. Результат перемножения в блоке 1 входного и опорного сигналов фильтруется в блоке 2, детектируется в блоке 3, сравнивается с порогом в блоке 4. При превышении порога блок 4 формирует команду "1", при поступлении которой блок 5 прекращает сканирование опорного сигнала блока 6. Недостатком прототипа является низкая помехоустойчивость.

Для устранения указанных недостатков в устройстве, содержащее последовательно соединенные первый перемножитель, вход которого является входом устройства, первый фильтр и первый амплитудный детектор, последовательно соединенные блок управления поиском и генератор кода, выход которого соединен с опорным входом первого перемножителя, а также блок сравнения с порогом, введены последовательно соединенные первый ключ, первый элемент задержки, вычитатель, второй перемножитель, второй фильтр и второй амплитудный детектор, последовательно соединенные второй ключ, третий перемножитель, третий фильтр и регулируемый усилитель, последовательно соединенные четвертый перемножитель и интегратор, а также второй и третий элементы задержки и решающий блок. Причем выход первого амплитудного детектора через решающий блок соединен со входом блока управления поиском, выход генератора кода одновременно через первый элемент задержки соединен с опорным входом второго перемножителя, а через третий элемент задержки - с опорным входом третьего перемножителя. Выход регулируемого усилителя одновременно соединен со вторыми входами вычитателя и четвертого перемножителя, первый вход которого соединен с выходом вычитателя, вход интегратора соединен с управляющим входом регулируемого усилителя, выход второго амплитудного детектора соединен со входом блока сравнения с порогом, выход которого соединен с управляющим входом решающего блока, второй выход которого одновременно соединен с управляющими входами первого и второго ключей, вход которого соединен с выходом первого фильтра, а вход первого ключа соединен со входом первого перемножителя.

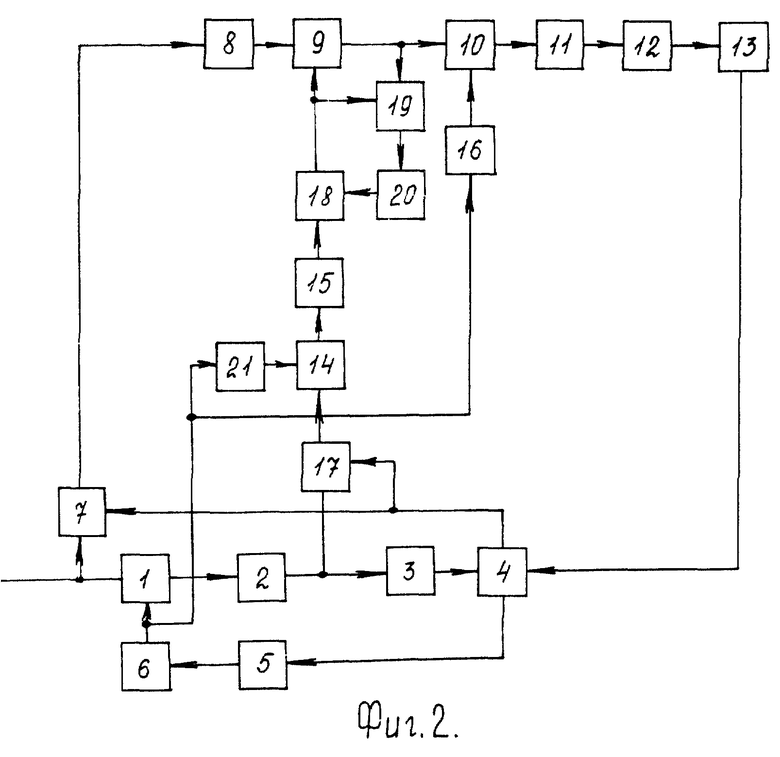

Структурная схема предлагаемого устройства приведена на фиг. 2, где использованы следующие обозначения:

1, 10, 14, 19 - первый, второй, третий и четвертый перемножители;

2, 11, 15 - первый, второй и третий фильтры;

3, 12 - первый и второй амплитудные детекторы;

4 - решающий блок;

5 - блок управления поиском;

6 - генератор кода;

7, 17 - первый и второй ключ;

8, 16, 21 - первый, второй и третий элементы задержки;

9 - вычитатель;

13 - блок сравнения с порогом;

18 - регулируемый усилитель;

20 - интегратор.

Заявляемое устройство содержит последовательно соединенные первый перемножитель 1, первый фильтр 2, первый амплитудный детектор 3, решающий блок 4, блок управления поиском 5, генератор кода 6, третий перемножитель 14, третий фильтр 15, регулируемый усилитель 18, вычитатель 9, второй перемножитель 10, второй фильтр 11, второй амплитудный детектор 12, блок сравнения с порогом 13 содержит последовательно соединенные первый ключ 7 и первый элемент задержки 8, включенные между входом первого перемножителя 1, вход которого является входом устройства, и вторым входом вычитателя 9, содержит последовательно соединенные четвертый перемножитель 19 и интегратор 20, включенные между точкой соединения вычитателя 9 и второго перемножителя 10 и управляющим входом регулируемого усилителя 18, содержит второй ключ 17, включенный между точкой соединения первого фильтра 2 и первого амплитудного детектора 3 и сигнальным входом третьего перемножителя 14, содержит второй элемент задержки 16 и третий элемент задержки 21, при этом выход генератора кода 6 через второй элемент задержки 16 соединен с опорным входом второго перемножителя 10, а через третий элемент задержки 21 - с опорным входом третьего перемножителя 14, выход амплитудного детектора 3 через решающий блок 4 соединен с управляющими входами первого 7 и второго 17 ключей и с управляющим входом блока управления поиском 5, выход блока сравнения с порогом 13 соединен с управляющим входом решающего блока 4, выход регулируемого усилителя 18 соединен со вторым входом четвертого перемножителя 19, вход ключа 7 соединен со входом перемножителя 1.

Заявляемое устройство работает следующим образом.

В исходный момент времени ключи 7 и 17 закрыты. Входная смесь, содержащая полезный широкополосный сигнал и узкополосную помеху, поступает на блок 1, где она перемножается с опорным сигналом блока 6. Результат перемножителя фильтруется в блоке 2, детектируется в блоке 3, в блоке 4 накопленное напряжение сравнивается с порогом, при этом формируются две команды, одна из которых подается на блок 5, а другая - на ключи 7 и 17.

При несовпадении начальных фаз (задержки) входного полезного и опорного сигналов в блоке 1 происходит расширение спектра как полезного широкополосного сигнала, так и узкополосной помехи за счет манипуляции их по фазе на [0,π] опорной кодовой последовательности.

В этом случае превышение порога в блоке 4 может произойти только под воздействием мощной помехи, что соответствует ложной синхронизации. При совпадении начальных фаз полезного и опорного сигналов в блоке 1 происходит свертка полезного широкополосного сигнала в узкокополосный сигнал, а узкополосная помеха становится широкополосной за счет манипуляции ее по фазе опорным широкополосным сигналом (кодовой последовательностью). В этом случае порог в блоке 4 может быть превышен как полезным сигналом, что соответствует правильной синхронизации, так и помехой, что соответствует ложной синхронизации.

При превышении порога блок 4 подает команду "1" на ключи 7 и 17, открывая их. В этом случае входная смесь поступает через блоки 7 и 8 на вычитатель 9, где из нее вычитается оценка полезного широкополосного сигнала, которая формируется следующим образом. Напряжение с выхода блока 2 через ключ 17 подается на блок 14, где оно перемножается (манипулируется по фазе на 0,π) опорной кодовой последовательностью блока 6, в результате чего на выходе блока 14 формируется широкополосный полезный сигнал и широкополосная фазоманипулированная помеха, сформировавшаяся из помехи во входной смеси за счет ее прохождения через блоки 1, 2, 14. Полученная смесь фильтруется в блоке 15, полоса пропускания которого равна ширине спектра полезного сигнала.

С выхода блока 15 смесь оценки полезного сигнала и широкополосной помехи, сформировавшейся из узкополосной помехи, через блок 18 подается на второй вход блока 9, на первый его вход подается входная смесь со входа устройства через элемент задержки 8. В блоке 9 происходит компенсация полезного сигнала во входной смеси и на выходе его выделяются две составляющие помехи, одна из которых является узкополосной помехой из входной смеси, а другая - широкополосной помехой, сформировавшейся из узкополосной в блоках 14, 15. Блоки 18, 19, 20 обеспечивают автоматическую регулировку амплитуды оценки сигнала с целью его максимального подавления в блоке 9.

С выхода блока 9 две составляющие помехи подаются на перемножитель 10, где за счет перемножения с опорной кодовой последовательностью, подаваемой на опорный вход блока 10 с выхода блока 6 через элемент задержки 16, узкополосная помеха расширяет свой спектр, часть расширенного спектра помехи попадает в полосу блока 11, детектируется в блоке 12. В то же время широкополосная составляющая помехи в блоке 10 сворачивается в узкополосную помеху, которая также фильтруется в блоке 11, детектируется в 12. Свертка широкополосной составляющей помехи в блоке 10 объясняется тем, что по своей структуре она аналогична полезному сигналу и отличается от него только начальной фазой, что объясняется методом его формирования в блоках 2, 14, 15. С выхода блока 12 продетектированная смесь двух составляющих помех сравнивается с порогом в блоке 13. Сигнал о превышении ("1") или непревышении порога подается на блок 4.

Так как полезный сигнал в блоке 9 скомпенсирован, то превышение порога в блоке 13 может произойти только под влиянием помехи.

Алгоритм принятия решения блоком 4 об окончании или продолжении поиска состоит в следующем. Если после превышения порога в блоке 4, в блоке 13 порог не превышен, блок 4 принимает решение об окончании поиска.

Такое решение обусловлено тем, что на входе блока 13 сигнал отсутствует (он скомпенсирован в блоке 9), поэтому непревышение порога в блоке 13 на втором, проверочном, этапе поиска свидетельствует о правильном обнаружении сигнала на первом этапе.

Если порог превышен и на первом этапе поиска (в блоке 4) и на втором, проверочном, этапе (в блоке 13), принимается решение о ложной синхронизации на первом этапе поиска и режим поиска возобновляется.

Аналогичным образом производится обнаружение ложной синхронизации по структурной помехе.

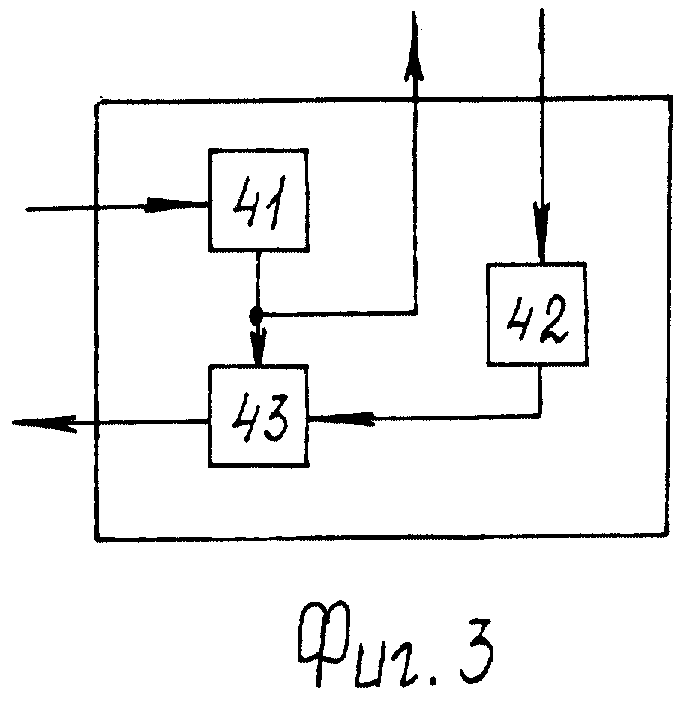

Структурная схема блока 4, реализующая указанный алгоритм принятия решений, представлена на фиг. 3, где использованы следующие обозначения:

41 - блок сравнения с порогом;

42 - инвертор;

43 - элемент "И".

Блок 4 работает следующим образом. Напряжение с выхода блока 3 подается на блок 41, где оно сравнивается с порогом. Команда о превышении (непревышении) порога подается на блоки 7 и 17, отпирая (или запирая их), и на первый вход блока 43, на второй вход которого подается команда от блока 13 через блок 42. С выхода блока 43 команда ("1" или "0") подается на управляющий вход блока 5. В исходном режиме отсутствия синхронизации с полезным сигналом на выходе блока 4 формируется команда "0", которая, поступая на ключи 7 и 17, обеспечивает их запирание.

В этом случае на выходе блока 13 также формируется команда "0", так как дополнительный канал, содержащий блоки 8-13, отключен от входа устройства. Команда "0", поступающая от блока 13, инвертируясь в блоке 42, превращается в команду "1". Таким образом на входах блока 43 присутствует "0" и "1", и на выходе его формируется "0", который подается на блок 5. В этом случае блок 5 обеспечивает режим поиска по задержке. При превышении порога в блоке 41 формируется команда "1", которая открывает ключи 7 и 17. Если в этом случае в блоке 13 порог не превышается, то на входы блока 43 поступают команды "1" и "1" и на его выходе также формируется команда "1", которая, поступая на блок 5, прекращает режим поиска. В этом случае блок 4 принимает решение о синхронизации по полезному сигналу.

Если на выходе блока 13 формируется "1" то на входы блока 43 подаются команды "0" и "1", а на его выходе формируется команда "0".

В этом случае блок 4 принимает решение о ложной синхронизации и переводит устройство в режим поиска за счет подачи команды "0" на блок 5. При переводе в режим поиска на выходе блока 43 формируется команда "0", которая запирает ключи 7 и 17.

Блок 5 может быть выполнен в виде управляемого генератора тактовых частот (см. монографию Г.И. Тузова "Статистическая теория приема сложных сигналов". Москва, "Сов. радио", 1977 г., стр. 326, рис. 7.2). В режиме поиска, когда на генератор кода подается команда "0", он формирует тактовую частоту (fт+Δf), отличающуюся от тактовой частоты генератора кода передатчика на величину Δf ≪ fт. Введение расстройки Δf обеспечивает режим взаимного скольжения между входной и опорной кодовыми последовательностями. При поступлении на вход блока 5 команды "1" в нем устанавливается частота fт, при этом обеспечивается синхронность между входной и опорной кодовыми последовательностями. Блоки 8, и 16, и 21 обеспечивают выравнивание сигналов по времени с учетом их задержек в тактах обработки.

Устройство-прототип не отличает синхронизацию по помехе от синхронизации по полезному сигналу, при воздействии мощной помехи (узкополосной, структурной, имитационной и т.д.) вероятность ложной синхронизации для прототипа близка к 1.

В заявленном устройстве после фиксации факта превышения порога на втором этапе поиска проводится дополнительная процедура, позволяющая выяснить, чем обусловлено превышение порога - сигналом или помехой. Эта процедура предполагает формирование оценки полезного сигнала на первом этапе принятия решения о завершении поиска и компенсации полезного сигнала с использованием этой оценки во входной смеси на втором этапе поиска. В случае превышения порога на 2-м этапе поиска решение об окончании поиска не принимается, так как на втором этапе превышение порога может быть обусловлено только помехой (так как полезный сигнал исключен из входной смеси).

За счет реализации указанной процедуры вероятность ложной синхронизации в заявляемом устройстве практически исключается.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ ПО ЗАДЕРЖКЕ | 1999 |

|

RU2165129C2 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ СТРУКТУРНЫХ ПОМЕХ ДЛЯ ПРИЕМНИКОВ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1999 |

|

RU2166232C2 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ПОМЕХ ДЛЯ СПУТНИКОВЫХ СИСТЕМ СВЯЗИ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 1999 |

|

RU2143783C1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ШИРОКОПОЛОСНЫХ ПОМЕХ | 2001 |

|

RU2196385C2 |

| КОРРЕЛЯТОР ДЛЯ БАЗОВОЙ СТАНЦИИ СИСТЕМЫ СВЯЗИ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 2000 |

|

RU2190298C2 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ УЗКОПОЛОСНЫХ ПОМЕХ ДЛЯ ПРИЕМНИКОВ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2000 |

|

RU2204201C2 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ СТРУКТУРНЫХ ПОМЕХ | 2001 |

|

RU2209512C2 |

| СПОСОБ КОРРЕЛЯЦИОННОЙ ОБРАБОТКИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2000 |

|

RU2185658C2 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ СТРУКТУРНЫХ ПОМЕХ ДЛЯ ПРИЕМНИКОВ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2001 |

|

RU2205503C2 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ШИРОКОПОЛОСНЫХ ФАЗОМАНИПУЛИРОВАННЫХ ПОМЕХ | 2001 |

|

RU2204202C2 |

Устройство поиска широкополосных сигналов по задержке относится к области радиотехники и может найти применение в приемниках широкополосных сигналов. В устройстве после принятия решения о синхронизации по полезному сигналу вводится процедура проверки, основанная на исключении из входной смеси полезного сигнала за счет его компенсации, при этом оценка сигнала формируется на первом этапе поиска. Указанная процедура позволяет отличить правильную синхронизацию по полезному сигналу от ложной синхронизации по помехе. Достигаемый технический результат - исключение ложной синхронизации по помехе. Устройство содержит четыре перемножителя, три фильтра, два амплитудных детектора, решающий блок, блок управления поиском, генератор кода, два ключа, вычитатель, блок сравнения с порогом, регулируемый усилитель, интегратор, три элемента задержки. 3 ил.

Устройство поиска широкополосных сигналов по задержке, содержащее последовательно соединенные первый перемножитель, вход которого является входом устройства, первый фильтр и первый амплитудный детектор, последовательно соединенные блок управления поиском и генератор кода, выход которого соединен с опорным входом первого перемножителя, а также блок сравнения с порогом, отличающееся тем, что введены последовательно соединенные первый ключ, первый элемент задержки, вычитатель, второй перемножитель, второй фильтр и второй амплитудный детектор, последовательно соединенные второй ключ, третий перемножитель, третий фильтр и регулируемый усилитель, последовательно соединенные четвертый перемножитель и интегратор, а также второй и третий элементы задержки и решающий блок, при этом выход первого амплитудного детектора через решающий блок соединен со входом блока управления поиском, выход генератора кода одновременно через третий элемент задержки соединен с опорным входом третьего перемножителя и через второй элемент задержки - с опорным входом второго перемножителя, выход регулируемого усилителя одновременно соединен со вторыми входами вычитателя и четвертого перемножителя, первый вход которого соединен с выходом вычитателя, выход интегратора соединен с управляющим входом регулируемого усилителя, выход второго амплитудного детектора соединен со входом блока сравнения с порогом, выход которого соединен с управляющим входом решающего блока, второй выход которого одновременно соединен с управляющими входами первого и второго ключей, вход которого соединен с выходом первого фильтра, а вход первого ключа соединен со входом первого перемножителя.

| RU 2000664 С, 07.09.1993 | |||

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2020762C1 |

| АДАПТИВНОЕ УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ЗАДЕРЖКОЙ ШИРОКОПОЛОСНОГО СИГНАЛА | 1990 |

|

RU2040856C1 |

| US 4355398, 19.10.1982 | |||

| UA 4627080, 02.12.1986 | |||

| US 4726043, 16.02.1988 | |||

| ТУЗОВ Г.И | |||

| Статистическая теория приема сложных сигналов | |||

| - М.: Советское радио, 1977, с.326. | |||

Авторы

Даты

2001-04-27—Публикация

2000-01-10—Подача