Предлагаемое изобретение относится к радиотехнике и может найти применение в системах связи с широкополосными сигналами.

Известны устройства поиска широкополосных сигналов по задержке, описанные в а.с. N 1104677, H 04 B 7/04, патент РФ N 2020762, H 04 B 1/10 и др. , недостатком которых является большая вероятность ложной синхронизации по помехе.

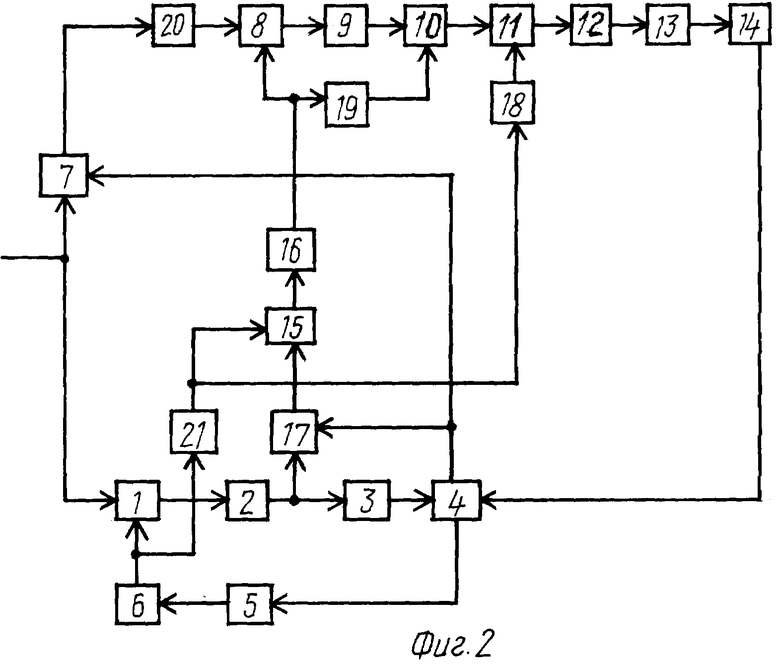

Наиболее близким по технической сущности к предлагаемому является "Устройство поиска широкополосных сигналов по задержке", описанные в патенте РФ N 2000664, H 04 B 1/10, 07.09.93, структурная схема которого приведена на фиг. 1, где использованы следующие обозначения:

1,7 - первый и второй согласованный фильтр;

2,8 - первый и второй детектор;

3,9 - первый и второй пороговый блок;

4,6 - первый и второй перемножитель;

5 - режекторный фильтр;

10 - генератор кода;

11 - элемент задержки;

12 - ключ;

13 - решающий блок;

14 - усилитель.

Устройство-прототип содержит последовательно соединенные ключ 12, первый перемножитель 4, режекторный фильтр 5, второй перемножитель 6, усилитель 14, второй согласованный фильтр 7, второй детектор 8, второй пороговый блок 9, решающий блок 13, последовательно соединенные первый согласованный фильтр 7, первый детектор 2, первый пороговый блок 3, содержит элемент задержки 11 и генератор кода 10, соединенный со входом первого перемножителя 4 непосредственно, а со входом второго перемножителя через элемент задержки 11, входы ключа 12 и генератора кода 10 объединены и соединены с другим выходом порогового блока 3, вход согласованного фильтра 2 и другой вход ключа 12 объединены и являются входом устройства.

Недостатком прототипа является большая вероятность ложной тревоги.

Для устранения указанного недостатка в устройство, содержащее последовательно соединенные второй перемножитель, режекторный фильтр, первый фазовый модулятор, последовательно соединенные генератор кода, четвертый элемент задержки, второй фазовый модулятор, последовательно соединенные первый амплитудный детектор и решающий блок, последовательно соединенные второй амплитудный детектор и блок сравнения с порогом, выходом соединенный с другим входом решающего блока, а также первый ключ, вход которого является входом устройства и второй элемент задержки, соединенный с другим входом первого фазового модулятора, введены последовательно соединенные первый перемножитель, первый полосовой фильтр, второй ключ, последовательно соединенные первый элемент задержки, третий перемножитель, второй полосовой фильтр, блок управления поиском, ограничитель и третий элемент задержки, при этом вход первого ключа соединен со входом первого перемножителя, выход решающего блока соединен со входом генератора кода через блок управления поиском, выход четвертого элемента задержки соединен также со входом первого элемента задержки, выход первого ключа через третий элемент задержки соединен со входом второго перемножителя, выход второго фазового модулятора через ограничитель соединен со входом второго элемента задержки и другим входом второго перемножителя.

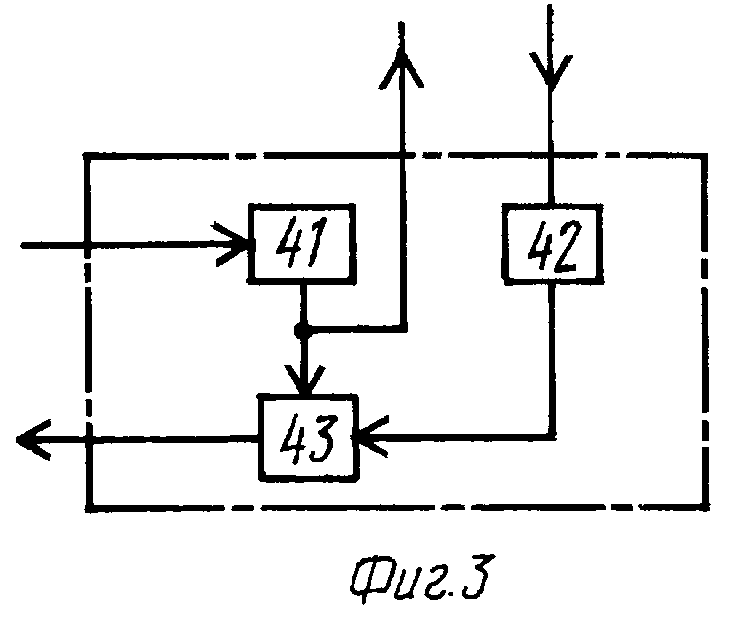

Структурная схема заявляемого устройства приведена на фиг. 2, где обозначено:

1,8, 11 - первый, второй и третий перемножители;

2,12 - первый и второй полосовой фильтр;

3,13 - первый и второй амплитудный детектор;

4 - решающий блок;

5 - блок управления поиском;

6 - генератор кода;

7,17 - первый и второй ключ;

9 - режекторный фильтр;

10,15 - первый и второй фазовый модулятор;

14 - блок сравнения с порогом;

16 - ограничитель;

8, 19, 20, 21 - первый, второй, третий и четвертый элемент задержки.

Предлагаемое устройство содержит последовательно соединенные перемножитель 1, первый полосовой фильтр 2, первый амплитудный детектор 3, решающий блок 4, блок управления поиском 5, генератор кода 6, выход которого соединен с другим входом перемножитиля 1, последовательно соединенные первый ключ 7, третий элемент задержки 20, второй перемножитель 8, режекторный фильтр 9, первый фазовый модулятор 10, третий перемножитель 11, второй полосовой фильтр 12, второй амплитудный детектор 13, блок сравнения с порогом 14, выход которого соединен с другим входом решающего блока 4. Выход генератора кода 6 через последовательно соединенные четвертый элемент задержки 21, второй фазовый модулятор 15 и ограничитель 16 соединен также с другим входом второго перемножителя 8, а через второй элемент задержки 19 - с другим входом первого фазового модулятора 10. Выход четвертого элемента задержки 21 соединен также через первый элемент задержки 18 с другим входом третьего перемножителя 11. При этом выход первого полосового фильтра 2 через второй ключ 17 соединен с другим входом второго фазового модулятора 15. Другой выход решающего блока 4 одновременно соединен с соответствующими входами первого ключа 7 и второго ключа 17. Входы первого перемножителя 1 первого ключа 7 объединены и являются входом устройства.

Работает заявляемое устройство следующим образом.

На вход устройства поступает входная смесь, содержащая полезный широкополосный сигнал и помеху, например, структурную.

В исходный момент времени ключи 7 и 17 закрыты. Входная смесь поступает на блок 1, где она перемножается с опорным сигналом генератора кода 6. Результат перемножения фильтруется в блоке 2, детектируется в блоке 3, после чего подается на решающий блок 4. В блоке 4 осуществляется сравнение накопленного напряжения с порогом (фиксированным) и формирование двух команд, одна из которых подается на блок 5, а другая - на ключи 7 и 17. При этом каждая из команд может принимать значения или "1" или "0".

При несовпадении начальной фазы (задержки) входного широкополосного сигнала и опорного сигнала в блоке 1 происходит расширение спектра как полезного сигнала, так и помехи. В этом случае превышение порога в блоке 4 может произойти под воздействием помехи.

При совпадении начальных фаз (задержки) кодовых последовательностей входного и опорного сигналов в блоке 1 происходит свертка широкополосного сигнала в узкополосный, а спектр помехи и в этом случае расширяется.

Порог в этом случае в блоке 4 может быть превышен как полезным сигналом (что соответствует правильной синхронизации), так и помехой (что соответствует ложной синхронизации). Для уменьшения вероятности ложной синхронизации используется дополнительный канал обработки.

При повышении порога блок 4 подает команду "1" на ключи 7 и 17 открывая их. В этом случае входная смесь поступает через блоки 7 и 20 на первый перемножитель 8, куда в качестве опорного сигнала с выхода ограничителя 16 подается оценка полезного сигнала, которая формируется в основном канале. В блоке 8 осуществляется свертка полезного широкополосного сигнала, которая формируется в узкополосный сигнал, который режектируется в блоке 9. В то же время помеха за счет перемножения с широкополосным опорным сигналов расширяет свой спектр, малая часть расширенного спектра режектируется в блоке 9, после чего помеха с расширенным спектром поступает на блок 10, где перемножается с тем же опорным сигналом, поступающим от блока 9 через блок 19. В результате в блоке 10 осуществляется снятие с помехи манипуляции, наложенной в блоке 8, и помеха восстанавливает свой первоначальный вид.

Отличие восстановленной на выходе блока 10 помехи от помехи во входной смеси заключается в том, что 1/Б -я часть ее (Б-база широпополосного сигнала) вырезана в блоке 9, при этом Б >> 10.

Восстановленная помеха с выхода блока 10 подается на блок 11, где перемножается с псевдослучайной последовательностью генератора 6, поступающей с его выхода через элементы задержки 21 и 18.

За счет перемножения помеха в блоке 11 опять расширяет свой спектр, часть ее спектра фильтруется блоком 12, детектируется в блоке 13 и сравнивается с порогом в блоке 14.

Формирование оценки полезного широкополосного сигнала осуществляется следующим образом.

Свернутый сигнал с выхода фильтра 2 через ключ 17 подается на блок 15, где манипулируется по фазе псевдослучайной последовательностью генератора 6, поступающей через элемент задержки 21. В результате полезный сигнал становится широкополосным, то есть аналогичным по структуре полезному сигналу во входной смеси.

Ограничитель 16 обеспечивает постоянство амплитуды сформированного опорного сигнала при изменении уровня полезного сигнала по входной смеси.

Сигнал о превышении ("1") или о непревышении ("0") порога в блоке 14 подается на блок 4.

Алгоритм принятия решения блоком 4 об окончании или продолжении поиска состоит в следующем.

Если после превышения порога в блоке 4 в блоке 13 не превышен порог, блок 4 принимает решение об окончании поиска. Такое решение обусловлено тем, что на входе блока 14 может присутствовать помеха, а сигнал отсутствует (он отрежектирован в блоке 9), поэтому непревышение порога в блоке 14 подтверждает правильное обнаружение сигнала на 1-м этапе. Если порог превышен и в блоке 4 и в блоке 14, принимается решение о сложной синхронизации на первом этапе и режим поиска возобновляется.

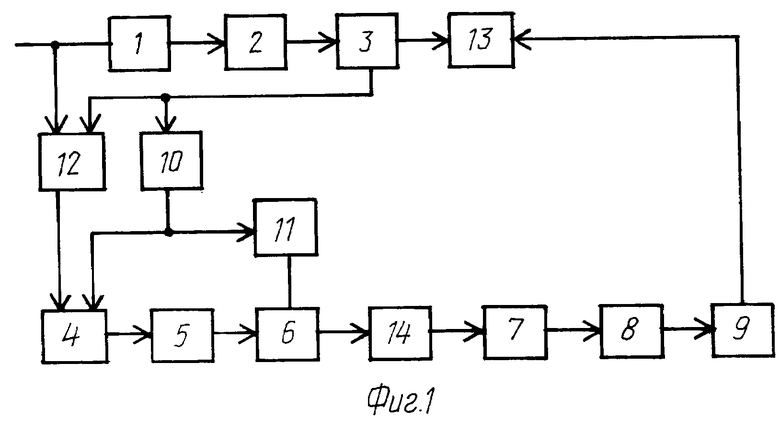

Структурная схема блока 4, реализующая указанный алгоритм, представлена на фиг. 3, где использованы следующие обозначения:

41 - блок сравнения с порогом,

42 - инвертор,

43 - элемент "И".

Блок 4 работает следующим образом. Напряжение с выхода блока 3 подается на блок 41, где оно сравнивается с порогом. Команды о превышении (непревышении) порога подается на блоки 7, 17 и 43, на второй вход которого подается команда от блока 14 через инвертор 42. С выхода блока 43 команда ("0" или "1") подается на блок 5.

В исходном режиме отсутствия синхронизации на выходе блока 4 формируется команда "0", которая запирает ключи 7 и 17. В этом случае на выходе блока 13 также присутствует "0", потому что дополнительный канал отключен от входа устройства. Команда "0", поступающая от блока 14, инвертируясь в блоке 42, превращается в команду "1". Таким образом на входах блока 43 присутствуют "0" и "1" и на его выходе формируется "0", который подается на блок 5. В этом случае блок 5 обеспечивает режим поиска (сканирования) по задержке. При превышении порога в блоке 41 формируется команда "1", которая открывает ключи 7 и 17. Если в этом случае в блоке 14 порог не превышен ("0" на его выходе), то на входы блока 43 поступают команды "1" и "1", а на выходе также формируется команда "1", которая поступая на блок 5, прекращает режим сканирования. В этом случае блок 4 принимает решение о правильной синхронизации полезным сигналом. Если на выходе блока 13 формируется "1", то на входах блока 43 присутствует "1" и "0", а на его выходе формируется "0". В этом случае блок 4 принимает решение о ложной синхронизации и переводит устройство в режим поиска.

Блок 5 может быть выполнен, например, в виде управляемого генератора тактовых частот. В режиме поиска по задержке, когда на его вход подается команда "0", он формирует тактовую частоту (fт+Δf), отличающуюся от тактовой частоты входного полезного сигнала fт на величину Δf. Введение расстройки Δf обеспечивает режим взаимного скольжения между входной и опорной кодовыми последовательностями.

При поступлении на вход блока 5 команды "1" в нем устанавливается частота fт, что обеспечивает синхронность тактовых частот кодовых последовательностей входного и опорного сигналов.

Блоки 18, 19, 20 обеспечивают выравнивание сигналов по задержке.

Устройство-прототип не отличает синхронизации по помехе от синхронизации по полезному сигналу, при этом при отсутствии полезного сигнала и воздействии мощной помехи вероятность ложной синхронизации близка к единице.

В заявляемом устройстве после фиксации превышения порога на первом этапе проводится дополнительная проверка, позволяющая выяснить, чем обусловлено превышение порога - полезным сигналом или помехой.

Эта проверка предполагает применение режекции полезного сигнала для исключения его из входной смеси, которая затем подвергается корреляционной обработке, при этом накопленное напряжение сравнивается с порогом.

В случае превышения порога на 2-м этапе, решение об окончании поиска не принимается. За счет реализации указанной проверки вероятность синхронизации по помехе в заявляемом устройстве значительно ниже, чем в прототипе.

Устройство поиска широкополосных сигналов по задержке относится к области радиотехники и может найти применение в системах связи с широкополосными сигналами. В устройстве после принятия решения о синхронизации полезным сигналом вводится дополнительная проверка, позволяющая выявить случаи ложной синхронизации по помехе. Достигаемый технический результат - повышение помехоустойчивости режима поиска по задержке. Устройство содержит три перемножителя, два полосовых фильтра, два амплитудных детектора, решающий блок, блок управления поиском, генератор кода, два ключа, режекторный фильтр, два фазовых модулятора, блок сравнения с порогом, ограничитель, четыре элемента задержки. 3 ил.

Устройство поиска широкополосных сигналов по задержке, содержащее первый амплитудный детектор, генератор кода, первый ключ, вход которого является входом устройства, последовательно соединенные второй перемножитель, режекторный фильтр и первый фазовый модулятор, последовательно соединенные второй амплитудный детектор, блок сравнения с порогом, выход которого соединен с одним из входов решающего блока, а также второй элемент задержки, выход которого соединен с другим входом первого фазового модулятора, отличающееся тем, что введены последовательно соединенные второй ключ, второй фазовый модулятор, ограничитель, выход которого соединен с другим входом второго перемножителя, при этом первый перемножитель последовательно соединен с первым полосовым фильтром, первым амплитудным детектором, решающим блоком, блоком управления поиском и генератором кода, выход которого соединен с другим входом первого перемножителя и через четвертый элемент задержки с другим входом второго фазового модулятора, первый ключ последовательно соединен с третьим элементом задержки и вторым перемножителем, первый фазовый модулятор последовательно соединен с третьим перемножителем, вторым полосовым фильтром и вторым амплитудным детектором, ограничитель последовательно соединен с вторым элементом задержки, другой выход решающего блока соединен с соответствующими входами первого и второго ключей, вход второго ключа соединен с выходом первого полосового фильтра, выход четвертого элемента задержки соединен через первый элемент задержки с другим входом третьего перемножителя, вход первого ключа соединен с входом первого перемножителя.

| RU 2000664 C, 07.09.1993 | |||

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2020762C1 |

| АДАПТИВНОЕ УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ЗАДЕРЖКОЙ ШИРОКОПОЛОСНОГО СИГНАЛА | 1990 |

|

RU2040856C1 |

| US 4355398, 19.10.1982 | |||

| UA 4627080, 02.12.1986 | |||

| US 4726043, 16.02.1988 | |||

| ТУЗОВ Г.И | |||

| Статистическая теория приема сложных сигналов | |||

| - М.: Советское радио, 1977, с.326. | |||

Авторы

Даты

2001-04-10—Публикация

1999-06-29—Подача