Изобретение относится к области вычислительной техники и интегральной электроники, а более конкретно - к интегральным логическим элементам СБИС.

Известен трехмерный интегральный логический элемент на комплементарных МОП-транзисторах (см. Bern Hoefflinger, Sie I. Liu, and Branislav Vajdic, A Three-Dimentional CMOS Design Metodology, IEEE Transactions of Electron Devices, Vol. ED-31, Num. 2, 1984, Fig. 2), содержащий полупроводниковую подложку первого типа проводимости с расположенными в ней сток-истоковыми областями транзисторов второго типа проводимости, полупроводниковую область второго типа проводимости, расположенную над слоем разделительного диэлектрика и содержащую сток-истоковые области транзисторов первого типа проводимости, слои тонкого диэлектрика, металлическую шину питания, соединенную с истоковыми областями транзисторов первого типа проводимости, металлическую шину нулевого потенциала, расположенную над истоковой областью транзистора второго типа проводимости и соединенную с ней, а также с полупроводниковой подложкой первого типа проводимости, две входные поликремниевые шины прямоугольной формы, являющиеся затворами транзисторов второго типа проводимости и расположенных над ними транзисторов первого типа проводимости, выходную металлическую шину, расположенную над областями элемента и соединенную со стоковыми областями транзисторов первого типа проводимости и стоковой областью транзистора второго типа проводимости.

Недостатками являются нерациональное использование площади кристалла, обусловленное горизонтальной ориентацией каналов транзисторов; низкая температурная устойчивость, обусловленная наличием слоя разделительного диэлектрика между полупроводниковой областью второго типа проводимости, содержащей сток-истоковые области транзисторов первого типа проводимости, и подложкой; низкое быстродействие вследствие изоляции сток-истоковых областей транзисторов второго типа проводимости, расположенных в подложке первого типа проводимости, обратно смещенными p-n-переходами, а также вследствие ограничения длины каналов транзисторов минимальным литографическим размером и эффектом смыкания переходов сток-подложка и исток-подложка.

Функциональным аналогом заявляемого объекта является интегральный логический элемент на комплементарных МДП-транзисторах (см. Проектирование специализированных КМОП БИС на основе БМК 5501ХМ2. Уч. пособие /Под ред. В. В. Ермака. - М.: МГИЭТ (ТУ), 1996. 180 с.: ил. - стр.75,54, рис. П2.1б, стр. 51, рис. П1.12), содержащий полупроводниковую подложку второго типа проводимости с расположенными в ней сток-истоковыми областями транзисторов первого типа проводимости, область кармана первого типа проводимости с расположенными в ней сток-истоковыми областями транзисторов второго типа проводимости, охранные кольцеобразные области первого типа проводимости, слои тонкого диэлектрика, слои разделительного диэлектрика, металлическую шину питания, расположенную над областями транзисторов первого типа проводимости и соединенную с истоковыми областями первого и пятого транзисторов первого типа проводимости, а также с полупроводниковой подложкой второго типа проводимости, металлическую шину нулевого потенциала, расположенную над областями транзисторов второго типа проводимости и соединенную с истоковыми областями четвертого и восьмого транзисторов второго типа проводимости, а также с областью кармана второго типа проводимости, входные поликремниевые прямоугольные шины, являющиеся затворами транзисторов первого и второго типов проводимости, три транзитные поликремниевые шины и выходную металлическую шину, расположенную над областями элемента и соединенную со стоковыми областями второго и шестого транзисторов первого типа проводимости, а также третьего и седьмого транзисторов второго типа проводимости.

Недостатками являются нерациональное использование площади кристалла, обусловленное планарным расположением транзисторов, горизонтальной ориентацией каналов транзисторов, а также наличием охранных областей первого типа проводимости кольцеобразной формы и пассивных областей в зоне аппроксимирующего прямоугольника элемента; низкое быстродействие вследствие изоляции сток-истоковых областей транзисторов обратно смещенными p-n-переходами, а также вследствие ограничения длины каналов транзисторов минимальным литографическим размером и эффектом смыкания переходов сток-подложка и исток-подложка.

Из известных наиболее близким по технической сущности к заявляемому объекту является интегральный элемент на полевых транзисторах с управляющими переходами Шоттки (см. Шур М. Современные приборы на основе арсенида галлия: Пер. с англ. - М.: Мир, 1991. - 632 с., - с. 472, рис. 9.6.5), содержащий области стоков, истоков и каналов четырех транзисторов второго типа проводимости, металлические затворы Шоттки транзисторов второго типа проводимости, четыре входные металлические шины, соединенные с затворами Шоттки транзисторов второго типа проводимости, выходную металлическую шину, соединенную со стоковыми областями первого и третьего транзисторов второго типа проводимости, слои разделительного диэлектрика, металлическую шину нулевого потенциала, металлическую шину питания, полупроводниковую полуизолирующую подложку, резистивную область нагрузочного резистора второго типа проводимости, первую приконтактную область нагрузочного резистора второго типа проводимости, соединенную с металлической шиной питания, вторую приконтактную область нагрузочного резистора второго типа проводимости, соединенную с выходной металлической шиной, причем металлическая шина нулевого потенциала соединена с истоковыми областями второго и четвертого транзисторов второго типа проводимости, длины каналов транзисторов второго типа проводимости определяются длинами металлических затворов Шоттки, имеющих прямоугольную форму, сток-истоковые области транзисторов второго типа проводимости расположены планарно в полупроводниковой полуизолирующей подложке, каналы транзисторов второго типа проводимости имеют горизонтальную ориентацию.

Недостатками являются нерациональное использование площади кристалла, обусловленное планарным расположением транзисторов, горизонтальной ориентацией каналов транзисторов, а также наличием пассивных областей в зоне аппроксимирующего прямоугольника элемента; низкая помехоустойчивость и высокая потребляемая мощность и энергия переключения вследствие использования полупроводникового нагрузочного резистора.

Задачей предлагаемого изобретения является сокращение занимаемой площади, повышение быстродействия элемента, сокращение потребляемой мощности и энергии переключения.

Для достижения необходимого технического результата в интегральный логический элемент, содержащий области стоков, истоков и каналов четырех транзисторов второго типа проводимости, металлические затворы Шоттки транзисторов второго типа проводимости, четыре входные металлические шины, соединенные с затворами Шоттки транзисторов второго типа проводимости, выходную металлическую шину, соединенную со стоковыми областями первого и третьего транзисторов второго типа проводимости, слои разделительного диэлектрика, металлическую шину нулевого потенциала, металлическую шину питания, введены полупроводниковая подложка второго типа проводимости, являющаяся совмещенной истоковой областью второго и четвертого транзисторов второго типа проводимости и соединенная по всей свободной поверхности с металлической шиной нулевого потенциала, области стоков, истоков и каналов четырех транзисторов первого типа проводимости, металлические затворы Шоттки транзисторов первого типа проводимости, соединенные с входными металлическими шинами, металлическая шина, соединенная с областями первого типа проводимости, являющимися истоками шестого и восьмого и стоками пятого и седьмого транзисторов первого типа проводимости, полупроводниковая подложка первого типа проводимости, являющаяся совмещенной истоковой областью пятого и седьмого транзисторов первого типа проводимости и соединенная по всей свободной поверхности с металлической шиной питания, причем транзисторы первого и второго типов проводимости выполнены в виде двух призм с квадратными основаниями, каждое из которых имеет площадь, равную площади одного контактного окна, при этом каждая призма содержит по два транзистора второго типа проводимости и по два транзистора первого типа проводимости, расположенные друг над другом и имеющие вертикальную ориентацию каналов, входная металлическая шина, соединенная с затворами Шоттки пятого транзистора первого типа проводимости и четвертого транзистора второго типа проводимости, расположена в семи слоях металлизации, входная металлическая шина, соединенная с затворами Шоттки шестого транзистора первого типа проводимости и первого транзистора второго типа проводимости, расположена в трех слоях металлизации, входная металлическая шина, соединенная с затворами Шоттки седьмого транзистора первого типа проводимости и третьего транзистора второго типа проводимости, расположена в пяти слоях металлизации, входная металлическая шина, соединенная с затворами Шоттки восьмого транзистора первого типа проводимости и второго транзистора второго типа проводимости, расположена в пяти слоях металлизации, металлические затворы Шоттки транзисторов первого и второго типов проводимости имеют кольцеобразную форму, длины каналов транзисторов первого и второго типов проводимости определяются толщиной металлических затворов, входные металлические шины и металлическая шина, соединенная с областями первого типа проводимости, являющимися истоками шестого и восьмого и стоками пятого и седьмого транзисторов первого типа проводимости, расположены в тех же слоях, что и области транзисторов первого и второго типов проводимости, металлические шины расположены в девяти слоях, изолированных слоями разделительного диэлектрика, взаимное соединение металлических шин, расположенных в различных слоях, осуществляется посредством металлических межслойных переходов, расположенных друг над другом.

Сравнивая предлагаемое устройство с прототипом, видим, что оно содержит новые признаки, то есть соответствует критерию новизны. Проводя сравнение с аналогами, приходим к выводу, что предлагаемое устройство соответствует критерию "существенные отличия", так как в аналогах не обнаружены предъявляемые новые признаки. За счет введения в конструкцию двух полупроводниковых подложек с различными типами проводимости, девяти уровней металлических соединений, причем полупроводниковые области транзисторов и металлические соединения расположены в одних и тех же слоях, металлической шины питания, покрывающей всю свободную поверхность полупроводниковой подложки первого типа проводимости и соединенной с ней по всей ее площади, металлической шины нулевого потенциала, покрывающей всю свободную поверхность полупроводниковой подложки второго типа проводимости и соединенной с ней по всей ее площади, металлических межслойных переходов, расположенных друг над другом в пределах площади одного контактного окна, комплементарных полевых транзисторов с управляющими переходами Шоттки, выполненных в виде двух призм с квадратными основаниями, каждое из которых имеет площадь, равную площади одного контактного окна, при этом каждая призма содержит по два транзистора второго типа проводимости и по два транзистора первого типа проводимости, расположенные друг над другом и имеющие вертикальную ориентацию каналов, причем длины каналов транзисторов первого и второго типов проводимости определяются толщиной металлических затворов Шоттки, получен положительный эффект, заключающийся в сокращении занимаемой площади, повышении быстродействия, уменьшении потребляемой мощности и энергии переключения устройств на основе предлагаемого элемента.

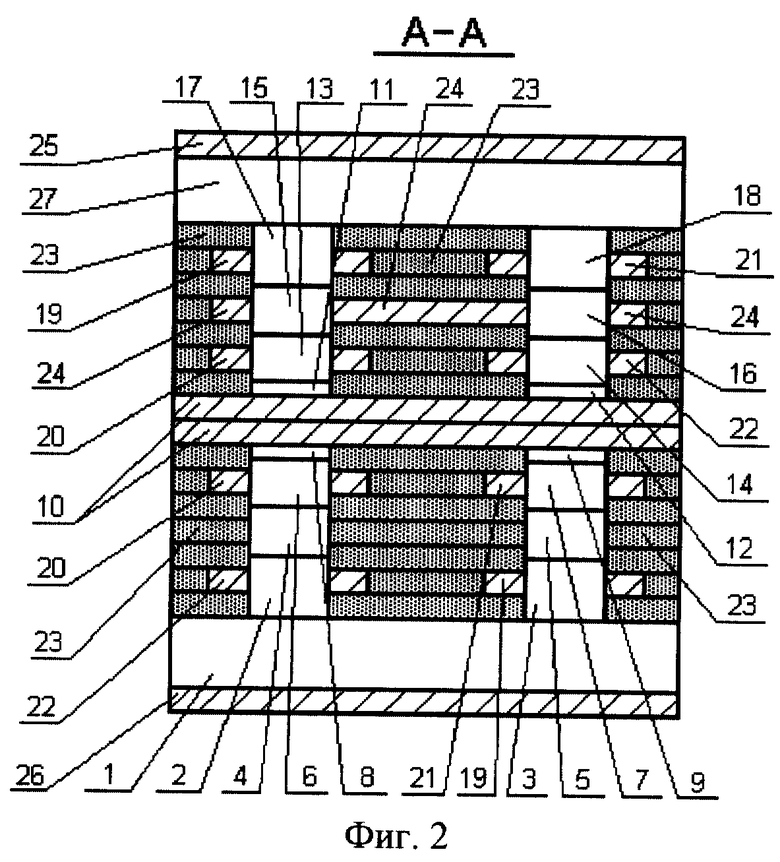

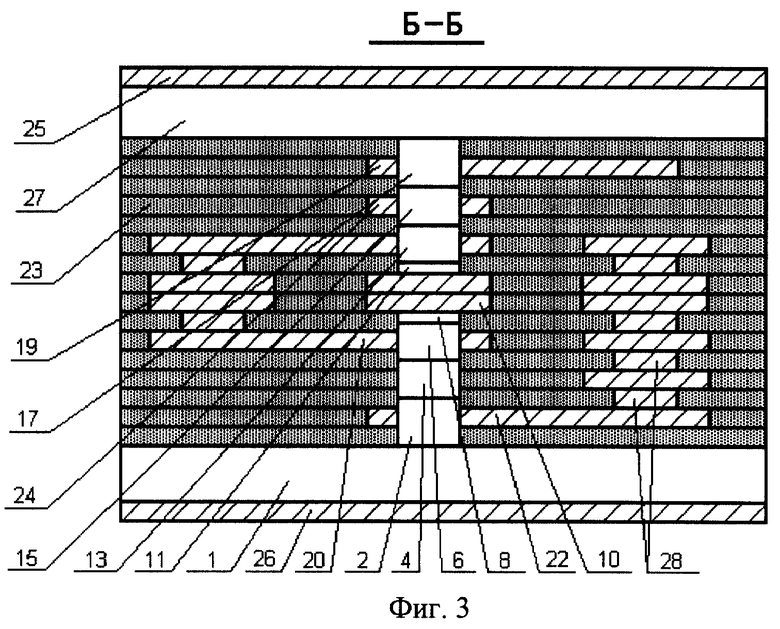

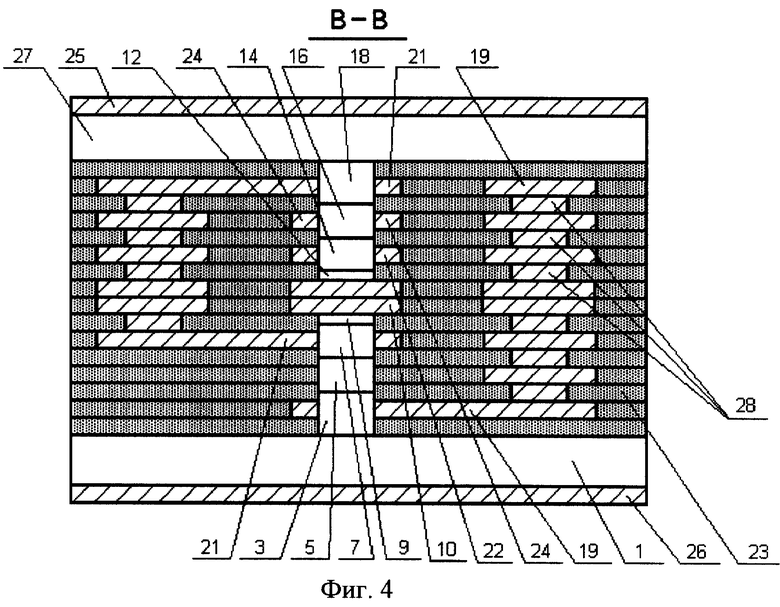

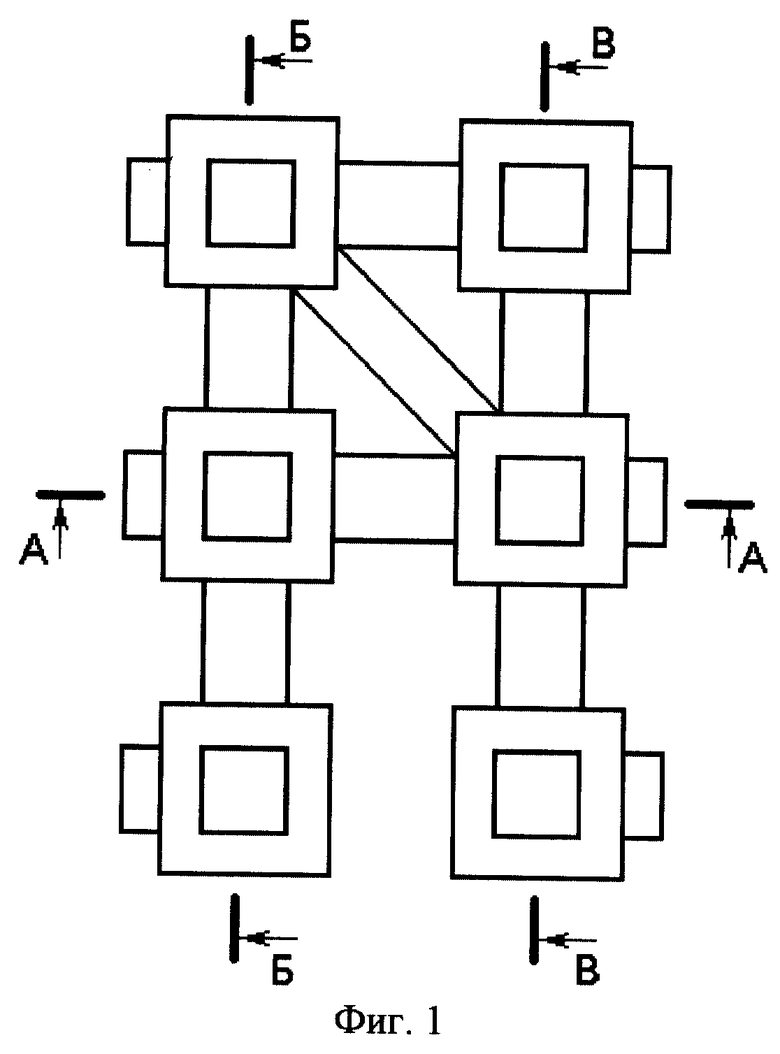

На фиг. 1 приведена топология предлагаемого интегрального логического элемента. На фиг. 2 приведено сечение предлагаемого интегрального логического элемента по областям восьми транзисторов. На фиг. 3 приведено сечение предлагаемого интегрального логического элемента по областям первого, второго, пятого и шестого транзисторов и двум входным шинам, соединенным с затворами этих транзисторов. На фиг. 4 приведено сечение предлагаемого интегрального логического элемента по областям третьего, четвертого, седьмого и восьмого транзисторов и двум входным шинам, соединенным с затворами этих транзисторов.

Интегральный логический элемент содержит полупроводниковую подложку второго типа проводимости 1, расположенные над ней области каналов второго и четвертого транзисторов второго типа проводимости 2, 3, расположенные над ними области второго типа проводимости 4, 5, являющиеся стоками второго и четвертого и истоками первого и третьего транзисторов второго типа проводимости, расположенные над ними области каналов первого и третьего транзисторов второго типа проводимости 6, 7, расположенные над ними области второго типа проводимости 8, 9, являющиеся стоками первого и третьего транзисторов второго типа проводимости, выходную металлическую шину 10, расположенную над стоковыми областями первого и третьего транзисторов второго типа проводимости 8, 9 и соединенную с ними, области первого типа проводимости 11, 12, являющиеся стоками шестого и восьмого транзисторов первого типа проводимости, расположенные над выходной металлической шиной 10 и соединенные с ней, расположенные над ними области каналов шестого и восьмого транзисторов первого типа проводимости 13, 14, расположенные над ними области первого типа проводимости 15, 16, являющиеся истоками шестого и восьмого и стоками пятого и седьмого транзисторов первого типа проводимости, расположенные над ними области каналов пятого и седьмого транзисторов первого типа проводимости 17, 18, входную металлическую шину 19, расположенную в семи слоях металлизации и соединенную с затворами пятого транзистора первого типа проводимости и четвертого транзистора второго типа проводимости, входную металлическую шину 20, расположенную в трех слоях металлизации и соединенную с затворами шестого транзистора первого типа проводимости и первого транзистора второго типа проводимости, входную металлическую шину 21, расположенную в пяти слоях металлизации и соединенную с затворами седьмого транзистора первого типа проводимости и третьего транзистора второго типа проводимости, входную металлическую шину 22, расположенную в пяти слоях металлизации и соединенную с затворами восьмого транзистора первого типа проводимости и второго транзистора второго типа проводимости, слои разделительного диэлектрика 23, металлическую шину 24, соединенную с областями первого типа проводимости 15, 16, являющимися истоками шестого и восьмого и стоками пятого и седьмого транзисторов первого типа проводимости, металлическую шину питания 25, металлическую шину нулевого потенциала 26, соединенную с подложкой второго типа проводимости 1, полупроводниковую подложку первого типа проводимости 27, расположенную над областями каналов пятого и седьмого транзисторов первого типа проводимости 17, 18 и являющуюся общим истоком этих транзисторов, металлические межслойные переходы 28.

Работает устройство следующим образом. При подаче напряжения питания на металлическую шину 25, соединенную с полупроводниковой подложкой первого типа проводимости 27, относительно металлической шины нулевого потенциала 26, соединенной с полупроводниковой подложкой второго типа проводимости 1, и действующих высоких уровнях напряжения логической единицы на входных металлических шинах 20 и 22, расположенных за счет использования металлических межслойных переходов 28 в трех и пяти слоях металлизации, соответственно, изолированных друг от друга слоями разделительного диэлектрика 23 и соединенных с затворами Шоттки к полупроводниковым областям вертикальных каналов шестого и восьмого транзисторов первого типа проводимости 13, 14 и к полупроводниковым областям вертикальных каналов первого и второго транзисторов второго типа проводимости 6, 2, соединенных последовательно с общей сток-истоковой областью 4, или на входных металлических шинах 19 и 21, расположенных за счет использования металлических межслойных переходов 28 в семи и пяти слоях металлизации, соответственно, изолированных друг от друга слоями разделительного диэлектрика 23 и соединенных с затворами Шоттки к полупроводниковым областям вертикальных каналов пятого и седьмого транзисторов первого типа проводимости 17, 18 и к полупроводниковым областям вертикальных каналов третьего и четвертого транзисторов второго типа проводимости 7, 3, соединенных последовательно с общей сток-истоковой областью 5, первый и второй транзисторы второго типа проводимости или третий и четвертый транзисторы второго типа проводимости открыты, а шестой и восьмой транзисторы первого типа проводимости или пятый и седьмой транзисторы первого типа проводимости, стоковые области 15, 16 которых соединены металлической шиной 24, закрыты, в результате чего на выходной металлической шине 10, соединенной с полупроводниковыми областями второго типа проводимости 8, 9, являющимися стоками первого и третьего транзисторов второго типа проводимости, и с полупроводниковыми областями первого типа проводимости 11, 12, являющимися стоками шестого и восьмого транзисторов первого типа проводимости, действует низкий уровень напряжения логического нуля.

При подаче низкого напряжения логического нуля хотя бы на одну из входных металлических шин 20, 22 и хотя бы на одну из входных металлических шин 19, 21, первый или/и второй транзисторы второго типа проводимости и третий или/и четвертый транзисторы второго типа проводимости закроются, а шестой или/и восьмой транзисторы первого типа проводимости и пятый или/и седьмой транзисторы первого типа проводимости откроются, что приведет к установлению на выходной металлической шине 10 высокого уровня напряжения логической единицы.

Таким образом, предлагаемое устройство представляет собой четырехвходовый интегральный логический элемент И-ИЛИ-НЕ на комплементарных нормально закрытых полевых транзисторах с управляющими переходами Шоттки.

Выполнение комплементарных полевых транзисторов с управляющими переходами Шоттки в виде полупроводниковых призм с квадратным основанием позволяет размещать четыре транзистора (два транзистора первого типа проводимости и два - второго типа проводимости) на площади, равной площади одного контактного окна. Полупроводниковые области транзисторов и металлические соединения расположены в девяти слоях, причем в одних и тех же слоях расположены как полупроводниковые области, так и металлические соединения. Межслойные металлические переходы позволяют осуществлять соединение нескольких слоев металлизации в пределах площади одного контактного окна, что повышает эффективность использования площади и объема кристалла более чем в 10 раз по сравнению с интегральными схемами на основе планарных элементов. Использование кольцевых затворов Шоттки, вертикальной ориентации каналов транзисторов, а также боковой изоляции слоями разделительного диэлектрика позволяет сократить длины каналов и паразитные емкости, более чем в 5 раз повысить быстродействие и более чем на порядок сократить энергию переключения по сравнению с планарными интегральными логическими элементами. Использование двух полупроводниковых подложек с различными типами проводимости и металлических шин питания и нулевого потенциала, покрывающих всю свободную поверхность подложек, позволяет уменьшить плотности токов в шинах питания и нулевого потенциала и повысить эффективность отвода тепла от кристалла.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1995 |

|

RU2094944C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1996 |

|

RU2115998C1 |

| ИНТЕГРАЛЬНЫЙ ПОЛЕВОЙ ТРАНЗИСТОР ШОТТКИ СО СТАТИЧЕСКОЙ ИНДУКЦИЕЙ | 2000 |

|

RU2183885C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1994 |

|

RU2079986C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1992 |

|

RU2062528C1 |

| БАЗОВЫЙ ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1667574A1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ИЛИ НА КВАНТОВЫХ ЭФФЕКТАХ | 2004 |

|

RU2279155C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "ИЛИ-НЕ" НА КВАНТОВЫХ ЭФФЕКТАХ | 2004 |

|

RU2278445C1 |

| ИНТЕГРАЛЬНЫЙ БИПОЛЯРНЫЙ МАГНИТОТРАНЗИСТОР | 2001 |

|

RU2204144C2 |

| ПОЛУПРОВОДНИКОВЫЙ ПРИБОР С ОТРИЦАТЕЛЬНЫМ СОПРОТИВЛЕНИЕМ (ВАРИАНТЫ) | 2012 |

|

RU2513644C1 |

Изобретение относится к вычислительной технике и интегральной электронике, а более конкретно - к интегральным логическим элементам СБИС и, в частности, к логическому элементу И-ИЛИ-НЕ на комплиментарных нормально закрытых полевых транзисторах с управляющими переходами Шоттки. Для сокращения занимаемой площади, повышения быстродействия, уменьшения потребляемой мощности и энергии переключения в интегральный логический элемент, содержащий области стоков, истоков и каналов четырех транзисторов второго типа проводимости, металлические затворы Шоттки транзисторов второго типа проводимости, четыре входные металлические шины, соединенные с затворами Шоттки транзисторов второго типа проводимости, выходную металлическую шину, соединенную со стоковыми областями первого и третьего транзисторов второго типа проводимости, слоя разделительного диэлектрика, металлическую шину нулевого потенциала, металлическую шину питания, введены полупроводниковая подложка второго типа проводимости, являющаяся совмещенной истоковой областью второго и четвертого транзисторов второго типа проводимости и соединенная по всей свободной поверхности с металлической шиной нулевого потенциала, области стоков, истоков и каналов четырех транзисторов первого типа проводимости, металлические затворы Шоттки транзисторов первого типа проводимости, соединенные с входными металлическими шинами, металлическая шина, соединенная с областями первого типа проводимости, являющимися истоками шестого и восьмого и стоками пятого и седьмого транзисторов первого типа проводимости, полупроводниковая подложка первого типа проводимости, являющаяся совмещенной истоковой областью пятого и седьмого транзисторов первого типа проводимости и соединенная по всей свободной поверхности с металлической шиной питания, причем транзисторы выполнены в виде двух призм с квадратными основаниями, каждое из которых имеет площадь, равную площади одного контактного окна, при этом каждая призма содержит по два транзистора второго типа проводимости и по два транзистора первого типа проводимости, расположенных друг над другом и имеющих вертикальную ориентацию каналов, металлические затворы Шоттки имеют кольцеобразную форму, длины каналов транзисторов определяются толщиной металлических затворов, металлические шины расположены в девяти слоях, изолированных слоями разделительного диэлектрика, причем входные металлические шины расположены в тех же слоях, что и полупроводниковые области транзисторов. 4 ил.

Интегральный логический элемент И-ИЛИ-НЕ, содержащий области стоков, истоков и каналов четырех транзисторов второго типа проводимости, металлические затворы Шоттки транзисторов второго типа проводимости, четыре входные металлические шины, соединенные с затворами Шоттки транзисторов второго типа проводимости, выходную металлическую шину, соединенную со стоковыми областями первого и третьего транзисторов второго типа проводимости, слои разделительного диэлектрика, металлическую шину нулевого потенциала, металлическую шину питания, отличающийся тем, что в него введены полупроводниковая подложка второго типа проводимости, являющаяся совмещенной истоковой областью второго и четвертого транзисторов второго типа проводимости и соединенная по всей свободной поверхности с металлической шиной нулевого потенциала, области стоков, истоков и каналов четырех транзисторов первого типа проводимости, металлические затворы Шоттки транзисторов первого типа проводимости, соединенные с входными металлическими шинами, металлическая шина, соединенная с областями первого типа проводимости, являющимися истоками шестого и восьмого и стоками пятого и седьмого транзисторов первого типа проводимости, полупроводниковая подложка первого типа проводимости, являющаяся совмещенной истоковой областью пятого и седьмого транзисторов первого типа проводимости и соединенная по всей свободной поверхности с металлической шиной питания, причем транзисторы первого и второго типов проводимости выполнены в виде двух призм с квадратными основаниями, каждое из которых имеет площадь, контактного окна, при этом каждая призма содержит по два транзистора второго типа проводимости и по два транзистора первого типа проводимости, расположенные друг над другом и имеющие вертикальную ориентацию каналов, входная металлическая шина, соединенная с затворами Шоттки пятого транзистора первого типа проводимости и четвертого транзистора второго типа проводимости, расположена в семи слоях металлизации, входная металлическая шина, соединенная с затворами Шоттки шестого транзистора первого типа проводимости и первого транзистора второго типа проводимости, расположена в трех слоях металлизации, входная металлическая шина, соединенная с затворами Шоттки седьмого транзистора первого типа проводимости и третьего транзистора второго типа проводимости, расположена в пяти слоях металлизации, входная металлическая шина, соединенная с затворами Шоттки восьмого транзистора первого типа проводимости и второго транзистора второго типа проводимости, расположена в пяти слоях металлизации, металлические затворы Шоттки транзисторов первого и второго типов проводимости имеют кольцеобразную форму, длины каналов транзисторов первого и второго типов проводимости определяются толщиной металлических затворов, входные металлические шины и металлическая шина, соединенная с областями первого типа проводимости, являющимися истоками шестого и восьмого и стоками пятого и седьмого транзисторов первого типа проводимости, расположены в тех же слоях, что и области транзисторов первого и второго типов проводимости, металлические шины расположены в девяти слоях, изолированных слоями разделительного диэлектрика, взаимное соединение металлических шин, расположенных в различных слоях, осуществляется посредством металлических межслойных переходов, расположенных друг над другом.

| ШУР М | |||

| Современные приборы на основе арсенида галия | |||

| - М.: Мир, 1991, с | |||

| Устройство для нахождения генерирующих точек контактного детектора | 1923 |

|

SU472A1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1996 |

|

RU2115998C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1995 |

|

RU2094944C1 |

| EP 0476341 А1, 22.08.1991. | |||

Авторы

Даты

2001-05-10—Публикация

2000-01-25—Подача