Изобретение относится к области вычислительной техники и интегральной электроники, а более конкретно - к интегральным логическим элементам БИС.

Известен интегральный логический элемент на nМДП-транзисторах [1], содержащий полупроводниковую подложку первого типа проводимости с расположенными в ней сток-истоковыми областями транзисторов второго типа проводимости, слой разделительного диэлектрика, слои тонкого диэлектрика, металлическую шину питания, расположенную над стоковой областью нагрузочного транзистора и соединенную с ней, металлическую шину нулевого потенциала, полупроводниковый слой встроенного канала нагрузочного транзистора второго типа проводимости, поликремниевый затвор нагрузочного транзистора, входные поликремниевые прямоугольные шины, являющиеся затворами ключевых транзисторов и выходную металлическую шину.

Недостатками являются нерациональное использование площади кристалла, обусловленное наличием пассивных областей в зоне аппроксимирующего прямоугольника элемента и прямоугольной формой входных поликремниевых шин, низкие быстродействие и нагрузочная способность для определенной площади аппроксимирующего прямоугольника элемента, обусловленные малым отношением ширины к длине каналов ключевых транзисторов и конфигурацией канала нагрузочного транзистора, сложность автоматизированного проектирования и большая занимаемая площадь узлов на основе данного логического элемента.

Функциональным аналогом заявляемого объекта является интегральный логический элемент на КМОП-транзисторах [2], содержащий полупроводниковую подложку первого типа проводимости с расположенными в ней сток-истоковыми областями транзисторов второго типа проводимости, полупроводниковую область второго типа проводимости, расположенную над слоем разделительного диэлектрика и содержащую сток-истоковые области транзисторов первого типа проводимости, слои тонкого диэлектрика, металлическую шину питания, соединенную с истоковыми областями транзисторов первого типа проводимости, металлическую шину нулевого потенциала, расположенную над истоковой областью транзистора второго типа проводимости и соединенную с ней, а также с полупроводниковой подложкой первого типа проводимости, две входные поликремниевые шины прямоугольной формы, являющиеся затворами транзисторов второго типа проводимости и расположенных над ними транзисторов первого типа проводимости, выходную металлическую шину, расположенную над областями элемента и соединенную со стоковыми областями транзисторов первого типа проводимости и стоковой областью транзистора второго типа проводимости.

Недостатками являются нерациональное использование площади кристалла, обусловленное прямоугольной формой входных поликремниевых шин, и сложность автоматизированного проектирования узлов на основе данного элемента, обусловленная фиксированным расположением входных и выходных шин, а также отсутствием транзитной (транзитных) шин.

Из известных наиболее близким по технической сущности к заявляемому объекту является интегральный логический элемент на КМОП-транзисторах [3], содержащий полупроводниковую подложку первого типа проводимости с расположенными в ней сток-истоковыми областями транзисторов второго типа проводимости, полупроводниковую область второго типа проводимости с расположенными в ней сток-истоковыми областями транзисторов первого типа проводимости, слои разделительного диэлектрика, слои тонкого диэлектрика, зону питания, содержащую металлическую шину питания, соединенную с полупроводниковой областью второго типа проводимости, зону нулевого потенциала, содержащую металлическую шину нулевого потенциала, соединенную с полупроводниковой подложкой первого типа проводимости, две входные зоны, каждая из которых содержит транзистор первого типа проводимости, расположенный в полупроводниковой области второго типа проводимости, и транзистор второго типа проводимости, расположенный в подложке первого типа проводимости, входную поликремниевую шину прямоугольной формы, являющуюся затвором транзистора первого типа проводимости, расположенного в полупроводниковой области второго типа проводимости, и затвором транзистора второго типа проводимости, расположенного в подложке первого типа проводимости, выходную зону, содержащую выходную поликремниевую шину, соединенную со стоками первого и второго транзисторов второго типа проводимости и стоком первого транзистора первого типа проводимости, исток которого соединен со стоком второго транзистора первого типа проводимости, исток второго транзистора первого типа проводимости соединен с шиной нулевого потенциала, а истоки транзисторов второго типа проводимости соединены с шиной питания, зону транзита, содержащую транзитную поликремниевую шину, соединенную с поликремниевой выходной шиной, металлическую П-образную выходную шину, перпендикулярную поликремниевым шинам, причем расположенные между шинами питания и нулевого потенциала входные, выходная и транзитная зоны имеют одинаковые размеры.

Недостатками логического элемента прототипа являются нерациональное использование площади кристалла, обусловленное наличием зон питания и нулевого потенциала, пониженное быстродействие, обусловленное задержками в поликремниевых входных, выходных и транзитных шинах.

Задача изобретения - дальнейшее сокращение занимаемой площади, повышение быстродействия и помехоустойчивости элемента.

Для достижения необходимого технического результата в интегральный логический элемент, содержащий полупроводниковую подложку первого типа проводимости с расположенными в ней сток-истоковыми областями транзисторов второго типа проводимости, полупроводниковую область второго типа проводимости, расположенную над слоем разделительного диэлектрика и содержащую сток-истоковые области транзисторов первого типа проводимости, слои тонкого диэлектрика, зону питания, содержащую металлическую шину питания, соединенную с истоковыми областями транзисторов первого типа проводимости, зону нулевого потенциала, содержащую металлическую шину нулевого потенциала, расположенную над истоковой областью транзистора второго типа проводимости и соединенную с ней, а также с полупроводниковой подложкой первого типа проводимости, введены входная зона, содержащая транзистор первого типа проводимости, расположенный в полупроводниковой области второго типа проводимости над слоем разделительного диэлектрика, транзистор второго типа проводимости, расположенный в полупроводниковой подложке первого типа проводимости, входную поликремниевую шину, расположенную параллельно металлическим шинам питания и нулевого потенциала, выполненную в виде буквы S в зеркальном отображении и являющуюся затвором транзистора первого типа проводимости, расположенного в полупроводниковой области второго типа проводимости над слоем разделительного диэлектрика, и затвором транзистора второго типа проводимости, расположенного в полупроводниковой подложке первого типа проводимости, входная зона, содержащая транзистор первого типа проводимости, расположенный в полупроводниковой области второго типа проводимости над слоем разделительного диэлектрика, транзистор второго типа проводимости, расположенный в полупроводниковой подложке первого типа проводимости, входную поликремниевую шину, расположенную параллельно металлическим шинам питания и нулевого потенциала, выполненную в виде буквы S, являющуюся затвором транзистора первого типа проводимости, расположенного в полупроводниковой области второго типа проводимости над слоем разделительного диэлектрика, и затвором транзистора второго типа проводимости, расположенного в полупроводниковой подложке первого типа проводимости, выходная зона, содержащая выходную поликремниевую шину, расположенную параллельно металлическим шинам питания и нулевого потенциала и выполненную в виде буквы S, выходная металлическая шина прямоугольной формы, расположенная над областями элемента перпендикулярно металлическим шинам питания и нулевого потенциала и соединенная с выходной поликремниевой шиной, а также со стоковыми областями транзисторов первого типа проводимости и стоковой областью транзистора второго типа проводимости, зона транзита, содержащая транзитную поликремниевую шину, расположенную параллельно металлическим шинам питания и нулевого потенциала и выполненную в виде буквы S в зеркальном отображении, причем входные, выходная и транзитная зоны имеют одинаковые размеры, а условные границы входных зон, транзитной зоны, зон питания и нулевого потенциала пересекают контактные окна, соединяющие металлическую шину питания и выходную металлическую шину с областями элемента.

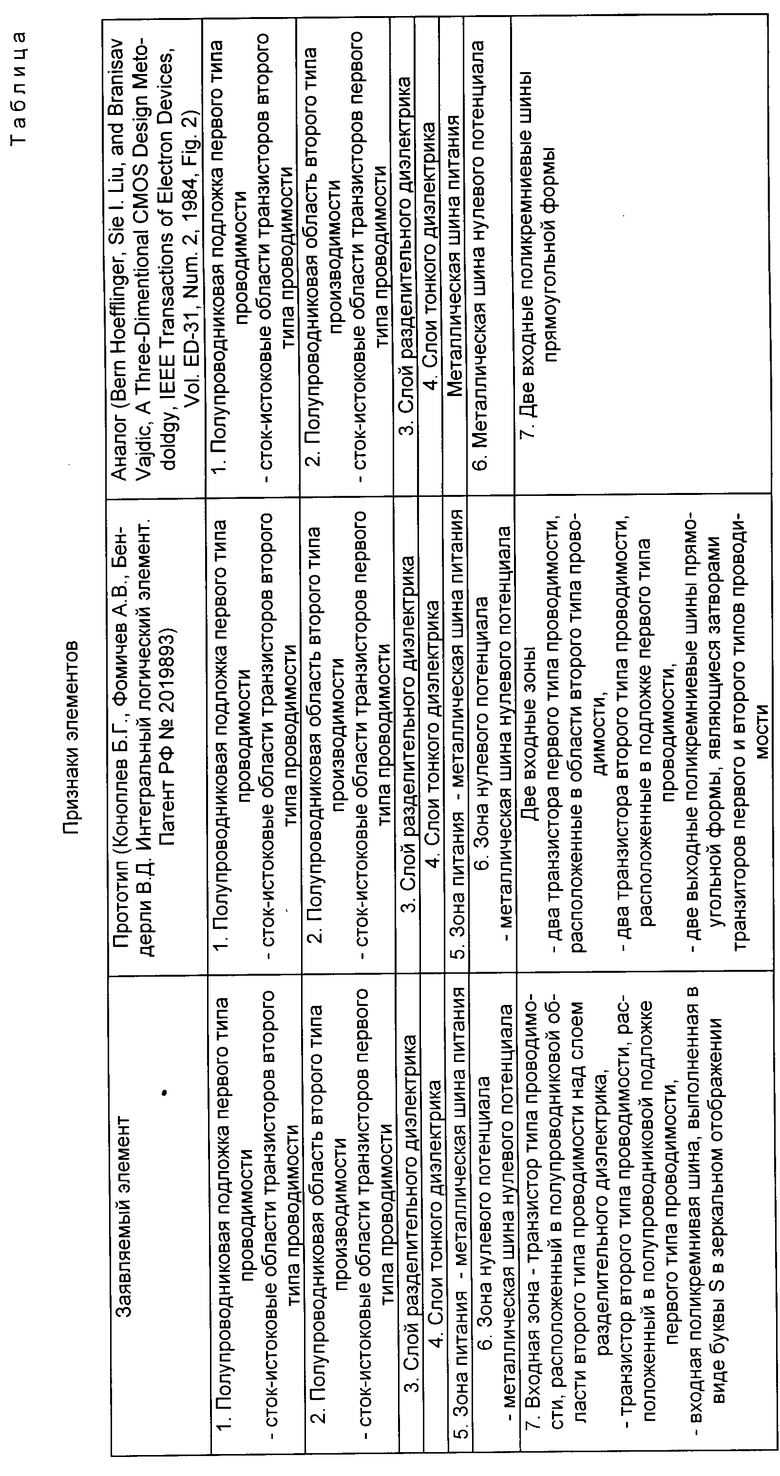

Для проведения сравнительного анализа заявляемого устройства, прототипа и аналога расположим их признаки в виде таблицы.

Сравнивая предлагаемое устройство с прототипом, видим, что оно содержит новые признаки, т.е. соответствует критерию новизны. Проводя сравнение с аналогами, приходим к выводу, что предлагаемое устройство соответствует критерию "существенные отличия", так как в аналогах не обнаружены предъявляемые новые признаки. За счет введения в конструкцию электрически и топологически совместимых входных, выходной и транзитной зон условные границы которых пересекают контактные окна, соединяющие металлическую шину питания и выходную металлическую шину с областями элемента, получен положительный эффект, заключающийся в сокращении занимаемой площади, повышении быстродействия и помехоустойчивости устройств на основе предлагаемого элемента.

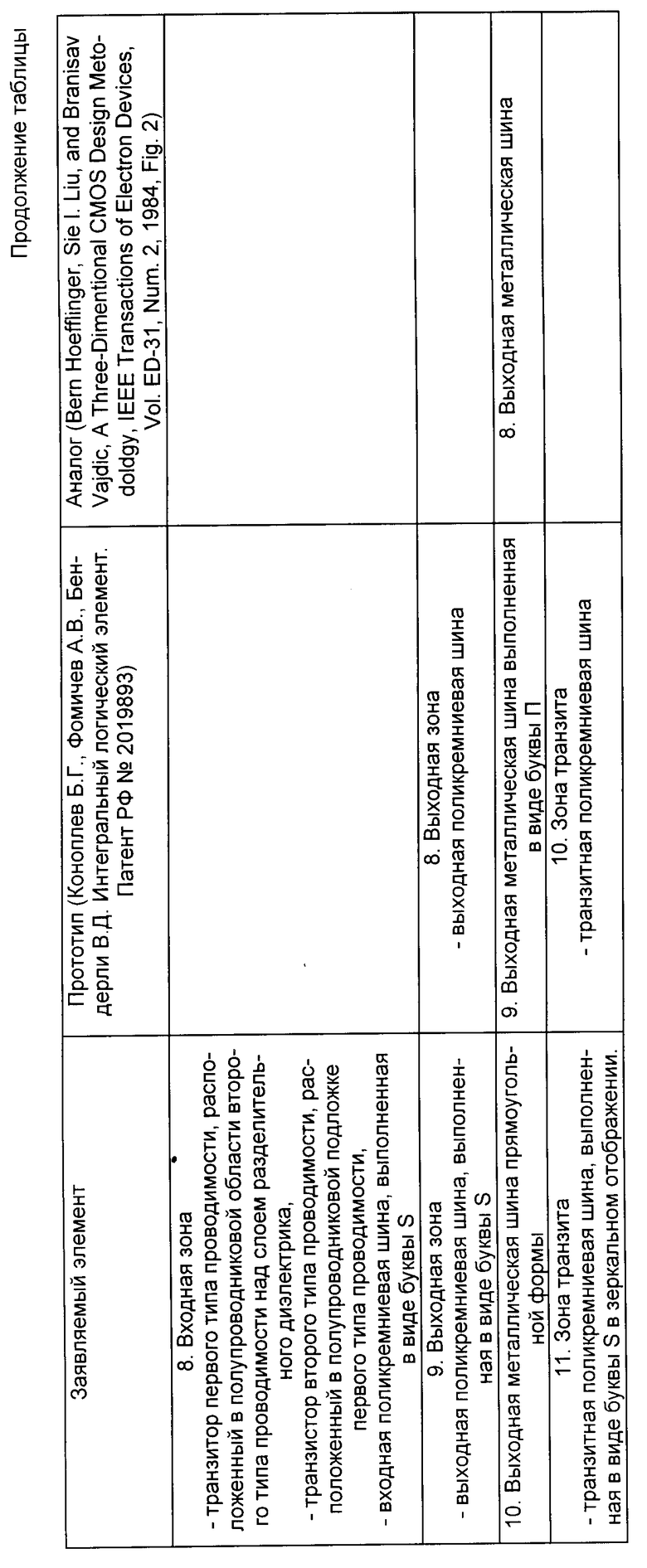

На чертеже приведены топология и структура предлагаемого интегрального логического элемента. Он содержит полупроводниковую подложку первого типа проводимости 1 с расположенными в ней сток-истоковыми областями транзисторов второго типа проводимости 2 - 4, полупроводниковую область второго типа проводимости 5, расположенную над слоем разделительного диэлектрика 6 и содержащую сток-истоковые области транзисторов первого типа проводимости 7 - 9, слои тонкого диэлектрика 10, зону питания, содержащую металлическую шину питания 11, соединенную с истоковыми областями транзисторов первого типа проводимости 8, зону нулевого потенциала, содержащую металлическую шину нулевого потенциала 12, расположенную над истоковой областью транзистора второго типа проводимости 4 и соединенную с ней, а также с полупроводниковой подложкой первого типа проводимости 1, входную зону, содержащую транзистор первого типа проводимости, расположенный в полупроводниковой области второго типа проводимости 5 над слоем разделительного диэлектрика 6, транзистор второго типа проводимости, расположенный в полупроводниковой подложке первого типа проводимости 1, входную поликремниевую шину 13, расположенную параллельно металлическим шинам питания 11 и нулевого потенциала 12, выполненную в виде буквы S в зеркальном отображении и являющуюся затвором транзистора первого типа проводимости, расположенного в полупроводниковой области второго типа проводимости 5 над слоем разделительного диэлектрика 6, и затвором транзистора второго типа проводимости, расположенного в полупроводниковой подложке первого типа проводимости 1, входную зону, содержащую транзистор первого типа проводимости, расположенный в полупроводниковой области второго типа проводимости 5 над слоем разделительного диэлектрика 6, транзистор второго типа проводимости, расположенный в полупроводниковой подложке первого типа проводимости 1, входную поликремниевую шину 14, расположенную параллельно металлическим шинам питания 11 и нулевого потенциала 12, выполненную в виде буквы S и являющуюся затвором транзистора первого типа проводимости, расположенного в полупроводниковой области второго типа проводимости 5 над слоем разделительного диэлектрика 6, и затвором транзистора второго типа проводимости, расположенного в полупроводниковой подложке первого типа проводимости 1, выходную зону, содержащую выходную поликремниевую шину 15, расположенную параллельно металлическим шинам питания 11 и нулевого потенциала 12, выполненную в виде буквы S, выходную металлическую шину прямоугольной формы 16, расположенную над областями элемента перпендикулярно металлическим шинам питания 11 и нулевого потенциала 12, соединенную с выходной поликремниевой шиной 15, а также со стоковыми областями транзисторов первого типа проводимости 7, 9 и стоковой областью транзистора второго типа проводимости 2, зону транзита, содержащую транзитную поликремниевую шину 17, расположенную параллельно металлическим шинам питания 11 и нулевого потенциала 12, выполненную в виде буквы S в зеркальном отображении. Для удобства рассмотрения интегрального логического элемента штриховыми линиями обозначены условные границы зон.

Работает устройство следующим образом.

При подаче напряжения питания на шину 11 и действующих высоких уровнях напряжения логической единицы на входные поликремниевых шинах 13, 14, расположенных над слоями тонкого диэлектрика 10 и являющихся затворами транзисторов первого типа проводимости, образованных сток-истоковыми областями 7 - 9, расположенными в полупроводниковой области второго типа проводимости 5 над слоем разделительного диэлектрика 6, и затворами транзисторов второго типа проводимости, образованных сток-истоковыми областями 2 - 4, расположенными в полупроводниковой подложке первого типа проводимости 1, транзисторы второго типа проводимости, образованные сток-истоковыми областями 2 - 4, расположенными в полупроводниковой подложке первого типа проводимости 1, причем истоковая область 4 соединена с шиной нулевого потенциала 12, открыты, а транзисторы первого типа проводимости, образованные сток-истоковыми областями 7 - 9, находящимися в полупроводниковой области второго типа проводимости 5 над слоем разделительного диэлектрика 6, закрыты, поэтому на выходе схемы - поликремниевая шина 15, соединенная с выходной металлической шиной 16, - действует низкий уровень напряжения логического нуля.

При подаче низкого уровня напряжения логического нуля на одну или обе входные шины 13, 14 один или оба транзистора второго типа проводимости, соединенные последовательно, закроются, а один или оба транзистора первого типа проводимости, соединенные параллельно, откроются, что приведет к установлению на выходе схемы - шина 15 - высокого уровня напряжения логической единицы. Поликремниевая шина транзита 17 служит для обеспечения связей между элементами, расположенными через один или несколько элементов друг от друга.

Таким образом, предлагаемое устройство представляет собой двухвходовой интегральный логический элемент И-НЕ на КМОП-транзисторах.

Возможность введения в состав элемента произвольного количества транзитных шин позволяет исключить обходные пути при обеспечении связей между элементами, расположенными через один или несколько элементов друг от друга.

Полностью топологически и электрически совместимые между собой входные, выходная и транзитная зоны (примитивы) дают возможность их произвольной перестановки (подстройки цоколевки выводов) в зависимости от предъявляемых требований.

Та особенность, что условные границы входных зон, транзитной зоны, зон питания и нулевого потенциала пересекают контактные окна, соединяющие металлическую шину питания и выходную металлическую шину с областями элемента, позволяет уменьшить площадь, занимаемую блоками БИС на основе предлагаемого элемента, на 40 - 60% по сравнению с прототипом. Сокращение суммарной длины линий связи обеспечивает повышение быстродействия схемы на 15 - 25%. Предлагаемая регулярная конструкция элемента, собираемая из набора функциональных зон (примитивов), легко адаптируется к САПР БИС, обуславливая снижение затрат на проектирование микросхем в целом.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1995 |

|

RU2094944C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1994 |

|

RU2079986C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ-НЕ | 2000 |

|

RU2166837C1 |

| БАЗОВЫЙ ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1667574A1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1991 |

|

RU2019893C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1992 |

|

RU2062528C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1992 |

|

RU2022408C1 |

| ИНТЕГРАЛЬНЫЙ ПОЛЕВОЙ ТРАНЗИСТОР ШОТТКИ СО СТАТИЧЕСКОЙ ИНДУКЦИЕЙ | 2000 |

|

RU2183885C1 |

| ИНТЕГРАЛЬНЫЙ КАСКАДНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ "ЯЙЛЕТКАН" | 2001 |

|

RU2215368C2 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1991 |

|

RU2006989C1 |

Изобретение относится к области вычислительной техники и интегральной электроники, к интегральным логическим элементам БИС. Целью изобретения является сокращение занимаемой площади и повышение быстродействия. Элемент содержит полупроводниковую подложку первого типа проводимости, полупроводниковую область второго типа проводимости, слои тонкого диэлектрика, зону питания, зону нулевого потенциала, две входные зоны, транзистор второго типа проводимости, входную поликремниевую шину, выполненную в виде буквы S, выходную зону, выполненную в виде буквы S . Зона транзита содержит транзитную поликремниевую шину, выполненную в виде буквы S в зеркальном отображении. Входные, выходная и транзитная зоны имеют одинаковые размеры. Условные границы входных зон, транзитной зоны, зон питания и нулевого потенциала пересекают контактные окна. 1 ил., 1 табл.

Интегральный логический элемент, содержащий полупроводниковую подложку первого типа проводимости с расположенными в ней сток-истоковыми областями транзисторов второго типа проводимости, полупроводниковую область второго типа проводимости, расположенную над слоем разделительного диэлектрика и содержащую сток-истоковые области транзисторов первого типа проводимости, слои тонкого диэлектрика, зону питания, содержащую металлическую шину питания, соединенную с истоковыми областями транзисторов первого типа проводимости, зону нулевого потенциала, содержащую металлическую шину нулевого потенциала, расположенную над истоковой областью транзистора второго типа проводимости и соединенную с ней, а также с полупроводниковой подложкой первого типа проводимости, отличающийся тем, что в него введены входная зона, содержащая транзистор первого типа проводимости, расположенный в полупроводниковой области второго типа проводимости над слоем разделительного диэлектрика, транзистор второго типа проводимости, расположенный в полупроводниковой подложке первого типа проводимости, входную поликремниевую шину, расположенную параллельно металлическим шинам питания и нулевого потенциала, выполненную в виде буквы S в зеркальном отображении и являющуюся затвором транзистора первого типа проводимости, расположенного в полупроводниковой области второго типа проводимости над слоем разделительного диэлектрика, и затвором транзистора второго типа проводимости, расположенного в полупроводниковой подложке первого типа проводимости, входная зона, содержащая транзистор первого типа проводимости, расположенный в полупроводниковой области второго типа проводимости над слоем разделительного диэлектрика, транзистор второго типа проводимости, расположенный в полупроводниковой подложке первого типа проводимости, входную поликремниевую шину, расположенную параллельно металлическим шинам питания и нулевого потенциала, выполненную в виде буквы S, являющуюся затвором транзистора первого типа проводимости, расположенного в полупроводниковой области второго типа проводимости над слоем разделительного диэлектрика, и затором транзистора второго типа проводимости, расположенного в полупроводниковой подложке первого типа проводимости, выходная зона, содержащая выходную поликремниевую шину, расположенную параллельно металлическим шинам питания и нулевого потенциала и выполненную в виде буквы S, выходная металлическая шина прямоугольной формы, расположенная над областями элемента перпендикулярно металлическим шинам питания и нулевого потенциала и соединенная с выходной поликремниевой шиной, а также со стоковыми областями транзисторов первого типа проводимости и стоковой областью транзистора второго типа проводимости, зона транзита, содержащая транзитную поликремниевую шину, расположенную параллельно металлическим шинам питания и нулевого потенциала и выполненную в виде буквы S в зеркальном отображении, причем входные, выходная и транзитная зоны имеют одинаковые размеры, а условные границы входных зон, транзитной зоны, зон питания и нулевого потенциала пересекают контактные окна, соединяющие металлическую шину питания и выходную металлическую шину с областями элемента.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Эйрис Р | |||

| Проектирование СБИС | |||

| Метод кремниевой компиляции | |||

| - М.: Главная редакция физико-математической литературы, 1988, с.40, рис.1.14 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Bern Hocfflinger, Sie I | |||

| Liu, and Branislav Vajdic, A Three - Dimentional CMOS Desigh Metodology, IEEE Transactions of Electron Devices, v | |||

| Способ очистки нефти и нефтяных продуктов и уничтожения их флюоресценции | 1921 |

|

SU31A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| RU, патент, 2019893, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1998-07-20—Публикация

1996-04-23—Подача