Изобретение относится к области вычислительной техники и интегральной электроники, а более конкретно к интегральным логическим элементам БИС.

Целью изобретения является уменьшение занимаемой площади, повышение быстродействия, нагрузочной способности и помехоустойчивости интегрального логического элемента и устройств на его основе, а также снижение затрат на проектирование микросхем в целом.

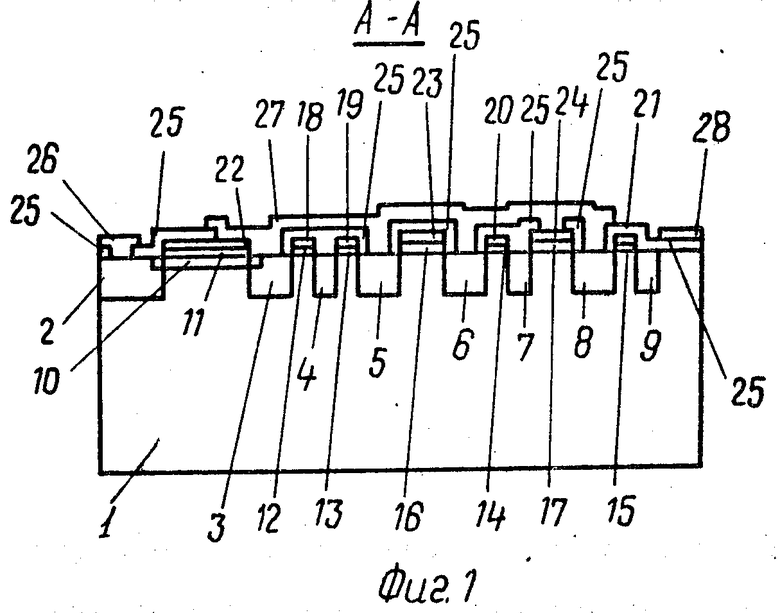

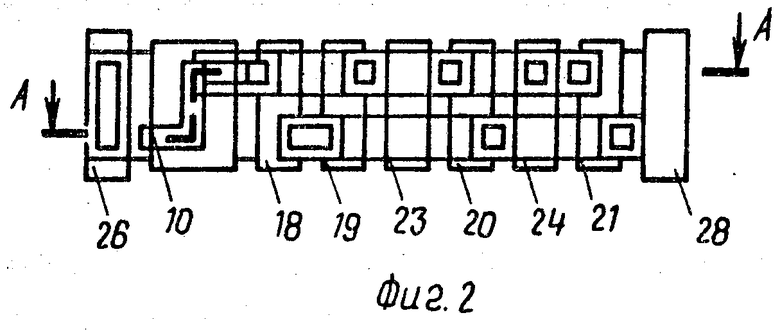

На фиг. 1 представлен интегральный элемент, поперечный разрез; на фиг.2 его топология.

Интегральный логический элемент содержит подложку 1 р-типа пpоводимости, сток-истоковые области 2-9 n-типа проводимости, слой 10 встроенного канала нагрузочного транзистора n-типа проводимости, слои 11-15 подзатворного диэлектрика, слои 16 и 17 толстого диэлектрика под транзитной и выходной поликремниевой шинами, поликремниевые входные шины 18-21, поликремниевый затвор 22 нагрузочного транзистора, поликремниевые транзитную шину 23 и выходную шину 24, защитный диэлектрик 25, металлическую шину 26 питания, металлическую выходную шину 27 и металлическую шину 28 нулевого потенциала. Шина 28 соединена с истоковыми областями 4, 7 и 9 ключевых транзисторов, шина 27 с истоковой областью 3 и затвором 22 нагрузочного транзистора, со стоковыми областями 3, 5, 6 и 8 ключевых транзисторов (область 3 является одновременно стоком ключевого и истоком нагрузочного транзисторов) и шиной 24. Шина 26 соединена со стоковой областью 2 нагрузочного транзистора. Шины 18-21 имеют S-образную форму, а слой 10  -образную форму.

-образную форму.

Работает устройство следующим образом.

При подаче напряжения питания на шину 26 и действующих низких уровней напряжений логического "0" на всех входных шинах 18-21 все ключевые транзисторы схемы закрыты, токи каналов отсутствуют, поэтому на выходе схемы шина 24 действует высокий уровень напряжения логической "1". При подаче высокого уровня напряжения логической "1" на любой один или несколько входов открываются один или несколько ключевых транзисторов, а так как они соединены параллельно (стоки объединены и соединены с выходной шиной) на выходе появляется низкий уровень напряжения логического "0". Таким образом, устройство представляет собой четырехвходовый (многовходовый) логический элемент ИЛИ-НЕ на n-МДП-транзисторах.

Конструкция позволяет повысить основные характеристики интегрального логического элемента по сравнению с прототипом. Использование S-образных входных поликремниевых шин-затворов обусловливает специфичную конфигурацию сток-истоковых областей, что в совокупности позволяет исключить пассивные области в зоне аппроксимирующего прямоугольника элемента и уменьшить его габаритный размер в горизонтальной плоскости (фиг.1). Это привело к уменьшению площади, занимаемой данным элементом на кристалле микросхемы, на 10-25% по сравнению с прототипом.

Ширина каналов ключевых транзисторов элемента увеличена по сравнению с прототипом почти в 2 раза (при неизменной длине) и равна практически ширине элемента при тех же конструктивно-технологических ограничениях. Перестройка же параметров нагрузочного транзистора обеспечивается в широком диапазоне изменением в несколько раз соотношения ширина/длина встроенного оригинального канала без изменения размеров транзистора и элемента в целом. Расширение канала производится в направлении сверху вниз для правой горизонтальной (фиг.1) его части снизу вверх для левой горизонтальной и в обе стороны для средней вертикальной его частей. Указанные особенности позволяют в среднем в 1,3-1,5 раза повысить быстродействие, нагрузочную способность и помехоустойчивость предлагаемого элемента по сравнению с прототипом.

При использовании предлагаемого устройства для проектирования БИС на его основе с помощью САПР логический элемент собирается согласно символьному описанию из структурно-топологических примитивов (СТП), границы которых проходят через середины следующих областей: нагрузочный транзистор 2 и 3, вход 3 и 4, или 4 и 5, или 6 и 7, или 8 и 9, выход 7 и 8, транзитная шина 5 и 6, область подключения нулевого потенциала 9 и 28. При сборке элемента СТП входных, выходных и транзитных областей могут переставляться в произвольном порядке, обеспечивая гибкую цоколевку выводов элемента для связи его с соседними элементами в составе БИС. Введение в состав элемента транзитной (транзитных) шины позволяет исключить обходные пути для межсоединений при обеспечении связей не между соседними элементами, а между элементами, стоящими через один, через два, и т.д.

Указанные факторы обеспечивают практически беззазорную стыковку элементов в узле и узлов в блоках при полностью автоматизированном проектировании микросхем. Применение элемента и устройств на его основе в составе САПР БИС позволяет экономить до 20-30% площади кристалла по сравнению с прототипом с жесткой цоколевкой выводов при одинаковой сложности реализуемых микросхем. Это означает, что примерно на 1/3 уменьшается площадь кристалла, увеличивается процент выхода годных и, следовательно, снижается стоимость микросхем. Интегральный логический элемент может быть использован при разработке САПР БИС на основе методологии кремниевой компиляции.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1994 |

|

RU2079986C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1995 |

|

RU2094944C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1996 |

|

RU2115998C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1991 |

|

RU2019893C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1992 |

|

RU2022408C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1991 |

|

RU2006989C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1992 |

|

RU2062528C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ-НЕ | 2000 |

|

RU2166837C1 |

| ИНТЕГРАЛЬНЫЙ КАСКАДНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ "ЯЙЛЕТКАН" | 2001 |

|

RU2215368C2 |

| ИНТЕГРАЛЬНАЯ СТРУКТУРА ДЛЯ БИС | 1992 |

|

RU2084989C1 |

Изобретение относительно к области вычислительной техники и интегральной электроники, а более конкретно к интегральным логическим элементам цифровых БИС. Цель изобретения уменьшение занимаемой площади, повышение быстродействия, нагрузочной способности и помехоустойчивости интегрального логического элемента и устройства на его основе, а также снижение затрат на проектирование микросхем в целом. В БИС введены расположенные над слоем толстого диэлектрика поликремниевая выходная шина, соединенная с выходной металлической шиной и, поликремниевая транзитная шина, причем поликремниевые входные шины имеют S-образную форму, а полупроводниковый слой встроенного канала нагрузочного транзистора имеет  форму. 2 ил.

форму. 2 ил.

БАЗОВЫЙ ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ, содержащий подложку первого типа проводимости, стоковые и истоковые области нагрузочного и ключевых МОП-транзисторов, металлическую шину питания, расположенную над стоковой областью нагрузочного транзистора, и соединенную с ней металлическую общую шину, расположенную над областями стоков, истоков и затворов, соединенную с истоковыми областями ключевых транзисторов, полупроводниковый слой встроенного канала нагрузочного транзистора, слои подзатворного диэлектрика, на которых расположены поликремниевые входные шины, и выходную металлическую шину, соединенную со стоковыми областями ключевых транзисторов, затвором и истоковой областью нагрузочного транзистора, отличающийся тем, что, с целью уменьшения площади, занимаемой БИС на его основе, повышения быстродействия, нагрузочной способности и помехоустойчивости, а также уменьшения затрат на проектирование микросхем, он дополнительно содержит поликремниевую выходную шину, соединенную с выходной металлической шиной, и поликремниевую транзитную шину, причем входные шины имеют S-образную форму, а встроенный канал нагрузочного транзистора имеет  -образную форму.

-образную форму.

| Эйрис Р | |||

| Проектирование СБИС | |||

| Метод кремниевой компилляции | |||

| Физ-мат | |||

| лит | |||

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1995-10-27—Публикация

1989-05-03—Подача