Изобретение относится к радиоизмерениям и может быть использовано при контроле характеристик различных радиоэлектронных устройств.

Известно устройство для определения статистических характеристик случайных процессов [1] , содержащее нуль-орган, блок нормирования, генератор треугольного напряжения, два блока умножения, квадратор, блок сравнения и блок усреднения.

Данное устройство имеет узкие функциональные возможности.

Известно также устройство для определения характеристик случайного процесса [2], содержащее измерительный блок ранжирования, формирователь сигнала сброса, вычитатель, блок деления, блок постоянной памяти коэффициента деления, делитель на два, блок регистрации среднеквадратического отклонения и блок регистрации среднего.

Данное устройство не обеспечивает определения принадлежности закона распределения вероятности случайных величин при возможном отличии его от нормального распределения.

Известно кроме того устройство для измерения характеристик случайных процессов [3] , содержащее нормирующий усилитель, вход которого соединен с входной шиной, а выход через последовательно соединенные двойной квадратичный детектор, первый интегратор, первый делитель и арифметический вычитатель подключен к первому входу индикатора, при этом выход нормирующего усилителя через последовательно соединенные первый детектор, второй интегратор и второй детектор подключен также к второму входу первого делителя.

Данное устройство не обеспечивает определения вида симметричного закона распределения случайных величин при отличии от нормального распределения вероятностей случайных процессов.

Наиболее близким к предлагаемому по технической сущности является устройство для измерения характеристик случайных процессов [4], содержащее нормирующий усилитель, вход которого соединен с входной шиной, а выход через последовательно соединенные двойной квадратичный детектор, первый интегратор, первый делитель и арифметический вычислитель подключен к первому входу индикатора, при этом выход нормирующего усилителя через последовательно соединенные первый детектор, второй интегратор и второй детектор подключен также к второму входу первого делителя, при этом последовательно соединенные первый умножитель, третий интегратор и второй делитель, третий детектор, блок извлечения квадратного корня и второй умножитель, первый вход которого непосредственно, а второй вход через блок извлечения квадратного корня подключены к выходу второго интегратора, выход второго умножителя подключен к второму входу второго делителя, выход которого подключен к второму входу индикатора, при этом первый вход первого умножителя непосредственно, а второй через третий детектор подключены к выходу нормирующего усилителя, при этом последовательно соединенные элемент И-НЕ и ключ, первый вход которого соединен с выходом третьего делителя, первый и второй входы которого соединены соответственно с выходами нормирующего усилителя и блока извлечения квадратного корня, вторые входы первого и второго компараторов являются входными шинами, первые входы первого и второго компараторов одновременно соединены с выходом второго делителя, а выходы первого и второго компараторов подключены соответственно к первому и второму входам элемента ИЛИ-НЕ, выход которого подключен к первому входу элемента И-НЕ, второй вход которого соединен с выходом элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами третьего и четвертого компараторов, вторые входы которых соединены соответственно с входными шинами, а первые входы соединены одновременно с первым входом индикатора, третий, четвертый, пятый, шестой и седьмой входы которого соединены соответственно с первым, вторым, третьим, четвертым и пятым выходами дешифратора, первый вход которого соединен одновременно с выходом элемента И-НЕ и вторым входом ключа, выход которого подключен одновременно к первым входам пятого, шестого и седьмого компараторов, вторые входы которых соединены соответственно с входными шинами, а выходы - подключены соответственно к второму, третьему и четвертому входам дешифратора.

Недостатком известного устройства является низкая достоверность определения вида симметричного закона распределения случайных величин.

Цель изобретения - повышение достоверности определения вида симметричного закона распределения вероятности случайных величин за счет определения энтропийного коэффициента и значения контрэксцесса.

Цель достигается тем, что в устройство для измерения характеристик случайных процессов [4], содержащее первый дешифратор, индикатор, первый элемент И-НЕ, нормирующий усилитель, вход которого соединен с входной шиной, а выход через последовательно соединенные двойной квадратичный детектор и первый интегратор подключен к первому входу первого делителя, при этом выход нормирующего усилителя через последовательно соединенные первый детектор, второй интегратор и второй детектор подключен также к второму входу первого делителя, при этом последовательно соединенные первый умножитель, третий интегратор и второй делитель, выход которого подключен одновременно к первым входам первого и второго компараторов, вторые входы которых соединены соответственно с входными шинами, а выходы - подключены соответственно к первому и второму входам элемента ИЛИ-НЕ, при этом первый вход второго умножителя непосредственно, а второй вход через первый блок извлечения квадратного корня подключены к выходу второго интегратора, выход второго умножителя подключен к второму входу второго делителя, при этом первый вход первого умножителя непосредственно, а второй через третий детектор подключены к выходу нормирующего усилителя, при этом выход третьего делителя подключен к первому входу первого ключа, выход которого подключен одновременно к первым входам пятого, шестого и седьмого компараторов, вторые входы которых соединены соответственно с входными шинами, первые входы третьего и четвертого компараторов объединены, вторые входы которых соединены соответственно с входными шинами, дополнительно введены восьмой, девятый, десятый, одиннадцатый и двенадцатый компараторы, вторые входы которых соединены соответственно с входными шинами, а объединенные первые входы соединены с выходом первого ключа, второй вход которого одновременно соединен с выходом элемента ИЛИ-НЕ и вторым входом второго ключа, выход которого одновременно подключен к первым входам третьего, четвертого, тринадцатого, четырнадцатого, пятнадцатого, шестнадцатого, семнадцатого и восемнадцатого компараторов, вторые входы которых соединены соответственно с входными шинами, при этом введены второй, третий, четвертый, пятый, шестой и седьмой элементы И-НЕ, выходы которых соответственно подключены к второму, третьему, четвертому, пятому, шестому и седьмому входам индикатора, первый вход которого соединен с выходом первого элемента И-НЕ, а восьмой, девятый, десятый и одиннадцатый входы соединены соответственно с первым, вторым, третьим и четвертым выходами коммутатора, пятый вход которого соединен с входной шиной, а первый, второй, третий и четвертый входы соединены соответственно с первым, вторым, третьим и четвертым выходами второго дешифратора, первый вход которого одновременно соединен с входной шиной и объединенными девятыми входами первого и второго мультиплексоров, при этом второй вход второго дешифратора одновременно соединен с входной шиной и объединенными десятыми входами первого и второго мультиплексоров, а объединенные девятые и объединенные десятые входы первого и второго регистров соединены соответственно с входными шинами, первый, второй, пятый и шестой входы первого мультиплексора соединены соответственно с первым, пятым, вторым и шестым выходами первого регистра, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами пятого, шестого, седьмого, восьмого, девятого, десятого, одиннадцатого и двенадцатого компараторов, при этом третий, седьмой, четвертый и восьмой выходы первого регистра подключены соответственно к первому, второму, пятому и шестому входам второго мультиплексора, третий, четвертый, седьмой и восьмой входы которого соединены соответственно с третьим, седьмым, четвертым и восьмым выходами второго регистра, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами третьего, четвертого, тринадцатого, четырнадцатого, пятнадцатого, шестнадцатого, семнадцатого и восемнадцатого компараторов, а первый, пятый, второй и шестой выходы второго регистра подключены соответственно к третьему, четвертому, седьмому и восьмому входам первого мультиплексора, первый и второй выходы которого подключены соответственно к первому и второму входам первого дешифратора, третий и четвертый входы которого соединены соответственно с первым и вторым выходами второго мультиплексора, второй выход первого дешифратора одновременно подключен к первым входам первого и второго элементов И, вторые входы которых соответственно соединены с пятым и восьмым выходами первого дешифратора, десятый выход которого подключен к второму входу четвертого элемента И-НЕ, первый вход которого одновременно соединен с первыми входами третьего и второго элементов И-НЕ и двенадцатым выходом первого дешифратора, одиннадцатый выход которого одновременно подключен и объединенным второму входу седьмого элемента И-НЕ, третьему входу третьего элемента И-НЕ и второму входу второго элемента И-НЕ, при этом первый выход первого дешифратора подключен к четвертому входу седьмого элемента И-НЕ, третий вход которого одновременно соединен с третьим входом первого элемента И-НЕ и пятнадцатым выходом первого дешифратора, четырнадцатый выход которого подключен к объединенным вторым входам четвертого элемента И и третьего элемента И-НЕ, четвертый вход которого одновременно соединен с вторым входом шестого элемента И-НЕ и третьим выходом первого дешифратора, тринадцатый выход которого одновременно подключен к первым входам четвертого элемента И и первого элемента И-НЕ, объединенные второй и четвертый входы которого одновременно соединены с выходом первого элемента И и первым входом третьего элемента И, выход которого одновременно подключен к четвертому входу четвертого элемента И-НЕ и первому входу пятого элемента И- НЕ, второй вход которого одновременно соединен с первым входом шестого элемента И-НЕ и четвертым выходом первого дешифратора, шестой выход которого одновременно подключен к объединенным четвертым входам пятого и второго элементов И-НЕ, при этом седьмой выход первого дешифратора подключен к третьему входу второго элемента И-НЕ, а девятый выход подключен к третьему входу пятого элемента И-НЕ, выход второго элемента И одновременно подключен к второму входу третьего элемента И, первому входу седьмого элемента И-НЕ и объединенным четвертому и третьему входам шестого элемента И-НЕ, а выход четвертого элемента И подключен к третьему входу четвертого элемента И-НЕ, при этом вход второго блока извлечения квадратного корня соединен с выходом первого делителя, а выход подключен к первому входу третьего делителя, второй вход которого соединен с входной шиной, первые входы первого и второго амплитудных селекторов одновременно соединены с выходом нормирующего усилителя, а вторые входы соединены соответственно с первым и вторым выходами генератора ступенчатого напряжения, вход которого соединен с входной шиной, при этом выходы первого и второго амплитудных селекторов подключены соответственно к первому и второму входам вычитающего устройства, выход которого подключен к входу четвертого интегратора, выход которого одновременно подключен к входу логарифмического усилителя и второму входу третьего умножителя, первый вход которого соединен с выходом логарифмического усилителя, а выход подключен к входу пятого интегратора, выход которого подключен к входу блока вычисления экспоненциальной функции, выход которого подключен к первому входу четвертого делителя, второй вход которого соединен с входной шиной, а выход подключен к первому входу пятого делителя, второй вход которого соединен с выходом первого блока извлечения квадратного корня, а выход подключен к первому входу второго ключа.

Степень отличия исследуемого закона распределения от нормального происходит благодаря знанию коэффициента эксцесса и коэффициента асимметрии и могут быть использованы при регулировке или исследовании радиотехнических устройств, например переход закона распределения мгновенных значений электрических флуктуаций на выходе радиоэлектронных устройств от нормального к равномерному, треугольному, трапецеидальному, антимодальному и т.д., указывают на причину перехода к данному распределению. Как правило причиной изменения распределения являются нелинейные искажения, снижение либо увеличение порога ограничения последующих каскадов, сужение динамического диапазона, изменение параметров устройств, относительно быстрое старение отдельных элементов, приводящее к изменению отношений между элементами радиоэлектронного устройства, изменения влияющих факторов и величин как естественного так и искусственного происхождения и т.д.

Знание закона распределения мгновенных значений электрических флуктуаций, причин, вызывающих данное изменение, может быть использовано не только при исследовании, но и при регулировке радиотехнических устройств.

В качестве характеристики сглаженности или обостренности кривой распределения около ее моды используют безразмерный коэффициент эксцесса [5, с. 96] , либо эксцесс

где

где x - значение входной величины;

ω - закон распределения случайной входной величины.

Характеристикой несимметричности кривой распределения относительно ее моды является коэффициент асимметрии [5, с. 95 и 96]

где

Таким образом, нормальное распределение имеет коэффициенты эксцесса и асимметрии, равные нулю, а эксцесс, равный 3. Положительное значение γ указывает на то, что кривая распределения в окрестности моды имеет более высокую и более острую вершину, чем кривая нормального распределения с тем же средним и дисперсией. Отрицательное значение коэффициента эксцесса указывает на более плоский характер вершины по сравнению с соответствующей кривой нормального закона распределения. Положительное значение коэффициента асимметрии указывает на то, что кривая распределения справа от моды имеет скошенность, отрицательное значение S указывает на то, что кривая распределения слева от моды имеет скошенность по сравнению с соответствующей кривой нормального закона распределения, то есть в этом случае кривая распределения несимметрична относительно моды.

Значение коэффициента эксцесса (эксцесса) и коэффициента асимметрии лишь указывает на отличие распределения мгновенных значений электрических флуктуаций от нормального, но какое именно будет в этом случае распределение неизвестно.

Определение закона распределения мгновенных значений электрических флуктуаций производится лишь для симметричных распределений, когда значение коэффициента асимметрии равно нулю.

Данное условие выбрано потому, что определяемые законы распределения симметричные. Для симметричных распределений коэффициент асимметрии равен нулю. Чтобы определить симметричный закон распределения случайных величин необходимо знать значение контрэксцесса [10, с. 78], который рассчитывается по формуле

и для любых распределений заключено в пределах от 0 (при э → ∞ и до 1 (при э = 1) так как эксцесс различных распределений колеблется в бесконечных пределах, (от 1 до ∞), ) из-за чего эксцесс неудобен.

Однако совершенно разные законы распределения могут иметь совпадающие значения эксцесса и контрэксцесса. Так, например, значения эксцесса и контрэксцесса трапецеидальных распределений с различным отношением оснований и арксинусоидальных распределений в значительной мере перекрываются.

Поэтому, в качестве второго независимого признака, который совместно с контрэксцессом характеризует форму и вид симметричного распределения, принят энтропийный коэффициент [10, с. 58-60, 78], значение которого рассчитывается по формуле

где Δэ - энтропийное значение входной величины;

σ - среднее квадратическое отклонение входной величины;

Н(х) - энтропия входной величины.

Энтропия случайной входной величины является мерой ее неопределенности, зависит от вида закона распределения и рассчитывается по формуле

Значение энтропийного коэффициента для любых законов распределения изменяется в пределах от 0 до

Для наиболее часто встречающихся на практике распределений значение энтропийного коэффициента колеблется от 1,11 у арисинусоильного распределения до 2,066 у нормального распределения. Исключение составляет "антимодальное II" распределение, у которого значение энтропийного коэффициента составляет 0,35.

При использовании контрэксцесса и энтропийного коэффициента в качестве классификационных признаков, характеризующих форму и вид распределений, изображающая точка (либо некоторая область) с координатами Кэ и χ будет всегда находиться в пределах прямоугольника, ограниченного значениями Кэ от 0 до 2,066 и значениями χ от 0 до 1, а представление симметричных законов распределения в виде изображающих точек (либо некоторых областей) на плоскости признаков позволяет определить не только закон распределения, но и близость или удаленность различных законов распределений между собой.

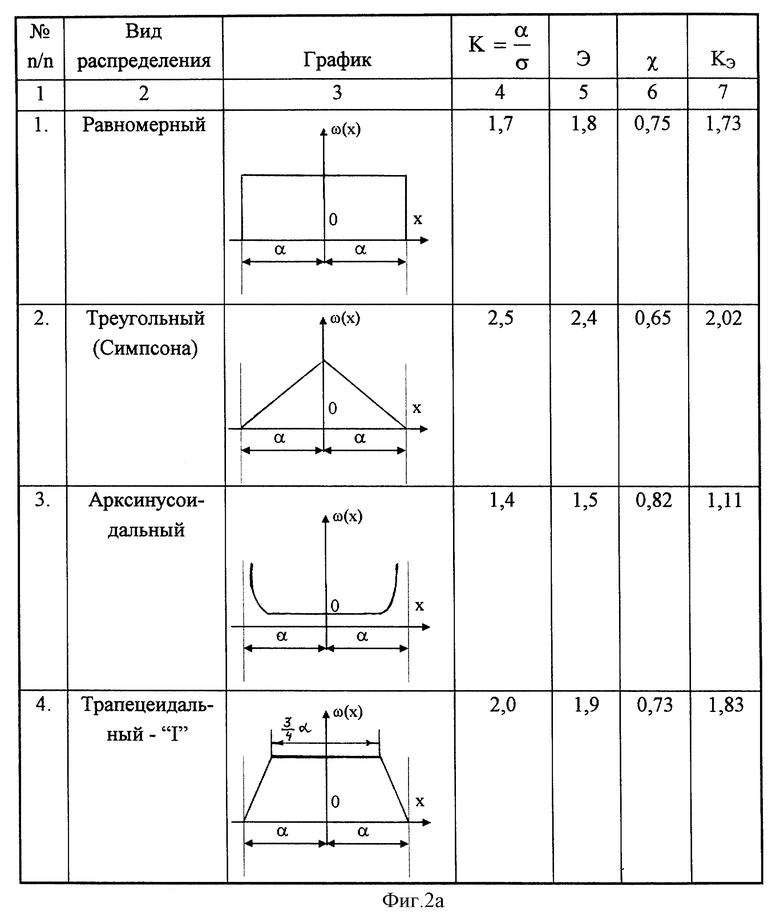

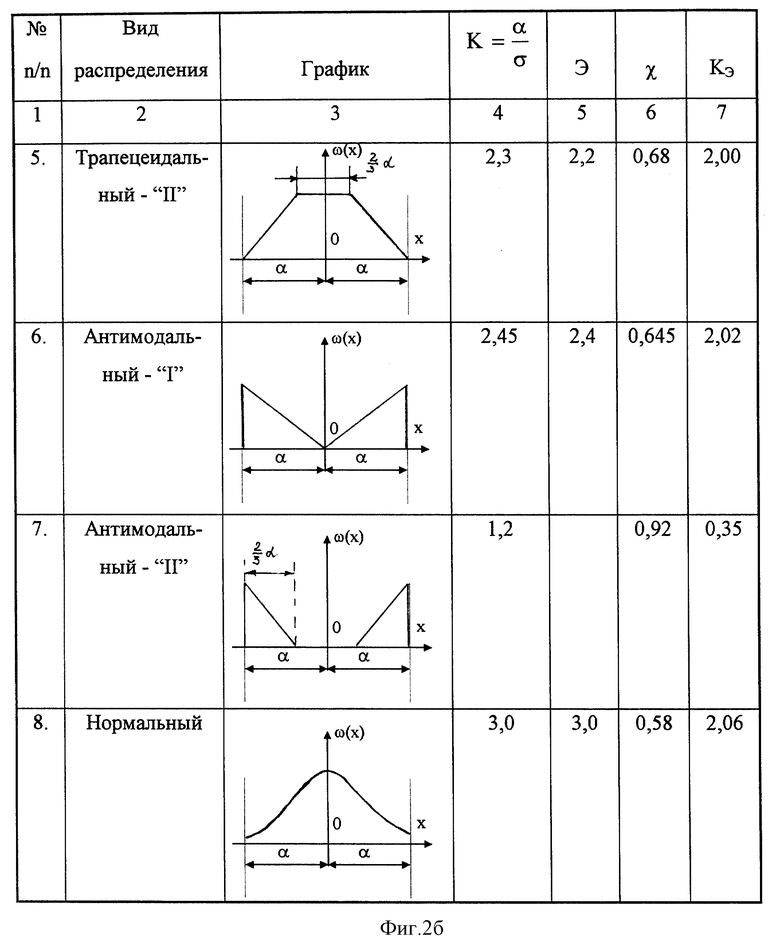

На фиг. 2 приведены законы распределения случайных величин и соответствующие им значения контрэксцесса χ, энтропийного коэффициента Кэ, коэффициента  где α = x, так как случайный процесс центрированный и т. д.

где α = x, так как случайный процесс центрированный и т. д.

Таким образом, подобная классификация симметричных распределений по значениям Кэ и χ позволяет определить закон распределения, так как определение вида распределения по одному лишь эксцессу (коэффициенту эксцесса) или коэффициенту  не обеспечивает однозначного определения закона распределения, так как все симметричные распределения располагаются по одной оси при асимметрии, равной нулю [6, с.91, 10, с.78].

не обеспечивает однозначного определения закона распределения, так как все симметричные распределения располагаются по одной оси при асимметрии, равной нулю [6, с.91, 10, с.78].

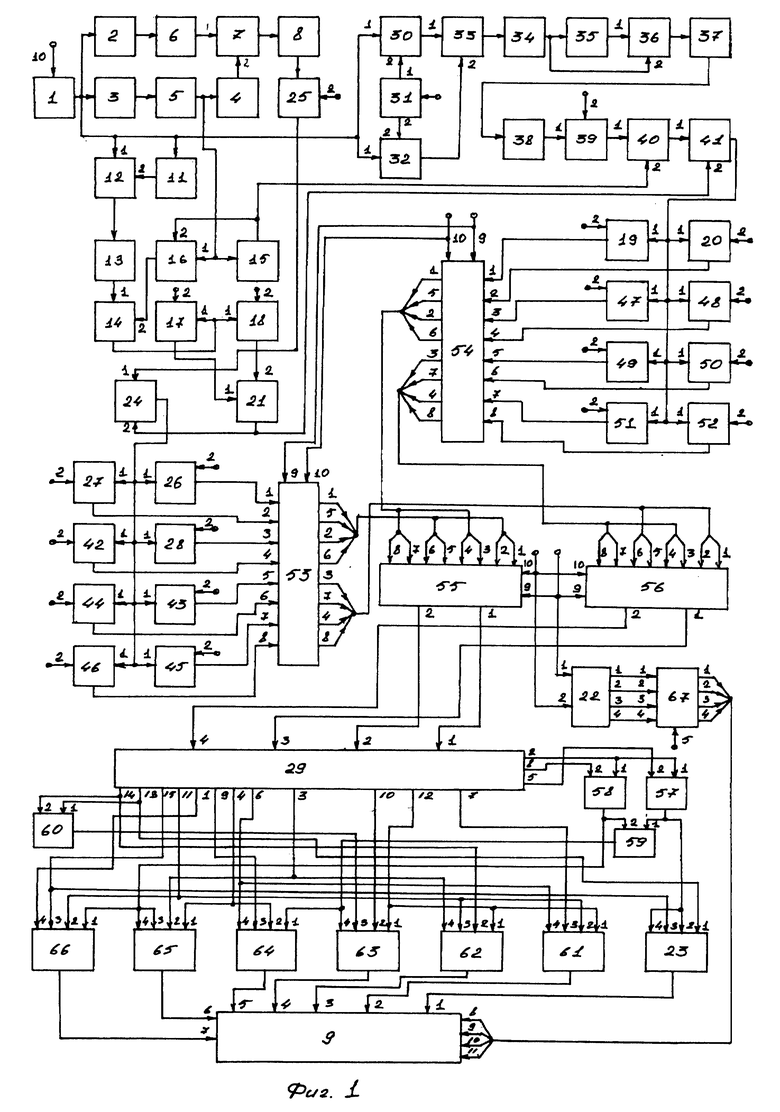

На фиг. 1 приведена структурная электрическая схема устройства для измерения характеристик случайных процессов.

Устройство содержит нормирующий усилитель 1, двойной квадратичный детектор 2, первый детектор 3, второй детектор 4, второй интегратор 5, первый интегратор 6, первый делитель 7, второй блок извлечения квадратного норме 8, индикатор 9, первую входную шину 10, третий детектор 11, первый умножитель 12, третий интегратор 13, второй делитель 14, первый блок извлечения квадратного норме 15, второй умножитель 16, первый компаратор 17, второй компаратор 18, третий компаратор 19, четвертый компаратор 20, элемент ИЛИ-НЕ 21, второй дешифратор 22, первый элемент И-НЕ 23, первый ключ 24, третий делитель 25, пятый компаратор 26, шестой компаратор 27, седьмой компаратор 28, первый дешифратор 29, первый амплитудный селектор 30, генератор ступенчатого напряжения 31, второй амплитудный селектор 32, вычитающее устройство 33, четвертый интегратор 34, логарифмический усилитель 35, третий умножитель 36, пятый интегратор 37, блок вычисления экспоненциальной функции 38, четвертый делитель 39, пятый делитель 40, второй ключ 41, восьмой компаратор 42, девятый компаратор 43, десятый компаратор 44, одиннадцатый компаратор 45, двенадцатый компаратор 46, тринадцатый компаратор 47, четырнадцатый компаратор 48, пятнадцатый компаратор 49, шестнадцатый компаратор 50, семнадцатый компаратор 51, восемнадцатый компаратор 52, первый регистр 53, второй регистр 54, первый мультиплексор 55, второй мультиплексор 56, первый элемент И 57, второй элемент И 58, третий элемент И 59, четвертый элемент И 60, второй элемент И-НЕ 61, третий элемент И-НЕ 62, четвертый элемент И-НЕ 63, пятый элемент И-НЕ 64, шестой элемент И-НЕ 65, седьмой элемент И-НЕ 66 и коммутатор 67.

Вход нормирующего усилителя 1 соединен с входной шиной 10, а выход через последовательно соединенные двойной квадратичный детектор 2 и первый интегратор 6 подключен к первому входу первого делителя 7, при этом выход нормирующего усилителя 1 через последовательно соединенные первый детектор 3, второй интегратор 5 и второй детектор 4 подключен также к второму входу первого делителя 7, при этом последовательно соединенные первый умножитель 12, третий интегратор 13 и второй делитель 14, выход которого подключен одновременно к первым входам первого компаратора 17 и второго компаратора 18, вторые входы которых соединены соответственно с входными шинами, а выходы подключены соответственно к первому и второму входам элемента ИЛИ-НЕ 21, при этом первый вход второго умножителя 16 непосредственно, а второй вход через первый блок извлечения квадратного корня 15 подключены к выходу второго интегратора 5, выход второго умножителя 16 подключен к второму входу второго делителя 14, при этом первый вход первого умножителя 12 непосредственно, а второй через третий детектор 11 подключены к выходу нормирующего усилителя 1, при этом выход третьего делителя 25 подключен к первому входу первого ключа 24, выход которого подключен одновременно к первым входам пятого компаратора 26, шестого компаратора 27 и седьмого компаратора 28, вторые входы которых соединены соответственно с входными шинами, первые входы третьего компаратора 19 и четвертого компаратора 20 объединены, вторые входы которых соединены соответственно с входными шинами, при этом вторые входы восьмого компаратора 42, девятого компаратора 43, десятого компаратора 44, одиннадцатого компаратора 45 и двенадцатого компаратора 46 соединены соответственно с входными шинами, а объединенные первые входы соединены с выходом первого ключа 24, второй вход которого одновременно соединен с выходом элемента ИЛИ-НЕ 21 и вторым входом второго ключа 41, выход которого одновременно подключен к первым входам третьего компаратора 19, четвертого компаратора 20, тринадцатого компаратора 47, четырнадцатого компаратора 48, пятнадцатого компаратора 49, шестнадцатого компаратора 50, семнадцатого компаратора 51 и восемнадцатого компаратора 52, вторые входы которых соединены соответственно с входными шинами, при этом выходы второго элемента И-НЕ 61, третьего элементов И-НЕ 62, четвертого элементов И-НЕ 63, пятого элементов И-НЕ 64, шестого элементов И-НЕ 65 и седьмого элементов И-НЕ 66 соответственно подключены к второму, третьему, четвертому, пятому, шестому и седьмому входам индикатора 9, первый вход которого соединен с выходом первого элемента И-НЕ 23, а восьмой, девятый, десятый и одиннадцатый входы соединены соответственно с первым, вторым, третьим и четвертым выходами коммутатора 67, пятый вход которого соединен с входной шиной, а первый, второй, третий и четвертый входы соединены соответственно с первым, вторым, третьим и четвертым выходами второго дешифратора 22, первый вход которого одновременно соединен с входной шиной и объединенными девятыми входами первого мультиплексора 55 и второго мультиплексора 56, при этом второй вход второго дешифратора 22 одновременно соединен с входной шиной и объединенными десятыми входами первого мультиплексора 55 и второго мультиплексора 56, а объединенные девятые и объединенные десятые входы первого регистра 53 и второго регистра 54 соединены соответственно с входными шинами, первый, второй, пятый и шестой входы первого мультиплексора 55 соединены соответственно с первым, пятым, вторым и шестым выходами первого регистра 53, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами пятого компаратора 26, шестого компаратора 27, седьмого компаратора 28, восьмого компаратора 42, девятого компаратора 43, десятого компаратора 44, одиннадцатого компаратора 45 и двенадцатого компаратора 46, при этом третий, седьмой, четвертый и восьмой выходы первого регистра 53 подключены соответственно к первому, второму, пятому и шестому входам второго мультиплексора 56, третий, четвертый, седьмой и восьмой входы которого соединены соответственно с третьим, седьмым, четвертым и восьмым выходами второго регистра 54, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами третьего компаратора 19, четвертого компаратора 20, тринадцатого компаратора 47, четырнадцатого компаратора 48, пятнадцатого компаратора 49, шестнадцатого компаратора 50, семнадцатого компаратора 51 и восемнадцатого компаратора 52, а первый, пятый, второй и шестой выходы второго регистра 54 подключены соответственно к третьему, четвертому, седьмому и восьмому входам первого мультиплексора 55, первый и второй выходы которого подключены соответственно к первому и второму входам первого дешифратора 29, третий и четвертый входы которого соединены соответственно с первым и вторым выходами второго мультиплексора 56, второй выход первого дешифратора 29 одновременно подключен к первым входам первого элемента И 57 и второго элемента И 58, вторые входы которых соответственно соединены с пятым и восьмым выходами первого дешифратора 29, десятый выход которого подключен к второму входу четвертого элемента И-НЕ 63, первый вход которого одновременно соединен с первыми входами третьего элемента И-НЕ 62 и второго элемента И-НЕ 61 и двенадцатым выходом первого дешифратора 29, одиннадцатый выход которого одновременно подключен к объединенным второму входу седьмого элемента И-НЕ 66, третьему входу третьего элемента И-НЕ 62 и второму входу второго элемента И-НЕ 61, при этом первый выход первого дешифратора 29 подключен к четвертому входу седьмого элемента И-НЕ 66, третий вход которого одновременно соединен с третьим входом первого элемента И-НЕ 23 и пятнадцатым выходом первого дешифратора 29, четырнадцатый выход которого подключен к объединенным вторым входам четвертого элемента И 60 и третьего элемента И-НЕ 62, четвертый вход которого одновременно соединен с вторым входом шестого элемента И-НЕ 65 и третьим выходом первого дешифратора 29, тринадцатый выход которого одновременно подключен к первым входам четвертого элемента И 60 и первого элемента И-НЕ 23, объединенные второй и четвертый входы которого одновременно соединены с выходом первого элемента И 57 и первым входом третьего элемента И 59, выход которого одновременно подключен к четвертому входу четвертого элемента И-НЕ 63 и первому входу пятого элемента И-НЕ 64, второй вход которого одновременно соединен с первым входом шестого элемента И-НЕ 65 и четвертым выходом первого дешифратора 29, шестой выход которого одновременно подключен к объединенным четвертым входам пятого элемента И-НЕ 64 и второго элемента И-НЕ 61, при этом седьмой выход первого дешифратора 29 подключен к третьему входу второго элемента И-НЕ 61, а девятый выход подключен к третьему входу пятого элемента И-НЕ 64, выход второго элемента И 58 одновременно подключен к второму входу третьего элемента И 59, первому входу седьмого элемента И-НЕ 66 и объединенным четвертому и третьему входам шестого элемента И-НЕ 65, а выход четвертого элемента И 60 подключен к третьему входу четвертого элемента И-НЕ 63, при этом вход второго блока извлечения квадратного корня 8 соединен с выходом первого делителя 7, а выход подключен к первому входу третьего делителя 25, второй вход которого соединен с входной шиной, первые входы первого амплитудного селектора 30 и второго амплитудного селектора 32 одновременно соединены с выходом нормирующего усилителя 1, а вторые входы соединены соответственно с первым и вторым выходами генератора ступенчатого напряжения 31, вход которого соединен с входной шиной, при этом выходы первого амплитудного селектора 30 и второго амплитудного селектора 32 подключены соответственно к первому и второму входам вычитающего устройства 33, выход которого подключен к входу четвертого интегратора 34, выход которого одновременно подключен к входу логарифмического делителя 35 и второму входу третьего умножителя 36, первый вход которого соединен с выходом логарифмического усилителя 35, а выход подключен к входу пятого интегратора 37, выход которого подключен к входу блока вычисления экспоненциальной функции 38, выход которого подключен к первому входу четвертого делителя 39, второй вход которого соединен с входной шиной, а выход подключен к первому входу пятого делителя 40, второй вход которого соединен с выходом первого блока извлечения квадратного корня 15, а выход подключен к первому входу второго ключа 41.

Устройство работает следующим образом.

На вход 10 нормирующего усилителя 1 поступает исследуемый электрический сигнал X, где усиливается, ограничивается и с выхода поступает на входы двойного квадратичного детектора 2, первого детектора 3, третьего детектора 11, и первые входы первого умножителя 12, первого амплитудного селектора 30 и второго амплитудного селектора 32. С выхода двойного квадратичного детектора 2 сигнал X4 поступает на вход первого интегратора 6, на выходе которого формируется сигнал, пропорциональный центральному моменту случайной величины четвертого порядка

который поступает на первый вход первого делителя 7. С выхода первого детектора 3 сигнал X2 поступает на вход второго интегратора 5, на выходе которого формируется сигнал, пропорциональный центральному моменту случайной величины второго порядка

который поступает на входы второго детектора 4 и первого блока извлечения квадратного корня 15, а также первый вход второго умножителя 16.

На выходе второго детектора 4 формируется сигнал, пропорциональный квадрату центрального момента случайной величины второго порядка М22, который поступает на второй вход первого делителя 7, на выходе которого формируется сигнал пропорциональный эксцессу

Выход первого делителя 7 подключен к входу второго блока извлечения квадратного корня 8, выход которого подключен к первому входу третьего делителя 25. Второй вход третьего делителя 25 соединен с входной шиной, на которую подается значение сигнала, пропорциональное 1. На выходе третьего делителя 25 формируется сигнал, пропорциональный контрэксцессу

С выхода первого блока извлечения квадратного корня 15 сигнал, пропорциональный среднему квадратическому отклонению случайной величины

одновременно поступает на вторые входы пятого делителя 40 и второго умножителя 16. С выхода второго умножителя 16 сигнал, пропорциональный кубу среднего квадратического отклонения случайной величины, поступает на второй вход второго делителя 14, на выходе которого формируется сигнал, пропорциональный коэффициенту асимметрии S, который одновременно поступает на первые входы первого компаратора 17 и второго компаратора 18, которые могут быть выполнены по схеме, приведенной в [8, с. 312- 314].

На вторые входы первого компаратора 17 и второго компаратора 18 подаются соответственно пороговые значения коэффициента асимметрии S+ и S-.

На выходе первого компаратора 17 формируется сигнал логической единицы, если текущее значение коэффициента асимметрии S > S+, а на выходе второго компаратора 18 наоборот, если S < S-. Выход первого компаратора 17 подключен к первому входу элемента ИЛИ-НЕ 21, второй вход которого соединен с выходом второго компаратора 18.

На выходе элемента ИЛИ-НЕ 21 формируется сигнал логической единицы при условии, если коэффициент асимметрии S- < S < S+. Выполнение условия S- < S < S+ соответствует симметричному распределению, в противном случае распределение несимметричное.

Выход элемента ИЛИ-НЕ 21 одновременно подключен к вторым входам первого ключа 24 и второго ключа 41, которые открыты, если на вторых входах присутствует сигнал логической 1. Первый ключ 24 и второй ключ 41 могут быть выполнены по схеме, приведенной в [8, с. 375].

Выход третьего делителя 25, который может быть выполнен по схеме, приведенной в [8, с. 321], сигнал, пропорциональный значению контрэксцесса поступает на первый вход первого ключа 24, выход которого одновременно подключен к первым входам пятого компаратора 26, шестого компаратора 27, седьмого компаратора 28, восьмого компаратора 42, девятого компаратора 43, десятого компаратора 44, одиннадцатого компаратора 45 и двенадцатого компаратора 46, вторые входы которых соединены соответственно с входными шинами, на которые соответственно подаются входные сигналы, пропорциональные пороговым значениям контрэксцесса χ.

Значения контрэксцесса для равномерного, треугольного, арксинусоидального, трапецеидального - "I", трапецеидального - "II", антимодального I, антимодального II и нормального распределений приведены на фиг. 2.

На выходах пятого компаратора 26, шестого компаратора 27, седьмого компаратора 28, восьмого компаратора 42, девятого компаратора 43, десятого компаратора 44, одиннадцатого компаратора 45 и двенадцатого компаратора 46 соответственно формируются сигналы логического нуля, если сигнал на первых входах компараторов, пропорциональный значению контрэксцесса χ: χ ≥ 0,75; χ ≥ 0,65; χ ≥ 0,82; χ ≥ 0,73; χ ≥ 0,68; χ ≥ 0,87; χ ≥ 0,92; χ ≥ 0,58 соответственно.

Выходы пятого компаратора 26, шестого компаратора 27, седьмого компаратора 28, восьмого компаратора 42, девятого компаратора 43, десятого компаратора 44, одиннадцатого компаратора 45 и двенадцатого компаратора 46 подключены соответственно к первому, второму, третьему, четвертому, пятому, шестому, седьмому и восьмому входам первого регистра 53.

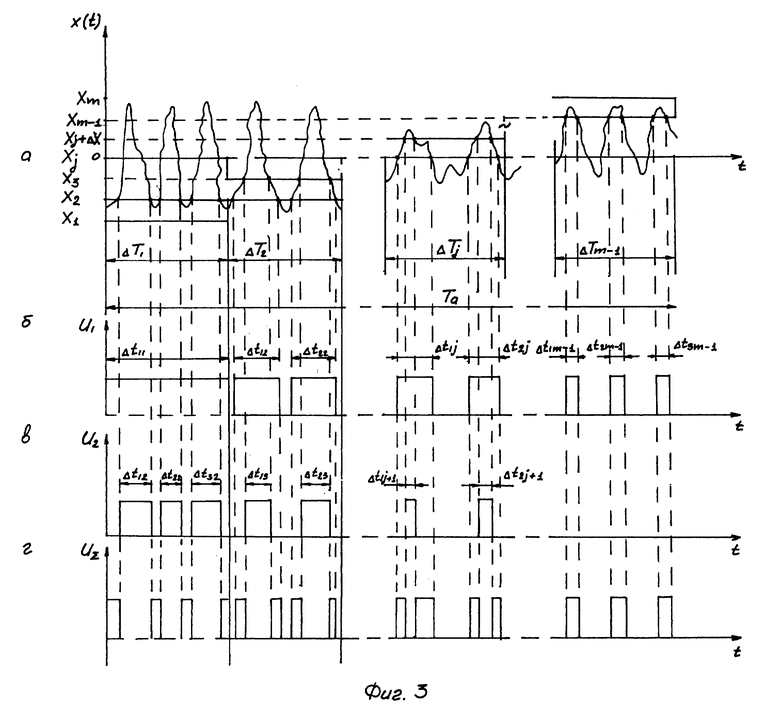

На фиг. 3 показаны временные диаграммы, поясняющие принцип формирования импульсов единичной амплитуды на выходе вычитающего устройства 33.

Первый амплитудный селектор 30 и второй амплитудный селектор 32 вырабатывают прямоугольные импульсы единичной амплитуды, длительности которых на выходе каждого селектора равны соответственно

Δtij(Xj)

и

Δtij+1(Xj+Δx)

и соответствуют интервалам времени, когда X(t)>Xj и X(t) > Xj+Δx (см. фиг. 3, а, б, в). Уровни Xj и Xj+Δx (фиг. 3, а) задаются генератором ступенчатого напряжения 31, управляющий вход которого соединен с входной шиной. На управляющий вход подается последовательность импульсов, которые управляют работой генератора ступенчатого напряжения 31 при формировании ступенчатого напряжения.

Первый и второй выходы генератора ступенчатого напряжения 31 подключены соответственно к вторым входам первого амплитудного селектора 30 и второго амплитудного селектора 32 на которые соответственно подаются напряжения, пропорциональные уровню Xj и уровню Xj+Δx. Генератор ступенчатого напряжения 31 обеспечивает изменение уровней Xj и Xj+Δx на первом и втором выходах соответственно с Δx = const. При этом изменение уровней Xj и Xj+ΔX на первом и втором выходах генератора ступенчатого напряжения 31 осуществляется через интервал времени ΔT.

Длительность интервала времени ΔT определяется временем анализа Tа случайного процесса X(t) и количеством уровней m, которое зависит от диапазона изменения амплитуды X(t) и шага ΔX. Длительность последовательности импульсов постоянной амплитуды на выходах первого амплитудного селектора 30 и второго амплитудного селектора 32 изменяется по закону вероятности изменения X(t). Первый амплитудный селектор 30 и второй амплитудный селектор 32 могут быть выполнены по схеме, приведенной в [8, с. 374 и 9, с. 87], а генератор ступенчатого напряжения по схеме, приведенной в [9 с. 125].

Выход первого амплитудного селектора 30 и выход второго амплитудного селектора 32 подключены соответственно к первому и второму входам вычитающего устройства 33, которое может быть выполнено по схеме, приведенной в [8, с. 368 и 9, с. 307-319]. На выходе вычитающего устройства 33 формируются импульсы единичной амплитуды, длительность которых, соответствует интервалам, когда Xj< x(t) < Xj+ΔX (см. фиг. 3, г). Изменяя уровни Xj и Xj+ΔX через интервалы ΔT на первом и втором выходах генератора 31 так, чтобы шаг ΔX сохранялся одинаковым для различных участков X(t), обеспечивает получение серии импульсов единичной амплитуды на выходе вычитающего устройства 33, соответствующие различным уровням Xj за время анализа Tа.

Интегрирование импульсов (см. фиг. 3, г) за время анализа Tа определяет плотность распределения вероятности ω(x). Операция интегрирования осуществляется четвертым интегратором 34, вход которого соединен с выходом вычитающего устройства 33, а выход подключен одновременно к входу логарифмического усилителя 35 и второму входу третьего умножителя 36. Первый вход третьего умножителя 36 соединен с выходом логарифмического усилителя 35, а выход подключен к входу пятого интегратора 37. На выходе пятого интегратора 37 формируется сигнал, значение которого пропорционально энтропии случайной величины X

Логарифмический усилитель 35 может быть выполнен по схеме, приведенной в [9, с. 158].

Выход пятого интегратора 37 подключен к входу блока вычисления экспоненциальной функции 38, который может быть выполнен по схеме, приведенной в [9, с. 161-163] . Выход блока вычисления экспоненциальной функции 38 подключен к первому входу четвертого делителя 39, второй вход которого соединен с входной шиной, на которую подается входной сигнал, значение которого пропорционально 2. На выходе четвертого делителя 39 формируется сигнал, пропорциональный энтропийному значению входной величины

Выход четвертого делителя 39, подключен к первому входу пятого делителя 40, второй вход которого соединен с выходом первого блока извлечения квадратного корня 15, а выход подключен к первому входу второго ключа 41. На выходе пятого делителя 40 формируется сигнал, пропорциональный энтропийному коэффициенту

Выход второго ключа 41 одновременно подключен к первым входам третьего компаратора 19, четвертого компаратора 20, тринадцатого компаратора 47, четырнадцатого компаратора 48, пятнадцатого компаратора 49, шестнадцатого компаратора 50, семнадцатого компаратора 51 и восемнадцатого компаратора 52, вторые входы которых соединены соответственно с входными шинами, на которые соответственно подаются входные сигналы, пропорциональные пороговым значениям энтропийного коэффициента Кэ.

Значения энтропийного коэффициента для равномерного, треугольного, арксинусоидального, трапецеидального - "I", трапецеидального -"II", антимодального I, антимодального II и нормального распределений приведены на фиг. 2.

На выходах третьего компаратора 19, четвертого компаратора 20, тринадцатого компаратора 47, четырнадцатого компаратора 48, пятнадцатого компаратора 49, шестнадцатого компаратора 50, семнадцатого компаратора 51 и восемнадцатого компаратора 52 соответственно формируются сигналы логического нуля, если сигнал на первых входах компараторов, пропорциональный значению энтропийного коэффициента Кэ: Кэ≥1,73; Кэ≥2,02; Кэ≥1,11; Кэ≥1,83; Кэ≥2,00; Кэ≥1,12; Кэ≥0,35; Кэ≥2,06 соответственно.

Выходы третьего компаратора 19, четвертого компаратора 20, тринадцатого компаратора 47, четырнадцатого компаратора 48, пятнадцатого компаратора 49, шестнадцатого компаратора 50, семнадцатого компаратора 51 и восемнадцатого компаратора 52 подключены соответственно к первому, второму, третьему, четвертому, пятому, шестому, седьмому и восьмому входам второго регистра 54.

Шестнадцатиразрядный код, получающийся на выходе компараторов 19-20, компараторов 26-28, компараторов 42-52 записывается в первый регистр 53 и второй регистр 54 сигналом записи, поступающий на десятые управляющие входы первого регистра 53 и второго регистра 54. Десятые входы первого регистра 53 и второго регистра 54 объединены и соединены с входной шиной, на которую подается сигнал записи.

Установка регистров в нулевое состояние при включении сети, а также перед началом очередного цикла анализа Tа производится автоматически, путем подачи сигнала обнуления на объединенные девятые входы первого регистра 53 и второго регистра 54. Объединенные девятые входы первого регистра 53 и второго регистра 54 соединены с входной шиной, на которую подается сигнал обнуления.

Первый, второй, пятый и шестой входы первого мультиплексора 55 соединены соответственно с первым, пятым, вторым и шестым выходами первого регистра 53, третий, седьмой, четвертый и восьмой выходы которого подключены соответственно к первому, второму, пятому и шестому входам второго мультиплексора 56. Третий, четвертый, седьмой и восьмой входы второго мультиплексора 56 соединены соответственно с третьим, седьмым, четвертым и восьмым выходами второго регистра 54. Первый, пятый, второй и шестой выходы второго регистра 54 подключены соответственно к третьему, четвертому, седьмому и восьмому входам первого мультиплексора 55. Содержимое первого регистра 53 и второго регистра 54 считываются через первый мультиплексор 55 и второй мультиплексор 56 в виде последовательности четырехразрядных кодов на первый дешифратор 29 (см, табл. 1), что позволяет вместо четырех дешифраторов использовать только один. Управление первым мультиплексором 55 и вторым мультиплексором 56 осуществляется сигналами управления, поступающие на девятые и десятые входы первого и второго мультиплексоров. Девятый вход первого мультиплексора 55 объединен с девятым входом второго мультиплексора 56 и соединены с входной шиной, на которую подается сигнал управления. Десятый вход первого мультиплексора 55 объединен с десятым входом второго мультиплексора 56 и соединены с входной шиной, на которую подается сигнал управления.

Первый регистр 53, второй регистр 54, первый мультиплексор 55 и второй мультиплексор 56 могут быть выполнены по схеме, приведенной в [7].

Первый и второй выходы первого мультиплексора 55 подключены соответственно к первому и второму входам первого дешифратора 29, третий и четвертый входы которого соединены соответственно с первым и вторым выходами второго мультиплексора 56.

Первый дешифратор 29 совместно с первым элементом И 57, вторым элементом И 58, третьим элементом И 59, четвертым элементом И 60, первым элементом И-НЕ 23, вторым элементом И-НЕ 61, третьим элементом И-НЕ 62, четвертым элементом И-НЕ 63, пятым элементом И-НЕ 64, шестым элементом И-НЕ 65 и седьмым элементом И-НЕ 66 обеспечивает преобразование четырехразрядного двоичного кода в семиразрядный код, соответствующий нестандартному шестнадцатиричному коду, который отображается семисигментным индикатором 9. Первый, второй, третий, четвертый, пятый, шестой и седьмой входы индикатора 9 соединены соответственно с выходами первого элемента И-НЕ 23, второго элементом И-НЕ 61, третьего элементом И-НЕ 62, четвертого элементом И-НЕ 63, пятого элементом И-НЕ 64, шестого элементом И-НЕ 65 и седьмого элементом И-НЕ 66, которые могут быть выполнены по схеме, приведенной в [7].

Для сокращения потребляемой мощности, а также сокращения аппаратурных затрат в устройстве используется динамическая индикация, что позволяет использовать одноканальный дешифратор 29, который может быть выполнен по схеме, приведенной в [7].

При этом содержимое первого регистра 53 и второго регистра 54 считывается в виде последовательности четырехразрядных параллельных двоичных чисел.

Синхронно со считыванием подается питание поочередно на элементы индикатора 9. Синхронизация переключений четырехразрядных кодов на первый дешифратор 29 и индикатор 9 осуществляется сигналами управления, одновременно поступающие соответственно на девятые и десятые входы первого мультиплексора 55 и второго мультиплексора 56, а также первый и второй входы второго дешифратора 22, которые соединены соответственно с девятыми и десятыми входами первого мультиплексора 55 и второго мультиплексора 56. Первый, второй, третий и четвертый выходы второго дешифратора 22 подключены соответственно к первым, вторым, третьим и четвертым входам коммутатора 67, пятый вход которого соединен с входной шиной, на которую подается напряжение питания. Первый, второй, третий и четвертый выходы коммутатора 67 подключены соответственно к восьмому, девятому, десятому и одиннадцатому входам индикатора 9.

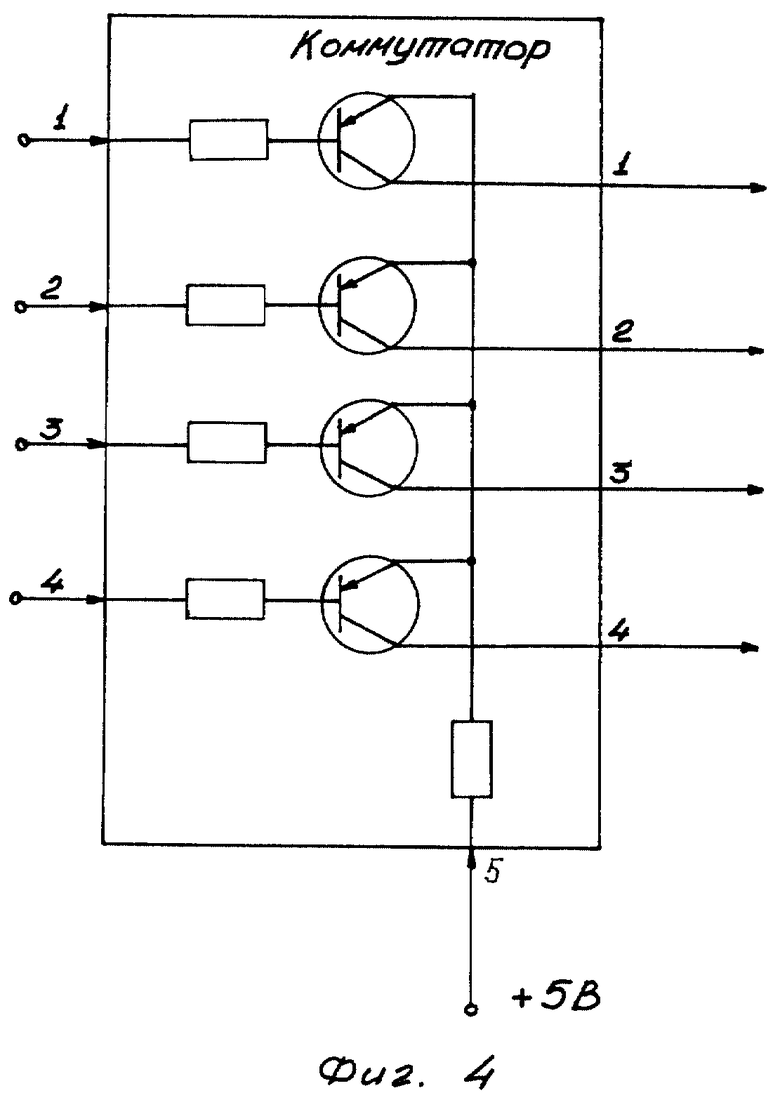

Второй дешифратор 22 обеспечивает коммутацию питания индикатора 9 синхронно с коммутацией первого мультиплексора 55 и второго мультиплексора 56 первого регистра 53 и второго регистра 54 и управляется теми же сигналами, что и мультиплексоры. Коммутация осуществляется с помощью транзисторных ключей коммутатора 67, который может быть выполнен по схеме, приведенной на фиг. 4 и управляемых сигналами второго дешифратора 22.

Вид закона распределения отображается на четырех знаковом семисегментном индикаторе 9, который может быть выполнен по схеме, приведенной в [7].

Семисегментный индикатор отображает информацию о виде закона распределения в нестандартном шестнадцатиричном коде, если на первом-четвертом входах первого дешифратора 29 последовательно присутствуют в виде четырех групп четырехразрядных параллельных двоичных чисел, приведенных в табл. 2.

При этом, если на индикаторе отображается код:

1. 7U00 - "распределение нормальное"

2. 3U80 - "распределение треугольное"

3. 03UF - "распределение арксинусоидальное"

4. 0UP0 - "распределение трапецеидальное - I"

5. IUF0 - "распределение трапецеидальное - II"

6. 01U8 - "распределение антимодальное - I"

7. 00UP - "распределение антимодальное - II"

8. 07U0 - "распределение равномерное"

9. UUUU - "распределение не симметричное"

10. Все остальные коды - "распределение не определено".

В известных технических решениях авторы не обнаружили совокупности признаков, аналогичных предлагаемым и обеспечивающих достижение цели изобретения.

В предлагаемом устройстве для изменения характеристик случайных процессов по сравнению с прототипом путем введения аналоговых и дискретных устройств повышена достоверность определения симметричного закона распределения. Совокупность введенных элементов обеспечивает новое качество устройства - повышает достоверность определения симметричного закона распределения случайных величин.

Источники информации:

1. Патент РФ N 2018952, кл. G 06 F 15/36, 30.08.94.

2. Патент РФ N 2007757, кл. G 06 G 7/52, 15.02.94.

3. Авторское свидетельство СССР N 926605, кл. G 01 R 29/04, 07.05.82.

4. Патент РФ N 2110806, кл. G 01 R 29/04, 10.05.98, прототип.

5. Вентцель Е.С. Теория вероятностей. - М.: Государственное издательство физ.- мат. литературы, 1962, 564 с.

6. Шишкин И.Ф. Основы метрологии, стандартизации и контроля качества. - М.: Изд-ва стандартов, 1988, 320 с.

7. Цифровые интегральные микросхемы. Справочник. М.И. Богданович, И.Н. Грель, В.А. Прохоренко, B.C. Шалимо. - Мн.: Беларусь, 1991, 493 с.

8. Аналоговые и цифровые интегральные микросхемы. Справочное пособие. Якубовский С.В., Барканов Н.А., Нисельсон Л.И. и др. / Под ред. С.В. Якубовского. 2-е изд., переработанное и доп. - М.: Радио и связь, 1984, 432 с.

9. Коломбет Е.А., Юркович К., Зодл Я. Применение аналоговых микросхем. - М.: Радио и связь, 1990, 320 с.

10. Новицкий П.В., Зограф И.А. Оценка погрешностей результатов измерений. - Л.: Энергоатомиздат. Ленинград. отд-ние, 1991, 304 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 1995 |

|

RU2110806C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 2006 |

|

RU2336562C2 |

| ИЗМЕРИТЕЛЬ ОТНОСИТЕЛЬНЫХ АМПЛИТУДНО-ЧАСТОТНЫХ ХАРАКТЕРИСТИК | 2001 |

|

RU2291452C2 |

| АВТОКОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ ПСЕВДОСЛУЧАЙНОГО ФАЗОМАНИПУЛИРОВАННОГО СИГНАЛА | 1991 |

|

RU2007875C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 2004 |

|

RU2280278C1 |

| ПАССИВНЫЙ ПРИЕМОПЕРЕДАТЧИК | 1999 |

|

RU2178897C2 |

| ИМПУЛЬСНО-ДОПЛЕРОВСКАЯ РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1997 |

|

RU2109306C1 |

| ДИСКРЕТНАЯ СИСТЕМА ОЦЕНИВАНИЯ | 2007 |

|

RU2398258C2 |

| РАСХОДОМЕР ТОПЛИВА | 1990 |

|

RU2035699C1 |

| АВТОКОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ ПСЕВДОСЛУЧАЙНОГО ФАЗОМАНИПУЛИРОВАННОГО СИГНАЛА | 1990 |

|

RU2011299C1 |

Изобретение относится к области радиоизмерений и может быть использовано для контроля характеристик случайных процессов. Техническим результатом является повышение достоверности определения вида закона распределения случайных величин. Изобретение содержит дешифратор, индикатор, элементы И-НЕ, нормирующий усилитель, двойной квадратичный детектор, интеграторы, делители, детекторы, умножитель, элемент ИЛИ-НЕ, блоки извлечения квадратного корня, элементы И, умножители, компараторы, ключи и коммутатор. 2 табл, 5 ил.

Устройство для измерения характеристик случайных процессов, содержащее первый дешифратор, индикатор, первый элемент И-НЕ, нормирующий усилитель, вход которого соединен с входной шиной, а выход через последовательно соединенные двойной квадратичный детектор и первый интегратор подключен к первому входу первого делителя, при этом выход нормирующего усилителя через последовательно соединенные первый детектор, второй интегратор и второй детектор подключен также к второму входу первого делителя, последовательно соединенные первый умножитель, третий интегратор и второй делитель, выход которого подключен одновременно к первым входам первого и второго компараторов, вторые входы которых соединены соответственно с входными шинами, а выходы подключены соответственно к первому и второму входам элемента ИЛИ-НЕ, при этом первый вход второго умножителя непосредственно, а второй вход через первый блок извлечения квадратного корня подключены к выходу второго интегратора, выход второго умножителя подключен к второму входу второго делителя, при этом первый вход первого умножителя непосредственно, а второй через третий детектор подключены к выходу нормирующего усилителя, при этом выход третьего делителя подключен к первому входу первого ключа, выход которого подключен одновременно к первым входам пятого, шестого и седьмого компараторов, вторые входы которых соединены соответственно с входными шинами, первые входы третьего и четвертого компараторов объединены, вторые входы которых соединены соответственно с входными шинами, отличающееся тем, что в него дополнительно введены восьмой, девятый, десятый, одиннадцатый и двенадцатый компараторы, вторые входы которых соединены соответственно с входными шинами, а объединенные первые входы соединены с выходом первого ключа, второй вход которого одновременно соединен с выходом элемента ИЛИ-НЕ и вторым входом второго ключа, выход которого одновременно подключен к первым входам третьего, четвертого, тринадцатого, четырнадцатого, пятнадцатого, шестнадцатого, семнадцатого и восемнадцатого компараторов, вторые входы которых соединены соответственно с входными шинами, при этом введены второй, третий, четвертый, пятый, шестой и седьмой элементы И-НЕ, выходы которых соответственно подключены к второму, третьему, четвертому, пятому, шестому и седьмому входам индикатора, первый вход которого соединен с выходом первого элемента И-НЕ, а восьмой, девятый, десятый и одиннадцатый входы соединены соответственно с первым, вторым, третьим и четвертым выходами коммутатора, пятый вход которого соединен с входной шиной, а первый, второй, третий и четвертый входы соединены соответственно с первым, вторым, третьим и четвертым выходами второго дешифратора, первый вход которого одновременно соединен с входной шиной и объединенными девятыми входами первого и второго мультиплексоров, при этом второй вход второго дешифратора одновременно соединен с входной шиной и объединенными десятыми входами первого и второго мультиплексоров, а объединенные девятые и объединенные десятые входы первого и второго регистров соединены соответственно с входными шинами, первый, второй, пятый и шестой входы первого мультиплексора соединены соответственно с первым, пятым, вторым и шестым выходами первого регистра, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами пятого, шестого, седьмого, восьмого, девятого, десятого, одиннадцатого и двенадцатого компараторов, при этом третий, седьмой, четвертый и восьмой выходы первого регистра подключены соответственно к первому, второму, пятому и шестому входам второго мультиплексора, третий, четвертый, седьмой и восьмой входы которого соединены соответственно с третьим, седьмым, четвертым и восьмым выходами второго регистра, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с выходами третьего, четвертого, тринадцатого, четырнадцатого, пятнадцатого, шестнадцатого, семнадцатого и восемнадцатого компараторов, а первый, пятый, второй и шестой выходы второго регистра подключены соответственно к третьему, четвертому, седьмому и восьмому входам первого мультиплексора, первый и второй выходы которого подключены соответственно к первому и второму входам первого дешифратора, третий и четвертый входы которого соединены соответственно с первым и вторым выходами второго мультиплексора, второй выход первого дешифратора одновременно подключен к первым входам первого и второго элементов И, вторые входы которых соответственно соединены с пятым и восьмым выходами первого дешифратора, десятый выход которого подключен к второму входу четвертого элемента И-НЕ, первый вход которого одновременно соединен с первыми входами третьего и второго элементов И-НЕ и двенадцатым выходом первого дешифратора, одиннадцатый выход которого одновременно подключен к объединенным второму входу седьмого элемента И-НЕ, третьему входу третьего элемента И-НЕ и второму входу второго элемента И-НЕ, при этом первый выход первого дешифратора подключен к четвертому входу седьмого элемента И-НЕ, третий вход которого одновременно соединен с третьим входом первого элемента И-НЕ и пятнадцатым выходом первого дешифратора, четырнадцатый выход которого подключен к объединенным вторым входам четвертого элемента И и третьего элемента И-НЕ, четвертый вход которого одновременно соединен с вторым входом шестого элемента И-НЕ и третьим выходом первого дешифратора, тринадцатый выход которого одновременно подключен к первым входам четвертого элемента И и первого элемента И-НЕ, объединенные второй и четвертый входы которого одновременно соединены с выходом первого элемента И и первым входом третьего элемента И, выход которого одновременно подключен к четвертому входу четвертого элемента И-НЕ и первому входу пятого элемента И-НЕ, второй вход которого одновременно соединен с первым входом шестого элемента И-НЕ и четвертым выходом первого дешифратора, шестой выход которого одновременно подключен к объединенным четвертым входам пятого и второго элементов И-НЕ, при этом седьмой выход первого дешифратора подключен к третьему входу второго элемента И-НЕ, а девятый выход подключен к третьему входу пятого элемента И-НЕ, выход второго элемента И одновременно подключен к второму входу третьего элемента И, первому входу седьмого элемента И-НЕ и объединенным четвертому и третьему входам шестого элемента И-НЕ, а выход четвертого элемента И подключен к третьему входу четвертого элемента И-НЕ, при этом вход второго блока извлечения квадратного корня соединен с выходом первого делителя, а выход подключен к первому входу третьего делителя, второй вход которого соединен с входной шиной, первые входы первого и второго амплитудных селекторов одновременно соединены с выходом нормирующего усилителя, а вторые входы соединены соответственно с первым и вторым выходами генератора ступенчатого напряжения, вход которого соединен с входной шиной, при этом выходы первого и второго амплитудных селекторов подключены соответственно к первому и второму входам вычитающего устройства, выход которого подключен к входу четвертого интегратора, выход которого одновременно подключен к входу логарифмического усилителя и второму входу третьего умножителя, первый вход которого соединен с выходом логарифмического усилителя, а выход подключен к входу пятого интегратора, выход которого подключен к входу блока вычисления экспоненциальной функции, выход которого подключен к первому входу четвертого делителя, второй вход которого соединен с входной шиной, а выход подключен к первому входу пятого делителя, второй вход которого соединен с выходом первого блока извлечения квадратного корня, а выход подключен к первому входу второго ключа.

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 1995 |

|

RU2110806C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СТАТИСТИЧЕСКИХ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 1991 |

|

RU2018952C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНОГО ПРОЦЕССА | 1991 |

|

RU2007757C1 |

| Устройство для измерения характеристик случайных процессов | 1980 |

|

SU926605A1 |

| ВЕНТЦЕЛЬ Е.C | |||

| Теория вероятностей | |||

| - М.: Государственное издательство физико-математической литературы, 1962, с.149-154 | |||

| SU 922805 A, 23.04.1982 | |||

| ЗАХВАТНОЕ УСТРОЙСТВО К АВТОПОГРУЗЧИКУ | 0 |

|

SU177058A1 |

Авторы

Даты

2001-06-10—Публикация

1999-04-19—Подача