Изобретение относится к радиотехнике и автоматике, в частности может использоваться в радиолокации для высокоточного оценивания координатной информации.

Известны дискретные системы [1, 2, 3], предназначенные для оценивания параметров движения объектов. Эти системы позволяют оптимальным образом оценивать входную информацию при известном законе движения объекта и заданных характеристиках канала наблюдения.

Недостатком данных систем является низкая точность оценивания при изменении параметров движения объекта наблюдения. Известна также дискретная система оценивания [4], содержащая последовательно соединенные элементы сравнения, блок коррекции, сумматор, блок задержки, блок экстраполяции, блок обратной связи, а также первый и второй вычислительные блоки, второй элемент сравнения и блок управления. Данная система позволяет получить оптимальную оценку при изменении динамических свойств объекта наблюдения, однако она не ориентирована на качественное управление динамической точностью в переходном режиме.

Наиболее близкой к предлагаемой является дискретная система оценивания [5], имеющая возможность качественного управления динамической точностью в переходном режиме.

Общими признаками этой системы с предлагаемой являются: последовательно соединенные - первый вычитатель, блок коррекции, первый сумматор, блок задержки, блок экстраполяции, а также второй и третий вычитатели, второй сумматор, счетчик, компаратор, двухканальный мультиплексор, элементы памяти коэффициентов и умножитель.

К признакам данной системы, устраняемым предложением, относятся последовательно соединенные блок задержки, вход которого соединен с выходом первого вычитателя, и усилитель, выход которого подключен к первой группе информационных входов мультиплексора.

Недостатком системы [5] является низкая точность оценивания при изменении динамических параметров объекта наблюдения.

Цель изобретения - повышение точности оценивания системы при изменении динамических параметров объекта наблюдения.

Эта цель достигается за счет введения в известную систему блоков идентификации, управления и режимов работы.

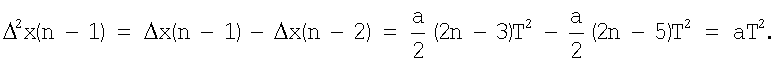

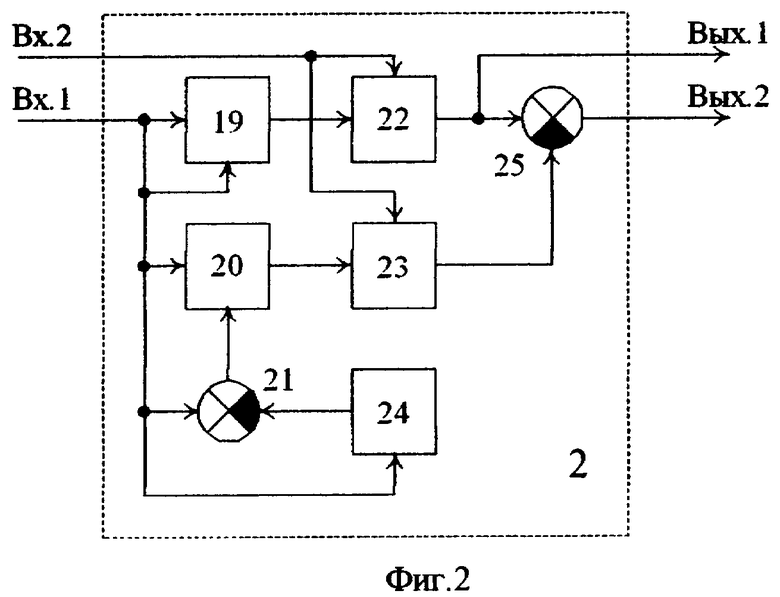

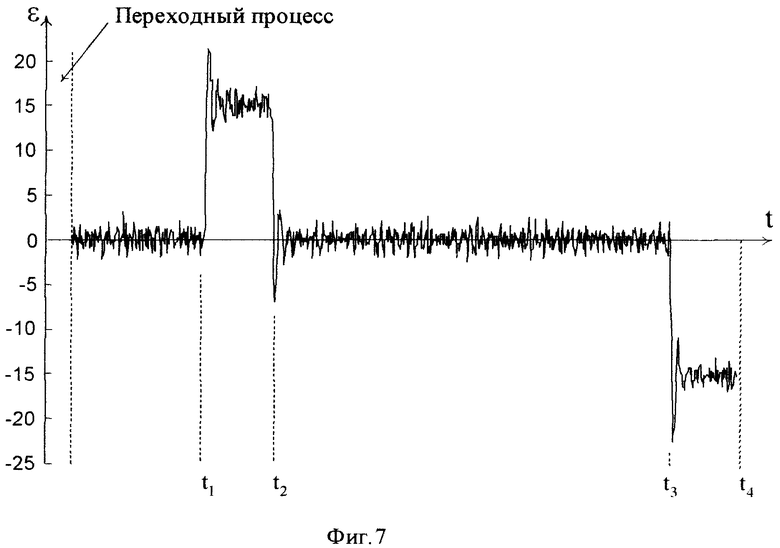

На фиг.1 изображена структурная схема предлагаемой системы оценивания, на фиг.2 - структурная схема блока идентификации, на фиг.3 - структурная схема блока вычисления математического ожидания, на фиг.4 - структурная схема блока коррекции, на фиг.5 - структурная схема блока управления.

Дискретная система оценивания (фиг.1) содержит вычитатели 1, 8, 9, блок 2 идентификации, блок 3 коррекции, сумматоры 4, 15, блок 5 задержки с оператором задержки Z-1, блок 6 экстраполяции, блок 7 управления, счетчик 10, двухканальный мультиплексор 11, блок 12 режимов работы, компаратор 13, умножитель 14, элементы 16-18 памяти коэффициентов.

В статическом состоянии система оценивания характеризуется следующими связями: содержит последовательно соединенные вычитатель 1, блок 3 коррекции, сумматор 4, блок 5 задержки, блок 6 экстраполяции, а также вычитатели 8 и 9, сумматор 15, счетчик 10, компаратор 13, двухканальный мультиплексор 11, элементы 16-18 памяти коэффициентов и умножитель 14. Первый вход умножителя 14 соединен с первым выходом блока 6 экстраполяции, второй вход - с первым выходом мультиплексора 11, а выход - с первыми входами сумматора 15 и вычитателя 8. Выход вычитателя 8 подключен ко второму входу вычитателя 1. Второй выход мультиплексора 11 соединен со вторым входом сумматора 15, подключенного выходом ко второму входу вычитателя 9. Выход вычитателя 9 соединен со вторым входом сумматора 4. Выход счетчика 10 подключен к первому входу компаратора 13 и к адресному входу мультиплексора 11. Вторая группа информационных входов мультиплексора 11 соединена с выходами элементов 16-18 памяти коэффициентов. Первый вход вычитателя 1 и выход сумматора 4 являются соответственно информационным входом и выходом дискретной системы оценивания. Второй вход компаратора 13 соединен с шиной задания числа шагов. Тактовый вход счетчика 10 является тактовым входом системы. Кроме того, система оценивания содержит блок 2 идентификации, блок 7 управления и блок 12 режимов работы. Вход блока 12 подключен к выходу компаратора 13, первый выход - к установочному входу счетчика 10, а второй выход - ко второму входу блока 7 управления. Первый и третий входы блока 7 управления соединены соответственно со вторым выходом блока 6 экстраполяции и с тактовым входом системы оценивания, а четвертый вход - с шиной задания глубины памяти, подключенной ко второму входу блока 2 идентификации. Первый вход блока 2 идентификации соединен с выходом вычитателя 1, а первый и второй выходы подключены соответственно ко второму и третьему входам блока 3 коррекции. Второй выход блока 3 коррекции соединен с первой группой информационных входов мультиплексора 11, а четвертый и пятый входы - соответственно со вторым и третьим выходами блока 7 управления. Первый выход блока 7 управления подключен ко второму входу вычитателя 8 и первому входу вычитателя 9.

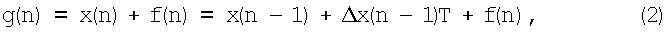

Система может функционировать в двух режимах: набора статистики и идентификации. Режим идентификации является основным. В этом режиме система работает следующим образом. Входной сигнал системы g(n), представляющий собой сумму полезного сигнала х(n) и ошибок измерения (помех) f(n), поступает на первый вход вычитателя 1. На его второй вход подается экстраполированное значение входного сигнала  от блока 6 экстраполяции через блок 7 управления и вычитатель 8. На выходе вычитателя 1 имеем сигнал невязки

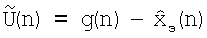

от блока 6 экстраполяции через блок 7 управления и вычитатель 8. На выходе вычитателя 1 имеем сигнал невязки  . Этот сигнал поступает на первый вход блока 2 для последующего вычисления дисперсий ошибок экстраполяции и ошибок измерений, а также на первый вход блока 3 для вычисления значений

. Этот сигнал поступает на первый вход блока 2 для последующего вычисления дисперсий ошибок экстраполяции и ошибок измерений, а также на первый вход блока 3 для вычисления значений  , корректирующих величину экстраполированного сигнала

, корректирующих величину экстраполированного сигнала  . В режиме идентификации счетчик 10, мультиплексор 11, компаратор 13, умножитель 14, сумматор 15, элементы 16-18 памяти коэффициентов не используются. Поэтому информация на первом входе вычитателя 8 отсутствует и не влияет на формирование сигнала

. В режиме идентификации счетчик 10, мультиплексор 11, компаратор 13, умножитель 14, сумматор 15, элементы 16-18 памяти коэффициентов не используются. Поэтому информация на первом входе вычитателя 8 отсутствует и не влияет на формирование сигнала  . На выходе сумматора 4 имеем сигнал оценки

. На выходе сумматора 4 имеем сигнал оценки  :

:

Первые два члена в правой части выражения (1) являются сигналом  , K(n) - весовой коэффициент. Сигнал

, K(n) - весовой коэффициент. Сигнал  формируется блоком 6 экстраполяции из условия, что входное воздействие на систему имеет вид:

формируется блоком 6 экстраполяции из условия, что входное воздействие на систему имеет вид:

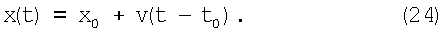

где x(n-1) - положение объекта в (n-1) - момент времени, Δx(n-1) - скорость объекта, n - дискретное время, Т - период обработки информации.

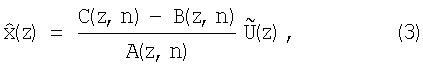

Для исключения динамической ошибки в системе, входное воздействие которой имеет вид (2), необходимо иметь порядок астатизма ν=2. Синтез такой системы возможен на основе метода "трех полиномов" [5, 6]. Используя выражение для оценки

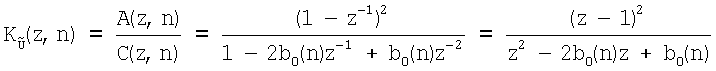

определим полиномы A(z,n), B(z,n), C(z,n) в виде:

Характеристический полином C(z, n) выбирается из условий устойчивости системы.

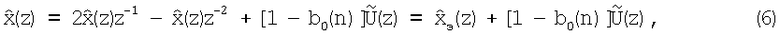

Подставляя (4) в (3) имеем

где  - невязка.

- невязка.

После преобразования (5) получим выражение для оценки в операторном виде

Представление выражения (6) во временной области приводит к уравнению (1).

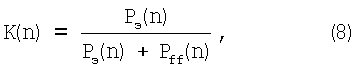

Так как входное воздействие (2) содержит ошибки измерения (помехи) f(n), то помимо исключения динамической ошибки в системе должны быть минимизированы дисперсии ошибок оценивания. Выполнение данной процедуры с использованием результатов теории оптимальной линейной фильтрации, например [7], приводит к определению оптимального коэффициента К(n) в виде:

где Рэ(n) - дисперсия ошибок экстраполяции, Рff(n) - дисперсия ошибок измерения.

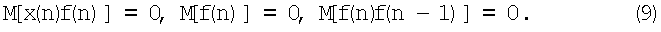

При определении К(n), так же как и в [7], предполагалось, что

Таким образом, величина К(n) в уравнении (1) определяется согласно выражению (8).

Решение задачи повышения точности оценивания системы при изменении статических характеристик наблюдаемого процесса возможно при выполнении следующего условия: по результатам измерений должны вычисляться дисперсии ошибок экстраполяции и измерения, а следовательно, и весовой коэффициент (в отличие от прототипа и указанных аналогов, где значение весового коэффициента рассчитывается теоретически).

Данное условие реализуется при помощи блока 2 идентификации и блока 3 коррекции.

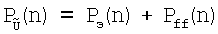

Блок 2 идентификации (фиг.2) содержит умножители 19, 20, вычитатели 21, 25, блок 24 задержки с оператором задержки Z-1, блоки 22, 23 вычисления математического ожидания. На первый вход блока 2 поступает сигнал невязки  с выхода вычитателя 1. На выходе блока 22, являющемся первым выходом блока 2, формируется сигнал

с выхода вычитателя 1. На выходе блока 22, являющемся первым выходом блока 2, формируется сигнал  . На выходе вычитателя 25, являющемся вторым входом блока 2, формируется сигнал Рэ(n).

. На выходе вычитателя 25, являющемся вторым входом блока 2, формируется сигнал Рэ(n).

Блок 2 работает следующим образом. Сигнал невязки

поступающий на первый вход блока, содержит информацию об ошибках экстраполяции  и ошибках измерения f(n). Так как ошибка оценки ортогональна наблюдениям [8], то это утверждение справедливо и в отношении ошибок экстраполяции. Поэтому с учетом (9) имеем

и ошибках измерения f(n). Так как ошибка оценки ортогональна наблюдениям [8], то это утверждение справедливо и в отношении ошибок экстраполяции. Поэтому с учетом (9) имеем

Вычисление математического ожидания согласно выражению (10) реализуется умножителем 19 и блоком 22.

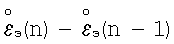

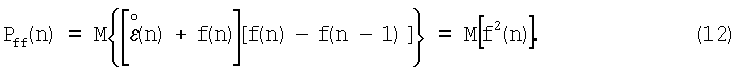

Умножитель 20, вычитатель 21, блоки 23, 24 предназначены для вычисления дисперсии ошибок измерения

где  - первая разность невязки

- первая разность невязки  , формируемая вычитателем 21 и блоком 24 задержки.

, формируемая вычитателем 21 и блоком 24 задержки.

При отсутствии в системе динамической ошибки разность  стремится к нулю, поэтому

стремится к нулю, поэтому  . Принимая во внимание допущения, использованные при определении (10), имеем

. Принимая во внимание допущения, использованные при определении (10), имеем

На выходе вычитателя 25 формируется сигнал.

Таким образом, блок 2 позволяет по результатам измерений вычислить (идентифицировать) дисперсии ошибок экстраполяции и измерения.

Второй вход блока 2 подключается к шине задания глубины L памяти и используется блоками 22, 23 вычисления математического ожидания. Структурная схема этих блоков показана на фиг.3. Они содержат блоки 26-29, 34 задержки с оператором задержки Z-1, вычитатели 30, 33, сумматор 32, мультиплексор 31, блок 35 деления, элемент 36 памяти.

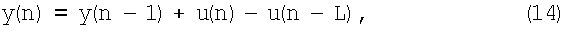

В основе работы блоков вычисления математического ожидания лежит метод определения скользящей суммы [9] с использованием рекуррентного уравнения вида:

где u(n) - входная информация, y(n) - скользящая сумма за L-тактов.

На выходе блока 35 формируется математическое ожидание my(n) путем деления скользящей суммы на величину L-1. Деление на L-1, а не на L обусловлено стремлением получить несмещенную величину дисперсий [10]. Мультиплексор 31 позволяет в зависимости от требуемой точности задавать глубину памяти в цепи последовательно включенных блоков 26-29 задержки. Вычитатель 33 позволяет использовать в мультиплексоре 31 информационные входы, имеющие код адреса, меньший, чем выбранная глубина памяти. Это достигается путем выполнения операции вычитания над кодом L выбранной и кодом К минимально необходимой глубины памяти, хранимым в элементе памяти 36. Например, если L=3 и К=3, то на выход мультиплексора будет коммутироваться выход третьего в цепи блока задержки по информационному входу, имеющему код адреса, равный нулю. При L=4 и К=3 будет скоммутирован информационный вход, имеющий код адреса, равный единице, и т.д.

На фиг.4 показана структурная схема блока 3 коррекции. Она содержит блок 37 деления, блоки 38, 44 логического умножения, блок 39 инвертирования, блок 40 памяти, блок 41 задержки с оператором задержки Z-1, умножители 42, 46, блок 43 логического сложения, мультиплексор 45, вычитатель 47, элемент 48 памяти.

Блок 3 коррекции в режиме идентификации работает следующим образом. На второй и третий входы блока 3, являющиеся входами блока 37 деления, поступает информация с первого и второго выходов блока 2 в виде - Рэ(n)+Pff(n) и Рэ(n). На выходе блока 37 формируется значение весового коэффициента К(n) в соответствии с выражением (8). Это значение поступает на первый вход блока 38, выполняющего роль переключателя в зависимости от уровня сигнала на его втором входе. Второй вход блока 38, являющийся четвертым входом блока 3, связан со вторым выходом блока 7 управления (фиг.5). Высокий уровень напряжения (логическая "1") возникает на этом выходе только тогда, когда количество тактов обработки информации стало равно или превысило коэффициент глубины памяти, т.е.

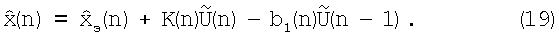

При выполнении данного условия значение К(n) через блоки 38 и 43 поступает в умножитель 42, где, перемножаясь с сигналом невязки  , подающимся на первый вход блока 3, формирует корректировочное значение

, подающимся на первый вход блока 3, формирует корректировочное значение  в сигнал оценки

в сигнал оценки  [см. выражение (1)]. Выход умножителя 42 является первым выходом блока 3.

[см. выражение (1)]. Выход умножителя 42 является первым выходом блока 3.

Блоки 39, 40, 41, 44, мультиплексор 45, умножитель 46, вычитатель 47 и элемент 48 памяти используются в режиме набора статистики.

Структурная схема блока 7 управления показана на фиг.5. Она содержит счетчик 49, компаратор 50, триггер 51, блоки 52, 53 логического умножения, блок 54 инвертирования, блок 55 логического сложения.

Блок 7 в режиме идентификации позволяет подавать значение экстраполированного сигнала

сформированного блоком 6 экстраполяции, соответственно на второй и первый входы вычитателей 8 и 9. Это осуществляется следующим образом. При выполнении условия (15) высокий уровень напряжения подается на второй вход блока 52. На его первый вход, являющийся первым входом блока 7, подается сигнал (16) со второго выхода блока 6. С выхода блока 52 через блок 55, выход которого является первым выходом блока 7 управления, этот сигнал поступает на входы вычитателей 8 и 9. Так как в режиме идентификации поступление информации на первый вход вычитателя 8 и второй вход вычитателя 9 заблокировано мультиплексором 11, то на выходе вычитателя 1 формируется невязка  , где

, где  определяется в соответствии с (16). На выходе сумматора 4 имеем сигнал оценки в виде (1).

определяется в соответствии с (16). На выходе сумматора 4 имеем сигнал оценки в виде (1).

Работу счетчика 49, компаратора 50, триггера 51, блоков 53, 54 отнесем к режиму набора статистики.

Структурная схема блока 6 экстраполяции такая же, как и в прототипе. С первого выхода блока снимается сигнал разности второго порядка

поступающий на первый вход умножителя 14, со второго выхода - сигнал вида (16).

Режим набора статистики предназначен для заполнения информацией блоков 22, 23 вычисления математического ожидания блока 2 идентификации на заданную глубину памяти L и для управления системой в переходном режиме.

В режиме набора статистики система работает следующим образом. При включении устройства блок 12 режимов работы вырабатывает импульс, поступающий с его второго выхода на второй вход блока 7 и устанавливающий триггер 51 этого блока в нулевое состояние. На втором выходе блока 12 после включения устройства устанавливается высокий уровень напряжения. Перед началом работы системы на второй вход компаратора 13 подается код N числа шагов работы системы в переходном режиме, а на второй вход блока 2 и четвертый вход блока 7 - код L глубины памяти. На вход счетчика 10 и на третий вход блока 7 поступает последовательность импульсов nТ, синхронная моментам выдачи информации. Выходные сигналы счетчика 10 поступают на адресный вход мультиплексора 11 (в качестве которого может быть использована, например, микросхема К155КП2).

Управление системой в переходном режиме, позволяющее улучшить качество переходного процесса, осуществляется алгоритмом управления вида [5]:

При этом выражение для оценки -

При этом выражение для оценки -

Перед началом работы системы на ее вход поступает сигнал о предполагаемом положении объекта, отличающийся от истинного на некоторую величину. Эту величину можно рассматривать как ступенчатое воздействие на систему, обусловленное априорной неопределенностью состояния объекта.

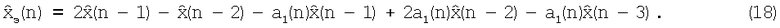

Для улучшения качества переходного процесса заранее, например по методике изложенной в [5], вычисляются коэффициенты a1(n) и количество шагов оптимизации N. При воздействии на вход ступенчатого воздействия N=3. Следовательно, в блоки 16-18 записываются коэффициенты a1(1), a1(2) и a1(3). В первом такте работы системы коэффициент a1(1) считывается из элемента 16 памяти и проходит через мультиплексор 11 на второй вход умножителя 14, в котором перемножается с сигналом (17), поступающим на его первый вход с первого выхода блока 6. На выходе умножителя 14 формируется сигнал  .

.

В то же время по второму каналу мультиплексора 11 поступает сигнал  со второго выхода блока 3 коррекции на второй вход сумматора 15. Информация с выхода умножителя 14 подается на первые входы сумматора 15 и вычитателя 8. На выходе сумматора 15 имеем сигнал

со второго выхода блока 3 коррекции на второй вход сумматора 15. Информация с выхода умножителя 14 подается на первые входы сумматора 15 и вычитателя 8. На выходе сумматора 15 имеем сигнал  . В результате на выходе вычитателя 8 формируется сигнал управления (18), а на выходе вычитателя 9 сигнал вида (19) без значения

. В результате на выходе вычитателя 8 формируется сигнал управления (18), а на выходе вычитателя 9 сигнал вида (19) без значения  . Это значение добавляется в сумматоре 4, и на выходе системы имеем сигнал оценки (19). В следующих двух тактах формирование сигналов осуществляется аналогично для коэффициентов а1(2), а1(3), b1(2), b1(3).

. Это значение добавляется в сумматоре 4, и на выходе системы имеем сигнал оценки (19). В следующих двух тактах формирование сигналов осуществляется аналогично для коэффициентов а1(2), а1(3), b1(2), b1(3).

Коэффициенты b1(n) определяются из выражения

где Δуст - запас на устойчивость системы.

В режиме набора статистики коэффициенты К(n) определяются заранее, например по алгоритму [7], и записываются в блок 40 памяти блока 3 коррекции. Считывание данного коэффициента из блока 40 производится следующим образом. Третий вход блока 7 (см. фиг.5), на который поступает последовательность импульсов nТ, является тактовым входом счетчика 49. Выходные сигналы счетчика 49 поступают через третий выход блока 7 на пятый вход блока 3 (см. фиг.4), являющийся адресным входом мультиплексора 45 (в качестве которого может быть использована, например, микросхема К155КП7). В соответствии с кодом адреса производится считывание значения К(n) из соответствующей ячейки блока 40. Так как в режиме набора статистики количество тактов обработки информации меньше коэффициента глубины памяти, т.е.

то на втором выходе блока 7 (см. фиг.5), являющемся выходом триггера 51, присутствует уровень логического "0". Этот сигнал поступает на четвертый вход блока 3 (см. фиг.4) и инвертируется блоком 39. Сигнал логической "1" с выхода блока 39 разрешает прохождение считанного из блока 40 и появившегося на выходе мультиплексора 45 значения К(n) через блок 44.

Формирование коэффициента b1(n), согласно выражения (20), осуществляется вычитателем 47 и элементом 48 памяти, в котором хранится значение Δуст. На первый вход умножителя 46 поступает сигнал  с выхода блока 41, на его второй вход подается значение b1(n) с выхода вычитателя 47. На выходе умножителя 46, являющемся вторым выходом блока 3, формируется корректировочное значение

с выхода блока 41, на его второй вход подается значение b1(n) с выхода вычитателя 47. На выходе умножителя 46, являющемся вторым выходом блока 3, формируется корректировочное значение  .

.

При достижении счетчиком 10 числа N компаратор 13 вырабатывает сигнал, устанавливающий первый выход блока 12 в нулевое состояние. Этим сигналом счетчик 10 обнуляется и остается в этом состоянии в течение оставшегося времени работы системы.

Блок 12 режимов работы представляет собой последовательное соединение формирователя установочных импульсов при включении устройства и триггер. Первым выходом блока 13 является выход триггера, вторым выходом - выход формирователя.

После остановки счетчика 10 считывание коэффициентов a1(n) из элементов 16-18 прекращается, и сигналы вида (18) и (19) формироваться не будут.

В следующих тактах работы системы, пока выполняется условие (21), выходные сигналы счетчика 49 блока 7 (см. фиг.5) поступают на адресный вход мультиплексора 45 блока 3 (см. фиг.4). При этом из блока 40 производится считывание последующих значений К(n), которые используются для формирования корректировочного значения  . Поскольку выключенный счетчик 10 блокирует работу мультиплексора 11, то на первом входе вычитателя 8 и втором входе вычитателя 9 информация будет отсутствовать. На второй вход вычитателя 8 и первый вход вычитателя 9 при этом подается значение

. Поскольку выключенный счетчик 10 блокирует работу мультиплексора 11, то на первом входе вычитателя 8 и втором входе вычитателя 9 информация будет отсутствовать. На второй вход вычитателя 8 и первый вход вычитателя 9 при этом подается значение  вида (16) с первого выхода блока 7. В данном случае этот сигнал со второго выхода блока 6 проходит на первый выход блока 7 через блоки 53, 55 (см. фиг.5). Возможность прохождения сигнала через блок 53 обусловлена высоким уровнем напряжения на его втором входе, которое подается с выхода блока 54. В результате на выходе системы происходит формирование сигнала вида (1).

вида (16) с первого выхода блока 7. В данном случае этот сигнал со второго выхода блока 6 проходит на первый выход блока 7 через блоки 53, 55 (см. фиг.5). Возможность прохождения сигнала через блок 53 обусловлена высоким уровнем напряжения на его втором входе, которое подается с выхода блока 54. В результате на выходе системы происходит формирование сигнала вида (1).

При достижении счетчиком 49 числа L компаратор 50 вырабатывает сигнал, устанавливающий триггер 51 в единичное состояние. Сигнал логической "1" с выхода этого триггера блокирует работу блоков, используемых в режиме набора статистики, и разрешает работу блоков в режиме идентификации.

Из рассмотрения работы системы следует, что в ней в режиме идентификации вычисляются дисперсии ошибок экстраполяции и измерения, реальные значения весового коэффициента. Это позволяет повысить точность оценивания системы при изменении статических характеристик наблюдаемого процесса, вызванном изменением динамических свойств объекта.

Возможность качественного управления в переходном режиме позволяет набрать статистику измерений, требуемую в режиме идентификации, с наименьшими искажениями.

Существенные признаки, характеризующие изобретение заключены в том, что в известную из а.с. №1727110 систему оценивания, содержащую последовательно соединенные вычитатель 1, блок 3 коррекции, сумматор 4, блок 5 задержки, блок 6 экстраполяции, а также вычитатели 8 и 9, сумматор 15, счетчик 10, компаратор 13, двухканальный мультиплексор 11, элементы 16-18 памяти коэффициентов и умножитель 14, первый вход которого подключен к первому выходу блока 6 экстраполяции, второй вход - к первому выходу мультиплексора 11, а выход - к первым входам сумматора 15 и вычитателя 8, соединенного выходом со вторым входом вычитателя 1, второй выход мультиплексора 11 подключен ко второму входу сумматора 15, соединенного с выходом со вторым входом вычитателя 9, выход которого подключен ко второму входу сумматора 4, выход счетчика 10 соединен с первым входом компаратора 13 и с адресным входом мультиплексора 11, вторая группа информационных входов которого подключена к выходам элементов 16-18 памяти коэффициентов, первый вход вычитателя 1 и выход сумматора 4 являются соответственно информационным входом и выходом дискретной системы оценивания, второй вход компаратора 13 соединен с шиной задания числа шагов, тактовый вход счетчика 10 является тактовым входом системы, введены блок 2 идентификации, блок 7 управления и блок 12 режимов работы, соединенный входом с выходом компаратора 13, первым выходом - с установочным входом счетчика 10, а вторым выходом - со вторым входом блока 7 управления, первый и третий входы которого подключены соответственно ко второму выходу блока 6 экстраполяции и к тактовому входу системы оценивания, а четвертый вход - к шине задания глубины памяти, соединенной со вторым входом блока 2 идентификации, первый вход которого подключен к выходу вычитателя 1, а первый и второй выходы соединены соответственно со вторым и третьим входами блока 3 коррекции, подключенного вторым выходом к первой группе информационных входов мультиплексора 11, а четвертым и пятым входами - соответственно ко второму и третьему выходам блока 7 управления, первый выход которого соединен со вторым входом вычитателя 8 и первым входом вычитателя 8 и первым входом вычитателя 9.

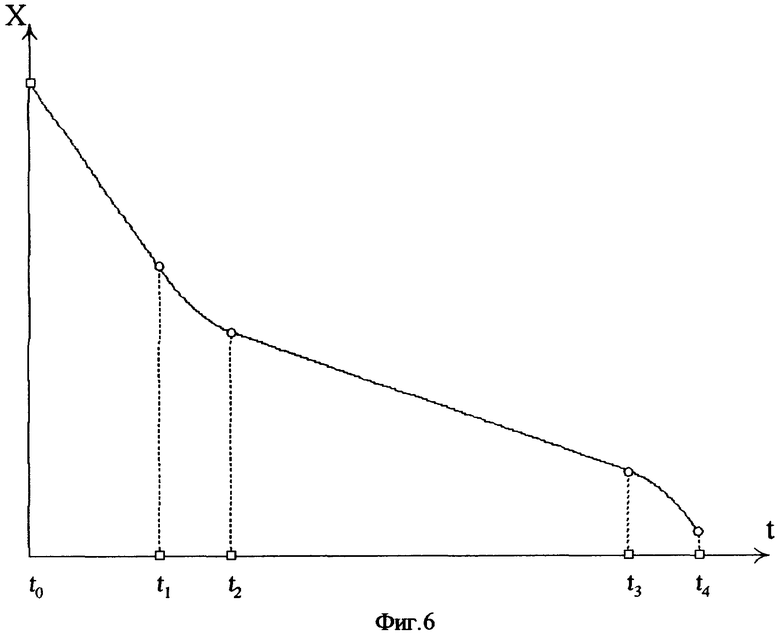

С целью подтверждения эффективности предлагаемой системы было проведено цифровое моделирование на ЭВМ. Входной сигнал системы представляет собой аддитивную смесь полезного сигнала и помехи -

Модель движения объекта описывается полиномиальным законом

где - x0, v, a, b - начальное значение положения объекта, его скорость, ускорение, изменение ускорения соответственно, t0 - момент времени, соответствующий точке разложения функции x(t) в степенной ряд.

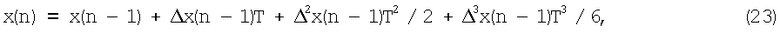

Выражение (22) можно представить в дискретном времени, используя соотношения: t=nT→n, t-t0=Т, v≡Δх, а≡Δ2x, b≡Δ3x.

Тогда

где Δx(n-1), Δ2x(n-1), Δ3x(n-1) - первая, вторая и третья разности от входного воздействия, Т - темп обработки информации.

График модели движения объекта, рассчитанный по выражению (22), представлен на фиг.6. Здесь на интервалах времени (t0, t1) и (t2, t3) модель движения описывается выражением.

На интервале времени (t1, t2) в уравнении (24) вводится ускорение.

Тогда

На интервале времени (t3, t4) в уравнении (25) вводится изменение ускорения. В результате имеем модель движения, описываемую (22).

Помеха f(n) моделируется с помощью датчика случайных чисел с распределением по нормальному закону и нулевым математическим ожиданием.

Эффективность предлагаемой системы оценивалась по точностной характеристике системы - ошибке оценивания, определяемой в соответствии с выражением

Прототип исследовался при ограничении нижнего предела величины К(n) на уровне 0,2.

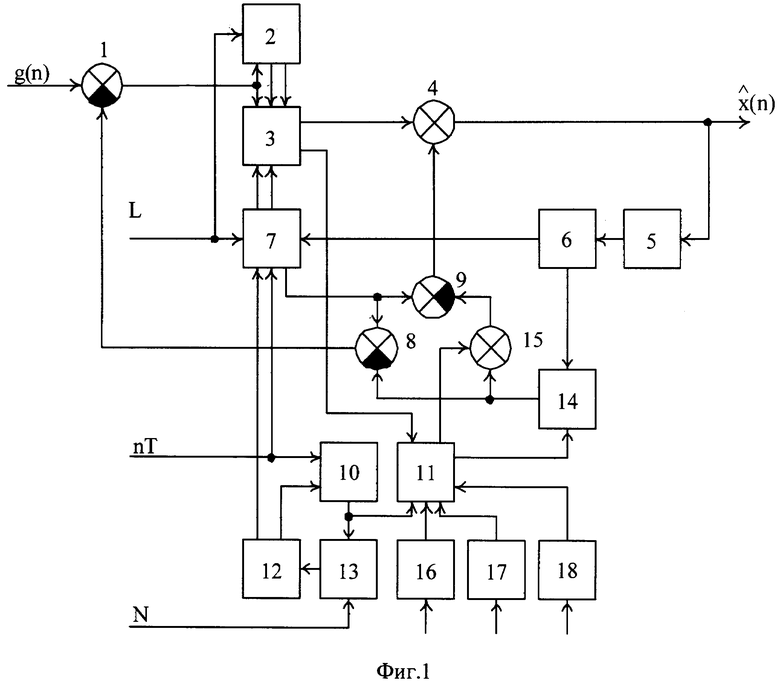

На фиг.7 приведены графики экспериментального исследования прототипа, а на фиг.8 - предлагаемой системы в режиме идентификации.

Переходной процесс, возникающий в первых тактах работы системы на фиг.7 и 8 не показан, так как для прототипа его характер приведен в [5]. В предлагаемой системе за счет изменения коэффициентов b1(n) удалось оптимизировать параметры переходного процесса. Величина ошибки оценки уменьшилась примерно на 5% при тех же исходных данных, что и в прототипе. При этом характер поведения ошибки оценки на временной оси не изменился.

Результаты моделирования представлены в табл.1.

Анализ результатов моделирования показал, что применение блоков 2, 7 и 12 позволяет повысить точность оценивания системы при изменении динамических параметров объекта наблюдения. При этом не возникает необходимости в изменении структуры системы, как это требуется, например, в [4]. Поэтому не существует предпосылок для возникновения ошибок, обусловленных инерционностью системы при изменении ее структуры.

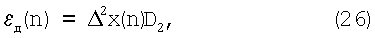

Уменьшению ошибок оценивания в предлагаемой системе при представлении полезного воздействия в виде (22) или (25) способствует самонастраивание весовых коэффициентов К(n) при изменении модели движения объекта. Так при поступлении на вход системы воздействия вида (25) к сигналу невязки  добавляется динамическая ошибка εд, обусловленная присутствием в полиноме (25) ускорения. Для оценки величины этой ошибки воспользуемся известным методом, например [11]. Для системы второго порядка астатизма

добавляется динамическая ошибка εд, обусловленная присутствием в полиноме (25) ускорения. Для оценки величины этой ошибки воспользуемся известным методом, например [11]. Для системы второго порядка астатизма

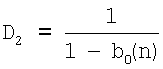

где D2 - коэффициент ошибки по ускорению, Δ2x(n) - разность второго порядка. Коэффициенты ошибки по ускорению определяется в виде

где  - передаточная функция по невязке

- передаточная функция по невязке  .

.

Вычисление D2 приводит к следующему результату:

, а с учетом (7)

, а с учетом (7)

Найдем вторую разность от задающего воздействия x(t)=at2/2, положив

t=nT.

Тогда

Поэтому динамическая ошибка будет определяться как

Присутствие динамической ошибки (28) в сигнале невязки  утяжеляет значение Рэ(n) в выражениях (10) и (13). Следовательно, величина К(n), определяемая в соответствии с (8), также возрастает, и система самонастраивается к изменению модели входного воздействия.

утяжеляет значение Рэ(n) в выражениях (10) и (13). Следовательно, величина К(n), определяемая в соответствии с (8), также возрастает, и система самонастраивается к изменению модели входного воздействия.

Источники информации

1. Авторское свидетельство №1084736 по классу G05B 17/00.

2. Кузьмин С.З. Основы теории цифровой обработки радиолокационной информации. М.: Сов. радио, 1974, с.383, 392.

3. Медич Дж. Статистически оптимальные линейные оценки и управление. М.: Энергия, 1973. с.208.

4. Авторское свидетельство №1356817 по классу G05B 17/00.

5. Авторское свидетельство №1727110 по классу G05B 17/00, G05F 1/00.

6. Зайцев Г.Ф., Пушкарев Ю.А. Возможности достижения инвариантности в дискретных системах оценивания с управлением наблюдения // Кибернетика и вычислительная техника. К.: ИК АН УССР, 1989, вып.83, с.90-96.

7. Гришин Ю.П., Казаринов Ю.М. Динамические системы, устойчивые к отказам. М.: Радио и связь, 1985, с.12-18.

8. Эйкхофф П. Основы идентификации систем управления. М.: Мир, 1975, с.554-555.

9. Рабинер Л., Гоулд Б. Теория и применение цифровой обработки сигналов. М.: Мир, 1978. С.699.

10. Бронштейн И.Н., Семендяев К.А. Справочник по математике для инженеров и учащихся втузов. - 13-е изд., исправленное. М.: Наука, Гл. ред. физ.-мат. лит., 1986, с.457.

11. Пушкарев Ю.А., Пятков В.В. Методика определения динамической точности в многомерных комбинированных дискретных системах управления // Электромеханика. Изв. вузов, 1988, №6, с.68-72.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретная система оценивания | 1989 |

|

SU1727110A1 |

| УСТРОЙСТВО ДЛЯ НАСТРОЙКИ КОРРЕКТОРА МЕЖСИМВОЛЬНОЙ ИНТЕРФЕРЕНЦИИ | 1991 |

|

RU2034404C1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТОР | 1987 |

|

SU1521242A1 |

| Устройство обнаружения и определения координат объекта на изображении | 1990 |

|

SU1737755A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ И ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2449350C1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2451328C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ И ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2470359C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2012 |

|

RU2517316C1 |

| СПОСОБ ПРИЕМА МНОГОЛУЧЕВОГО СИГНАЛА, СПОСОБ ПОИСКА И СПОСОБ ФОРМИРОВАНИЯ МЯГКИХ РЕШЕНИЙ ПРИ ПРИЕМЕ МНОГОЛУЧЕВОГО СИГНАЛА И УСТРОЙСТВА, ИХ РЕАЛИЗУЮЩИЕ | 2003 |

|

RU2251802C1 |

Изобретение относится к радиотехнике и автоматике, в частности может использоваться в радиолокации для высокоточного оценивания координатной информации. Технический результат - повышение точности оценивания системы при изменении динамических параметров объекта наблюдения. Достигается тем, что система оценивания содержит вычитатель (1), блок (2) идентификации, блок (3) коррекции, сумматор (4), блок (5) задержки, блок (6) экстраполяции, блок (7) управления, вычитатели (8 и 9), счетчик (10), двухканальный мультиплексор (11), блок (12) режимов работы, компаратор (13), умножитель (14), сумматор (15), элементы (16-18) памяти коэффициентов и сумматор (15), элементы (16-18) памяти коэффициентов, первый вход вычитателя (1) и выход сумматора (4) являются соответственно информационным входом и выходом дискретной системы оценивания, второй вход компаратора (13) соединен с шиной задания числа шагов, тактовый вход счетчика (10) является тактовым входом системы. 8 ил., 1 табл.

Дискретная система оценивания динамических параметров объектов наблюдения, содержащая последовательно соединенные первый вычитатель, блок коррекции, первый сумматор, блок задержки, блок экстраполяции, и включающая второй и третий вычитатели, второй сумматор, счетчик, компаратор, двухканальный мультиплексор, три элемента памяти коэффициентов и умножитель, первый вход которого соединен с первым выходом блока экстраполяции, второй вход с первым выходом двухканального мультиплексора, а выход с первыми входами второго сумматора и второго вычитателя, подключенного выходом ко второму входу первого вычитателя, второй выход двухканального мультиплексора соединен со вторым входом второго сумматора, подключенного выходом ко второму входу третьего вычитателя, выход которого соединен со вторым входом первого сумматора, выход счетчика подключен к первому входу компаратора и к адресному входу двухканального мультиплексора, вторая группа информационных входов которого соединена с входами элементов памяти коэффициентов, первый вход первого вычитателя и выход первого сумматора являются соответственно информационным входом и выходом системы, второй вход компаратора соединен с шиной задания числа шагов, обеспечивающей установку необходимого числа шагов оптимизации для улучшения качества переходного процесса системы, тактовый вход счетчика является тактовым входом системы, отличающаяся тем, что в нее введены блок идентификации, блок управления и блок режимов работы, причем блок идентификации обеспечивает вычисление (идентификацию) дисперсии ошибок экстраполяции и измерения по результатам измерений и содержит последовательно соединенные первый умножитель, первый блок вычисления математического ожидания, второй вычитатель, выход которого является вторым выходом блока идентификации, на нем формируется сигнал дисперсии ошибок экстраполяции, предназначенный для передачи в режиме идентификации на третий вход блока коррекции, первый вход второго вычитателя является одновременно первым выходом блока идентификации, на нем формируется суммарный сигнал дисперсий ошибок экстраполяции и измерения, предназначенный для передачи в режиме идентификации на второй вход блока коррекции, второй вход второго вычитателя соединен с выходом второго блока вычисления математического ожидания, первый вход которого подключен к выходу второго умножителя, а второй вход объединен со вторым входом первого блока вычисления математического ожидания и является вторым входом блока идентификации, на него подается код, сформированный шиной задания глубины памяти, обеспечивающей размер выборки для формирования «скользящей» суммы блоками вычисления математического ожидания, первый и второй входы первого умножителя, первый вход второго умножителя, первый вход первого вычитателя, вход блока задержки соединены вместе и образуют первый вход блока идентификации, на который поступает сигнал невязки с выхода первого вычитателя системы, выход блока задержки подключен ко второму входу первого вычитателя, выход которого соединен со вторым входом второго умножителя, блок управления предназначен для управления подачей экстраполированного сигнала в режиме идентификации и набора статистики, он содержит последовательно включенные счетчик, компаратор, триггер, блок инвертирования, второй блок логического умножения, блок логического сложения, а также первый блок логического умножения, выход которого соединен со вторым входом блока логического сложения, выход которого является первым выходом блока управления, через него подается экстраполированный сигнал на второй и первый входы соответственно второго и третьего вычитателей системы, вторые входы первого и второго блоков логического умножения соединены вместе и являются первым входом блока управления, на который подается экстраполированный сигнал, сформированный на втором выходе блока экстраполяции, второй вход триггера является вторым входом блока управления, на него приходит установочный импульс со второго выхода блока режимов работы, вход компаратора является четвертым входом блока управления, на него подается код, сформированный шиной задания глубины памяти, первый вход счетчика является третьим входом блока управления, на него подается последовательность импульсов с тактового входа системы оценивания, второй вход счетчика, выход триггера, первый вход первого блока логического умножения соединены вместе и образуют второй выход блока управления, на нем формируется сигнал логического нуля или логической единицы, подаваемый на четвертый вход блока коррекции, выходные сигналы счетчика через третий выход блока управления поступают на пятый вход блока коррекции, предназначенный для коррекции значений экстраполированного сигнала в режимах идентификации и набора статистики, он содержит последовательно соединенные блок памяти, мультиплексор, второй блок логического умножения, блок логического сложения, первый умножитель, выход которого является первым выходом блока коррекции, формирующим корректировочное значение в сигнале оценки в режиме идентификации, первый вход первого умножителя соединен с входом блока задержки и является первым входом блока коррекции, на который подается сигнал невязки, выход блока задержки подключен к первому входу второго умножителя, второй вход которого соединен с выходом вычитателя, а выход является вторым выходом блока коррекции, обеспечивающим формирование корректировочного значения в сигнал оценки в режиме набора статистики, и подключен к первой группе информационных входов двухканального мультиплексора системы, первый вход вычитателя соединен с выходом блока логического сложения и вторым входом первого умножителя, а второй вход - с выходом элемента памяти, блок деления подключен выходом к первому входу первого блока логического умножения, второй вход которого соединен со входом блока инвертирования и является четвертым входом блока коррекции, соединенным со вторым выходом блока управления системы, выход первого блока логического умножения подключен ко второму входу блока логического сложения, выход блока инвертирования соединен со вторым входом второго блока логического умножения, первый и второй входы блока деления являются вторым и третьим входами блока коррекции и подключены соответственно к первому и второму выходам блока идентификации системы, адресный вход мультиплексора является пятым входом блока коррекции, он соединен с третьим выходом блока управления системы, блок режимов работы обеспечивает функционирование системы в режиме набора статистики, он содержит последовательно соединенные формирователь установочных импульсов при включении устройства и триггер, первым выходом блока режимов работы является выход триггера, подключенный к установочному входу счетчика и обеспечивающий его сброс при завершении счета шагов оптимизации, а вторым выходом - выход формирователя, подключенный ко второму входу блока управления системы, входом блока режима работы является вход компаратора, вырабатывающий сигнал при окончании счета шагов оптимизации и устанавливающий первый выход блока режимов работы в нулевое состояние.

| Дискретная система оценивания | 1989 |

|

SU1727110A1 |

| RU 2000117427 A, 10.07.2002 | |||

| Адаптивное устройство для идентификации линейных объектов | 1981 |

|

SU957168A1 |

| RU 94030327 A1, 10.06.1996 | |||

| УСТРОЙСТВО АДАПТАЦИИ РЕГУЛЯТОРА | 2005 |

|

RU2285943C1 |

| JP 8021740 A, 23.01.1996 | |||

| WO 9732270 A1, 04.09.1997. | |||

Авторы

Даты

2010-08-27—Публикация

2007-06-13—Подача