Изобретение относится к измерительной технике и технике релейной защиты и предназначено для измерения частоты и предотвращения ее аварийного снижения в энергосистемах.

Известное устройство для измерения частоты гармонических сигналов [А.с. N 1626177, G 01 R 23/00, 1991, БИ N 5] содержащее аналого-цифровой преобразователь, блок регистров сдвига, сумматор, делитель, цифроаналоговый преобразователь, генератор импульсов измеряет частоту, но обладает низкой надежностью и ограниченными функциональными возможностями.

Известное устройство для измерения частоты гармонических сигналов [А.с. N 1705755, G 01 R 23/00, 1992, БИ N 15] содержащее аналого-цифровой преобразователь, регистры сдвига, генератор импульсов, блоки умножения, сумматоры, блок деления, блок преобразования функциональный измеряет частоту, но имеет низкую надежность, т.к при отсутствии диагностики выход из строя любого из узлов приведет к нарушению процесса измерения и к формированию ошибочных результатов.

Устройство обладает также ограниченными функциональными возможностями, т.к. только измеряет и только одну частоту сигнала.

Наиболее близким техническим решением является устройство для определения частоты гармонического сигнала [А.с. N 1691765, G 01 R 23/00, 1991, БИ N 42] содержащее блок выбора максимального значения, масштабный усилитель, блок сравнения двух чисел, блок запрета, три блока определения абсолютной величины и образования новых функциональных связей, аналого-цифровой преобразователь, три регистра памяти, сумматор, делитель, цифроаналоговый преобразователь, функциональный преобразователь, генератор импульсов и два блока задержки.

Прототип также обладает низкой надежностью за счет отсутствия диагностики входящих узлов и ограниченными функциональными возможностями, определяющимися только измерением частоты гармонического сигнала.

Цель изобретения - повышение надежности устройства за счет ведения диагностики входящих узлов и расширение функциональных возможностей за счет введения измерения скорости изменения частоты и действующего напряжения, а также введения функций автоматической частотной разгрузки, автоматического ограничения повышения частоты, автоматического повторного включения по частоте с возможностью контроля напряжения, а также введение многих других функций.

Поставленная цель достигается тем, что в известное устройство, содержащее аналого-цифровой преобразователь, масштабный усилитель, блок сравнения, блок запрета и два регистра памяти, причем выходы первого регистра соединены со входами второго регистра памяти, а выход масштабного усилителя соединен с первым входом блока сравнения, введены микропроцессор, блок ввода-вывода и микропроцессорная система, причем выход масштабного усилителя соединен с первым входом аналого-цифрового преобразователя, первый и второй выходы которого соединены соответственно с первым и вторым входом микропроцессора, первый выход которого соединен со вторым входом аналого-цифрового преобразователя, первый и второй выход блока сравнения соединены соответственно с третьим и четвертым входом микропроцессора, второй выход которого соединен со входом блока запрета, выход которого соединен со вторым входом блока сравнения, первая группа входов-выходов микропроцессора соединена с группой входов первого регистра памяти и группой выходов второго регистра, вторая группа входов которого соединена с первой группой выходов микропроцессора, вторая группа входов-выходов которого соединена с первой группой входов-выходов микропроцессорной системы, вторая и третья группа входов-выходов которой является соответственно группой входов-выходов для связи с АСУ и ПЭВМ, четвертая группа входов-выходов микропроцессорной системы соединена с группой входов-выходов блока ввода-вывода, первая группа выходов которого соединена с группой входов микропроцессора, вторая группа выходов блока ввода-вывода является группой релейных выходов устройства, группа входов которого является группой входов блока ввода-вывода.

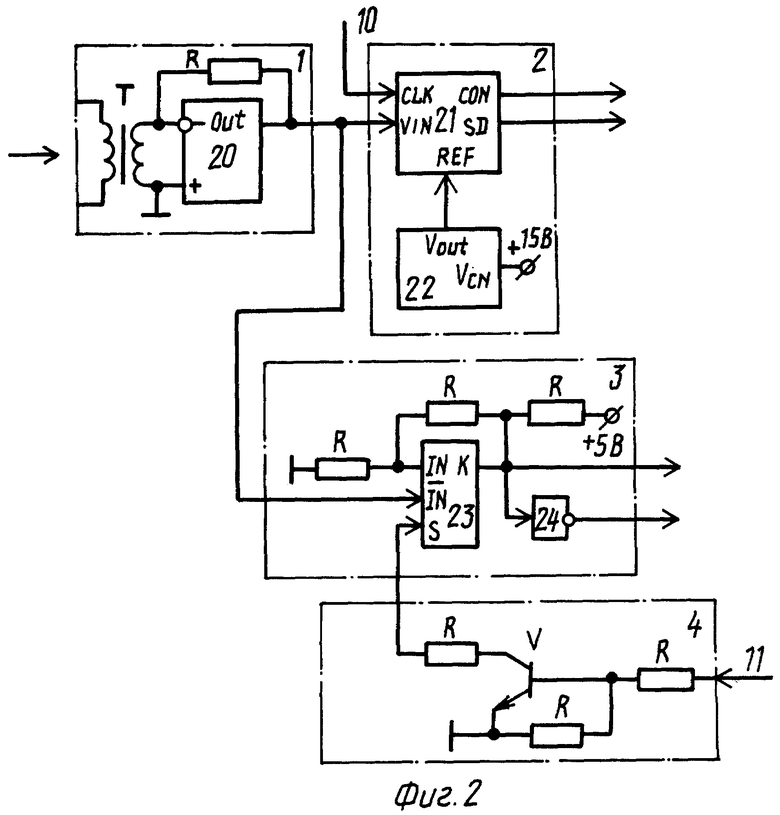

На фиг. 1 приведена структурная схема устройства;

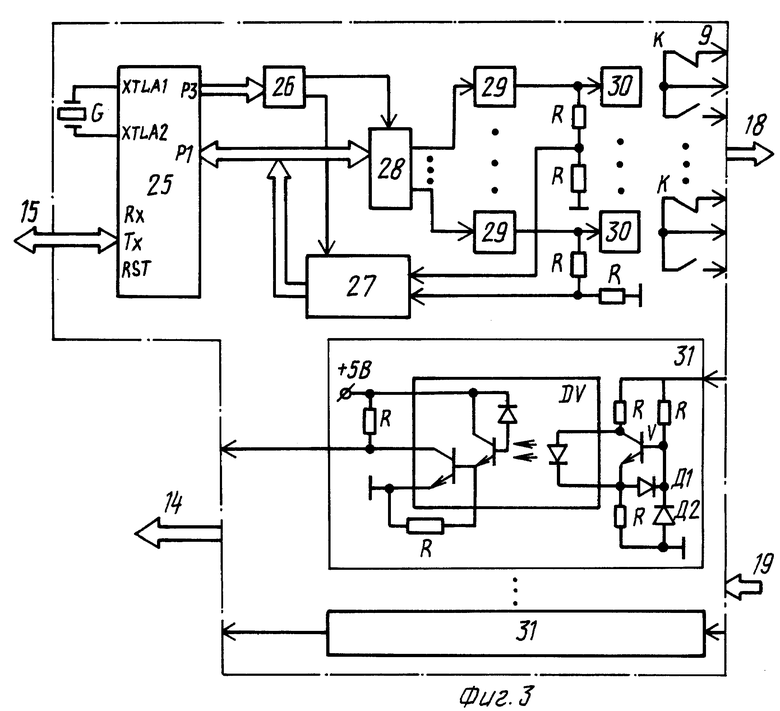

на фиг. 2 - пример реализации и соединений масштабного усилителя, аналого-цифрового преобразователя, блока сравнения и блока запрета;

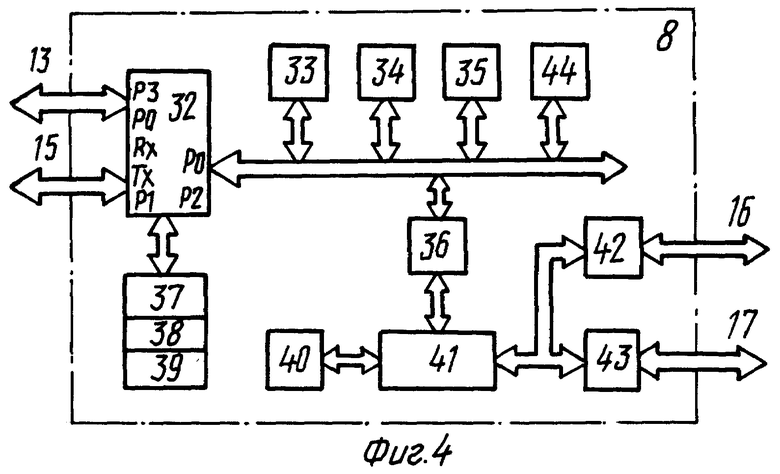

на фиг. 3 - пример реализации блока ввода-вывода;

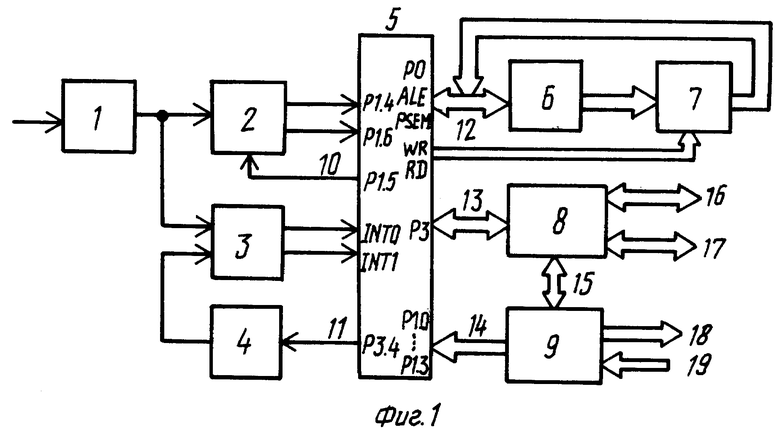

на фиг. 4 - пример реализации микропроцессорной системы.

На фиг. 1 обозначены:

1 - масштабный усилитель;

2 - аналого-цифровой преобразователь;

3 - блок сравнения (компаратор);

4 - блок запрета;

5 - микропроцессор (например AT 89C52-24PI с портами P0, P1, P3 и управляющими входами (выходами) ALE, PSEN, WR, RD, INT0, INT1 - не показан кварцевый резонатор и цепь сброса RST);

6 - первый регистр памяти (например, ИР 22);

7 - второй регистр памяти (например, AT28C256);

8 - микропроцессорная система;

9 - блок ввода-вывода;

10 - цепь сигнала управления CLK;

11 - цепь сигнала запрета;

12 - шина адрес/данные, управление;

13 - шина обмена микропроцессора с микропроцессорной системой;

14 - информационная шина состояния дискретных входов;

15 - шина обмена блока ввода-вывода с микропроцессорной системой;

16 - шина связи с АСУ;

17 - шина связи с ПЭВМ;

18 - группа выходных цепей управления и сигнализации;

19 - группа входных цепей дискретных сигналов от объекта.

На фиг. 2 обозначены:

Т - трансформатор согласующий;

20 - операционный усилитель, например OP177GP фирмы "Analog Device " или аналогичный;

21 - аналого-цифровой преобразователь, например AD7893AN-10 фирмы "Analog Device" или аналогичный;

22 - источник опорного напряжения, например AD680N фирмы "Analog Device" или аналогичный;

23 - компаратор, например K554CA3A или аналогичный;

24 - инвертор, например ЭКР 1554 ЛАЗ или аналогичный;

R - резисторы, например С2-33 или аналогичные;

V - транзистор, например КТ 3102 или аналогичный.

На фиг. 3 обозначены:

25 - микропроцессор, например AT89C2051 или аналогичный;

G - резонатор кварцевый, например РК 386 ММ или аналогичный;

26 - дешифратор, например SN74HC 138 или аналогичный;

27 - набор шинных формирователей, например SN74HC240 или аналогичные;

28 - регистр, например КР1554 ИР23 или SN 74 HC 374 или аналогичный;

29 - ключи (усилители Дарлингтона), например MCT 1413 BP или аналогичные;

30 - реле с контактами K, например G2RK-2-24VDC фирмы "Omron" или аналогичные;

R - резисторы, например C2-33 или набор резисторов HP 1-4-9 или аналогичные;

31 - узел согласования;

V - транзистор, например BC 547 или аналогичный;

Д1 - диод, например 2Д510А или аналогичный;

Д2 - стабилитрон, например B255C39 или аналогичный;

DV - оптрон, например H608-2 или аналогичный.

На фиг. 4 обозначены:

32 - центральный процессор, например AT89C52-24PI или аналогичный (не показан резонатор и некоторые цепи управления);

33 - ПЗУ, например AT28C256 или аналогичное;

34 - ЭППЗУ, например AT29C010A-12PI или аналогичное;

35 - ОЗУ, например SRM2A256LLCT или аналогичное;

36 - регистры обмена, например KP1554 ИР 23 или аналогичные;

37 - CPU, например AT mega 603-6A1 или аналогичный;

38, 39 - дисплей и клавиатура с индикаторами;

40 - ОЗУ, например SRM2A256 LLCT 85 или аналогичное;

41 - микропроцессор, например AT89C5224PI или аналогичный (показан без резонатора и цепей управления);

42, 43 - драйверы для связи с АСУ и ПЭВМ;

44 - часы реального времени, например RTC 72423 В фирмы "EPSON" или аналогичные.

Микропроцессорная система 8 может быть также реализована в соответствии с [Н.Н.Чернобровов, В.А.Семенов. Релейная защита энергетических систем, 1998 г. , с. 778. рис.22.4]. Подробная информация о работе микропроцессорной системы приведена там же на с. 778-783.

Микропроцессорное многофункциональное устройство реле частоты содержит масштабный усилитель 1, аналого-цифровой преобразователь 2, блок сравнения 3, блок запрета 4, микропроцессор 5, первый 6 и второй 7 регистры памяти, микропроцессорную систему 8 и блок ввода-вывода 9, причем выходы первого регистра памяти 6 соединены со входами второго регистра 7 памяти, выход масштабного усилителя 1 соединен с первым входом блока сравнения 3 и со входом аналого-цифрового преобразователя 2, первый и второй выход которого соединены соответственно с первым P1.4 и вторым P1.6 входом микропроцессора 5, первый выход P1.5 которого соединен со вторым входом 10 аналого-цифрового преобразователя 2, первый и второй выход блока сравнения 3 соединены соответственно с третьим INT0 и четвертым INT1 входом микропроцессора 5, второй выход P3.4 которого соединен со входом 11 блока запрета 4, выход которого соединен со вторым входом блока сравнения 4, первая группа входов-выходов 12 микропроцессора 5 соединена с группой входов первого регистра 6 и группой выходов второго регистра 7, вторая группа входов которого соединена с первой группой выходов "WR, RD" микропроцессора 5, вторая группа входов-выходов P3 которого соединена с первой группой входов-выходов 13 микропроцессорной системы 8, вторая 16 и третья 17 группа входов-выходов которой является соответственно группой входов-выходов для связи с АСУ и ПЭВМ, четвертая группа входов-выходов 15 микропроцессорной системы 8 соединена с группой входов-выходов блока ввода-вывода 9, первая группа выходов 14 которого соединена с группой входов P1.0...P1.3 микропроцессора 5, вторая группа выходов 18 блока ввода-вывода 9 является группой релейных выходов устройства, группа входов 19 которого является группой входов блока ввода-вывода 9.

Устройство измеряет следующие параметры:

- частоту F;

- скорость изменения частоты S;

- действующее значение напряжения U.

Частота сигнала измеряется по сумме длительностей полупериодов напряжения:

где T1 - длительность нечетного полупериода;

T2 - длительность четного полупериода.

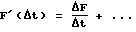

Скорость изменения частоты вычисляется как первая производная частоты сигнала по времени.

где dF - приращение частоты за время dt;

dt - малый интервал времени.

Для оценки первой производной частоты применяется метод численного дифференцирования данных:

Для оценивания частоты периодического сигнала применяется временной метод измерения.

Аппаратно измерение длительности полупериодов реализовано следующим образом:

контролируемый сигнал поступает через трансформатор T, обеспечивающий гармоническую развязку на операционный усилитель 20, с помощью которого осуществляется масштабное преобразование контролируемого аналогового сигнала к диапазону входных сигналов аналого-цифрового преобразователя (АЦП), цифровой код с АЦП поступает в микропроцессор 5, а также на него поступают сигналы от блока сравнения (компаратора) в виде последовательности прямоугольных импульсов с частотой контролируемого аналогового сигнала и информация о состоянии дискретных входов с блока ввода-вывода 9 т.е. из исходного сигнала формируется бинарный сигнал " меандр" который переключает между собой два канала измерения временных интервалов (INT0 и INT1 - два таймера микропроцессора). Таким образом один таймер измеряет длительность четного полупериода, а другой - нечетного. Каждый переход контролируемого напряжения через ноль активирует включение одного из таймеров, остановку счета второго таймера и считывание его значения. Такая реализация позволяет правильно обрабатывать возможные колебания управляющего сигнала "меандр" типа 0-1-0 в зоне перехода через ноль контролируемого напряжения. В каждый момент времени в памяти микропроцессора хранится N оценок длительности полупериодов в отсчетах таймера (один отсчет таймера при Fosc = 24 МГц равен 0,5 мкс), Fosc - частота резонатора

Ti = Kt•ti, i=1...N,

где Ti - текущая оценка длительности полупериода тактов.

KT -длительность квантования по времени (при Fosc = 24 МГц, KT = 2 МГц).

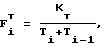

Текущая оценка частоты сигнала вычисляется один раз за период по формуле:

где Fi T - текущая оценка частоты;

Ti - длительность текущего полупериода;

Ti-1 - длительность предыдущего полупериода.

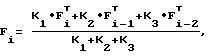

Для уменьшения воздействия шумов и случайных процессов первичная информация о частоте сглаживается с учетом весовых коэффициентов

где Fi - сглаженная оценка частоты;

K1, K2, K3 - весовые коэффициенты.

Выбор весовых коэффициентов осуществляется на этапе разработки по результатам моделирования и макетных испытаний.

Измерение скорости изменения частоты

Исходной информацией для измерения скорости изменения частоты являются массивы N сглаженных оценок частоты и длительностей полупериодов.

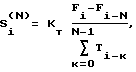

Оценка скорости вычисляется один раз за полупериод согласно формуле:

где Si (N) - текущая оценка скорости изменения частоты на основе;

N - отсчетов частоты;

Fi - текущая оценка скорости изменения частоты;

Fi-N - оценка скорости изменения частоты за N-й прошлый период;

Ti-k - оценка длительности N полупериодов.

Измерение действующего значения напряжения

Действующее значение переменного напряжения - величина, равная напряжению постоянного тока, при протекании которого через равную нагрузку, выделяется та же мощность, что и переменного.

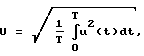

Действующее напряжение определяется по формуле:

где u(t) - зависимость сигнала от времени;

T - период сигнала;

U - действующее напряжение.

Для сокращения объема вычислений измеряется средневыпрямленное значение напряжения по формуле:

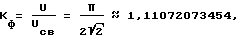

и преобразуется в действующее значение. Отношение действующего значения к средневыпрямленому (коэффициент формы) для синусоидального сигнала следующее:

где Kф - коэффициент формы.

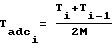

Для измерения напряжения используется АЦП с регулируемой частотой дискретизации. Частота дискретизации АЦП подстраивается один раз за полупериод по результатам измерения длительности таким образом, что за один период производится 2M отсчетов АЦП ,

,

где  - период дискретизации АЦП на следующий полупериод. Взятие отсчетов начинается через время сдвига после перехода контролируемого напряжения через ноль.

- период дискретизации АЦП на следующий полупериод. Взятие отсчетов начинается через время сдвига после перехода контролируемого напряжения через ноль.

tx = x•  ,

,

где tx - время сдвига, с;

x - величина сдвига в частях периода дискретизации АЦП.

Величина x определяется на этапе отладки и макетных испытаний (при моделировании x = 0,205). В каждый момент времени хранится в памяти 2M отсчетов АЦП (M - за предыдущий и M - за текущий полупериод) , m = 1...2M.

, m = 1...2M.

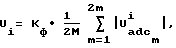

По окончании каждого полупериода производится вычисление средневыпрямленного значения напряжения по скользящему интервалу (учитываются данные запредыдущий и текущий полупериод), равному длительности текущей оценки периода согласно

где Ui - текущая оценка действующего значения напряжения;

Kф - коэффициент формы;

M - количество отсчетов АЦП за период.

Результаты измерений передаются по последовательному каналу в центральный процессор микропроцессорной системы. Сюда же из микропроцессора 5 поступает информация о состоянии дискретных входов, клавиш с клавиатуры 39, а также команды, поступающие по последовательным каналам через драйверы 42 и 43 из АСУ или ПЭВМ.

Центральный процессор производит логическую обработку поступающей информации (сравнение измеренных параметров контролируемого аналогового сигнала с уставками, отсчет выдержек времени и т.д.) и формирует команды управления и сигнализации, которые передаются на выходные реле 30, установленные в блоке ввода-вывода.

Кроме того, центральный процессор 32 микропроцессорной системы 8 обеспечивает управление индикаторами, установленными на пульте с клавиатурой 39 и готовит информацию для отображения на дисплее 38. Управление дисплеем производится микропроцессором дисплея 37.

Таким образом, устройство, кроме измерения с высокой точностью и в соответствии с алгоритмами частоты, измеряет скорость измерения частоты и действующее значение контролируемого напряжения.

Далее устройство, в части расширения функциональных возможностей, обеспечивает:

- автоматическую частотную разгрузку без выдержки времени с возможностью блокировки по скорости снижения частоты, т.е. производит отключение нагрузки после снижения частоты сети ниже предела значения уставки срабатывания по частоте и не производит отключение нагрузки, если снижение напряжения происходило со скоростью выше значения уставки по скорости снижения частоты напряжения;

- автоматическую частотную разгрузку АЧР с выдержкой времени с возможностью контроля снижения напряжения и блокировки срабатывания при коротких замыканиях, т.е. производит отключение нагрузки, если при сохранении частоты ниже частоты возврата в течение определенного времени, контролируемое напряжение остается ниже уставки в течение определенного времени. Если контролируемое напряжение вышло за определенные пределы, микропроцессор 5 формирует управляющий сигнал на блок запрета 4, который блокирует блок сравнения и на дисплей поступает определенная информация о выходе сигнала за установленные пределы;

- автоматическое ограничение повышения частоты АОПЧ с выдержкой по времени, с возможностью ускорения скорости изменения частоты, с возможностью выдачи команд отключения и регулировки;

- автоматическое повторное включение по частоте ЧАПВ с возможностью контроля напряжения, а также

- задание внутренней конфигурации (ввод и вывод любых алгоритмов АЧР, АОПЧ и ЧАПВ для управления любым реле 30) программным способом;

- местный и дистанционный ввод, хранение и отображение любого пакета уставок;

- отображение текущих электрических параметров сети;

- фиксацию, хранение и отображение аварийных электрических параметров сети для последних аварийных событий с автоматическим обновлением информации;

- двусторонний обмен информацией с АСУ и ПЭВМ по стандартным последовательным каналам связи;

- осциллографирование параметров частотной аварии.

Каналы связи устройства обеспечивают:

- дистанционное управление защищаемым объектом;

- передачу информации о входных и выходных дискретных сигналах;

- дистанционное измерение;

- передачу информации о параметрах аварийных событий;

- передачу осцилограмм.

Для повышения надежности в устройстве имеется система самодиагностики, которая состоит из двух подсистем - фоновой самодиагностики, которая обеспечивает контроль работоспособности основных узлов устройства в течение всего срока эксплуатации, и набора тестов, запускаемых по вызову.

Фоновая самодиагностика выполняется непрерывно в течение всего времени работы устройства, обеспечивая контроль работоспособности всех основных узлов. Результаты самодиагностики анализируются центральным процессором. В состав диагностики входят

- проверка аналоговых и дискретных входов и выходов;

- тестирование дисплея (программные известные методы);

- тестирование клавиатуры (программные известные методы);

- тестирование каналов и т.д.

Например, при диагностике выходов сигнал снимается с делителей R-R на выходах ключей 29 блока ввода-вывода 9 и поступает через шинные формирователи 27 в микропроцессор 25 (при обрыве цепи или неисправности ключа уровень сигнала на делителе будет отличаться от уровня имеющегося в исправном узле.)

Проверка каналов RS-232 и RS-485 производится контролем равенства переданной и принятой информации (путем установки заглушки и без нее).

Таким образом, введение самодиагностики и тестирования позволяет повысить надежность устройства путем контроля работоспособности, как в процессе работы, так и используя стендовое оборудование.

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРОПРОЦЕССОРНОЕ УСТРОЙСТВО АВТОМАТИЧЕСКОЙ ЧАСТОТНОЙ РАЗГРУЗКИ | 2002 |

|

RU2230414C2 |

| МИКРОПРОЦЕССОРНОЕ РЕЛЕЙНОЕ УСТРОЙСТВО ИМПУЛЬСНОЙ СИГНАЛИЗАЦИИ | 2000 |

|

RU2195707C2 |

| МИКРОПРОЦЕССОРНОЕ УСТРОЙСТВО РЕЛЕЙНОЙ ЗАЩИТЫ И АВТОМАТИКИ С ДИСТАНЦИОННЫМ УПРАВЛЕНИЕМ | 2002 |

|

RU2222083C2 |

| МИКРОПРОЦЕССОРНАЯ СИСТЕМА ЗАЩИТЫ | 2000 |

|

RU2173924C1 |

| МНОГОПРОЦЕССОРНАЯ ИНФОРМАЦИОННО-УПРАВЛЯЮЩАЯ СИСТЕМА РЕЛЕЙНОЙ ЗАЩИТЫ И АВТОМАТИКИ | 2001 |

|

RU2210104C2 |

| УСТРОЙСТВО ПРОТИВОАВАРИЙНОЙ АВТОМАТИКИ | 2001 |

|

RU2221318C2 |

| ИСТОЧНИК ПИТАНИЯ КОМБИНИРОВАННЫЙ | 2001 |

|

RU2216844C2 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Устройство для контроля работы транспортных средств | 1982 |

|

SU1045240A1 |

| УСТРОЙСТВО ДЛЯ ЭЛЕКТРИЧЕСКОГО ВЗАИМОДЕЙСТВИЯ С БИОЛОГИЧЕСКИ АКТИВНЫМИ ТОЧКАМИ | 2003 |

|

RU2266099C2 |

Микропроцессорное многофункциональное устройство реле частоты относится к измерительной технике и предназначено для установки в релейных отсеках, на панелях и в шкафах в релейных залах и пультах управления электростанций, микропроцессорных станций и других объектах. Технический результат - повышение надежности устройства за счет введения диагностики и тестирования основных входящих узлов и расширение функциональных возможностей за счет введения измерения скорости изменения частоты и действующего напряжения, а также введения функций автоматической разгрузки, автоматического ограничения повышения частоты, автоматического повторного включения по частоте с возможностью контроля напряжения и многих других функций. Устройство содержит масштабный усилитель, аналого-цифровой преобразователь, блок сравнения, блок запрета, микропроцессор, два регистра памяти, микропроцессорную систему и блок ввода-вывода. Предложенное устройство предназначено для измерения параметров электрической сети и для организации частотной разгрузки различных энергосистем в условиях аварийного дефицита активной мощности. 4 ил.

Микропроцессорное многофункциональное устройство реле частоты, содержащее аналого-цифровой преобразователь, масштабный усилитель, блок сравнения, блок запрета и два регистра памяти, причем группа выходов первого регистра памяти соединена с первой группой входов второго регистра памяти, а выход масштабного усилителя соединен с первым входом блока сравнения, отличающееся тем, что в него введены микропроцессор, блок ввода-вывода и микропроцессорная система, причем выход масштабного усилителя соединен с первым входом аналого-цифрового преобразователя, первый и второй выходы которого соединены соответственно с первым и вторым входами микропроцессора для передачи цифрового кода, соответствующего напряжению контролируемого сигнала, первый выход микропроцессора соединен со вторым входом аналого-цифрового преобразователя, первый и второй выходы блока сравнения соединены соответственно с третьим и четвертым входами микропроцессора для передачи сигналов в виде последовательности прямоугольных импульсов с частотой контролируемого сигнала, которые переключают два канала измерения длительности интервалов для четного и нечетного полупериодов соответственно, второй выход микропроцессора соединен со входом блока запрета, выход которого соединен со вторым входом блока сравнения, первая группа входов-выходов микропроцессора соединена с группой входов первого регистра памяти и группой выходов второго регистра памяти, вторая группа входов которого соединена с первой группой выходов микропроцессора, вторая группа входов-выходов которого соединена с первой группой входов-выходов микропроцессорной системы, вторая и третья группы входов-выходов которой являются соответственно группами входов-выходов для связи с АСУ и ПЭВМ, четвертая группа входов-выходов микропроцессорной системы соединена с группой входов-выходов блока ввода-вывода, первая группа выходов которого соединена с группой входов микропроцессора, в котором осуществляется оценка частоты контролируемого сигнала, скорости изменения его частоты и действующего значения его напряжения, полученные результаты оценок поступают в микропроцессорную систему, производящую их логическую обработку и формирующую команды управления и сигнализации, которые передаются на выходные реле, установленные в блоке ввода-вывода, вторая группа выходов которого является группой релейных выходов устройства, группа входов блока ввода-вывода является группой входов устройства.

| Адаптивный измеритель параметров сигнала | 1987 |

|

SU1465802A2 |

| SU 1485144 A, 07.06.1989 US 4912419 A, 27.03.1990 | |||

| ФИЛЬТРУЮЩАЯ КОНСТРУКЦИЯ, В ЧАСТНОСТИ ФИЛЬТР-УЛАВЛИВАТЕЛЬ ЧАСТИЦ ДЛЯ ОЧИСТКИ ВЫХЛОПНЫХ ГАЗОВ ДВИГАТЕЛЯ ВНУТРЕННЕГО СГОРАНИЯ И СОЕДИНЕННЫЙ С НИМ ВЫПУСКНОЙ КОЛЛЕКТОР | 2005 |

|

RU2386042C2 |

Авторы

Даты

2001-07-27—Публикация

2000-05-17—Подача