Изобретение относится к технике релейной защиты и противоаварийной автоматики и предназначено для предотвращения аварийного снижения частоты в энергосистеме и ее восстановления до заданного уровня путем автоматического отключения части потребителей при возникновении дефицита активной мощности (автоматическая частотная разгрузка) и для автоматического включения отключенных потребителей после ликвидации аварийного дефицита мощности.

Известная система дистанционного управления выключателями [A.C. US Н 02 Н 3/30, Н 02 J 13/00, №4965694, Б.И. №4, 1990г.], содержащая отдельные линии управления, выключатели, элементы И, процессор, коммутатор, позволяет управлять выключателями посредством пусковых сигналов, но обладает ограниченными функциональными возможностями в части частотной разгрузки и большими габаритами.

Известное устройство для блокировки включения секционного выключателя [А.С. Н 02 H 11/00, №1702480, Б.И. №48, 1991 г.], содержащее два трансформатора, управляемый ключ, диод, сглаживающий контур, реагирующий орган и реле, позволяет управлять выключателями по необходимости, имеет небольшие габариты, но обладает ограниченными функциональными возможностями в части частотной разгрузки.

Наиболее близким техническим решением является микропроцессорное многофункциональное устройство реле частоты [Патент RU G 01 R 23/00, H 02 Н 3/46, №2171475, Бюл.№21, 27.07.01], содержащее аналого-цифровой преобразователь, масштабный усилитель, блок сравнения, два регистра памяти, микропроцессор, блок ввода-вывода и микропроцессорную систему, позволяет организовать частотную разгрузку различных энергосистем в условиях аварийного дефицита активной мощности.

Прототип также имеет относительно большие габариты, достаточно сложную схему устройства и непростое взаимодействием с ним обслуживающего персонала при эксплуатации.

Цель изобретения - упрощение схемы устройства, снижение его габаритных размеров и упрощение эксплуатации при сохранении основных функций.

Поставленная цель достигается тем, что в известное устройство, содержащее блок сравнения, блок запрета, два регистра памяти, микропроцессор и блок ввода-вывода, причем выходы первого регистра соединены со входами второго регистра, выход блока сравнения соединен со вторым входом микропроцессора, выход которого соединен со входом блока запрета, группа входов-выходов микропроцессора соединена с группой входов первого регистра и группой выходов второго регистра, вторая группа входов которого соединена с первой группой выходов микропроцессора, первая группа выходов блока ввода-вывода соединена с группой входов микропроцессора, вторая группа выходов блока ввода-вывода является группой релейных выходов устройства, группа входов которого является первой группой входов блока ввода-вывода, введены счетчик и таймер, причем вход счетчика соединен с выходом из группы входов-выходов микропроцессора, вторая группа выходов которого соединена со второй группой входов блока ввода-вывода, группа входов-выходов которого соединена с группой входов-выходов микропроцессора и с группой выходов таймера, первый вход которого соединен с выходом счетчика, второй вход таймера соединен с выходом блока сравнения, первый и второй входы которого являются входами устройства, первый вход микропроцессора соединен с выходом таймера, третий вход которого соединен с выходом блока ввода-вывода, третья группа входов которого соединена с третьей группой выходов микропроцессора, первая и вторая группа входов таймера соединены, соответственно, с группой выходов первого регистра и с первой группой выходов микропроцессора.

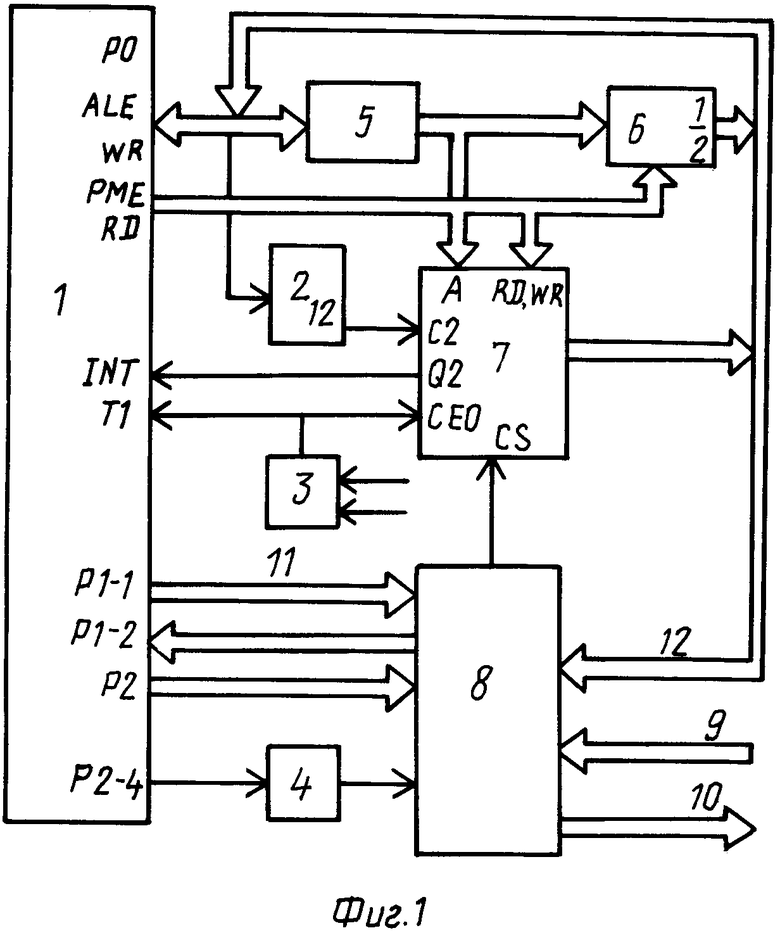

На фиг.1 приведена структурная схема устройства.

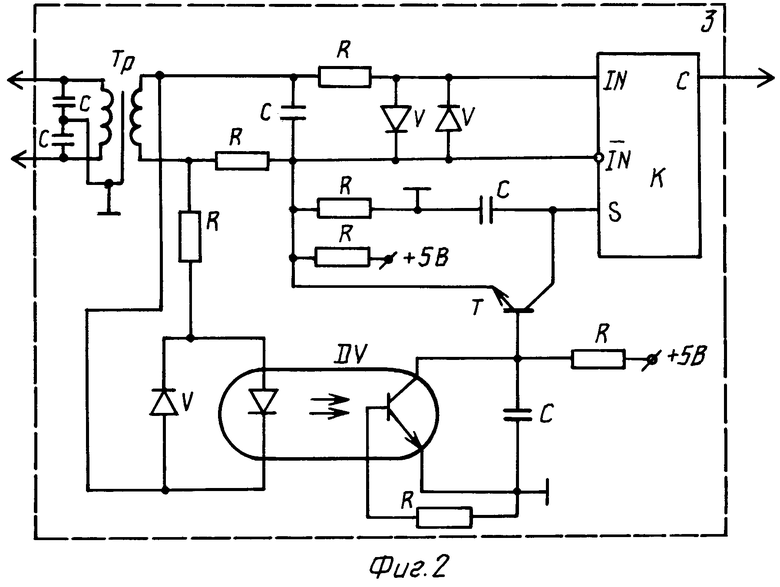

На фиг.2 - пример реализации блока сравнения.

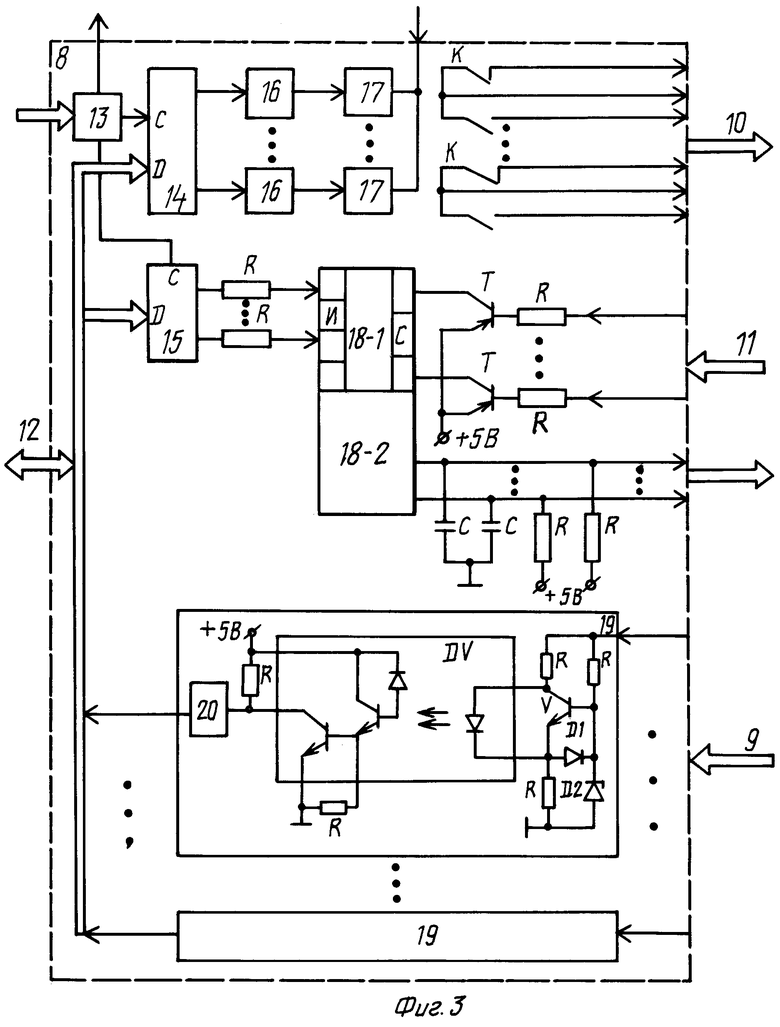

На фиг.3 - пример реализации блока ввода-вывода.

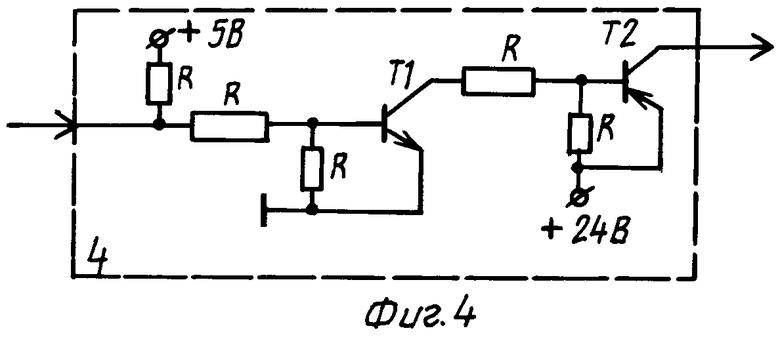

На фиг.4 - пример реализации блока запрета.

На фиг.1 обозначены:

1 - микропроцессор, например AT 89C52-24PI или аналогичный с портами Р0, P1, P2 и управляющими входами (выходами) ALE, РМЕ, WR, RD, INT, T1 (не показан кварцевый резонатор и цепь сброса RST);

2 - счетчик, например К561ИЕ16 или аналогичный;

3 - блок сравнения;

4 - блок запрета;

5 - первый регистр памяти, например КР1554ИР22 или аналогичный;

6 - второй регистр памяти;

6-1 - например КР537РУ13 или аналогичный;

6-2 - например КМ573РФ4 или аналогичный;

7 - таймер, например К580ВИ53 или аналогичный;

8 - блок ввода-вывода;

9 - группа входных цепей дискретных сигналов от объекта;

10 - группа выходных цепей управления и сигнализации;

11 - группа входных цепей сигналов от порта Р1 микропроцессора;

12 - магистраль микропроцессора (адрес/ данные, сигналы синхронизации).

На фиг.2 обозначены:

К - компаратор, например К554САЗА или аналогичный;

R - резисторы, например С2-33 или аналогичные;

V - диоды, например КД521А или аналогичные;

С - конденсаторы, например К10-17 или аналогичные;

Т - транзистор, например КТ315А или аналогичный;

DV - оптопара транзисторная, например SFN608-2 фирмы "SIEMENS" или аналогичная;

Тр - трансформатор.

На фиг.3 обозначены:

13 - дешифратор, например КР1554НД14 или аналогичный;

14 - регистр, например КР1554ИР23 или SN74HC374 или аналогичный;

15 - регистр, например КР1554ИР41 или аналогичный;

16 - ключи (усилители), например К1109ХТ22 или аналогичные;

17 - реле с контактами К, например RM83-1021-35-1024 фирмы "Relpol" или аналогичные;

R - резисторы, например С2-33 или аналогичные;

Т - транзистор, например КТ814Б или аналогичный;

18 - пульт управления:

18-1 - индикаторы (И), светодиоды (С);

18-2 - клавиатура;

19 - узел согласования;

Д1 - диод, например 2Д510А или аналогичный;

Д2 - стабилитрон, например В255С39 или аналогичный;

V - транзистор ВС547 или аналогичный;

R - резисторы, например С2-33 или аналогичные;

DV - оптрон, например Н608-2 или аналогичный;

20 - триггер Шмитта, например К155ТЛ1 или аналогичный.

На фиг.4 обозначены:

Т1 - транзистор, например КТ3102А, или аналогичный;

Т2 - транзистор, например КТ837Е, или аналогичный;

R - резисторы, например С2-33 или аналогичные.

Микропроцессорное устройство автоматической частотной разгрузки содержит блок сравнения 3, блок запрета 4, два регистра памяти 5 и 6, микропроцессор 1, блок ввода-вывода 8, счетчик 2 и таймер 7, причем выходы первого регистра 5 соединены со входами второго регистра 6, выход блока сравнения 3 соединен со вторым входом "Т1" микропроцессора 1, выход "Р2-4" которого соединен со входом блока запрета 4, группа входов-выходов 12 микропроцессора 1 соединена с группой входов первого регистра 5 и группой выходов второго регистра 6, вторая группа входов которого соединена с первой группой выходов "WR, RD" микропроцессора 1, первая группа выходов блока ввода-вывода 8 соединена с группой входов "Р1-2" микропроцессора 1, вторая группа выходов 10 блока ввода-вывода 8 является группой релейных выходов устройства, группа входов 9 которого является первой группой входов блока ввода-вывода 8, вход счетчика 2 соединен с выходом "ALE" из группы входов-выходов 12 микропроцессора 1, вторая группа выходов "Р2" которого соединена со второй группой входов блока ввода-вывода 8, группа входов-выходов которого соединена с группой входов-выходов 12 микропроцессора 1 и группой выходов таймера 7, первый вход "С2" которого соединен с выходом "12" счетчика 2, второй вход таймера "СЕО" соединен с выходом блока сравнения 3, первый и второй входы которого являются входами устройства, первый вход "INT" микропроцессора 1 соединен с выходом "Q2" таймера 7, третий вход "CS" которого соединен с выходом блока ввода-вывода 8, третья группа входов которого соединена с третьей группой выходов "Р1-1" микропроцессора 1, первая "А" и вторая "RD, WR" группа входов таймера 7 соединены, соответственно, с группой выходов первого регистра 5 и с первой группой выходов "WR,RD,PME" микропроцессора 1.

Устройство производит эффективное отключение нагрузки в начале частотной аварии при достижении заданных уставок по частоте, скорости, времени и автоматическое повторное включение по частоте при достижении уставок.

Устройство реализует четыре алгоритма функционирования:

АЧР1 - автоматическая частотная разгрузка без выдержки времени с возможностью блокировки по скорости снижения частоты;

АЧР2 - автоматическая частотная разгрузка с выдержкой времени;

АЧРС - автоматическая частотная разгрузка по скорости снижения частоты;

ЧАПВ - автоматическое повторное включение по частоте при выполнении определенных условий.

Устройство производит отключение нагрузки по алгоритму АЧР1, если частота сети снизилась ниже значения уставки АЧР1 по частоте, а скорость снижения частоты меньше значения уставки блокировки действия АЧР1 по скорости.

Устройство производит отключение нагрузки по алгоритму АЧР2 после снижения частоты сети ниже значения уставки по частоте запуска и сохранения частоты возврата в течение некоторого времени.

Устройство производит отключение нагрузки по алгоритму АЧРС, если скорость изменения частоты превышает значение уставки в течение определенного числа периодов контролируемого напряжения.

При выполнении алгоритма ЧАПВ устройство выдает три независимые команды для подключения нагрузок, отключенных алгоритмами АЧР1, АЧР2 и АЧРС при выполнении определенных условий.

При соответствующем задании уставок по скорости уменьшения частоты в сети возможно срабатывание всех алгоритмов разгрузки в процессе одной частотной аварии.

Устройство измеряет следующие параметры:

- частоту F;

- скорость изменения частоты S;

- контролирует нижний уровень напряжения сети (0,4Uном) при котором может нарушиться достоверность измерений. Частота сигнала измеряется по сумме длительностей полупериодов напряжения

где T1 - длительность нечетного полупериода,

T2 - длительность четного полупериода.

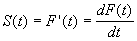

Скорость изменения частоты вычисляется как первая производная частоты сигнала повремени

где dF - приращение частоты за время dt;

dt - малый интервал времени.

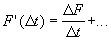

Для оценки первой производной частоты применяется метод численного дифференцирования данных

Для оценивания частоты периодического сигнала применяется временной метод измерения.

Аппаратно выполнение алгоритмов реализовано следующим образом: контролируемый сигнал поступает в блок сравнения 3 через трансформатор Тр, обеспечивающий гармоническую развязку, на компаратор К и оптопару DV с транзистором Т, обеспечивающие контроль нижнего уровня напряжения сети путем формирования сигнала на входе S компаратора К, при этом компаратор, при нарушении уровня входного напряжения, выдает в микропроцессор 1 сигнал, по которому микропроцессор формирует управляющий сигнал из порта Р2-4 на блок запрета 4, который снимает напряжение с реле 17 блока ввода-вывода 8, и на дисплей И поступает определенная информация. Если нижний уровень входного напряжения в норме, то компаратор формирует последовательность прямоугольных импульсов с частотой контролируемого аналогового сигнала, т.е. из исходного сигнала формируется бинарный сигнал "меандр", который переключает между собой два канала измерения временных интервалов (таймера Т1 микропроцессора и таймер 7). Синхронизация таймера 7 осуществляется сигналом ALE, деленным счетчиком 2 до частоты полупериода. Таким образом один таймер измеряет длительность четного полупериода, а другой - нечетного. Каждый переход контролируемого напряжения через ноль активирует включение одного из таймеров, остановку счета второго таймера и считывание его значения. Такая реализация позволяет правильно обрабатывать возможные колебания управляющего сигнала "меандр" типа 0-1-0 в зоне перехода через ноль контролируемого напряжения. В каждый момент времени в памяти микропроцессора хранится N оценок длительности полупериодов в отсчетах таймера.

Ti=Kt·ti, i=1... N

где Ti - текущая оценка длительности полупериода тактов,

Кт - длительность квантования по времени.

Текущая оценка частоты сигнала вычисляется один раз за период по формуле

где F

Ti - длительность текущего полупериода;

Тi-1 - длительность предыдущего полупериода.

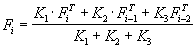

Для уменьшения воздействия шумов и случайных процессов первичная информация о частоте сглаживается с учетом весовых коэффициентов

где Fi - сглаженная оценка частоты,

K1, К2, К3 - весовые коэффициенты.

Выбор весовых коэффициентов осуществляется на этапе разработки по результатам моделирования и макетных испытаний.

Измерение скорости изменения частоты.

Исходной информацией для измерения скорости изменения частоты являются массивы N сглаженных оценок частоты и длительностей полупериодов.

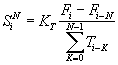

Оценка скорости вычисляется один раз за полупериод согласно формуле

где S

Fi - текущая оценка скорости изменения частоты,

Fi-n - оценка скорости изменения частоты за Nый прошлый период,

ti-K - оценка длительности N полупериодов.

Результаты измерений накапливаются в памяти микропроцессора

1. Сюда же, в порт Р0, по шине 12 из блока ввода-вывода 8 поступает информация о состоянии дискретных входов, а в порт Р1-2 - информация с клавиш клавиатуры 18-2 блока ввода-вывода. Микропроцессор производит логическую обработку поступающей информации (сравнение измеренных параметров контролируемого аналогового сигнала с уставками, отсчет выдержек времени и т.д.) и формирует команды сигнализации, которые передаются по шине 11 на светодноды С пульта управления 18 и на выходные реле 17, установленные в блоке ввода-вывода 8. Кроме того, микропроцессор 1 готовит информацию для отображения на индикаторах дисплея И 18-1. Управление регистром индикации 15 и регистром данных 14 производится микропроцессором через дешифратор 13.

Таким образом устройство, кроме измерения с высокой точностью и в соответствии с алгоритмами частоты:

1) измеряет скорость изменения частоты и контролирует нижний уровень напряжения сети;

2) обеспечивает:

- автоматическую частотную разгрузку без выдержки времени с возможностью блокировки по скорости снижения частоты, т.е. производит отключение нагрузки после снижения частоты сети ниже предела значения уставки срабатывания по частоте и не производит отключение нагрузки, если снижение напряжения происходило со скоростью, выше значения уставки по скорости снижения частоты напряжения;

3) отключение нагрузки по алгоритму АЧР2 после снижения частоты сети ниже значения уставки по частоте запуска и сохранение частоты возврата в течение некоторого времени;

4) автоматическое повторное включение по частоте ЧАПВ при выполнении определенных условий, например:

а) сработал соответствующий алгоритм АЧР;

б) частота сети установилась выше уставки и т.д.;

5) местный ввод, хранение и отображение уставок.

Для надежности в устройстве имеется система самодиагностики, которая состоит из двух подсистем - фоновой самодиагностики, которая обеспечивает контроль работоспособности основных узлов устройства в течение всего срока эксплуатации, и набора тестов, запускаемых по вызову.

Фоновая самодиагностика выполняется непрерывно, в течение всего времени работы устройства, обеспечивая контроль работоспособности всех основных узлов. Результаты самодиагностики анализируются микропроцессором. В состав диагностики входят:

- проверка дискретных входов;

- тестирование дисплея (программные известные методы);

- тестирование клавиатуры (программные известные методы).

Таким образом, устройство имеет простую схему (исключены масштабный усилитель, аналого-цифровой преобразователь и микропроцессорная система), соответственно, меньшие (в два раза) габариты и более простую эксплуатацию (управление четырьмя функциональными кнопками - ввод уставок, чтение уставок на восьмисегментных индикаторах) и обеспечивает выполнение основных функций по частотной разгрузке.

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРОПРОЦЕССОРНОЕ МНОГОФУНКЦИОНАЛЬНОЕ УСТРОЙСТВО РЕЛЕ ЧАСТОТЫ | 2000 |

|

RU2171475C1 |

| МИКРОПРОЦЕССОРНОЕ УСТРОЙСТВО РЕЛЕЙНОЙ ЗАЩИТЫ И АВТОМАТИКИ С ДИСТАНЦИОННЫМ УПРАВЛЕНИЕМ | 2002 |

|

RU2222083C2 |

| МИКРОПРОЦЕССОРНОЕ РЕЛЕЙНОЕ УСТРОЙСТВО ИМПУЛЬСНОЙ СИГНАЛИЗАЦИИ | 2000 |

|

RU2195707C2 |

| МНОГОПРОЦЕССОРНАЯ ИНФОРМАЦИОННО-УПРАВЛЯЮЩАЯ СИСТЕМА РЕЛЕЙНОЙ ЗАЩИТЫ И АВТОМАТИКИ | 2001 |

|

RU2210104C2 |

| МИКРОПРОЦЕССОРНАЯ СИСТЕМА ЗАЩИТЫ | 2000 |

|

RU2173924C1 |

| ИСТОЧНИК ПИТАНИЯ КОМБИНИРОВАННЫЙ | 2001 |

|

RU2216844C2 |

| УСТРОЙСТВО ПРОТИВОАВАРИЙНОЙ АВТОМАТИКИ | 2001 |

|

RU2221318C2 |

| Способ автоматической частотной разгрузки энергорайона в условиях отклонения показателей качества электроэнергии | 2021 |

|

RU2759220C1 |

| Устройство защиты и автоматики распределительной подстанции | 1988 |

|

SU1584023A1 |

| СПОСОБ АВТОМАТИЧЕСКОЙ ЧАСТОТНОЙ РАЗГРУЗКИ ЭНЕРГОСИСТЕМЫ | 1998 |

|

RU2153751C2 |

Изобретение относится к релейной технике и предназначено для предотвращения аварийного снижения частоты в энергосистеме и ее восстановления до заданного уровня путем автоматического отключения части потребителей при возникновении дефицита активной мощности и для автоматического включения отключенных потребителей после ликвидации аварийного дефицита мощности. Техническим результатом является упрощение, снижение габаритных размеров и упрощение эксплуатации при сохранении основных функций. Микропроцессорное устройство автоматической частотной разгрузки содержит блок сравнения, блок запрета, микропроцессор, два регистра памяти, счетчик, таймер и блок ввода-вывода. Устройство предназначено для установки в помещениях централизованных щитов управления и релейных блочных групповых щитов электростанций. 4 ил.

Микропроцессорное устройство автоматической частотной разгрузки, содержащее блок сравнения, блок запрета, два регистра памяти, микропроцессор, выполняющий логическую обработку поступающей информации, сравнение измеренных параметров контролируемого аналогового сигнала с уставками, отсчет выдержек времени и формирование команд сигнализации, и блок ввода-вывода, причем выходы первого регистра соединены со входами второго регистра, выход блока сравнения соединен со вторым входом микропроцессора, выполняющего логическую обработку поступающей информации, сравнение измеренных параметров контролируемого аналогового сигнала с уставками, отсчет выдержек времени и формирование команд сигнализации, выход которого соединен со входом блока запрета, группа входов-выходов микропроцессора, выполняющего логическую обработку поступающей информации, сравнение измеренных параметров контролируемого аналогового сигнала с уставками, отсчет выдержек времени и формирование команд сигнализации, соединена с группой входов первого регистра и группой выходов второго регистра, вторая группа входов которого соединена с первой группой выходов микропроцессора, выполняющего логическую обработку поступающей информации, сравнение измеренных параметров контролируемого аналогового сигнала с уставками, отсчет выдержек времени и формирование команд сигнализации, первая группа выходов блока ввода-вывода соединена с группой входов микропроцессора, выполняющего логическую обработку поступающей информации, сравнение измеренных параметров контролируемого аналогового сигнала с уставками, отсчет выдержек времени и формирование команд сигнализации, вторая группа выходов блока ввода-вывода является группой релейных выходов устройства, группа входов которого является первой группой входов блока ввода-вывода, отличающееся тем, что в него введены счетчик и таймер, причем вход счетчика соединен с выходом из группы входов-выходов микропроцессора, выполняющего логическую обработку поступающей информации, сравнение измеренных параметров контролируемого аналогового сигнала с уставками, отсчет выдержек времени и формирование команд сигнализации, вторая группа выходов которого соединена со второй группой входов блока ввода-вывода, группа входов-выходов которого соединена с группой входов-выходов микропроцессора, выполняющего логическую обработку поступающей информации, сравнения измеренных параметров контролируемого аналогового сигнала с уставками, отсчет выдержек времени и формирование команд сигнализации, и с группой выходов таймера, первый вход которого соединен с выходом блока сравнения, первый и второй входы которого являются входами устройства, первый вход микропроцессора, выполняющего логическую обработку поступающей информации, сравнение измеренных параметров контролируемого аналогового сигнала с уставками, отсчет выдержек времени и формирование команд сигнализации, соединен с выходом таймера, третий вход которого соединен с выходом блока ввода-вывода, третья группа входов которого соединена с третьей группой выходов микропроцессора, выполняющего логическую обработку поступающей информации, сравнение измеренных параметров контролируемого аналогового сигнала с уставками, отсчет выдержек времени и формирование команд сигнализации, первая и вторая группа входов таймера соединены соответственно с группой выходов первого регистра и с первой группой выходов микропроцессора, выполняющего логическую обработку поступающей информации, сравнение измеренных параметров контролируемого аналогового сигнала с уставками, отсчет выдержек времени и формирование команд сигнализации.

| МИКРОПРОЦЕССОРНОЕ МНОГОФУНКЦИОНАЛЬНОЕ УСТРОЙСТВО РЕЛЕ ЧАСТОТЫ | 2000 |

|

RU2171475C1 |

| МИКРОПРОЦЕССОРНАЯ СИСТЕМА ЗАЩИТЫ | 2000 |

|

RU2173924C1 |

| Устройство для блокировки включения секционного выключателя | 1990 |

|

SU1702480A1 |

| US 5309312 А, 03.05.1994 | |||

| US 5495384 А, 27.02.1996 | |||

| DE 3132730 А1, 10.03.1983 | |||

| DE 3611083 А1, 08.10.1987 | |||

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ЛЯРИНГОТРАХЕАЛЬНОГО ПРОСВЕТА | 1967 |

|

SU224749A1 |

| Экономайзер | 0 |

|

SU94A1 |

Авторы

Даты

2004-06-10—Публикация

2002-01-08—Подача