Изобретение относится к автоматике и вычислительной технике, в частности к устройствам управления, и может быть использовано для управления секционными выключателями. Известное устройство - микропроцессорная электронная система расцепления выключателя [А.С. РСТ (WO) 91/03827, Н 02 Н 3/08, БИ 7, 1991] , содержащая цепь для точного определения трехфазного тока, токовые датчики, трансформатор с входным и выходными реакторами, соленоид, сумматоры, процессор позволяет управлять выключателем, но обладает низкой помехоустойчивостью и надежностью. Известное устройство - процессорная система расцепления выключателя с надежным дисплеем состояния системы выключателя [АС. РСТ (WO), 91/03828, Н 02 Н 3/093, 3/24, Б.И. 7, 1990], содержащая жидкокристаллический индикатор с сегментом, батарею питания, ручной выключатель, защелку, транзисторы, процессор позволяет управлять выключателем, обладает большей надежностью за счет использования малопотребляющей цепи индикации расцепления, но имеет также низкую помехоустойчивость. Наиболее близким техническим решением является устройство для контроля и управления [AC. (SU) 1624481, G 06 F 15/46, Б.И. 4, 1991], содержащее генератор тактовых импульсов, элемент ИЛИ, два счетчика, два дешифратора, (к+2)-блоков элементов ИЛИ, (к+1)-блоков элементов И к-регистров уставок, схему сравнения, элемент И, элемент НЕ, к-выходных групп элементов И, блок формирования команд регулировки параметров и блок задержки. Прототип также обладает низкой надежностью за счет отсутствия диагностики входящих узлов и низкой помехоустойчивостью за счет отсутствия зашиты от внешних воздействий.

Цель изобретения - повышение надежности устройства за счет введения диагностики входящих узлов и повышение помехоустойчивости за счет обеспечения защиты от внешних воздействий путем введения гальванической развязки и создания высокой электрической прочности изоляции между первичной и вторичной цепями.

Поставленная цель достигается тем, что в известное устройство, содержащее пять регистров (при использовании пяти каналов), два счетчика, дешифратор, блок элементов И, элемент НЕ и блок формирования команд, введены n-входные узлы, счетный узел, коммутатор, два шинных формирователя, второй элемент НЕ, узел блокировки и m-реле с m-резисторами, причем входы n-входных узлов являются первой группой входов устройства, вторая группа входов которого является входами счетного узла, первый выход которого соединен со счетным входом первого счетчика, группа выходов которого соединена с первой группой входов второго регистра, вторая группа входов которого соединена с группой выходов второго счетчика, счетный вход которого соединен с выходом первого счетчика, вход сброса которого соединен со входом сброса второго счетчика и с первым выходом дешифратора, группа входов которого соединена с группой выходов первого шинного формирователя, группа входов которого соединена с первой группой входов-выходов коммутатора и третьей группой входов-выходов блока формирования команд, первая и вторая группы входов-выходов которого являются первой и второй группами входов-выходов устройства, выход сброса блока формирования команд соединен с первым входом узла блокировки, второй вход которого соединен с выходом второго элемента НЕ, вход которого соединен с первыми управляющими входами четвертого и пятого регистров и первым выходом первого шинного формирователя, второй выход которого соединен со входом первого элемента НЕ и с первым входом коммутатора, второй вход которого соединен с третьим выходом первого шинного формирователя, выход первого элемента НЕ соединен с первым входом первого регистра, группа входов которого соединена с выходами n-узлов входа, второй вход первого регистра соединен с третьим выходом дешифратора, второй вход которого соединен с первым входом второго регистра, группа выходов которого соединена с группами выходов второго шинного формирователя и первого регистра, с первой группой входов блока элементов И, с группами входов третьего и четвертого регистров и со второй группой входов-выходов коммутатора, второй вход второго регистра соединен со вторым выходом счетного узла, второй вход четвертого регистра соединен с четвертым выходом дешифратора, шестой выход которого соединен со входом третьего регистра, группа выходов которого соединена со второй группой входов блока элементов И, группа выходов которого соединена с группой входов пятого регистра, второй вход которого соединен с пятым выходом дешифратора, седьмой и восьмой выходы которого соединены соответственно с первым и вторым входами второго шинного формирователя, каждый вход из группы входов которого соединен через соответствующий резистор со входом соответствующей m-й обмотки реле и соответствующим выходом четвертого или пятого регистра, выходы узла блокировки соединены с выходами обмоток реле, цепи контактов которых являются третьей группой входов-выходов устройства, причем блок формирования команд содержит центральный процессор, супервизор, часы реального времени, постоянное запоминающее устройство, два оперативных запоминающих устройства, два набора буферных регистров, индикаторы, клавиатуру, микропроцессор, набор шинных формирователей, драйвер для связи с АСУ и драйвер для связи с ПЭВМ, первая группа входов-выходов которого является первой группой входов-выходов устройства, вторая группа входов-выходов которого является первой группой входов-выходов драйвера для связи с АСУ, вторая группа входов-выходов которого соединена со второй группой входов-выходов драйвера для связи с ПЭВМ и микропроцессора, первая группа входов-выходов которого соединена с группой входов-выходов второго оперативного запоминающего устройства, третья группа входов-выходов микропроцессора соединена с первой группой входов-выходов второго набора буферных регистров, вторая группа входов-выходов которого соединена с группами входов-выходов процессора и супервизора, часов реального времени, постоянного запоминающего устройства, первого оперативного запоминающего устройства и первой группой входов-выходов набора шинных формирователей, вторая группа входов-выходов которого является третьей группой входов-выходов блока формирования команд, выход сброса которого является выходом супервизора, группа входов-выходов которого соединена с группой входов-выходов первого набора буферных регистров, клавиатурой и индикаторами, причем входной узел содержит четыре резистора, стабилитрон, диод, транзистор и оптрон, выход которого является выходом входного узла, первый вход которого соединен со входами первого и второго резисторов, выход которого соединен с коллектором транзистора и первым входом оптрона, второй вход которого соединен с эмиттером транзистора, входом третьего резистора и анодом диода, катод которого соединен с базой транзистора, выходом первого резистора и катодом стабилитрона, анод которого соединен с выходом третьего резистора и является вторым входом входного узла, третий вход оптрона соединен со входом четвертого резистора, выход которого соединен с четвертым входом оптрона, причем счетный узел содержит три резистора, диод, оптрон, конденсатор и микропроцессор, первый выход которого является первым выходом счетного узла, второй выход которого является вторым выходом микропроцессора, первый вход которого соединен со входом третьего резистора и первым выходом оптрона, второй выход которого соединен со входом конденсатора и четвертым входом микропроцессора, второй и третий входы которого соединены с выходом конденсатора и выходом третьего резистора, первый вход оптрона соединен с выходами первого и второго резисторов и катодом диода, анод которого соединен со вторым входом оптрона, входом второго резистора и является вторым входом счетного узла, первый вход которого является входом первого резистора, причем узел блокировки содержит пять резисторов, диод, первый и второй транзисторы, коллектор которого является выходом узла блокировки, первый вход которого соединен с анодом диода и входами первого и второго резисторов, выход которого соединен со входом третьего резистора и базой первого транзистора, эмиттер которого соединен с выходом третьего резистора, коллектор первого транзистора соединен со входом четвертого резистора, выход которого соединен со входом пятого резистора и базой второго транзистора, эмиттер которого соединен с выходом пятого резистора, катод диода является вторым входом узла блокировки.

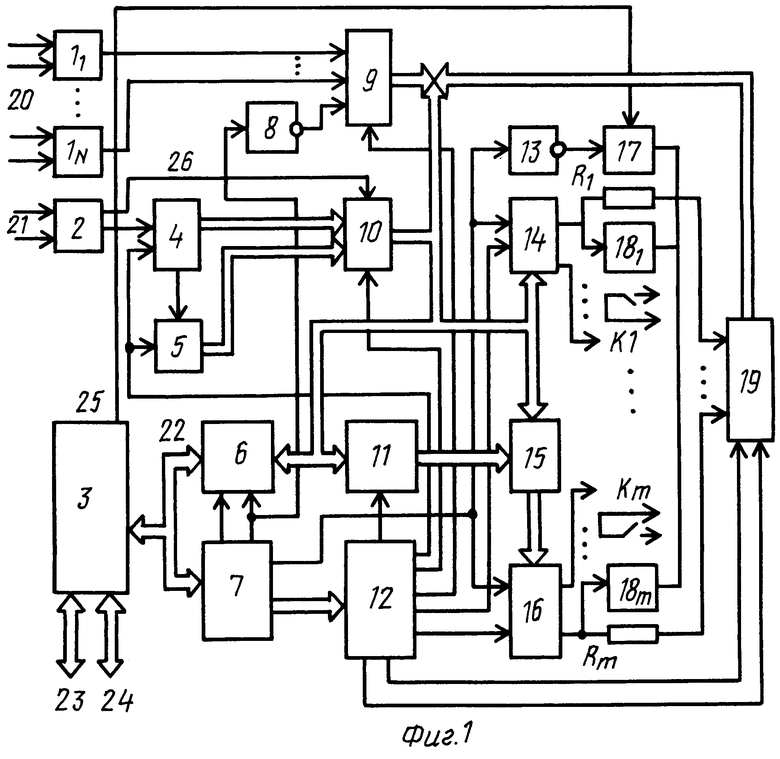

На фиг.1 приведена структурная схема устройства;

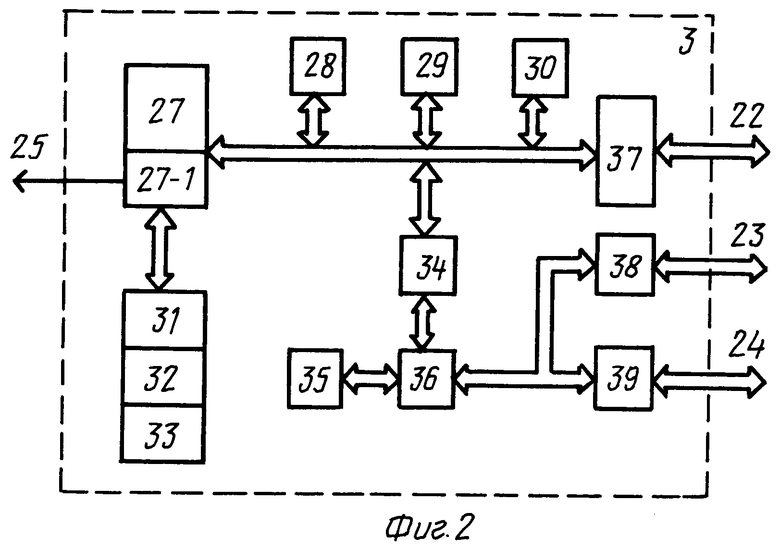

на фиг.2 - блок формирования команд управления;

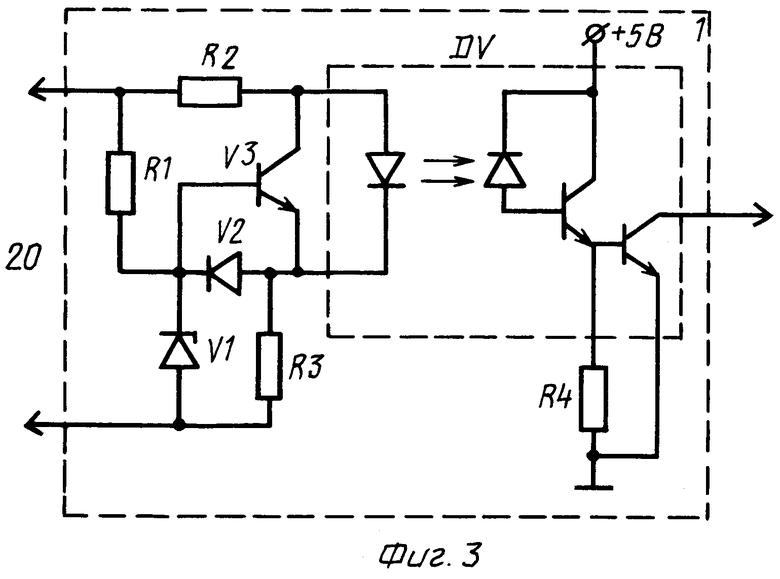

на фиг.3 - входной узел;

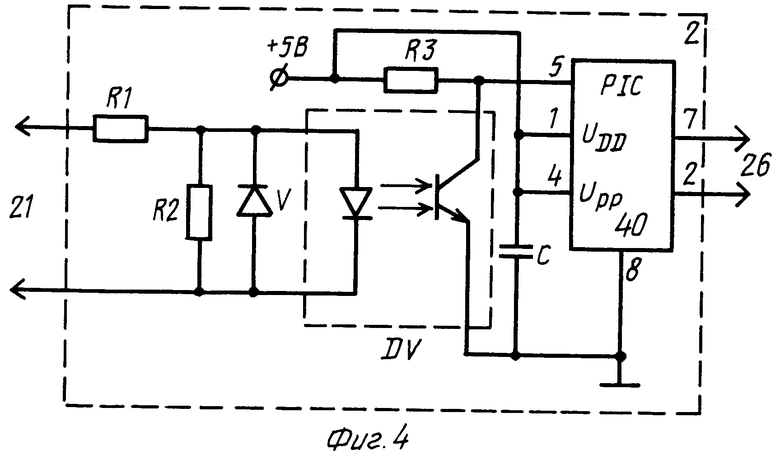

на фиг.4 - счетный узел;

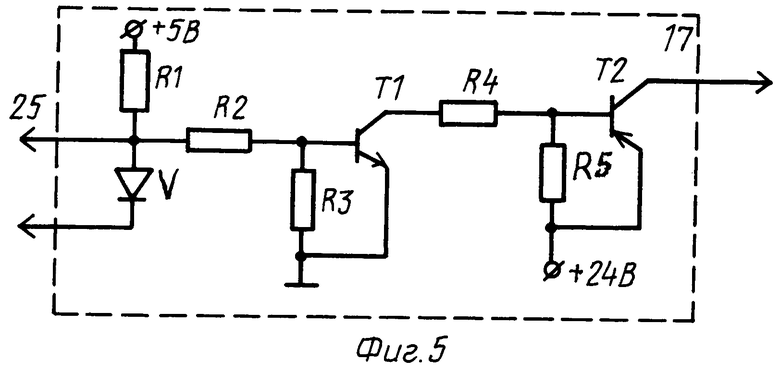

на фиг.5 - узел блокировки.

На фиг.1 обозначены:

11. ..1N - входные узлы; 2 - счетный узел; 3 - блок формирования команд, 4, 5 - первый и второй счетчики типа КР1554ИЕ23 или аналогичные;

6 - коммутатор типа КР1554АП9 или аналогичный;

7 - первый шинный формирователь типа КР1554АП5 или аналогичный;

8 - первый элемент НЕ типа КР1554ЛН1 или аналогичный;

9 - первый регистр типа КР1554ИР23 или аналогичный;

10 - второй регистр типа КР1554АП5 или аналогичный;

11 - третий регистр типа КР1554ИР23 или аналогичный;

12 - дешифратор типа КР1554ИД7 или аналогичный;

13 - второй элемент НЕ типа КР1554ЛН1 или аналогичный;

14 - четвертый регистр типа КР1554ИР41 с усилителями Дарлингтона типа МСТ1413ВР на выходе (на схеме для упрощения не показаны) или аналогичный;

15 - блок элементов И типа КР1554ЛИ1 или аналогичный;

16 - пятый регистр типа КР1554ИР41 с усилителями Дарлингтона типа МСТ1413ВР на выходе (на схеме для упрощения не показаны) или аналогичный;

17 - узел блокировки;

181...l8m - реле типа RM83-1021-35-1024 фирмы "RELOOL" или аналогичное;

K1. . .КМ - цепи контактов реле, составляющие третью группу входов-выходов;

R1...RM - резисторы типа С2-23 или аналогичные;

19 - второй шинный формирователь типа КР1554АП3 или аналогичный;

20 - линии дискретных входных сигналов;

21 - линии входных сигналов от телеметрических выходов электрического счетчика;

22 - шина адрес/данные/управление;

23 - шина связи с ПЭВМ;

24 - шина связи с АСУ;

25 - линия сигнала "RESET";

26 - линия сигнала "CLOCK".

На фиг.2 обозначены:

27 - центральный процессор типа AT89C52-24PI или аналогичный (для упрощения схемы не показан резонатор и цепи управления);

27-1 - супервизор типа ADM693AN фирмы "ANALOG DEVICES" или аналогичный;

28 - часы реального времени типа RTC72423B фирмы "EPSON" или аналогичные;

29 - ПЗУ типа АТ28С256 или аналогичное;

30 - ОЗУ типа SRM2A256LLCT или аналогичное;

31 - набор буферных регистров типа КР1554ИР23 или аналогичных;

32 - индикаторы;

33 - клавиатура;

34 - набор буферных регистров типа КР1554ИР23 или аналогичных;

35 - ОЗУ типа SRM2A256LLCT или аналогичное;

36 - микропроцессор типа AT89C52-24PI или аналогичный (для упрощения схемы не показан резонатор и цепи управления);

37 - набор шинных формирователей типа КР1554АП5 или 74НС244 или аналогичных;

38, 39 - драйверы для связи с АСУ и ПЭВМ типа ADM232AAN фирмы "ANALOG DEVICES" или аналогичные.

На фиг.3 обозначены:

R1 - резистор типа С2-33Н или аналогичный;

R2 - резистор типа С2-14 или аналогичный;

R3 - резистор тина С2-36 или аналогичный;

R4 - резистор типа С2-33Н или аналогичный;

V1 - стабилитрон типа BZX55C39 фирмы "PHILIPS" или аналогичный;

V2 - диод типа 1N4448 фирмы "PHILIPS" или аналогичный;

V3 - транзистор типа ВС547 фирмы "PHILIPS" или аналогичный;

DV - оптрон типа GN139 фирмы "HEWLET PACKARD" или аналогичный;

На фиг.4 обозначены:

R1...R3 - резисторы типа С2-33Н или аналогичные;

V2 - диод типа 2D510А или аналогичный;

DV - оптрон типа SFH618A-3 или аналогичный;

40 - микропроцессор типа PIC12C508A или аналогичный;

С - конденсатор типа К10-17 или аналогичный.

На фиг.5 обозначены:

R1...R5 - резисторы типа С2-33Н или аналогичные;

V - диод типа 2D510А или аналогичный;

Т1 - транзистор типа КТ3102А или аналогичный;

Т2 - транзистор типа КТ837Е или аналогичный.

Блок формирования команд 3 может быть также реализован на базе микропроцессорной системы в соответствии с [Н.Н.Чернобров, В.А.Семенов. "Репейная защита энергетических систем". 1998 г., с. 778-783]. Подробная информация о микропроцессорной системе приведена там же на с. 778-783.

Устройство противоаварийной автоматики содержит пять регистров 9...11, 14 и 16, два счетчика 4 и 5, дешифратор 12, блок элементов И 15, два элемента НЕ 8 и 13, блок формирования команд 3, n-входных узлов 11...1N, счетный узел 2, коммутатор 6, два шинных формирователя 7 и 19, узел блокировки 17, m-реле 181...18m с m-резисторами R1...RM и цепями контактов K1...КМ, причем входы 20 n-входных узлов являются первой группой входов устройства, вторая группа входов 21 которого является входами счетного узла 2, первый выход которого соединен со счетным входом первого счетчика 4, группа выходов которого соединена с первой группой входов второго регистра 10, вторая группа входов которого соединена с группой выходов второго счетчика 5, счетный вход которого соединен с выходом первого счетчика 4, вход сброса которого соединен со входом сброса второго счетчика 5 и с первым выходом дешифратора 6, группа входов которого соединена с группой выходов первого шинного формирователя 7, группа входов которого соединена с первой группой входов-выходов 22 коммутатора 6 и третьей группой входов-выходов блока формирования команд 3, первая 23 и вторая 24 группы входов-выходов которого являются первой и второй группами входов-выходов устройства, выход сброса 25 блока формирования команд соединен с первым входом узла блокировки 17, второй вход которого соединен с выходом второго 13 элемента НЕ, вход которого соединен с первыми управляющими входами четвертого 14 и пятого 16 регистров и первым выходом первого 7 шинного фopмиpoвaтeля, второй выход которого соединен со входом первого 8 элемента НЕ и с первым входом коммутатора 6, второй вход которого соединен с третьим выходом первого шинного формирователя 7, выход первого 8 элемента НЕ соединен с первым входом первого регистра 9, группа входов которого соединена с выходами n-узлов 11...1N входа, второй вход первого 9 регистра соединен с третьим выходом дешифратора 12, второй вход которого соединен с первым входом второго регистра 10, группа выходов которого соединена с группами выходов второго 19 шинного формирователя и первого регистра 9, с первой группой входов блока 15 элементов И, с группами входов третьего 11 и четвертого 14 регистров и со второй группой входов-выходов коммутатора 6, второй вход 26 второго регистра 10 соединен со вторым выходом счетного узла 2, второй вход четвертого регистра 14 соединен с четвертым выходом дешифратора 12, шестой выход которого соединен со входом третьего регистра 11, группа выходов которого соединена со второй группой входов блока 15 элементов И, группа выходов которого соединена с группой входов пятого регистра 16, второй вход которого соединен с пятым выходом дешифратора 12, седьмой и восьмой выходы которого соединены соответственно с первым и вторым входами второго 19 шинного формирователя, каждый вход из группы входов которого соединен через соответствующий резистор R1. ..RM со входом соответствующей m-й обмотки 181...18m реле и соответствующим выходом четвертого 14 или пятого 16 регистров, выходы узла блокировки 17 соединены с выходами обмоток реле 181. . . 18m, цепи контактов K1...КМ которых являются третьей группой входов-выходов устройства, блок формирования команд содержит центральный процессор 27, супервизоp 27-1, часы реального времени 28, постоянное запоминающее устройство 29, два оперативных запоминающих устройства 30 и 35, два набора буферных регистров 31 и 34, индикаторы 32, клавиатуру 33, микропроцессор 36, набор шинных формирователей 37, драйвер для связи с АСУ 38 и драйвер для связи с ПЭВМ 39, первая группа входов-выходов 24 которого является первой группой входов-выходов устройства, вторая группа входов-выходов 23 которого является первой группой входов-выходов драйвера для связи с АСУ 38, вторая группа входов-выходов которого соединена со второй группой входов-выходов драйвера для связи с ПЭВМ 39 и микропроцессора 36, первая группа входов-выходов которого соединена с группой входов-выходов второго оперативного запоминающего устройства 35, третья группа входов-выходов микропроцессора 36 соединена с первой группой входов-выходов второго набора буферных регистров 34, вторая группа входов-выходов которого соединена с группами входов-выходов процессора 27 и супервизора 27-1, часов реального времени 28, постоянного запоминающего устройства 29, первого оперативного запоминающего устройства 30 и первой группой входов-выходов набора шинных формирователей 37, вторая группа входов-выходов 22 которого является третьей группой входов-выходов блока формирования команд, выход сброса 25 которого является выходом супервизора 27-1, группа входов-выходов которого соединена с группой входов-выходов первого набора буферных регистров 31, клавиатурой 33 и индикаторами 32, входной узел 1 содержит четыре резистора R1...R4, стабилитрон V1, диод V2, транзистор V3 и оптрон DV, выход которого является выходом входного узла, первый вход которого соединен со входами первого R1 и второго R2 резисторов, выход которого соединен с коллектором транзистора V3 и первым входом оптрона DV, второй вход которого соединен с эмиттером транзистора V3, входом третьего резистора R3 и анодом диода V2, катод которого соединен с базой транзистора V3, выходом первого резистора R1 и катодом стабилитрона V1, анод которого соединен с выходом третьего резистора R3 и является вторым входом входного узла, третий вход оптрона DV соединен со входом четвертого резистора R4, выход которого соединен с четвертым входом оптрона DV, счетный узел 2 содержит три резистора R1...R3, диод V2, оптрон DV, конденсатор С и микропроцессор 40, первый выход 7 которого является первым выходом счетного узла, второй выход 2 которого является вторым выходом 26 микропроцессора 40, первый вход 5 которого соединен со входом третьего резистора R3 и первым выходом оптрона DV, второй выход которого соединен со входом конденсатора С и четвертым входом 8 микропроцессора 40, второй 1 и третий 4 входы которого соединены с выходом конденсатора С и выходом третьего резистора R3, первый вход оптрона соединен с выходами первого R1 и второго R2 резисторов и катодом диода V, анод которого соединен со вторым входом оптрона DV, входом второго резистора R2 и является вторым входом счетного узла, первый вход которого является входом первого резистора R1, узел блокировки 17 содержит пять резисторов R1...R5, диод V, первый Т1 и второй Т2 транзисторы, коллектор которого является выходом узла блокировки 17, первый вход 25 которого соединен с анодом диода V и входами первого R1 и второго R2 резисторов, выход которого соединен со входом третьего резистора R3 и базой первого транзистора Т1, эмиттер которого соединен с выходом третьего резистора R3, коллектор первого транзистора Т1 соединен со входом четвертого резистора R4, выход которого соединен со входом пятого резистора R5 и базой второго транзистора Т2, эмиттер которого соединен с выходом пятого резистора R5, катод диода V является вторым входом узла блокировки 17.

Устройство обеспечивает:

- местное и дистанционное управление выключателем;

- контроль положения выключателя, выдачу сигнала аварийного отключения выключателя, контроль цепей управления выключателя с выводом информации на пульт, выходные реле и по последовательным каналам;

- получение дискретных управляющих сигналов, выдачу команд управления, аварийной и предупредительной сигнализации;

- получение и передачу управляющей информации по стандартному каналу связи;

- получение и передачу информации от электрических счетчиков;

- хранение и выдачу информации о количестве, времени и причинах аварийных отключений выключателя;

- непрерывный оперативный контроль работоспособности (самодиагностика) в течение всего времени работы.

Управление выключателем обеспечивается формированием команд включения и отключения секционного выключателя по сигналам:

- от блоков релейной защиты, поступающих на входы 20;

- с клавиатуры 33;

- поступающим по последовательным каналам 23 и 24 (от ПЭВМ или АСУ).

Индикация положения выключателя обеспечивается индикаторами 32.

Устройство работает следующим образом.

При включении питания супервизор 27-1 микропроцессора 27 формирует сигнал "RESET", по которому происходит начальная установка. При возрастании на дискретных входах 20 входного напряжения от нуля до напряжения срабатывания транзистор V3 входного узла 1 (фиг.3) открыт, т.к. к переходу "база-эмиттер" приложено открывающее напряжение. Открытый переход "коллектор-эмиттер" этого транзистора шунтирует светодиод оптопары DV и сигнал на выход входного узла 1 не передается. При достижении входного напряжения значения напряжения срабатывания, ток, проходящий по цепи R2, "коллектор-эмиттер" транзистора V3, R3 достигает такой величины, что вызванное им падение напряжения на резисторе R3 приводит к закрытию транзистора V3, т.к. напряжение на базе транзистора V3 стабилизировано стабилитроном V1, а напряжение на эмиттере растет прямо пропорционально входному напряжению. Транзистор V3 закрывается, закрытый переход "коллектор-эмиттер" не шунтирует светодиод оптопары DV и сигнал передается на выход входного узла 1. Далее этот сигнал поступает в регистр 9. Регистр 9 сохраняет и передает информацию через коммутатор в блок формирования команд 3. Входной сигнал с телеметрических выходов 21 электрического счетчика поступает на узел 2 (фиг.4). Резисторы R1 и R2 образуют делитель напряжения, который определяет напряжение включения светодиода оптопары DV при входном токе срабатывания. Токовый сигнал высокого уровня, поступая на вход оптопары DV, приводит к открытию выходного транзистора оптопары и напряжение на коллекторе транзистора уменьшается до уровня логического нуля. Токовый сигнал низкого уровня не приводит к открыванию выходного транзистора оптопары DV и напряжение на коллекторе транзистора в этом случае соответствует уровню логической единицы.

Микропроцессор PIC40 постоянно опрашивает состояние логического уровня на коллекторе транзистора оптопары и оценивает длительности уровней напряжения и периоды повторения нулевых импульсов. При выполнении определенных условий на сигнальном выходе 7 формируется отрицательный фронт (срез), по которому в счетчике 4 добавляется единица. Тестовый сигнал "CLOCK" 26 вырабатывается постоянно для подтверждения исправности микропроцессора. Двоичный код со счетчиков и сигнал подтверждения исправности 26 "CLOCK" поступают на входы регистра 10. Регистр 10 сохраняет и передает в блок формирования команд 3 через коммутатор 6 информацию по сигналу чтения, поступающему от дешифратора 12. Микропроцессор 27 блока формирования команд 3 анализирует по соответствующей программе информацию, поступающую от счетного 2 и входных 1 узлов и формирует код (адрес/данные), который через коммутатор 6 поступает на регистр 14, а для расширения адресного пространства через регистр 11 и блок элементов И 15 на регистр 16. Далее по сигналам с выходов регистров 14 и 16 реле 181...18m переводится в положение, соответствующее определенной команде выключателя. Таким образом, устройство осуществляет контроль исправности выключателя и его цепей управления, а при появлении сигнала неисправности формируется сигнал, который поступает от микропроцессора через дешифратор 12, элемент НЕ 13 на узел блокировки 17 и блокирует все обмотки реле 18 (снимает напряжение с обмоток).

Для повышения надежности в устройстве имеется система самодиагностики, которая состоит из двух подсистем - фоновой самодиагностики, которая обеспечивает контроль работоспособности основных узлов устройства в течение всего срока эксплуатации, и набора тестов, запускаемых по вызову.

Фоновая самодиагностика выполняется непрерывно в течение всего времени работы устройства, обеспечивая контроль работоспособности всех основных узлов. Результаты самодиагностики анализируются центральным процессором. В состав диагностики входят:

- проверка дискретных входов и выходов;

- тестирование клавиатуры (программные известные методы);

- тестирование каналов и т.д.

Например, при диагностике выходов сигнал снимается с резисторов R1...RМ на выходах ключей Дарлингтона регистров 14 и 16 и поступает через шинные формирователи 19, коммутатор 3 в микропроцессор 27 (при обрыве цепи или неисправности ключа уровень сигнала на резисторе будет отличаться от уровня, имеющегося в исправном узле).

Проверка каналов RS-232 и RS-485 драйверов 38 и 39 производится контролем равенства переданной и принятой информации (путем установки заглушки и без нее).

Таким образом, введение самодиагностики и тестирования позволяет повысить надежность устройства путем контроля работоспособности как в процессе работы, так и используя стендовое оборудование. Повышение помехоустойчивости устройства обеспечивается применением оптронов во входных узлах. Оптроны обеспечивают гальваническую развязку и высокую электрическую прочность изоляции между первичной и вторичными цепями.

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРОПРОЦЕССОРНОЕ УСТРОЙСТВО АВТОМАТИЧЕСКОЙ ЧАСТОТНОЙ РАЗГРУЗКИ | 2002 |

|

RU2230414C2 |

| МИКРОПРОЦЕССОРНОЕ РЕЛЕЙНОЕ УСТРОЙСТВО ИМПУЛЬСНОЙ СИГНАЛИЗАЦИИ | 2000 |

|

RU2195707C2 |

| МИКРОПРОЦЕССОРНОЕ МНОГОФУНКЦИОНАЛЬНОЕ УСТРОЙСТВО РЕЛЕ ЧАСТОТЫ | 2000 |

|

RU2171475C1 |

| ИСТОЧНИК ПИТАНИЯ КОМБИНИРОВАННЫЙ | 2001 |

|

RU2216844C2 |

| МИКРОПРОЦЕССОРНОЕ УСТРОЙСТВО РЕЛЕЙНОЙ ЗАЩИТЫ И АВТОМАТИКИ С ДИСТАНЦИОННЫМ УПРАВЛЕНИЕМ | 2002 |

|

RU2222083C2 |

| МИКРОПРОЦЕССОРНАЯ СИСТЕМА ЗАЩИТЫ | 2000 |

|

RU2173924C1 |

| МНОГОПРОЦЕССОРНАЯ ИНФОРМАЦИОННО-УПРАВЛЯЮЩАЯ СИСТЕМА РЕЛЕЙНОЙ ЗАЩИТЫ И АВТОМАТИКИ | 2001 |

|

RU2210104C2 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Устройство для сопряжения двух электронно-вычислительных машин | 1988 |

|

SU1594555A2 |

| Устройство для приема информации с датчиков | 1988 |

|

SU1730649A1 |

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам управления. Технический результат - повышение надежности устройства за счет введения диагностики входящих узлов и повышение помехоустойчивости за счет обеспечения защиты от внешних воздействий путем введения гальванической развязки и создания высокой электрической прочности изоляции между первичной и вторичной цепями. Устройство противоаварийной автоматики содержит пять регистров, два счетчика, дешифратор, блок элементов И, два элемента НЕ, блок формирования команд, n-входных узлов, счетный узел, коммутатор, два шинных формирователя, узел блокировки и m-реле с m-резисторами и цепями контактов. Предложенное устройство может быть использовано для управления секционными выключателями. 5 ил.

Устройство противоаварийной автоматики, содержащее пять регистров, два счетчика, дешифратор, блок элементов И, элемент НЕ и блок формирования команд, отличающееся тем, что в него введены n входных узлов, счетный узел, коммутатор, два шинных формирователя, второй элемент НЕ, узел блокировки и m реле c m резисторами, причем входы n входных узлов являются первой группой входов устройства, вторая группа входов которого является входами счетного узла, первый выход которого соединен со счетным входом первого счетчика, группа выходов которого соединена с первой группой входов второго регистра, вторая группа входов которого соединена с группой выходов второго счетчика, счетный вход которого соединен с выходом первого счетчика, вход сброса которого соединен со входом сброса второго счетчика и с первым выходом дешифратора, группа входов которого соединена с группой выходов первого шинного формирователя, группа входов которого соединена с первой группой входов-выходов коммутатора и третьей группой входов-выходов блока формирования команд, первая и вторая группы входов-выходов которого являются первой и второй группами входов-выходов устройства, выход сброса блока формирования команд соединен с первым входом узла блокировки, второй вход которого соединен с выходом второго элемента НЕ, вход которого соединен с первыми управляющими входами четвертого и пятого регистров и первым выходом первого шинного формирователя, второй выход которого соединен со входом первого элемента НЕ и с первым входом коммутатора, второй вход которого соединен с третьим выходом первого шинного формирователя, выход первого элемента НЕ соединен с первым входом первого регистра, группа входов которого соединена с выходами n узлов входа, второй вход первого регистра соединен с третьим выходом дешифратора, второй вход которого соединен с первым входом второго регистра, группа выходов которого соединена с группами выходов второго шинного формирователя и первого регистра, с первой группой входов блока элементов И, с группами входов третьего и четвертого регистров и со второй группой входов-выходов коммутатора, второй вход второго регистра соединен со вторым выходом счетного узла, второй вход четвертого регистра соединен с четвертым выходом дешифратора, шестой выход которого соединен со входом третьего регистра, группа выходов которого соединена со второй группой входов блока элементов И, группа выходов которого соединена с группой входов пятого регистра, второй вход которого соединен с пятым выходом дешифратора, седьмой и восьмой выходы которого соединены соответственно с первым и вторым входами второго шинного формирователя, каждый вход из группы входов которого соединен через соответствующий резистор со входом соответствующей m-й обмотки реле и соответствующим выходом четвертого или пятого регистра, выходы узла блокировки соединены с выходами обмоток реле, цепи контактов которых являются третьей группой входов-выходов устройства, причем блок формирования команд содержит центральный процессор, супервизор, часы реального времени, постоянное запоминающее устройство, два оперативных запоминающих устройства, два набора буферных регистров, индикаторы, клавиатуру, микропроцессор, набор шинных формирователей, драйвер для связи с АСУ и драйвер для связи с ПЭВМ, первая группа входов-выходов которого является первой группой входов-выходов устройства, вторая группа входов - выходов которого является первой группой входов-выходов драйвера для связи с АСУ, вторая группа входов-выходов которого соединена со второй группой входов-выходов драйвера для связи с ПЭВМ и микропроцессора, первая группа входов-выходов которого соединена с группой входов-выходов второго оперативного запоминающего устройства, третья группа входов-выходов микропроцессора соединена с первой группой входов-выходов второго набора буферных регистров, вторая группа входов-выходов которого соединена с группами входов-выходов процессора и супервизора, часов реального времени, постоянного запоминающего устройства, первого оперативного запоминающего устройства и первой группой входов-выходов набора шинных формирователей, вторая группа входов-выходов которого является третьей группой входов-выходов блока формирования команд, выход сброса которого является выходом супервизора, группа входов-выходов которого соединена с группой входов-выходов первого набора буферных регистров, клавиатурой и индикаторами, причем входной узел содержит четыре резистора, стабилитрон, диод, транзистор и оптрон, выход которого является выходом входного узла, первый вход которого соединен со входами первого резистора и второго резистора, выход которого соединен с коллектором транзистора и первым входом оптрона, второй вход которого соединен с эмиттером транзистора, входом третьего резистора и анодом диода, катод которого соединен с базой транзистора, выходом первого резистора и катодом стабилитрона, анод которого соединен с выходом третьего резистора и является вторым входом входного узла, третий вход оптрона соединен со входом четвертого резистора, выход которого соединен с четвертым входом оптрона, причем счетный узел содержит три резистора, диод, оптрон, конденсатор и микропроцессор, первый выход которого является первым выходом счетного узла, второй выход которого является вторым выходом микропроцессора, первый вход которого соединен со входом третьего резистора и первым выходом оптрона, второй выход которого соединен со входом конденсатора и четвертым входом микропроцессора, второй и третий входы которого соединены с выходом конденсатора и выходом третьего резистора, первый вход оптрона соединен с выходами первого и второго резисторов и катодом диода, анод которого соединен со вторым входом оптрона, входом второго резистора и является вторым входом счетного узла, первый вход которого является входом первого резистора, причем узел блокировки содержит пять резисторов, диод, первый транзистор и второй транзистор, коллектор которого является выходом узла блокировки, первый вход которого соединен с анодом диода и входами первого резистора и второго резистора, выход которого соединен со входом третьего резистора и базой первого транзистора, эмиттер которого соединен с выходом третьего резистора, коллектор первого транзистора соединен со входом четвертого резистора, выход которого соединен со входом пятого резистора и базой второго транзистора, эмиттер которого соединен с выходом пятого резистора, катод диода является вторым входом узла блокировки.

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭНЕРГОПОТРЕБЛЕНИЕМ | 1987 |

|

RU2043687C1 |

| RU 93018817 А, 27.05.1995 | |||

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ФУНКЦИОНИРОВАНИЯ БЛОКА ОБРАБОТКИ ДАННЫХ | 1998 |

|

RU2143727C1 |

| US 5155846 А, 13.10.1992 | |||

| US 5390066 А, 14.02.1995 | |||

| Устройство для контроля сопротивления изоляции сетей постоянного тока | 1976 |

|

SU561149A1 |

| ПЛАСТИНЧАТЫЙ НАСОС | 2000 |

|

RU2184875C1 |

Авторы

Даты

2004-01-10—Публикация

2001-05-10—Подача