Изобретение относится к импульсной технике и может быть использовано в устройствах синхронизации, задатчиках и синтезаторах частоты.

Известен преобразователь код - частота (а.с. 1206959 H 03 M 5/10, публ. БИ N 3-86), содержащий два регистра, два комбинационных сумматора, компаратор, блок логики, шины: входного кода, режима, тактирующих импульсов, выхода. Известный преобразователь производит точное преобразование кода в частоту, причем выходная частота прямо пропорциональна входному коду и обратно пропорциональна коду режима. Это накладывает определенные ограничения на допустимые значения входного и режимного кодов и, как следствие, на число частот в частотной сетке. Кроме того, данный преобразователь является сложным.

Наиболее близким по технической сущности является преобразователь код - частота (патент 2092973 H 03 М 5/10, H 03 K 23/66, публ. БИ N 28-97, фиг. 3), взятый в качестве прототипа, содержащий блок коррекции, комбинационный сумматор, регистр, элемент И, шины: кода коррекции, входного кода, тактирующих импульсов, выхода.

Частота выходных импульсов в известном преобразователе выражается формулой:

F = NF0(2m-K)=ND

где N - входной код;

K - корректирующий код;

F0 - частота тактирующих импульсов;

m - число разрядов комбинационного сумматора;

D - частотный шаг преобразования (дискретность) преобразователя.

Из приведенной формулы следует, что в данном преобразователе расширение частотной сетки достигается тем, что корректирующий код расширяет частотный шаг и область производимых частот, что является его недостатком.

Задачей изобретения является расширение частотной сетки преобразователя код - частота при сохранении области производимых им частот.

Технический результат, который может быть получен при его осуществлении, состоит в том, что уменьшается в кратное число раз частотный шаг преобразователя при сохранении области производимых частот, упрощается программирование выходной частоты ввиду прямой пропорциональности ее входному коду и коду смещения.

Указанный технический результат достигается тем, что в известный преобразователь код-частота, содержащий шину входного кода, шину тактирующих импульсов, шину выхода, комбинационный сумматор и регистр, выход которого подключен к первому входу комбинационного сумматора, первый выход которого подключен к входу данных регистра, тактирующий вход которого подключен к шине тактирующих импульсов, дополнительно введены блок смещения и шина кода смещения, комбинационный сумматор снабжен третьим входом, причем первый вход блока смещения подключен к шине тактирующих импульсов, второй вход - к шине кода смещения, выход блока смещения подключен к третьему входу комбинационного сумматора, второй вход которого соединен с шиной входного кода, а второй выход комбинационного сумматора является выходом преобразователя.

В преобразователе код-частота блок смещения содержит инвертор, счетчик и компаратор кодов, причем первый вход блока смещения подключен к инвертору, выход которого подключен к счетному входу счетчика, выход кода состояния которого подключен к первому входу компаратора, второй вход которого подключен к второму входу блока смещения, выход компаратора является выходом блока смещения.

В преобразователе код-частота может быть достигнут дополнительный технический результат, заключающийся в уменьшении аппаратных затрат. С этой целью в преобразователь код-частота дополнительно введен формирователь импульсов, первый вход которого подключен к второму выходу комбинационного сумматора, второй вход формирователя подключен к шине тактирующих импульсов, выход формирователя является выходом преобразователя.

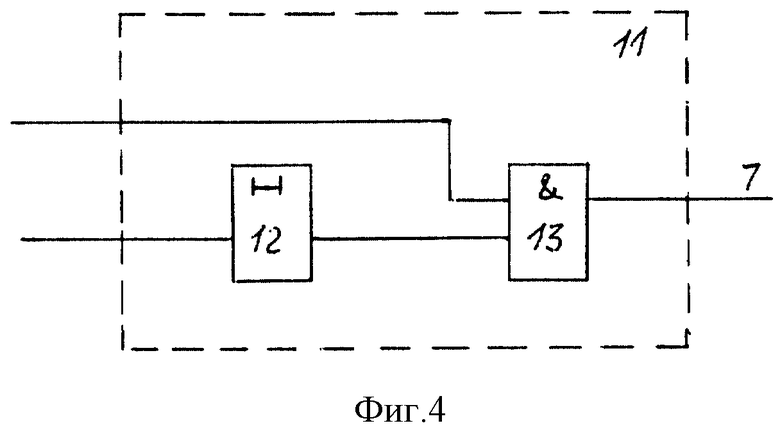

Формирователь импульсов содержит последовательно включенные элемент задержки и элемент И, второй вход которого является первым входом формирователя, вход элемента задержки является вторым входом формирователя, выход элемента И является выходом формирователя.

Наличие указанных признаков позволяет сделать вывод о новизне технического решения.

При сравнении заявленного решения с другими техническими решениями в данной области техники не выявлена совокупность признаков, отличающих заявленное решение от прототипа, что позволяет сделать вывод о соответствии заявленного технического решения критерию изобретения "изобретательский уровень".

Таким образом, заявленное техническое решение является новым, имеет изобретательский уровень, промышленно применимо.

Сущность изобретения поясняется чертежами, где на фиг. 1 изображена функциональная схема преобразователя код-частота, на фиг. 2 - функциональная схема блока смещения, на фиг. 3 - функциональная схема преобразователя код-частота с формирователем импульсов, на фиг. 4 - представлен один из вариантов функциональной схемы формирователя импульсов.

Преобразователь код-частота (фиг. 1) содержит комбинационный сумматор 1, регистр 2, блок 3 смещения, шину 4 входного кода, шину 5 тактирующих импульсов, шину 6 кода смещения, шину 7 выхода преобразователя. Шина 4 входного кода подключена к второму входу комбинационного сумматора 1, первый вход которого подключен к выходу регистра 2, вход данных которого соединен с первым выходом комбинационного сумматора 1. Шина 5 тактирующих импульсов подключена к первому входу блока 3 смещения и тактирующему входу регистра 2. Второй вход блока 3 смещения соединен с шиной 6 кода смещения, а выход блока 3 смещения подключен к третьему входу комбинационного сумматора 1, второй выход которого является выходом 7 преобразователя.

Блок 3 смещения (фиг. 2) состоит из последовательно соединенных инвертора 8, счетчика 9 и компаратора 10, второй вход компаратора подключен к шине 6 кода смещения. Вход инвертора 8 подключен к шине 5 тактирующих импульсов, выход компаратора 10 является выходом блока 3 смещения. Блок 3 смещения может быть выполнен на микросхемах: К 561 ЛН1 (инвертор 8), К 561 ИЕ10 (счетчик 9), К 561 ИП2 (компаратор 10).

Дополнительно в преобразователе код-частота между вторым выходом комбинационного сумматора 1 и шиной 7 выхода введен формирователь 11 импульсов (фиг. 3), который имеет второй вход, подключенный к шине 5 тактирующих импульсов.

Формирователь 11 импульсов (фиг. 4) состоит из последовательно соединенных элемента 12 задержки и элемента И 13, второй вход которого подключен к первому входу формирователя 11, а выход является выходом формирователя 11. Вход элемента 12 задержки является вторым входом формирователя 11.

Формирователь импульсов может быть выполнен на микросхеме К 561 ЛА7 и интегрирующей RC-цепи.

Преобразователь код-частота работает следующим образом. При нулевом коде на шине 6 смещения сигнал на выходе блока 3 смещения соответствует коду нуля. В этом случае тактирующие импульсы периодически производят запись в регистр 2 кода суммы:

Li = N + Li-1

где N - код на шине 4 входного кода;

Li-1 - код на выходе регистра 2, занесенный в регистр предыдущим тактирующим импульсом.

При этом каждый раз при достижении Li ≥ 2m (m - число разрядов комбинационного сумматора 1) на втором выходе комбинационного сумматора 1 вырабатывается сигнал переполнения и очередным тактирующим импульсом заносится в регистр 2 код суммы:

Li = N + Li-1 - 2m

При этом сигнал переполнения исчезает, содержимое регистра 2 становится меньше кода N и цикл повторяется вновь. Сигналы переполнения являются выходными импульсами. Длительность этих импульсов равна длительности периода тактирующих импульсов.

Частота соответствует формуле:

F = NF0/2m (1)

где F0 - частота тактирующих импульсов.

В том случае, когда код смещения K≠0, блок 3 смещения из тактирующих импульсов вырабатывает импульсы с периодом, равным 2k, и длительностью, равной K периодам тактирующих импульсов. K и k соответственно значение и максимальное число разрядов кода смещения. При этом сигнал импульса соответствует коду 1, а сигнал паузы - коду 0.

Тактирующие импульсы периодически производят запись в регистр 2 кодов сумм, образуемых комбинационным сумматором 1. При этом коды записываемых сумм соответствуют или Li = N + Li-1 или Li = N + 1 + Li-1 соответственно тому, какому коду соответствует сигнал на третьем входе комбинационного сумматора или 0, или 1.

При этом каждый раз при достижении Li ≥ 2m на втором выходе комбинационного сумматора 1 вырабатывается сигнал переполнения и очередной тактирующий импульс заносит в регистр 2 код суммы или Li = N + Li-1 - 2m или Li = N + 1 + Li-1 - 2m соответственно тому, какому коду соответствует сигнал в это время на третьем входе комбинационного сумматора или 0, или 1.

После этого сигнал переполнения исчезает, содержимое регистра 2 становится меньше значения кода N+1 и цикл повторяется вновь.

За период сформированных блоком смещения 3 импульсов в регистр 2 K раз заносится код суммы Li = N + 1 + Li-1 и (2k-K) раз код суммы Li = N + L1-1. При этом содержимое регистра 2 за 2k тактов возрастает на:

Δ L = (N+1)K+N(2k-K) = N2k+K (2)

или среднее значение приращения кода суммы в регистре 2 за 1 такт составляет;

Δ Lср = Δ L/2k = N + K/2k (3)

Справедливость формулы (3) очевидна, если на рассматриваемые 2k тактов не произошло переполнения комбинационного сумматора 1. Формула (3) справедлива и в случае возникновения указанного переполнения или переполнений. При этом приращение суммы в регистре 2 состоит из приращений при отсутствии сигнала переполнения комбинационного сумматора 1 и при наличии сигнала. При отсутствии сигнала переполнения каждый тактирующий импульс увеличивает код суммы регистра 2 на N или N+1 соответственно тому, какой в это время код на третьем входе комбинационного сумматора 1 ноль или единица. При наличии сигнала переполнения приращение состоит из двух частей: Δ L1 = 2m - Li-1 и Δ L2.

Причем Δ L2 = N + Li-1 - 2m или Δ L2 = N + 1 + Li-1 - 2m, а общее приращение за этот такт, определяемое как сумма Δ L1 и Δ L2, равно N или N+1 соответственно тому какой в это время код на третьем входе комбинационного сумматора 1 ноль или единица.

Из этого следует, что и в этом случае общее приращение кода суммы в регистре 2 за 2k тактов соответствует формуле (2). Из формулы (3) следует, что Δ Lср = Nср и частота вырабатываемых импульсов по аналогии с формулой (1) выражается формулой;

F = NсрF0/2m = NF0/2m + KF0/2m+k (4)

Второе слагаемое формулы (4) есть смещение частоты в пределах шага F0/2m, обусловленное кодом смещения. Текущее значение частоты вырабатываемых импульсов имеет флуктуацию и потому не соответствует формуле (4).

Флуктуация вызывается двумя факторами:

- биением частоты при нулевом коде смещения по той причине, что дробь 2m/N не всегда делится без остатка и циклы формирования периода выходных импульсов начинаются с разных значений кода Li-1;

- вариацией кода на третьем входе комбинационного сумматора при коде смещения, не равном нулю.

Флуктуация выходной частоты имеет периодический характер. Период флуктуации определяется по формуле:

T = Nср•c•2m/F0 = (N+K/2k)•c•2m/F0 (5)

где c - наименьший делитель дроби 2m/Nср=2m+k/(N2k+K) (после отделения целой части; при делении без остатка c=1, флуктуация отсутствует).

В течение периода по формуле (5) достигается точное соответствие формуле (4).

Указанный выше технический результат достигается тем, что при изменении кода смещения на единицу изменение частоты происходит на величину F0/2m+k, что фактически является новым частотным шагом преобразователя.

Очевидно, что если в блоке 3 смещения применить счетчик с другим основанием счета (счисления), например 3 или 5, то получится деление исходного частотного шага на это же число.

Если основанием счисления является число 2k, то веса разрядов входного кода и кода смещения становятся подобными весами одного двоичного кода с числом разрядов, равным сумме разрядов этих кодов, и программирование частоты становится предельно простым.

Счетчик 9 блока 3 смещения (фиг. 2) с числом разрядов k считает поступающие на его счетный вход выходные импульсы инвертора 8 и формирует период выходных импульсов равным 2k периодам тактирующей частоты.

Компаратор 10 вырабатывает сигнал кода "1" пока код выхода счетчика 9 меньше кода смещения. Когда код выхода счетчика 9 становится равным коду смещения или больше него, компаратор 10 вырабатывает сигнал кода "0". Инвертор 8 вносит временной сдвиг в процесс счета тактирующих импульсов. Тем самым в любом случае обеспечивается образование ожидаемой суммы на выходе комбинационного сумматора 1 к моменту занесения ее в регистр 2.

Формирователь 11 выходных импульсов (фиг. 3) производит выделение тактирующего импульса на шину выхода, когда на втором выходе комбинационного сумматора есть сигнал переполнения. Технический результат, получаемый посредством введения формирователя 11, заключается в уменьшении минимально допустимого числа разрядов комбинационного сумматора 1 и регистра 2 на один разряд. Для преобразователя код-частота (фиг. 1) минимальное число разрядов ограничивается числом n+1, где n - число разрядов входного кода; в преобразователе (фиг. 3) минимальное число разрядов ограничивается числом n.

В формирователе 11 импульсов (фиг. 4) элемент 12 задержки исключает появление ложных импульсов на выходе элемента 13. При непосредственном подключении тактирующих импульсов к элементу 13 на выходе элемента 13 возникают ложные импульсы из-за того, что сигналы переполнения комбинационного сумматора 1 частично захватывают второй после возникновения сигнала переполнения тактирующий импульс.

Таким образом, вышеизложенные сведения свидетельствуют о возможности осуществления заявленного изобретения с помощью известных средств и что средство воплощения заявленного изобретения способно обеспечить достижение усматриваемого заявителем технического результата.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ КОД - ЧАСТОТА | 1995 |

|

RU2092973C1 |

| Устройство для выделения признаков изображений | 1988 |

|

SU1553997A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ УПАКОВОЧНОЙ МАШИНОЙ ЦИКЛИЧЕСКОГО ДЕЙСТВИЯ | 1999 |

|

RU2171213C2 |

| Устройство для управления автономным инвертором | 1990 |

|

SU1810973A1 |

| Устройство для контроля качества ферромагнитных изделий | 1987 |

|

SU1499212A1 |

| Устройство для селекции признаков при распознавании образов | 1989 |

|

SU1735877A1 |

| Преобразователь код-частота | 1984 |

|

SU1206959A1 |

| ЧАСТОТНЫЙ ДЕТЕКТОР | 1991 |

|

RU2007844C1 |

| Синтезатор частот | 1987 |

|

SU1610599A1 |

| Устройство для классификации сигналов | 1988 |

|

SU1674182A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах синхронизации, задатчиках и синтезаторах частоты. Техническим результатом является расширение частотной сетки преобразователя код-частота при сохранении области производимых им частот. Устройство содержит комбинационный сумматор, регистр, шину входного кода, шину тактирующих импульсов, шину выхода преобразователя, шину кода смещения, блок смещения, состоящий из инвертора, счетчика и компаратора, формирователь импульсов, состоящий из элемента задержки и элемента И. 3 з.п. ф-лы, 4 ил.

| ПРЕОБРАЗОВАТЕЛЬ КОД - ЧАСТОТА | 1995 |

|

RU2092973C1 |

| Преобразователь код-частота | 1984 |

|

SU1206959A1 |

| Трансформаторная подстанция открытого типа | 1982 |

|

SU1170541A1 |

| Преобразователь код-частота | 1987 |

|

SU1474849A1 |

| US 5357248 A, 18.10.1994. | |||

Авторы

Даты

2001-11-10—Публикация

2000-04-03—Подача